Asynchronous FIFO memory accomplishing unequal breadth data transmission

A first-in-first-out, data transmission technology, used in data conversion, electrical digital data processing, instruments, etc., can solve the problem of inability to directly read/write data with unequal widths, and improve overall efficiency, flexible and efficient data transmission. , the effect of simplifying the system design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

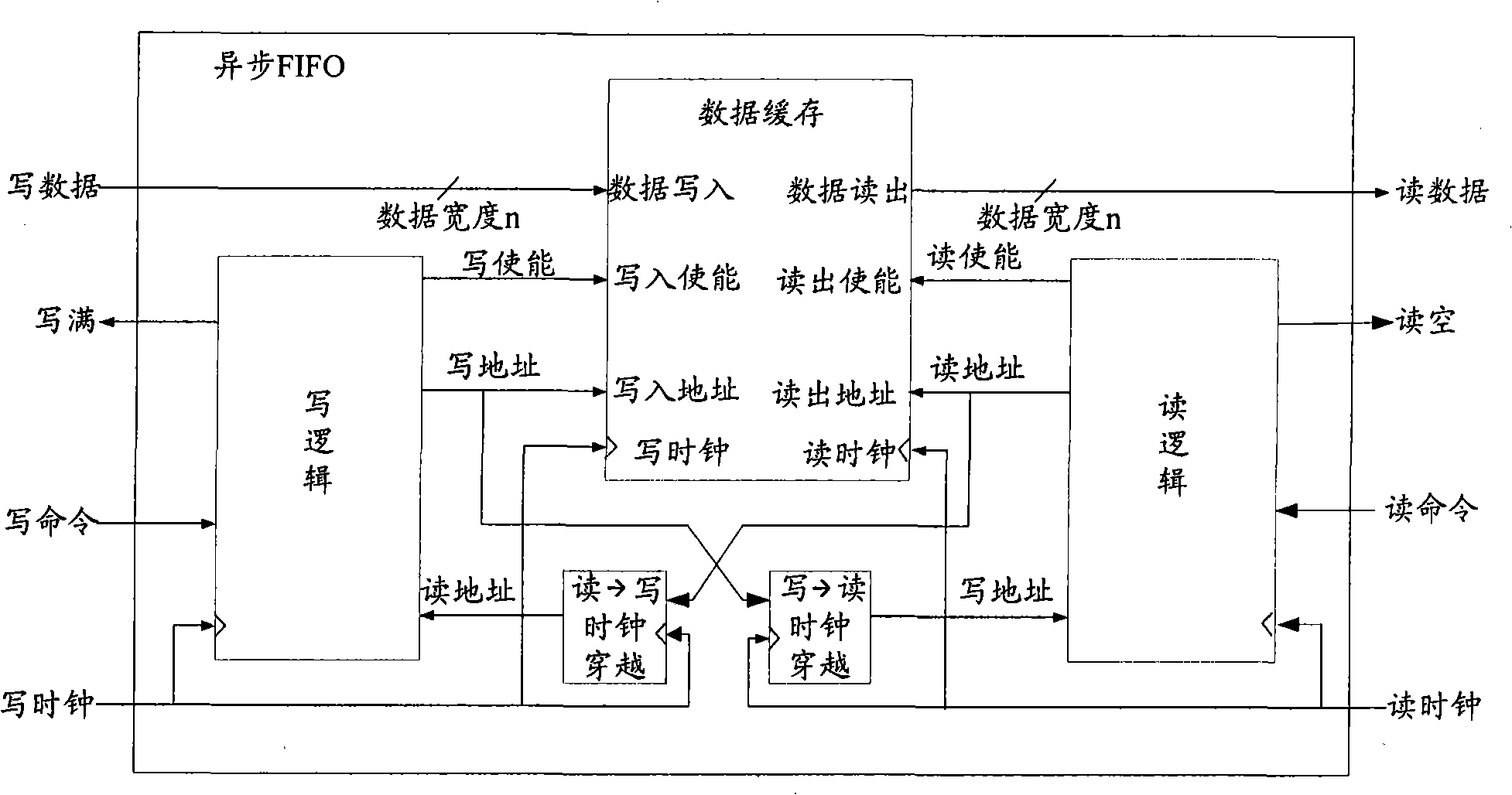

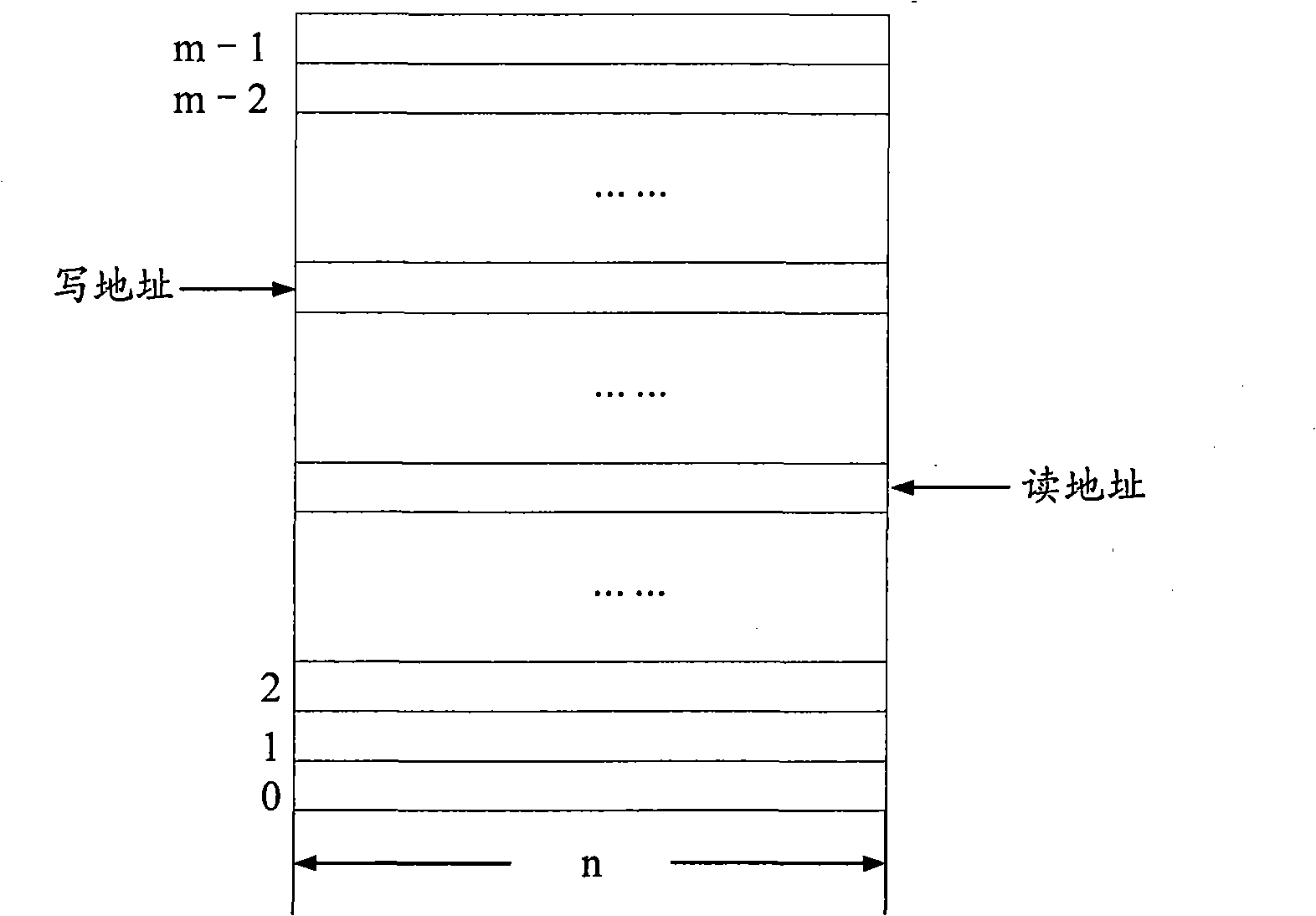

[0034] The present invention improves the functions of the write logic and the read logic, so that the read / write address pointers of the asynchronous FIFO memory correspond to data cache address spaces of different widths, and the read and write addresses are converted into The corresponding address in the data cache realizes the asynchronous clock domain transmission of unequal width data.

[0035] The specific implementation manners of the present invention will be described in further detail below in conjunction with the accompanying drawings.

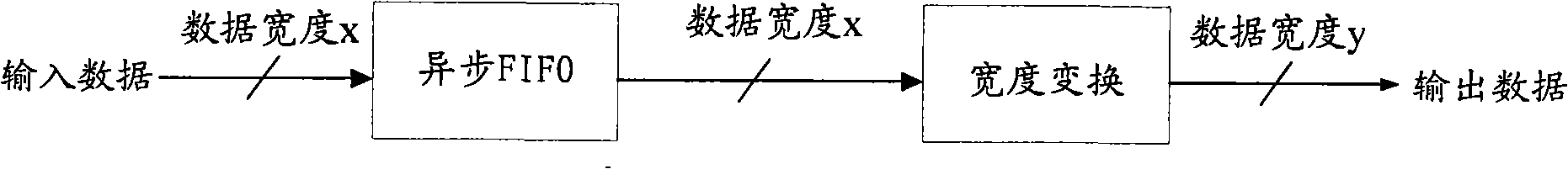

[0036] Such as Figure 4 as shown, Figure 4 It is a schematic diagram of the working principle of the asynchronous FIFO memory of the present invention, assuming that the write data width is x, the read data width is y, and x≠y.

[0037] Figure 4 The basic structure of the asynchronous FIFO shown with figure 2 same, but using Figure 4 The working principle diagram shown can directly realize that the width of the written da...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More