Memory device employing three-level cells and related methods of managing

A storage device, three-level technology, applied in information storage, static memory, read-only memory, etc., can solve problems such as limitations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

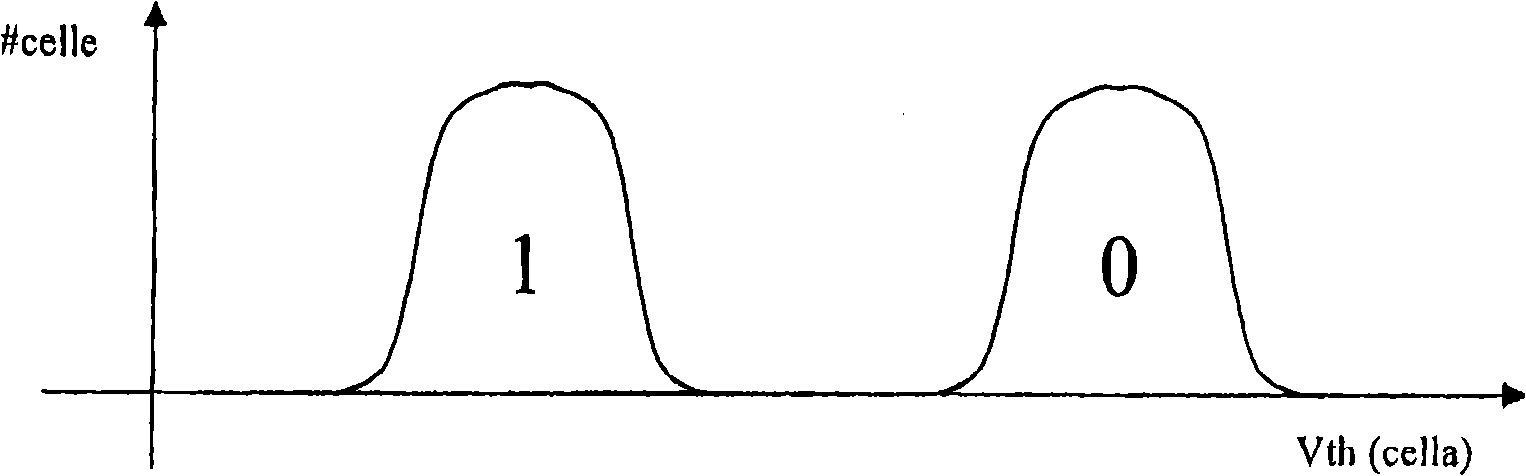

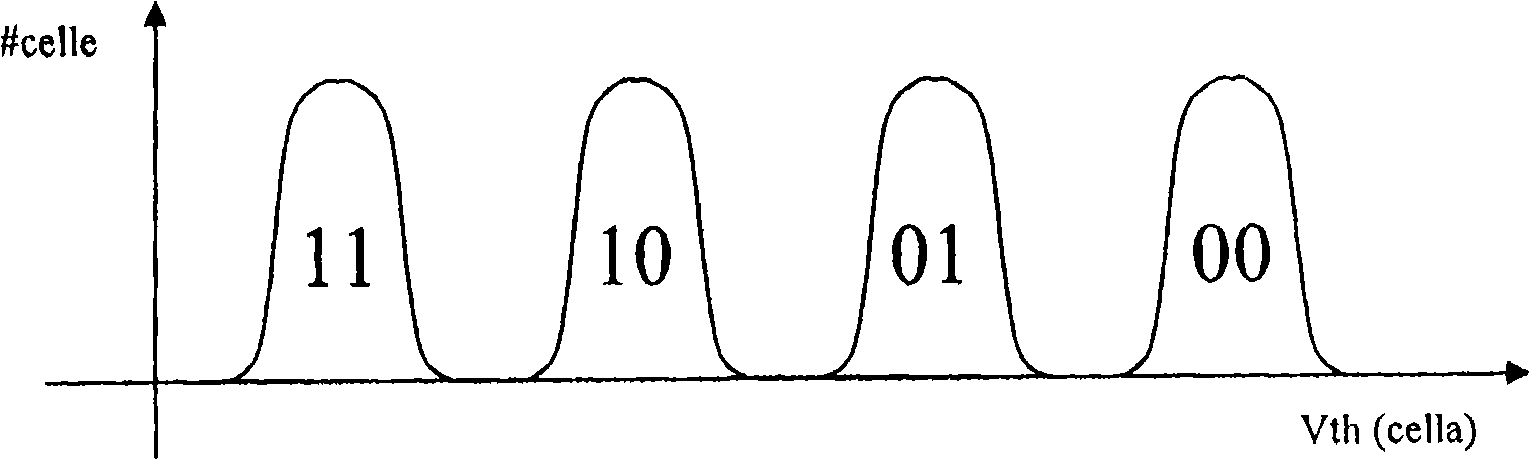

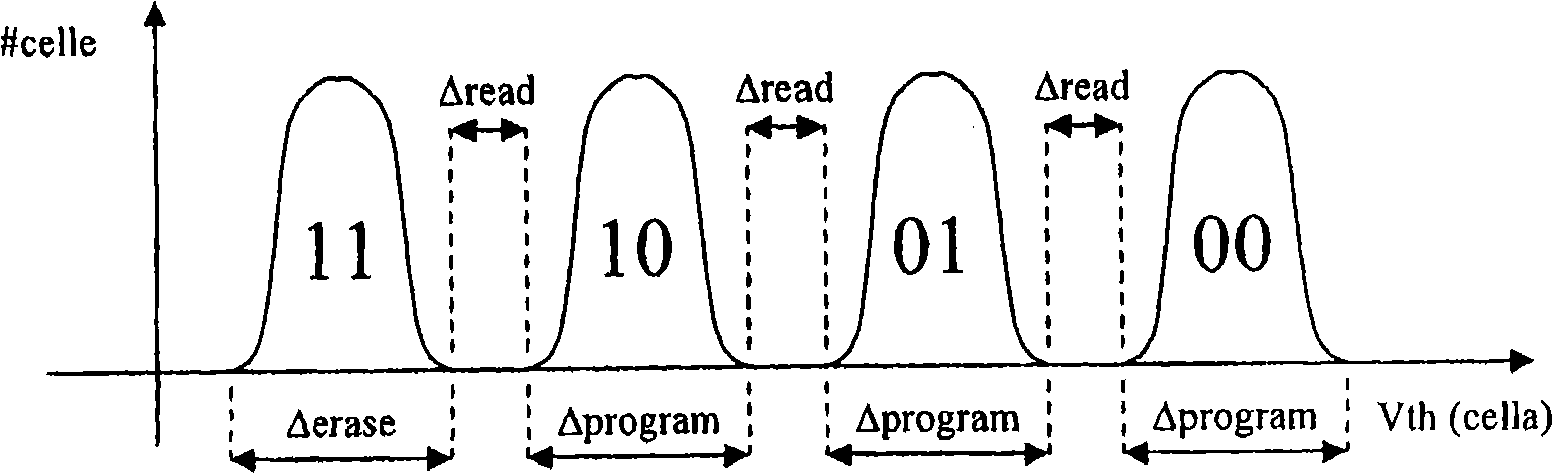

[0042] In the multi-level memory device of the present invention, each cell can take one of three possible logical values, which has the advantage of making the area occupied less than that of a one-bit memory device per cell, and having a lower area than that of a two-bit memory device per cell. Distribution of a smaller number of storage devices. Therefore, error correcting codes are not necessarily used to ensure reliability, and this allows "bit manipulation" to be entirely feasible.

[0043] In order to store a string of bits in a tri-level memory cell in an efficient manner, the encoding operations for a binary string that can be stored in a ternary string in a tri-level memory cell, and vice versa, need to be properly defined. Such as Figure 5As shown, 'A', 'B' and 'C' are the three levels that each cell can adopt ('A' is the erasing level, 'B' and 'C' are the two programming levels), for For each pair of cells (3×3=9 possible states), associate 3 bits (2 3 = 8 poss...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More