Patents

Literature

49 results about "Ternary numeral system" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The ternary numeral system (also called base 3) has three as its base. Analogous to a bit, a ternary digit is a trit (trinary digit). One trit is equivalent to log₂ 3 (about 1.58496) bits of information.

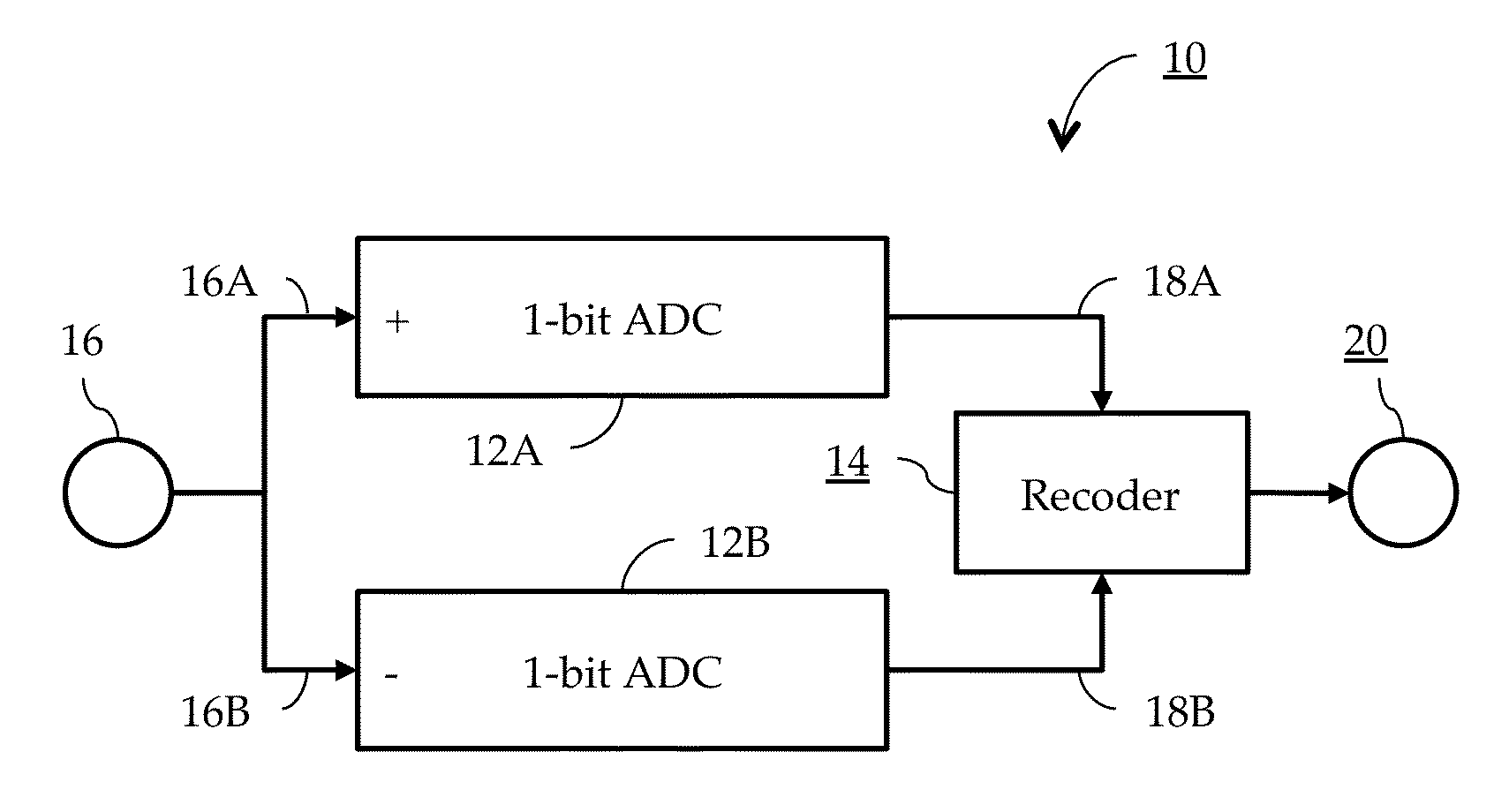

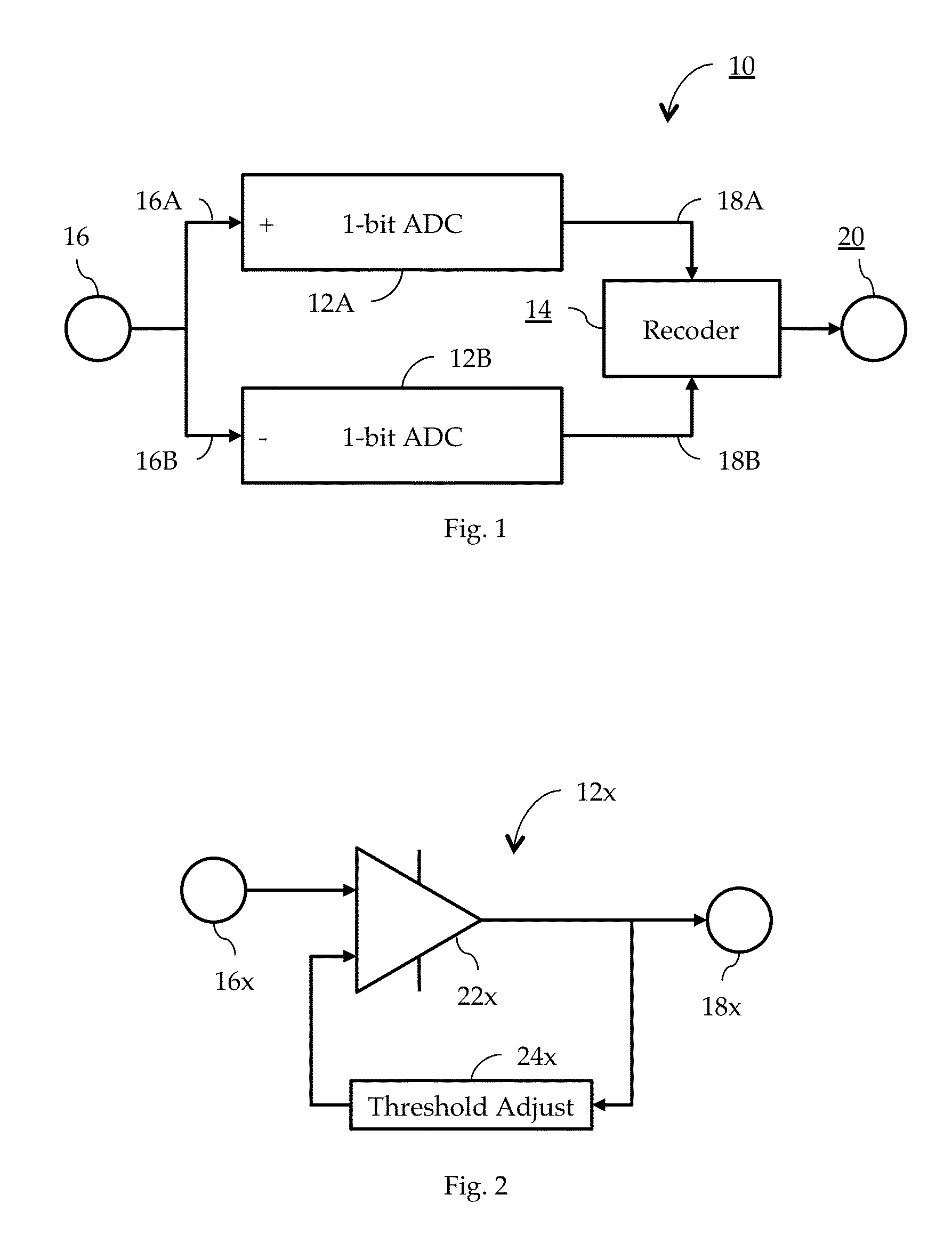

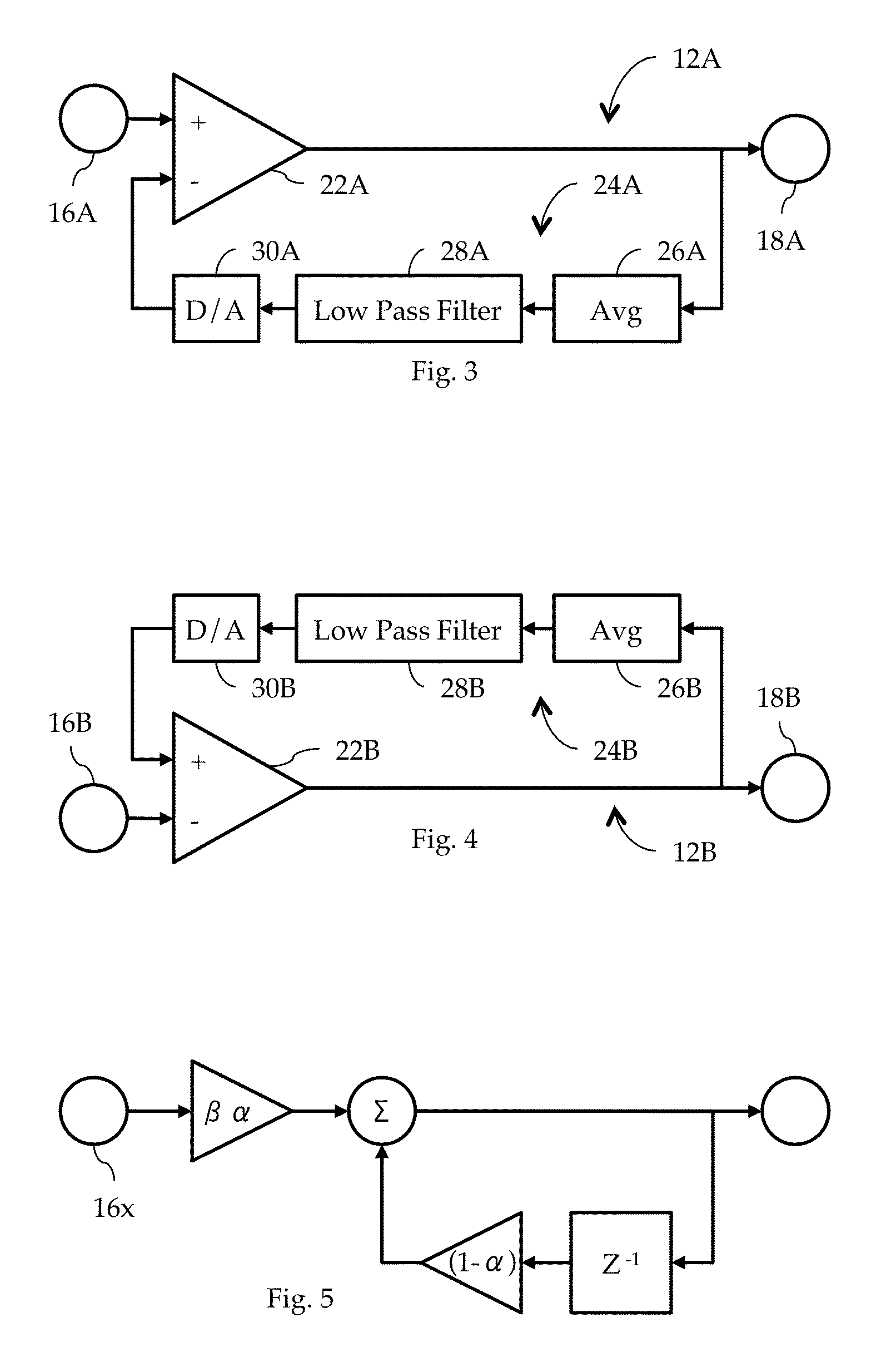

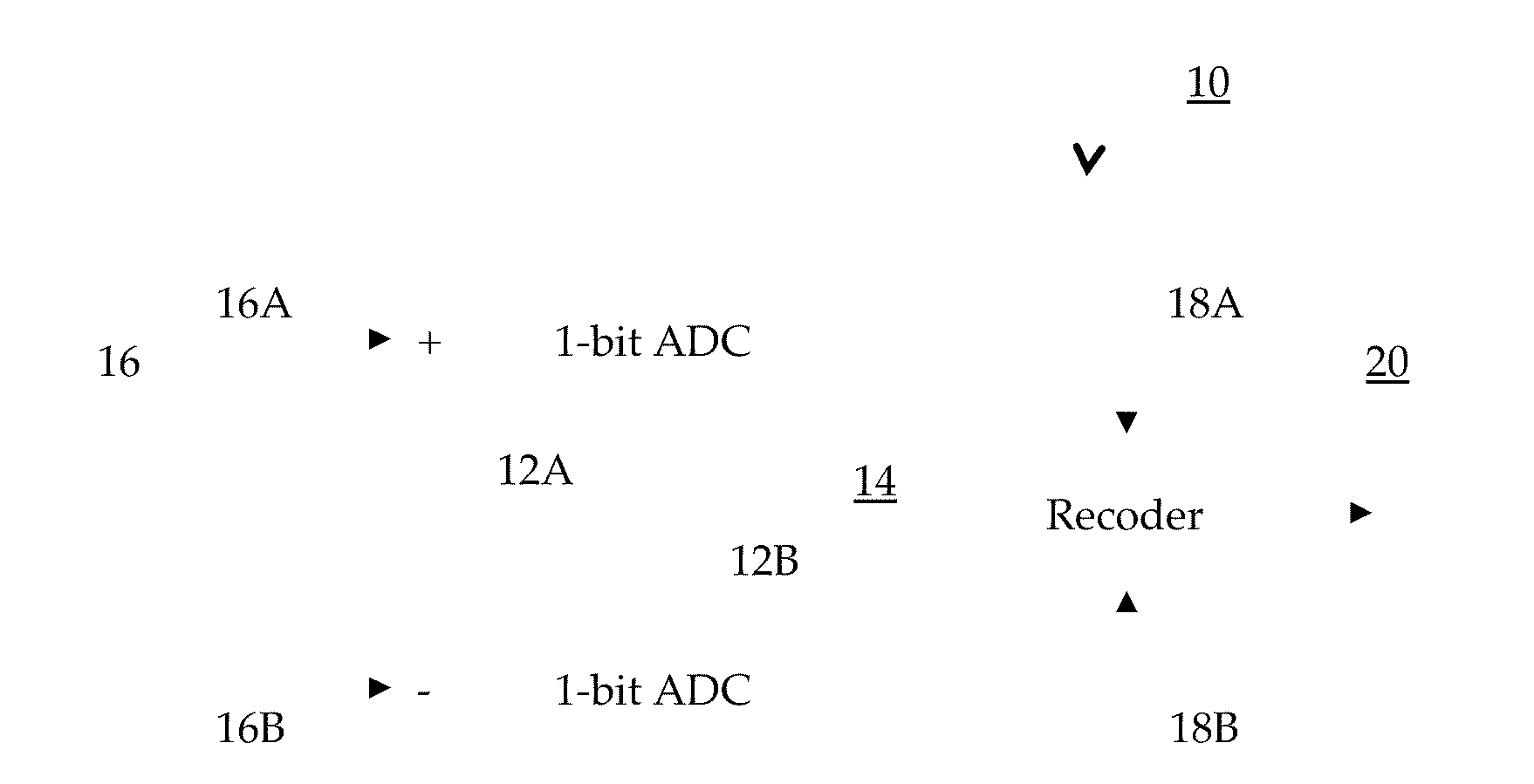

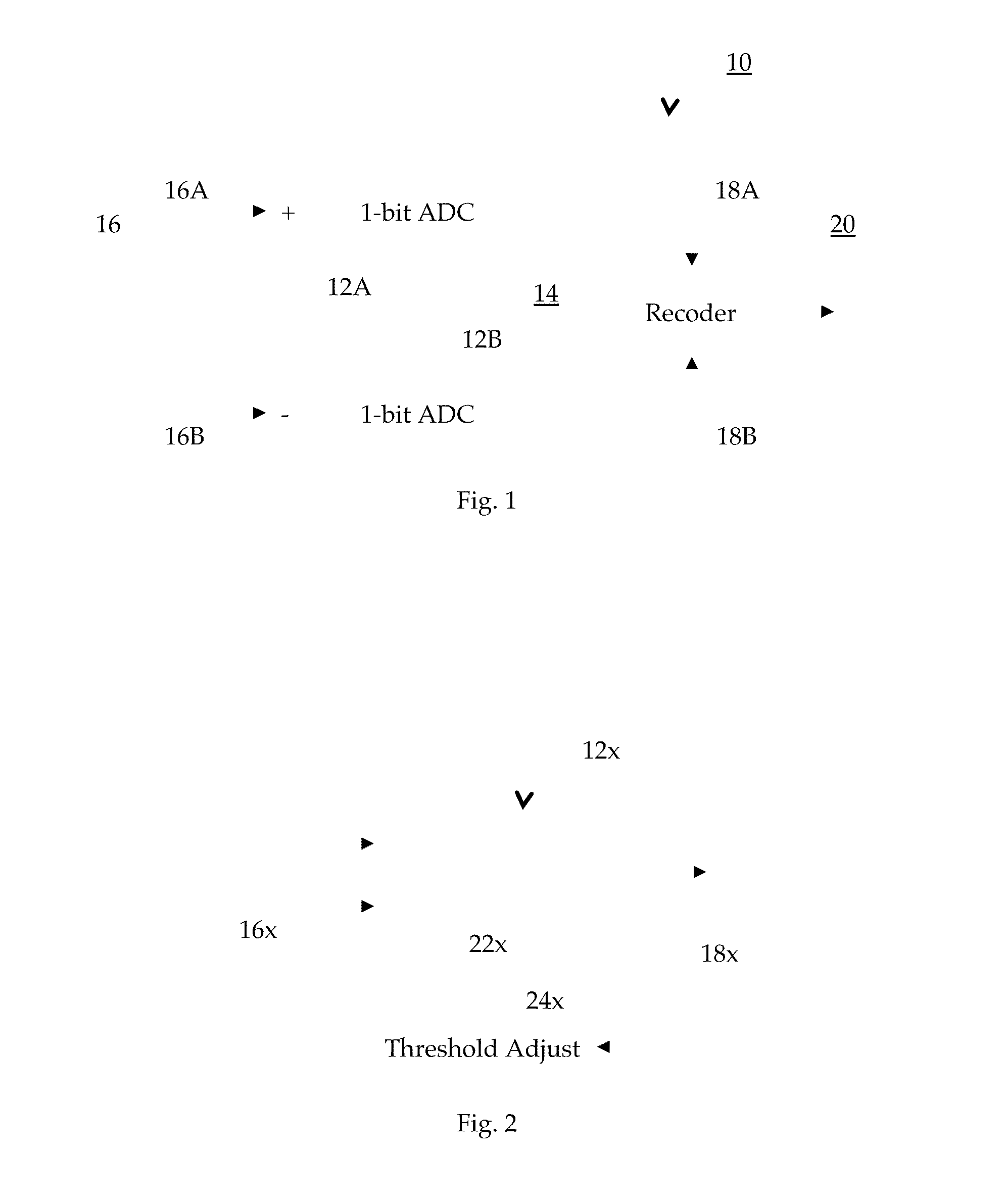

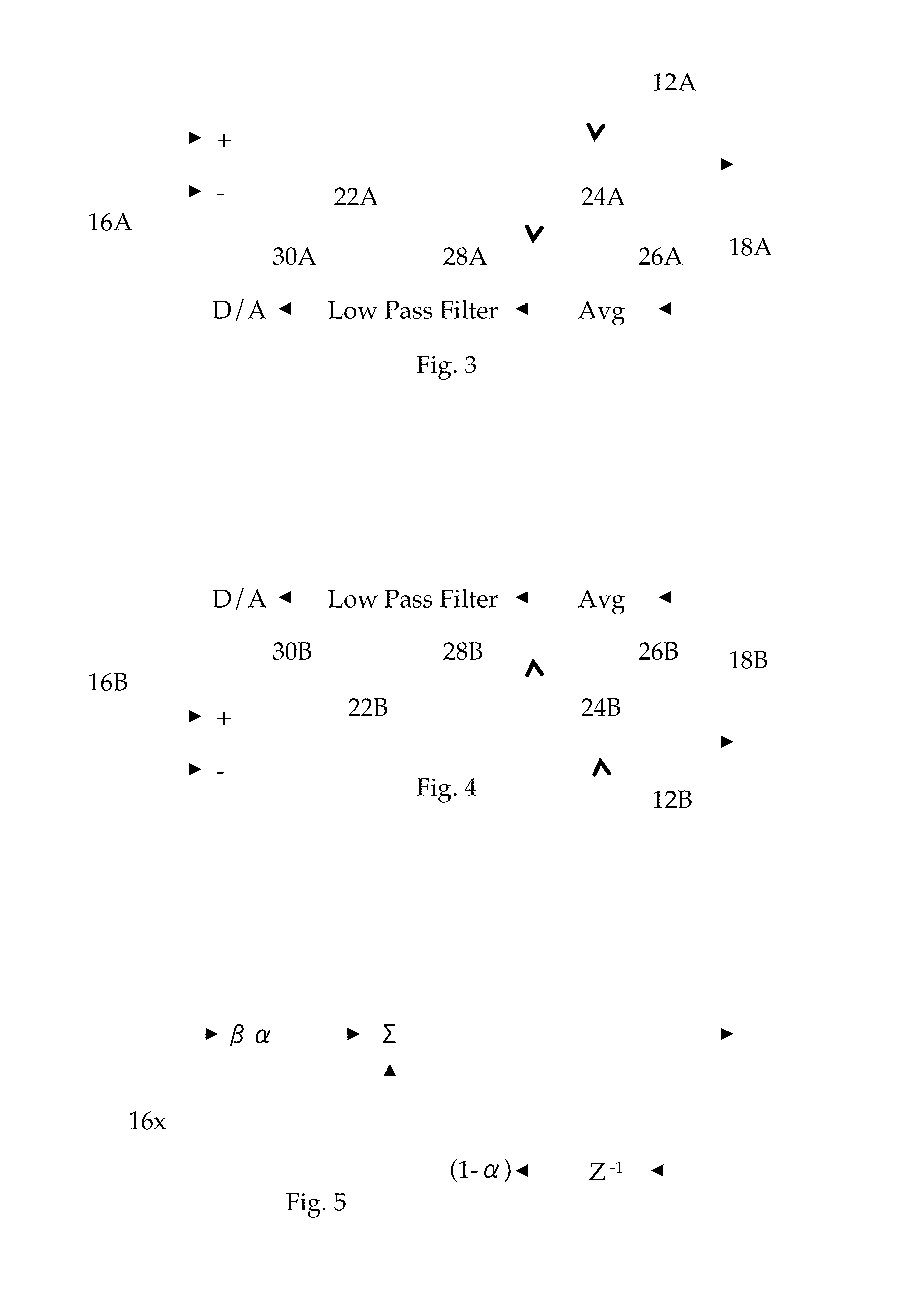

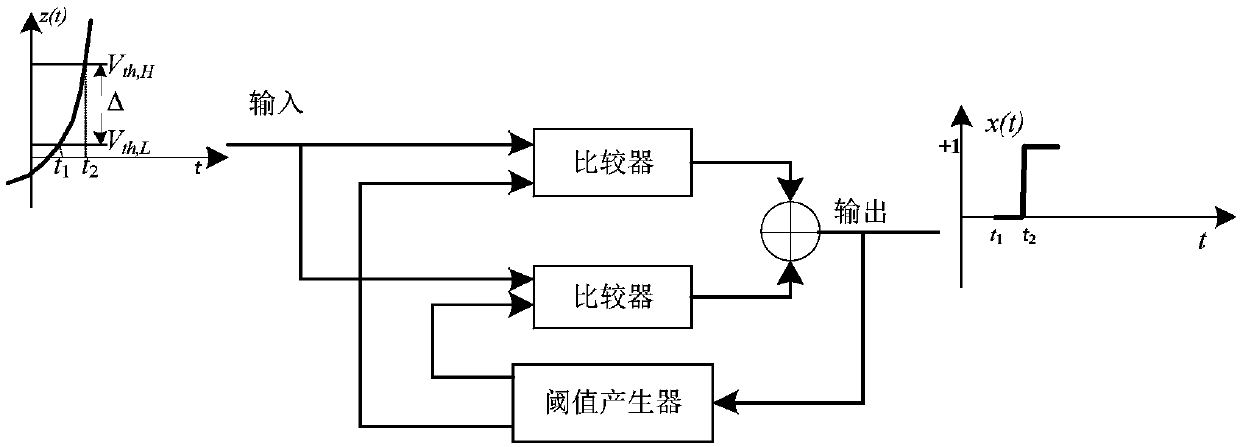

Adaptive ternary A/D converter for use in an ultra-wideband communication system

ActiveUS8436758B2Electric signal transmission systemsSynchronisation arrangementBuck converterĆuk converter

In an ultra-wideband communication system, a 1-trit ternary analog-to-digital converter (“ADC”) having dynamic threshold adaption and providing an output in ternary form [+1, 0, −1]. The ternary ADC includes a pair of 1-bit binary ADCs, one being configured in a non-inverting form, and one being configured in an inverting form. Each binary ADC includes an feedback network mechanism, thereby allowing for simultaneous and independent adaptation of the pair of thresholds, compensating for the effects of any DC offset that may be present. The use of a trit-based ternary encoding scheme improves system entropy.

Owner:DECAWAVE

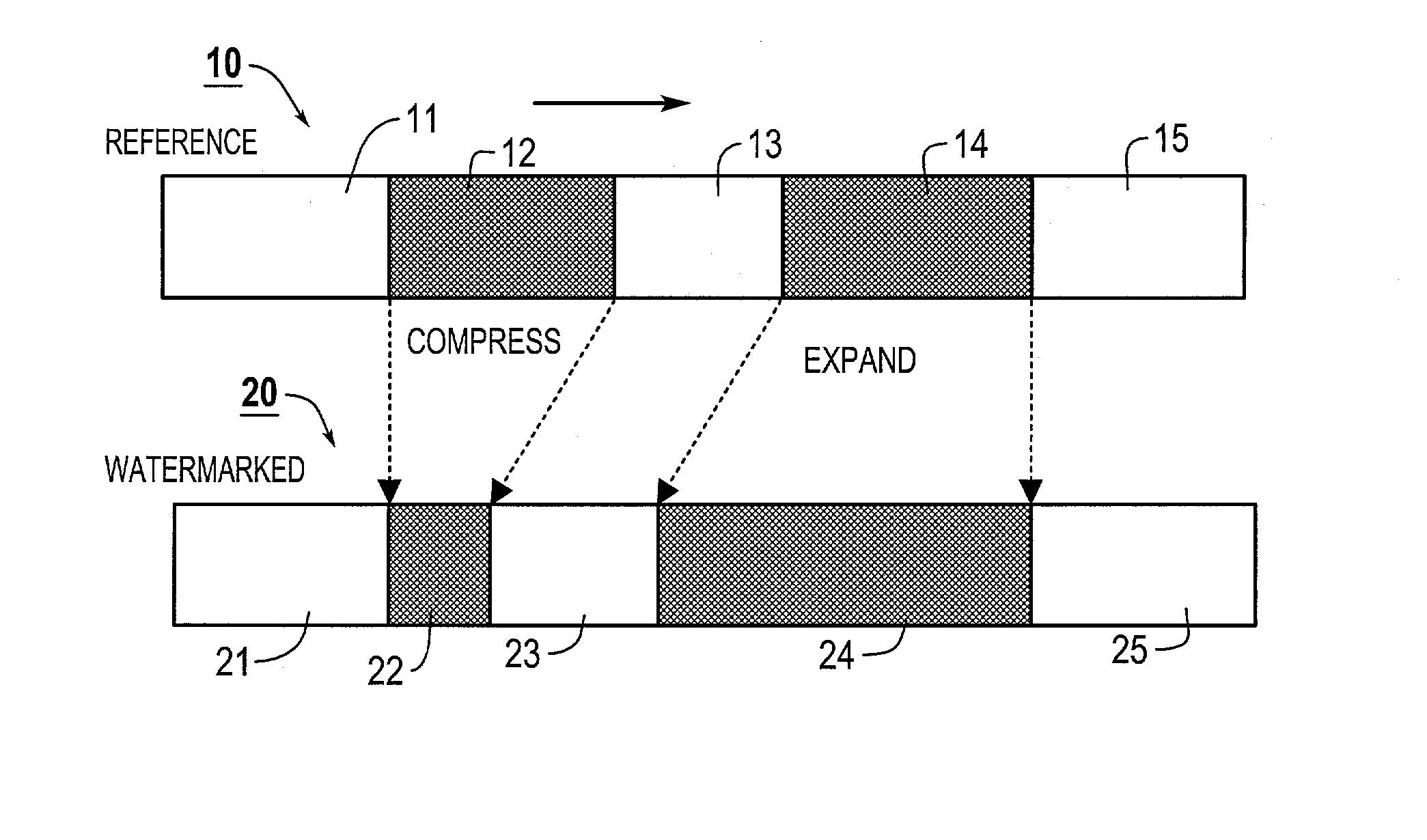

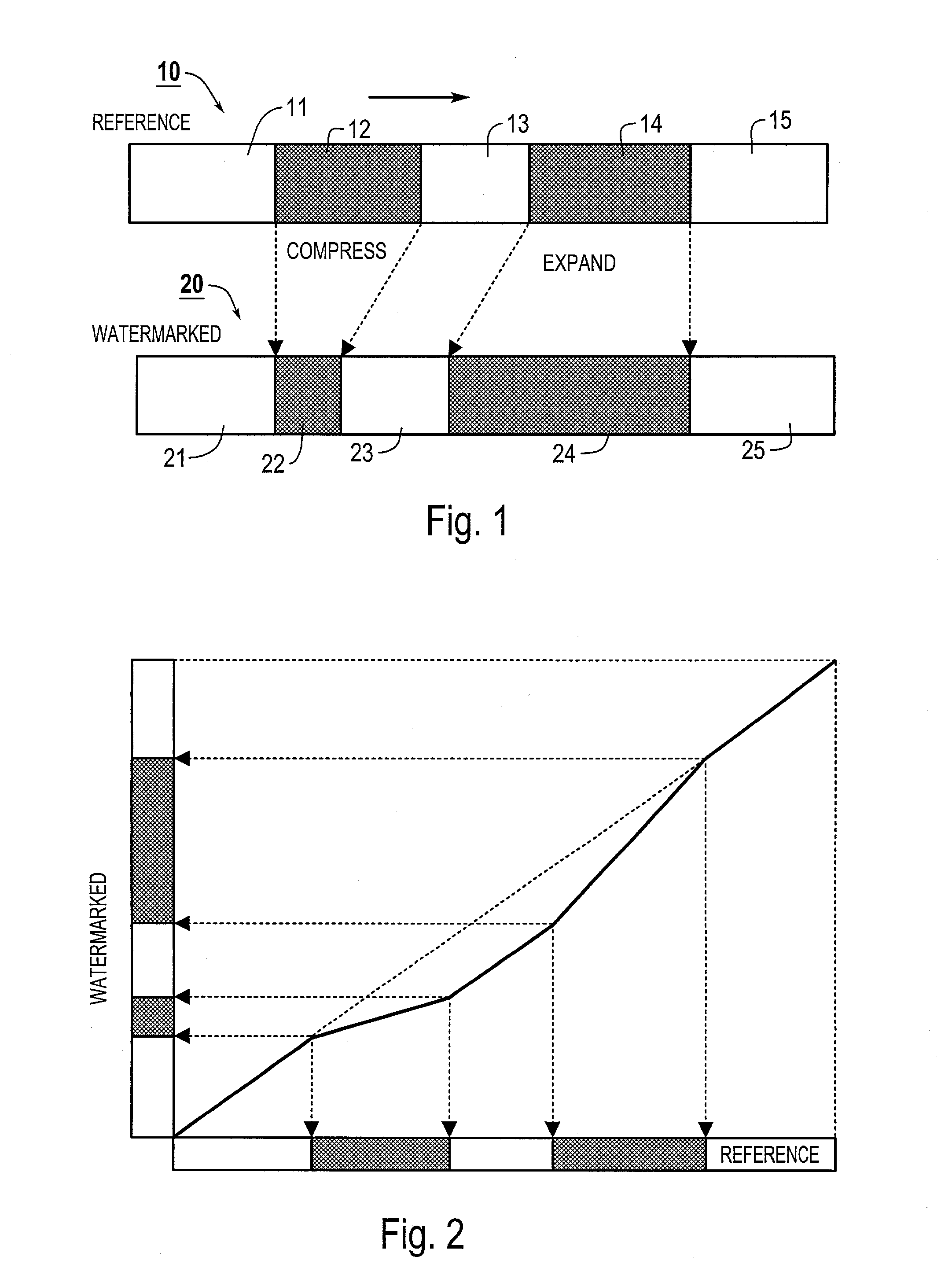

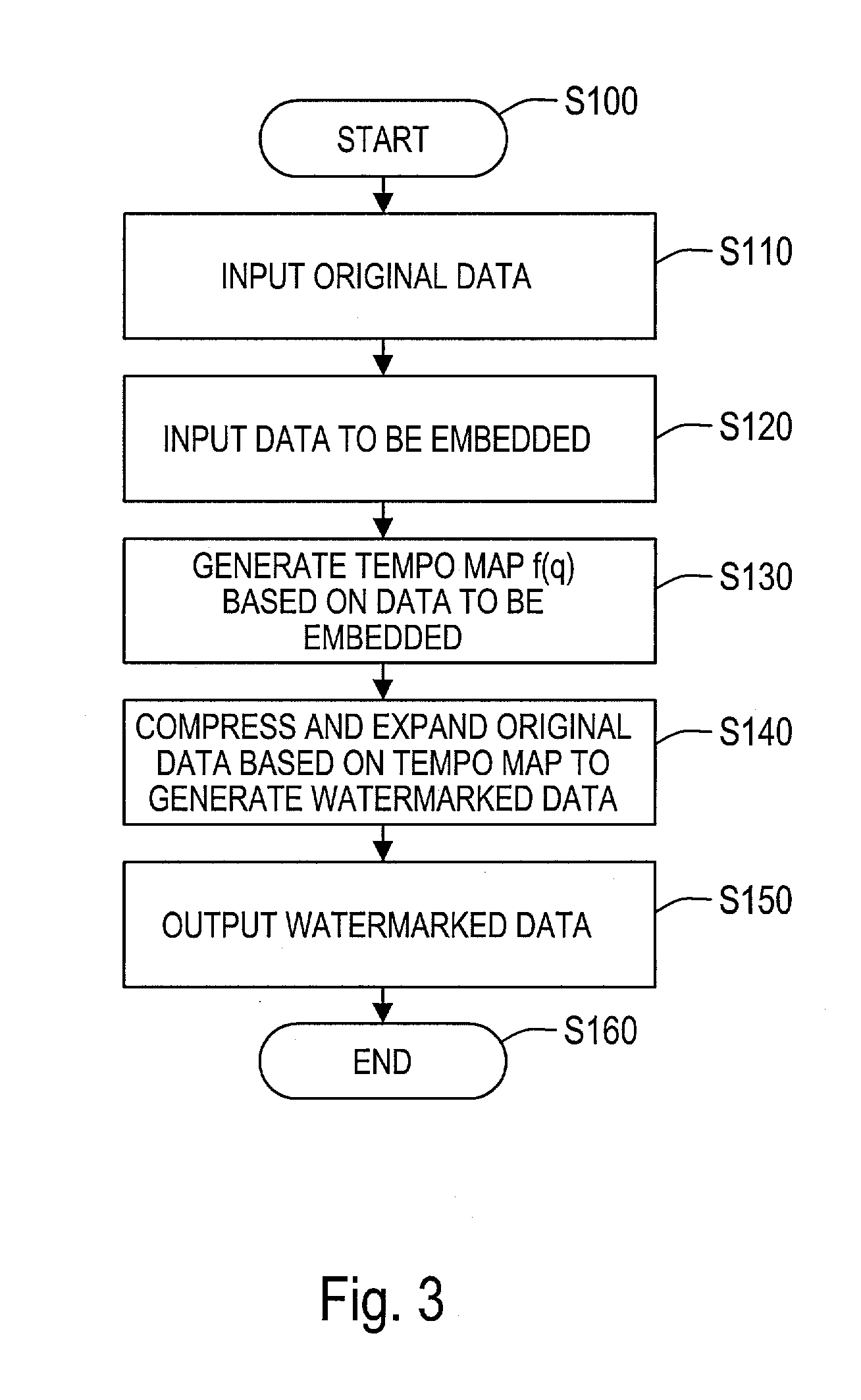

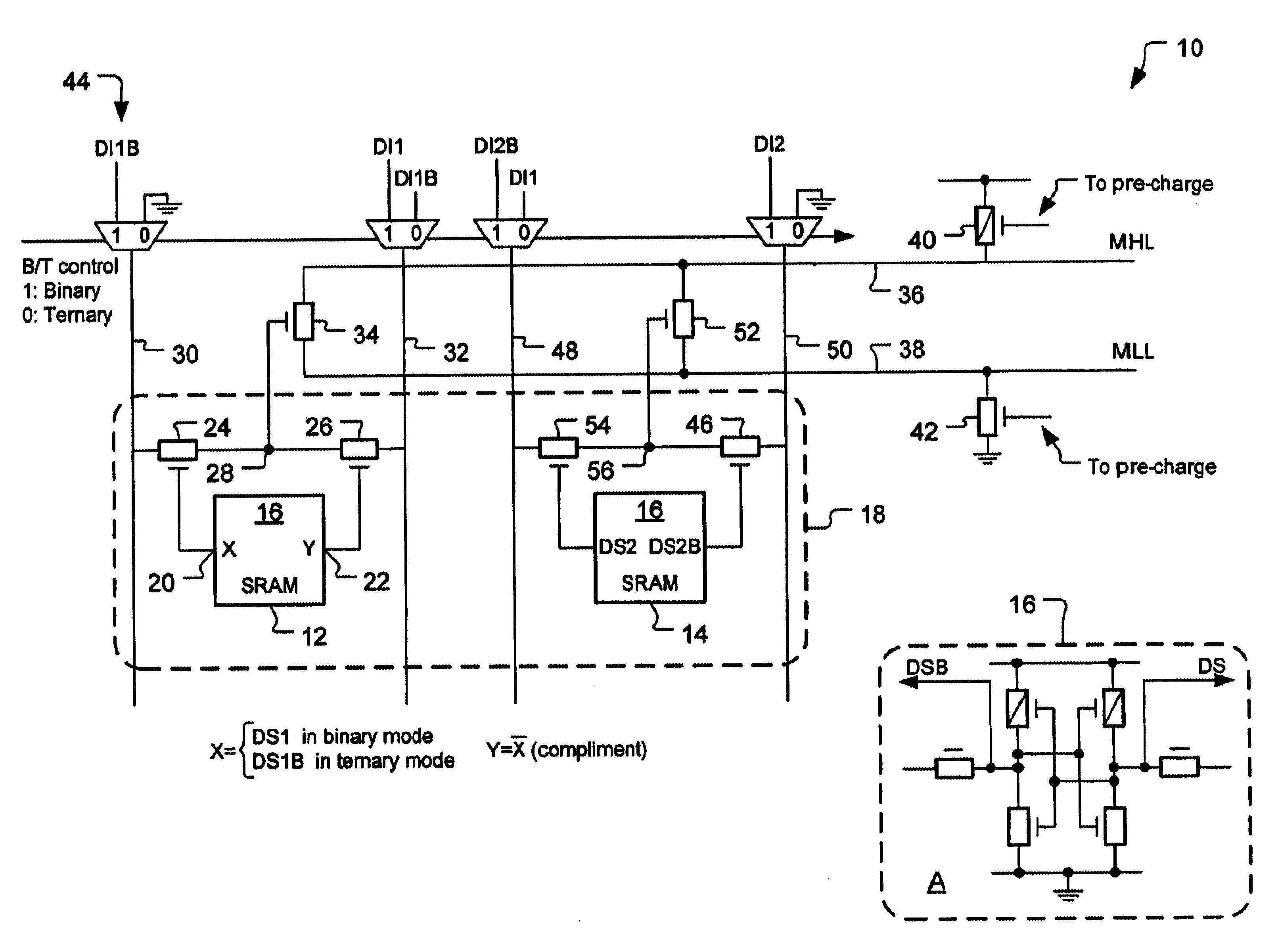

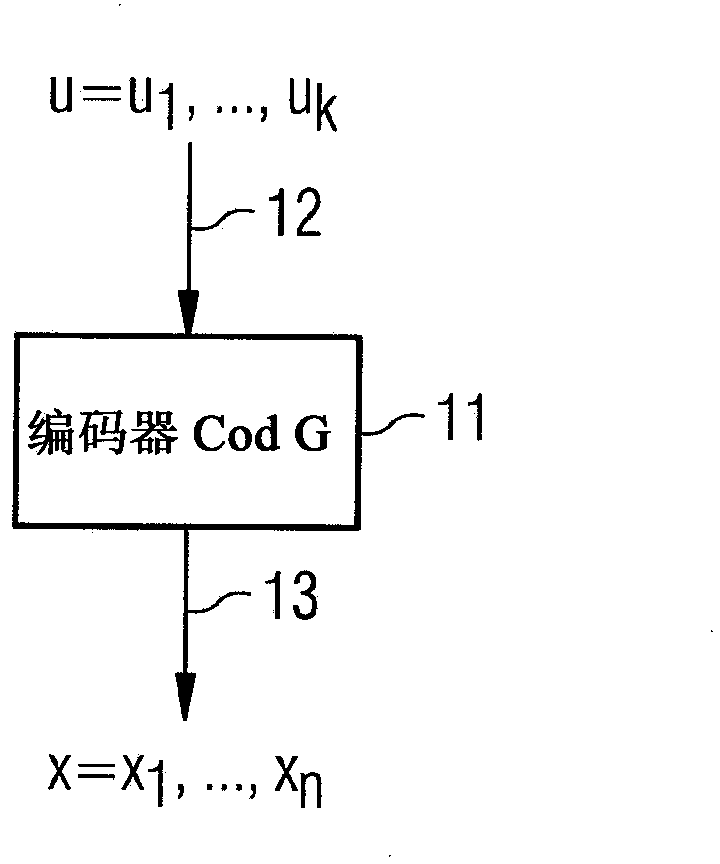

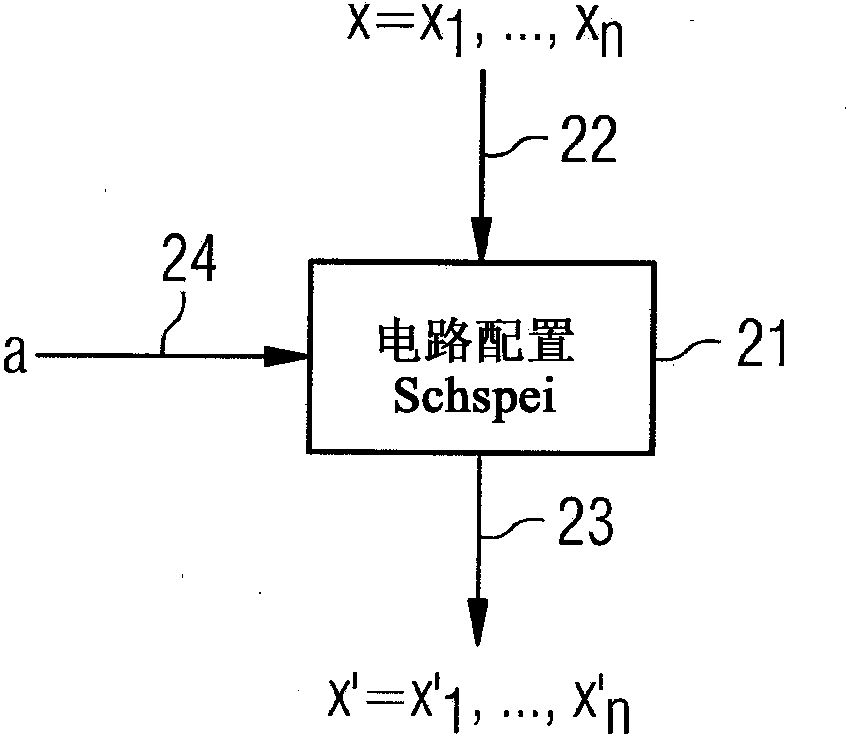

Systems and methods for embedding data by dimensional compression and expansion

ActiveUS20020172395A1User identity/authority verificationCharacter and pattern recognitionOriginal dataData file

The systems and methods of this invention watermark an original data file using dimensional compression and expansion. The original data file extends along a given dimension and has portions that extend along that given dimension. The information is embedded into the data file by selectively dimensionally compressing or expanding a size of each of some or all of the portions along the given dimension, which can be space or time. The portions of the data file are selectively dimensionally expanded or compressed according to a given encoding scheme. This encoding scheme can use the kind of modification, the relationships between the type of modification between adjacent portions, or the duration or degree of compression or expansion to store a portion of the embedded information. The portions of the embedded information can be individual bits of binary or trinary information, or can be a portion of analog information.

Owner:FUJIFILM BUSINESS INNOVATION CORP

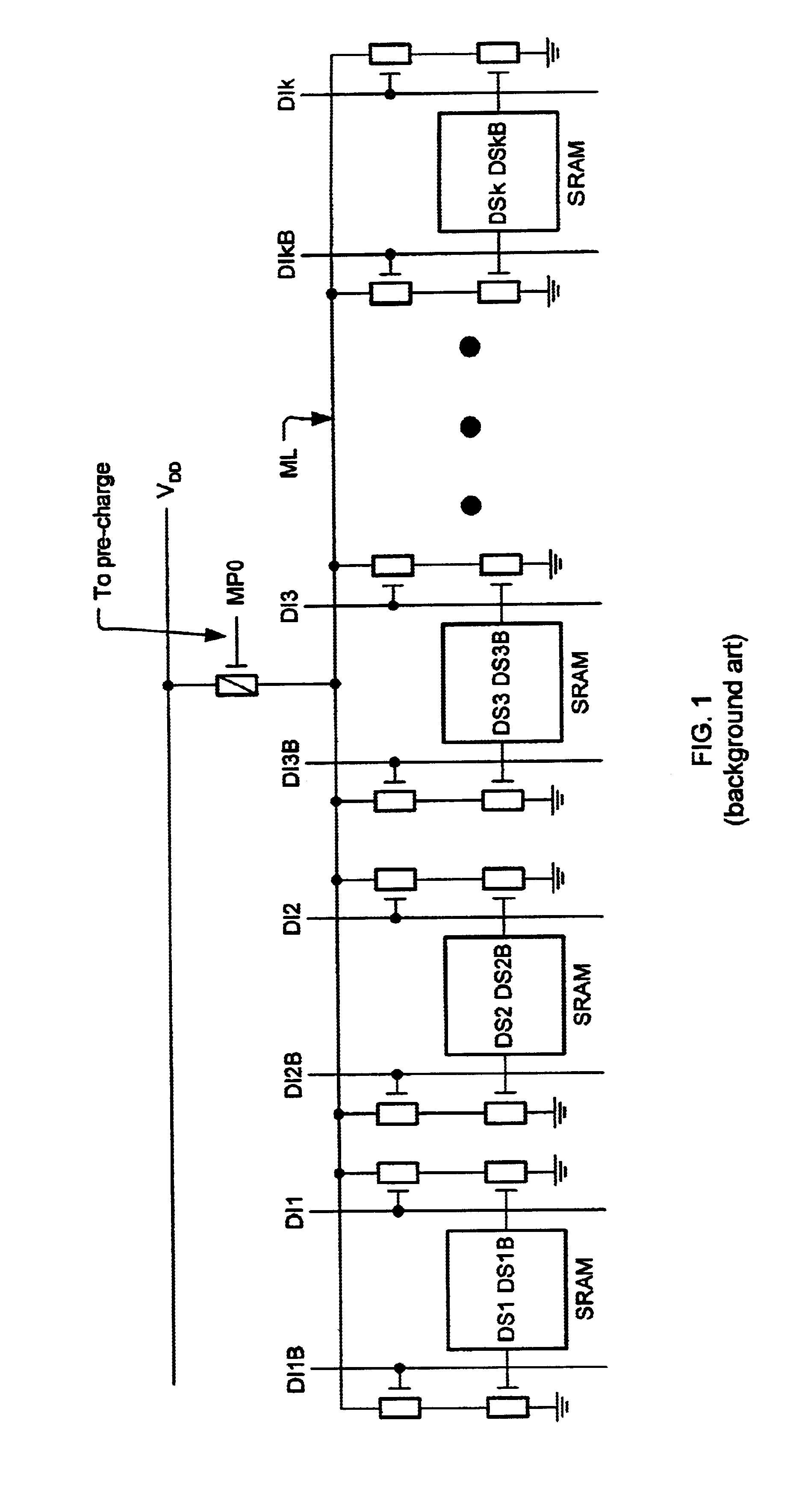

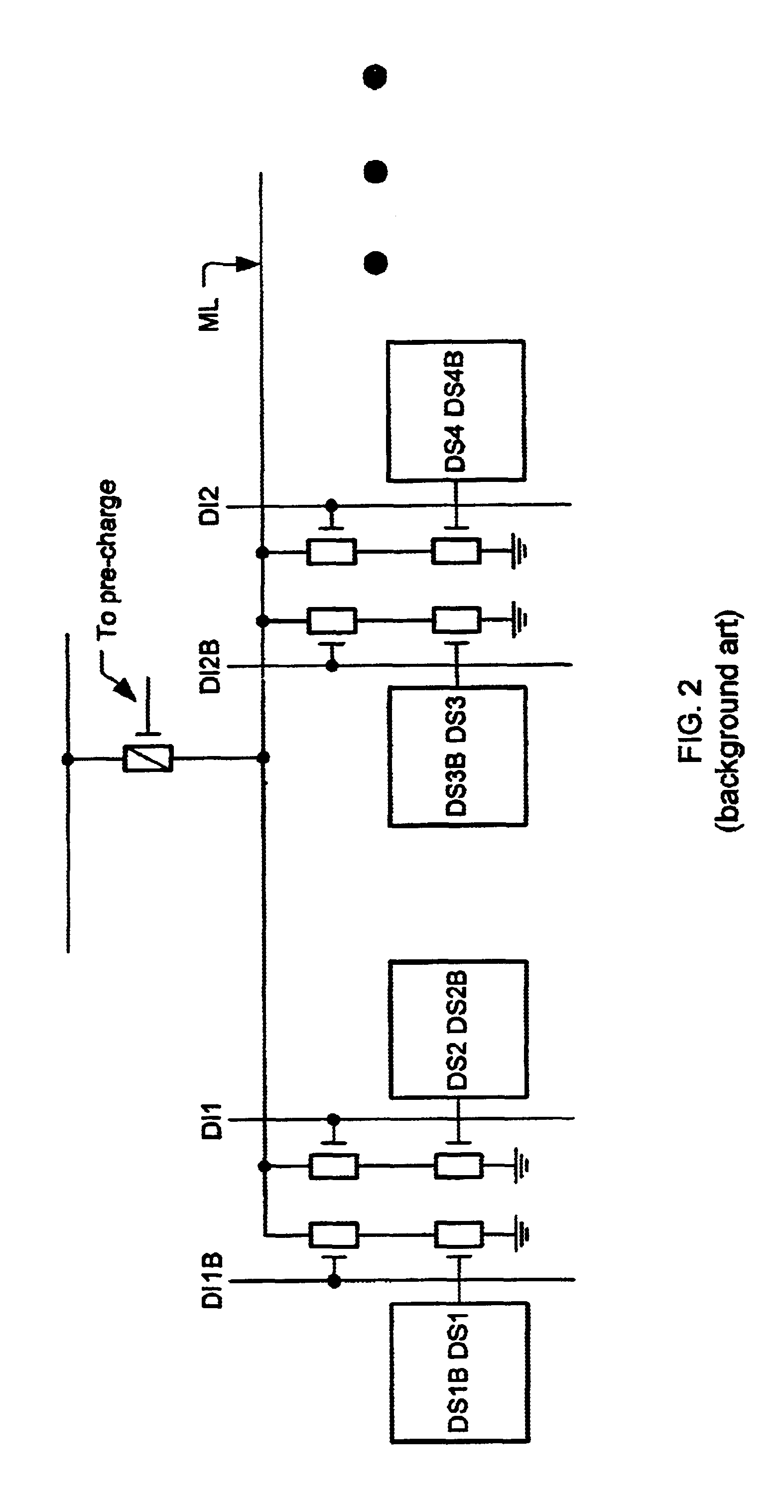

Dual match-line, twin-cell, binary-ternary CAM

Owner:CONVERSANT INTPROP MANAGEMENT INC

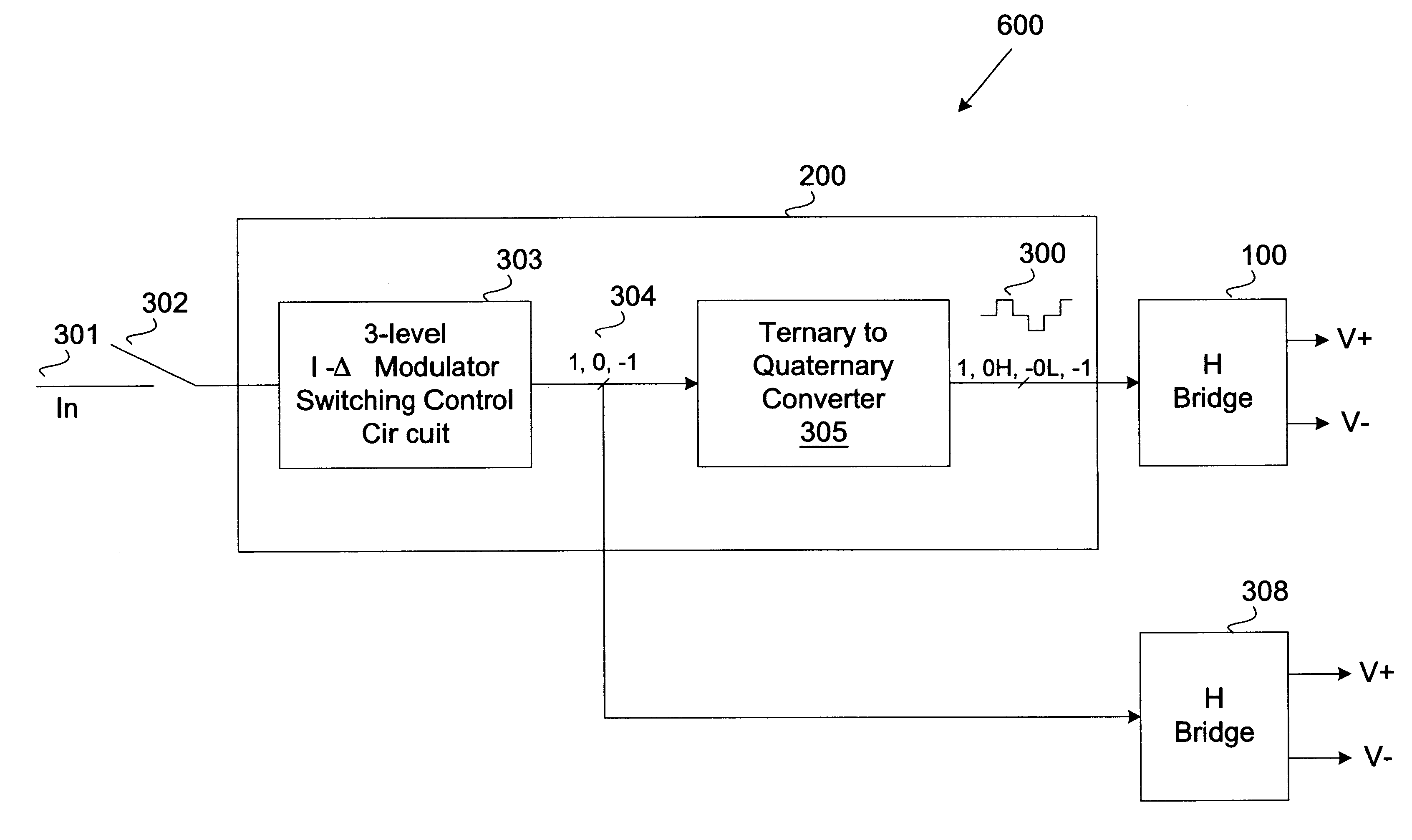

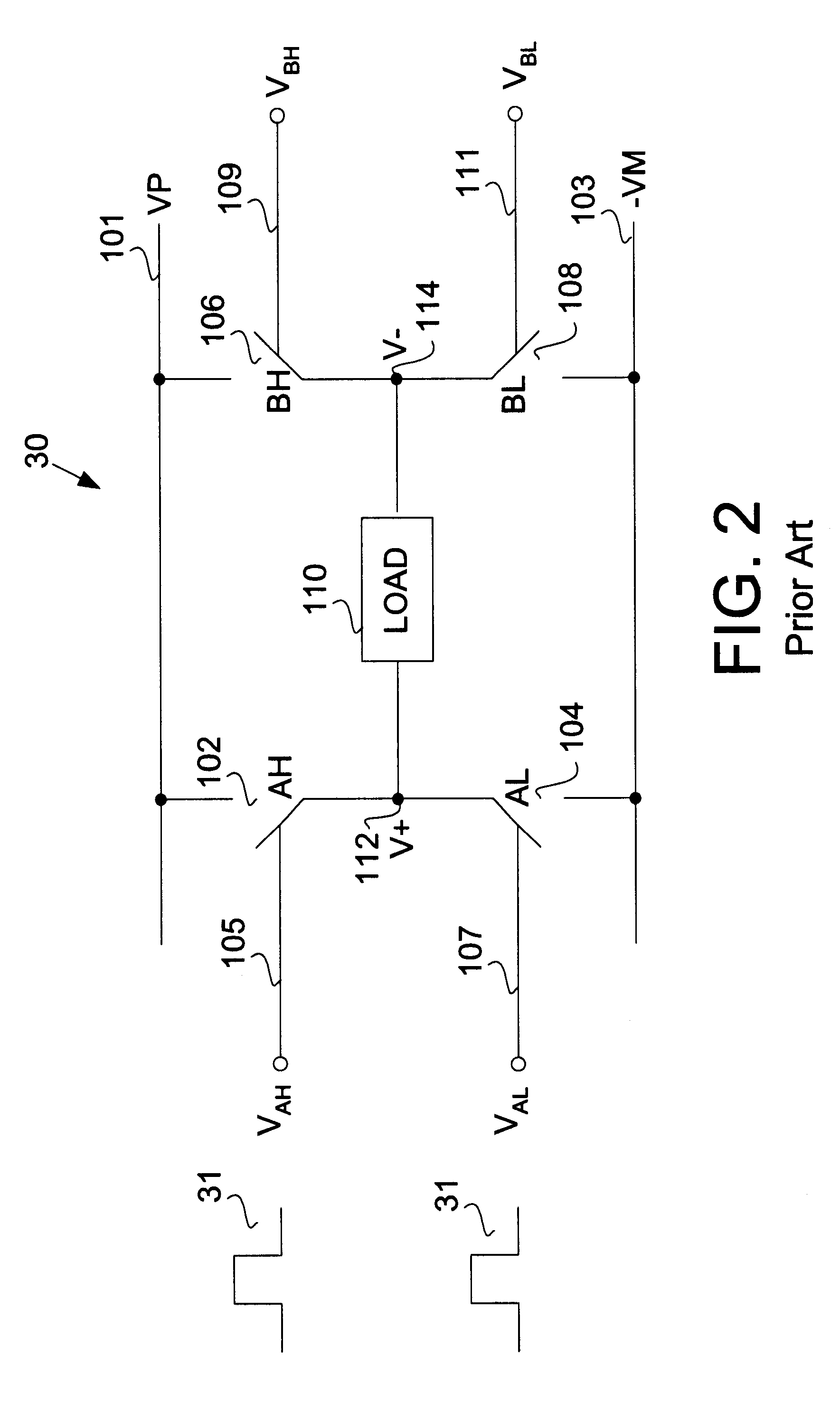

Switching amplifier incorporating return-to-zero quaternary power switch

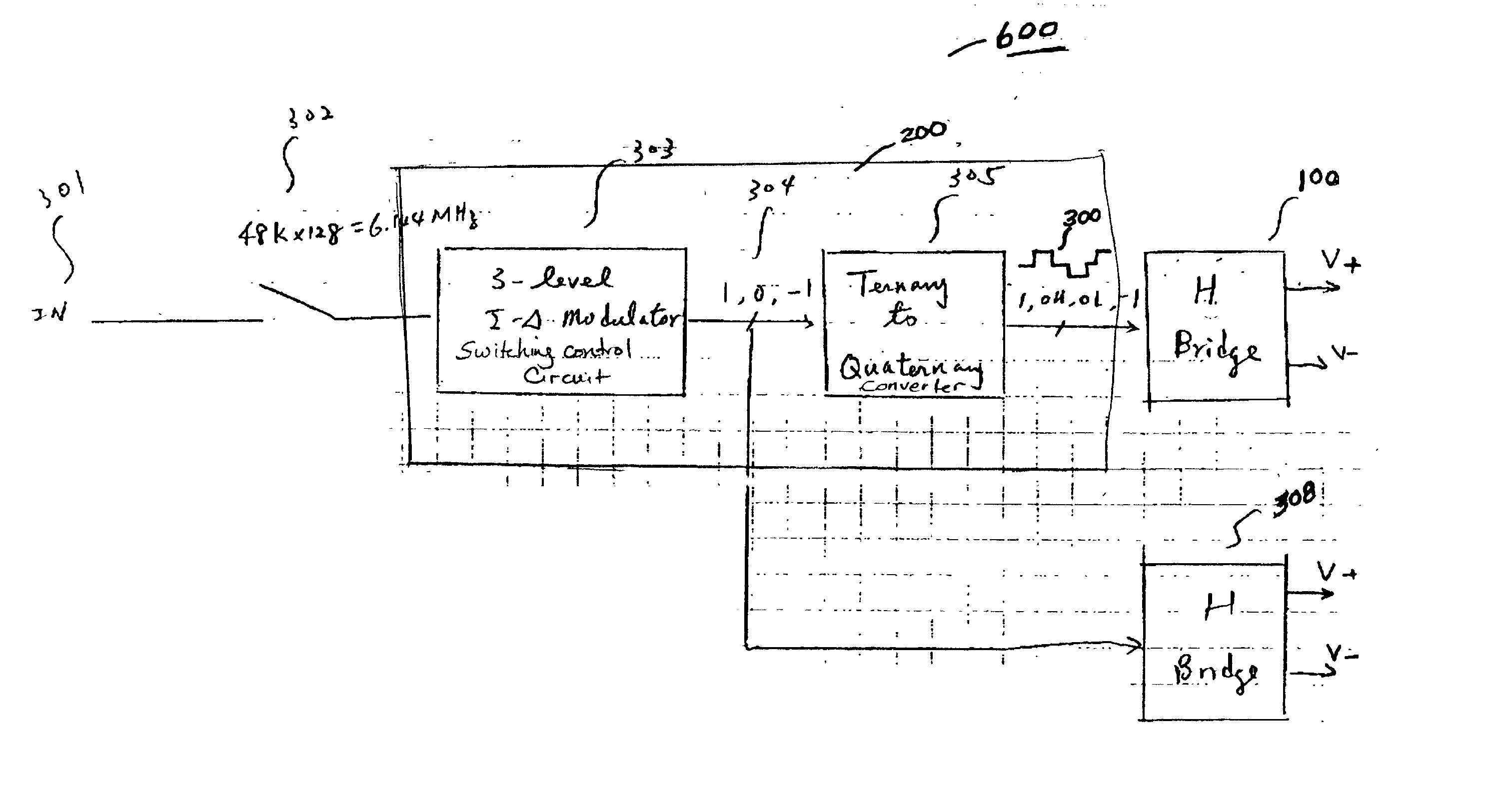

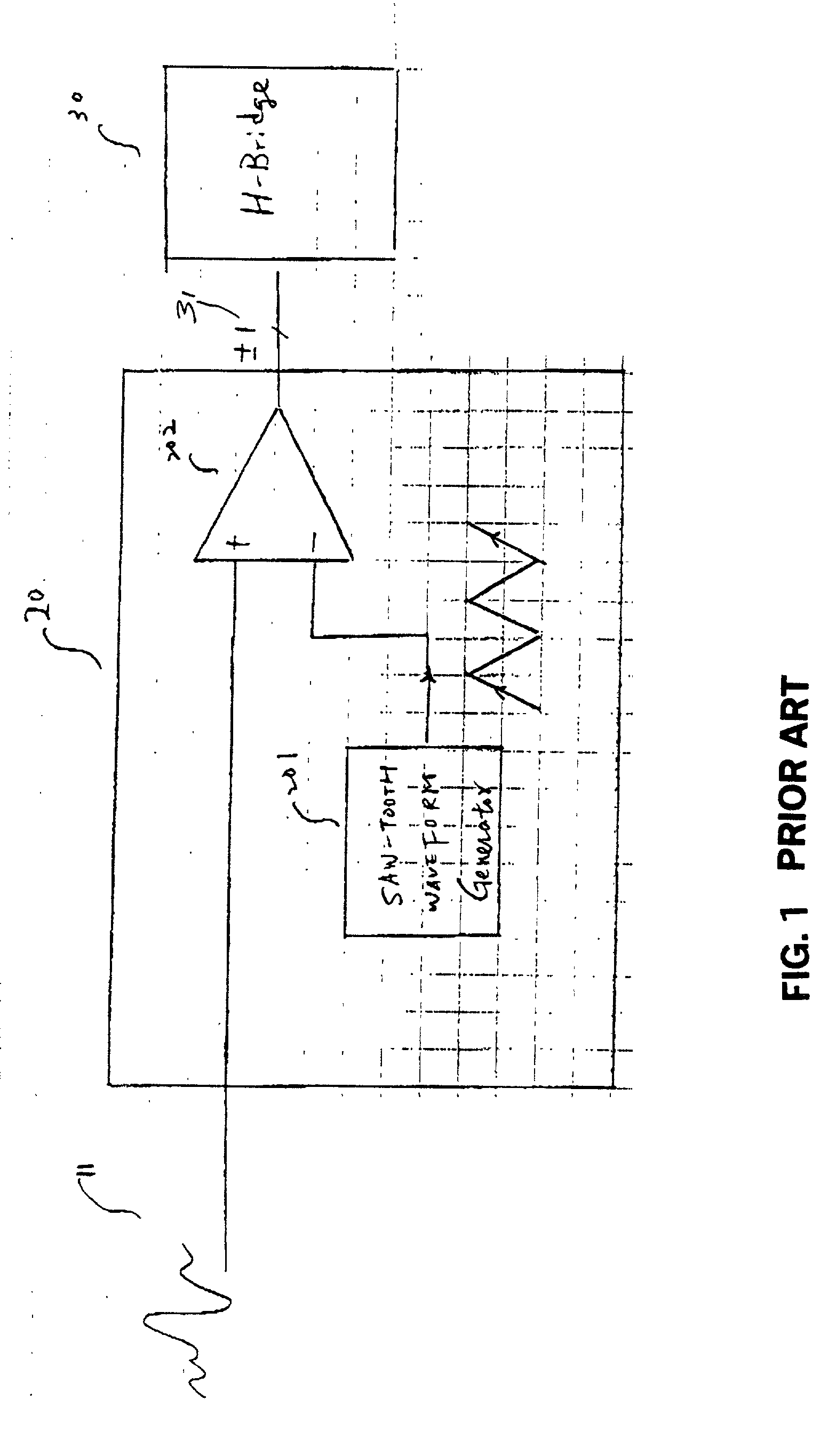

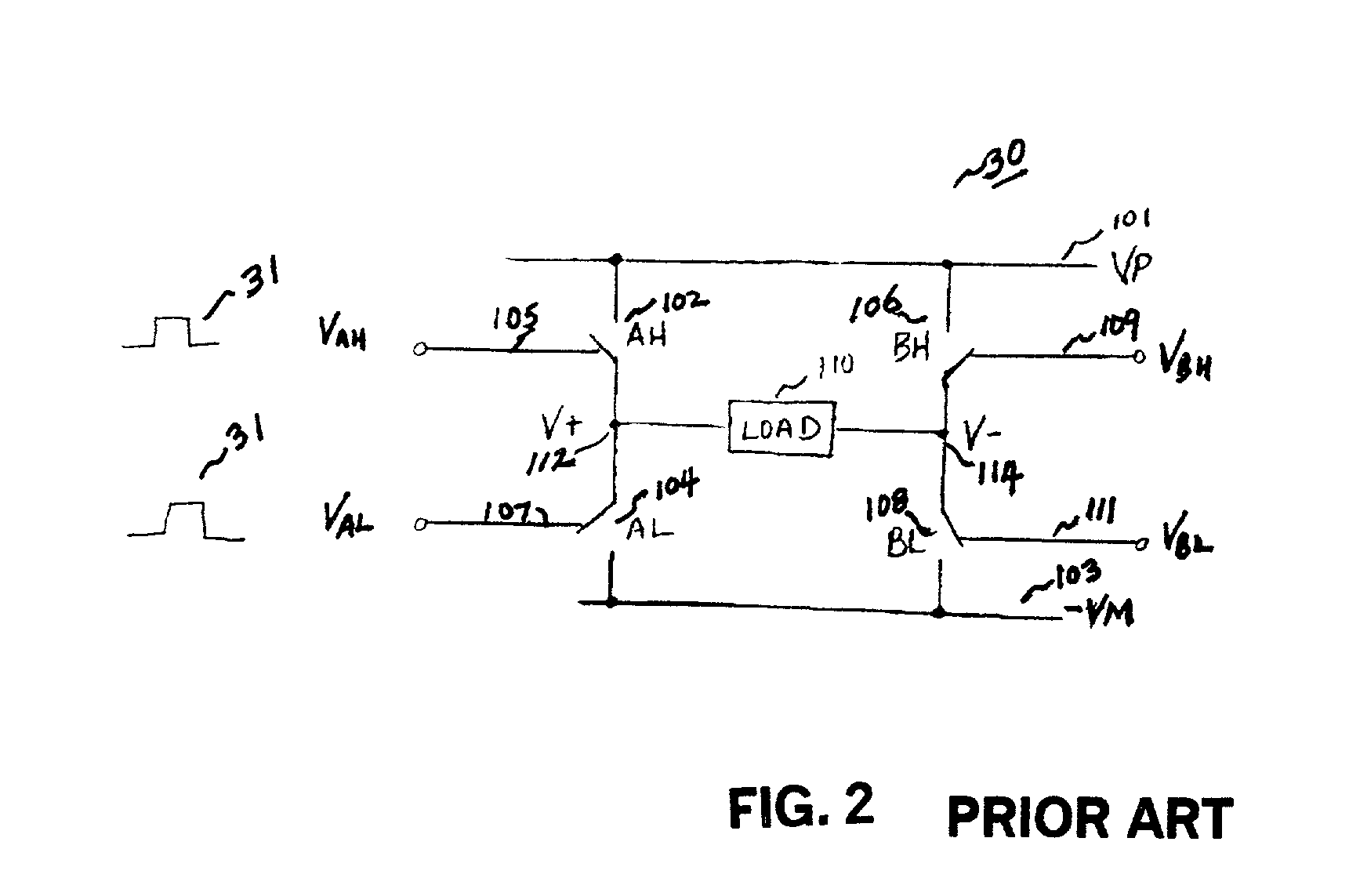

Invention resides in a switching amplifier having a quaternary input control signal that provides quaternary levels (1, 0H, -1, and 0L) which is coupled to an H-bridge amplifier to provide error cancellation in switching amplifier output signal. The quaternary control signal alternates from a zero state at a high level ("0H") to a zero state at a low level ("0L") between each non-zero state (+1 or -1). In a preferred embodiment, a three-level sigma-delta modulator is provided for greater operational efficiency for ease of detecting zero states and minimizing power. The three-level sigma-delta modulator receives and converts an amplifier input signal into a ternary output signal that is then coupled to a ternary-to-quaternary converter to generate the quaternary control signal to provide as input to the H-bridge.

Owner:RALPH CHANG JONG

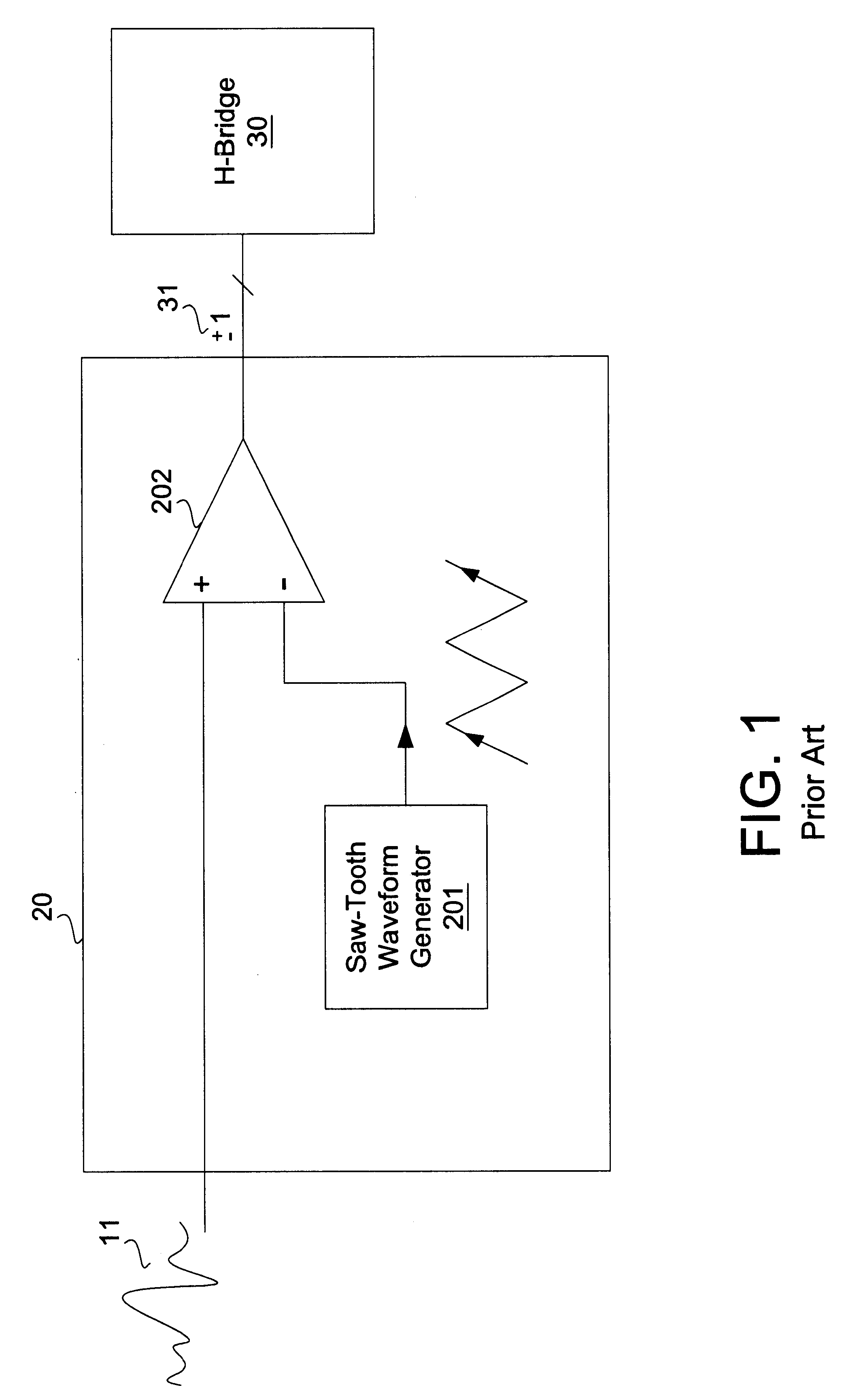

Switiching Amplifier Incorporating Return-to- Zero Quaternary Power Switch

InactiveUS20020075068A1Minimize error voltageMinimize harmonic distortionDc amplifiers with modulator-demodulatorThree levelAudio power amplifier

Invention resides in a switching amplifier having a quaternary input control signal that provides quaternary levels (1, 0H, -1, and 0L) which is coupled to an H-bridge amplifier to provide error cancellation in switching amplifier output signal. The quaternary control signal alternates from a zero state at a high level ("0H") to a zero state at a low level ("0L") between each non-zero state (+1 or -1). In a preferred embodiment, a three-level sigma-delta modulator is provided for greater operational efficiency for ease of detecting zero states and minimizing power. The three-level sigma-delta modulator receives and coverts an amplifier input signal into a ternary output signal that is then coupled to a ternary-to-quaternary converter to generate the quaternary control signal to provide as input to the H-bridge.

Owner:RALPH CHANG JONG

Generating searchable data entries and applications therefore

InactiveUS6484170B2Data processing applicationsDigital data information retrievalApplication softwareComputer science

Owner:OL SECURITY LIABILITY CO +1

Image sensor driving apparatus

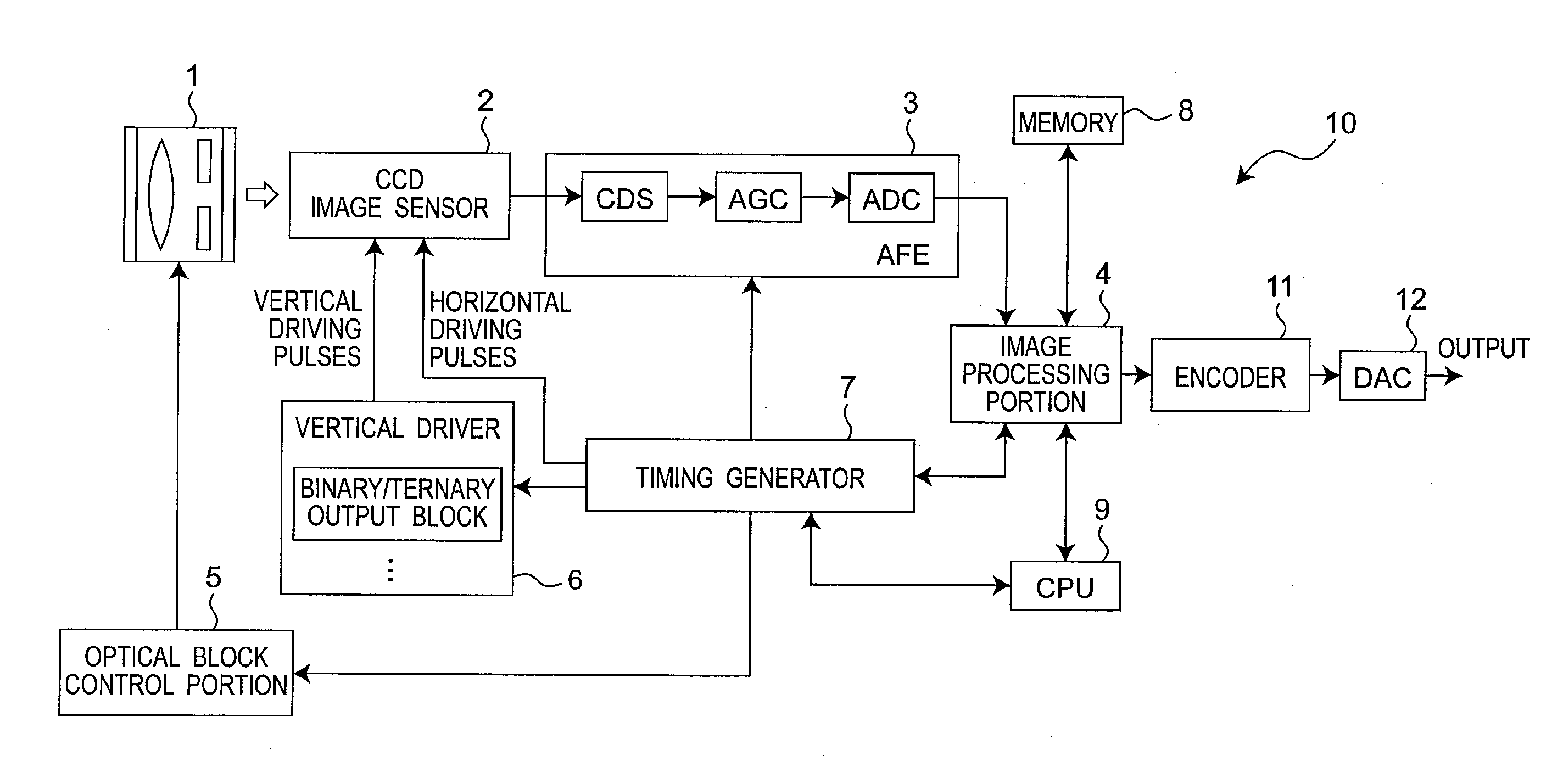

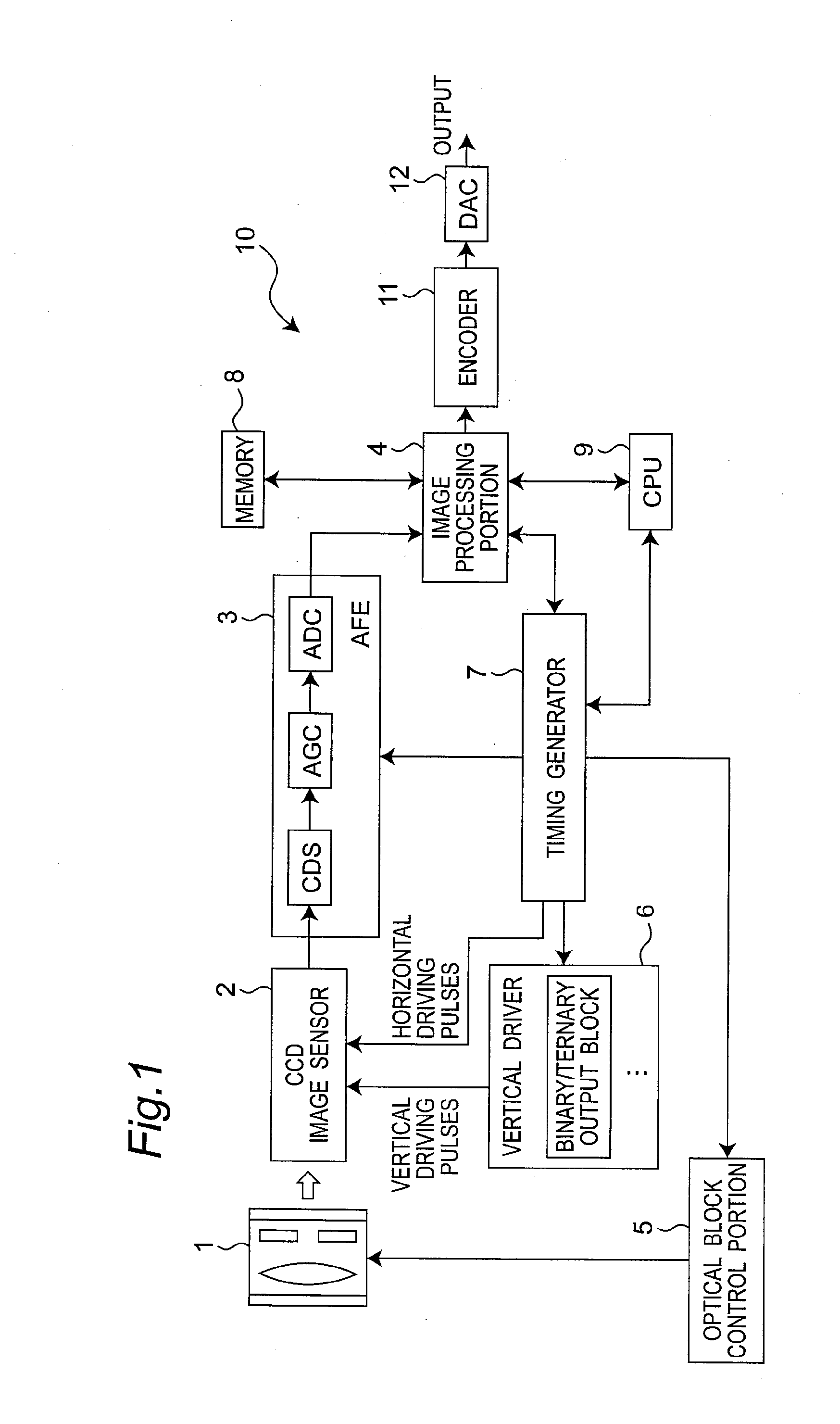

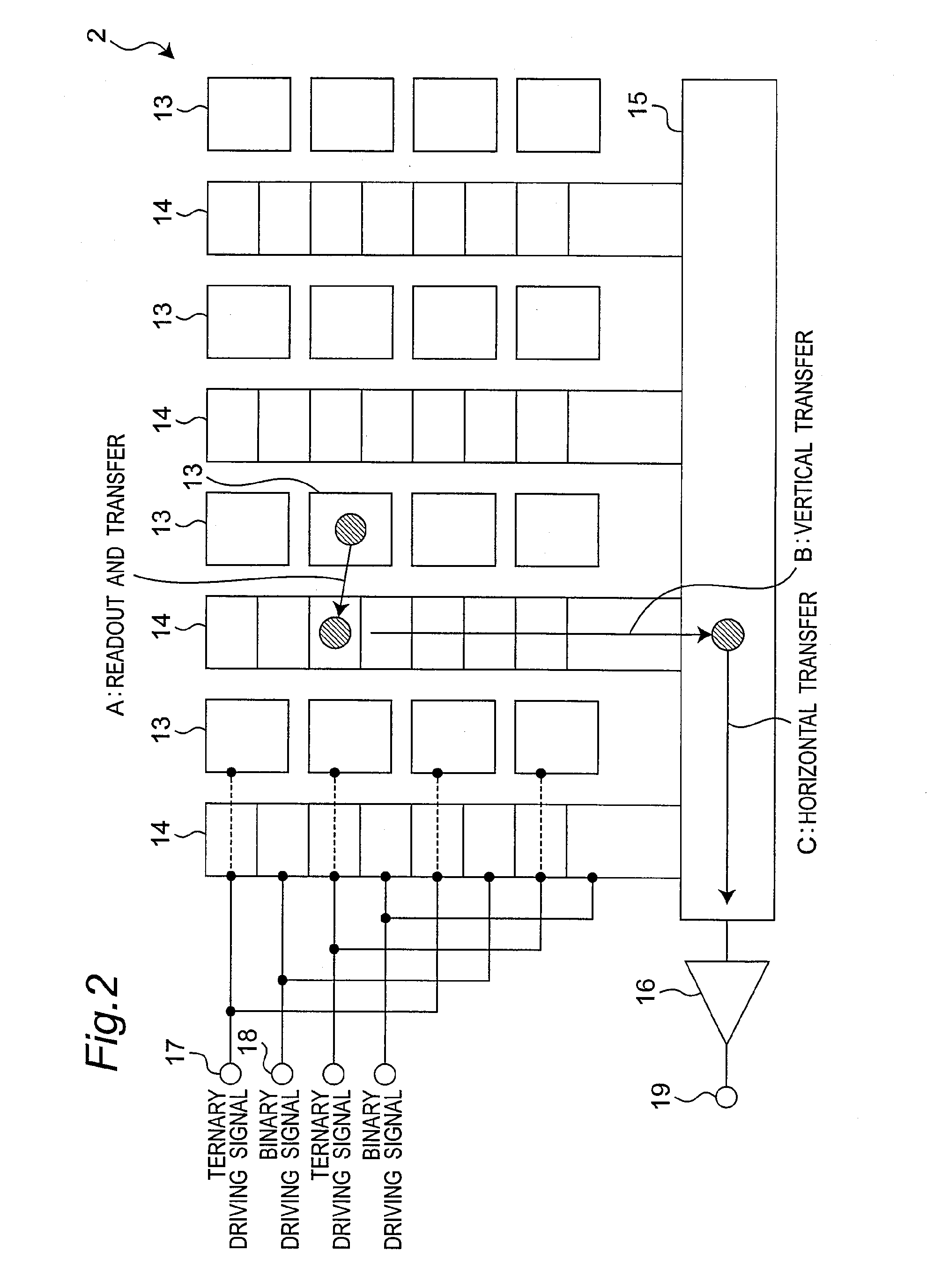

InactiveUS20100177230A1Reduce in quantityLow costTelevision system detailsTelevision system scanning detailsTiming generatorControl signal

An image sensor driving apparatus is provided with a plurality of output blocks having the functions of both a binary output block and a ternary output block and, therefore, is adaptable to image sensors with various types of specifications. The image sensor is provided with a plurality of dual-purpose binary / ternary output blocks having the functions of both a binary output block and a ternary output block and is configured to change over between binary operations and ternary operations, according to driving / controlling signals from a timing generator or selection signals from the outside of the apparatus.

Owner:PANASONIC CORP

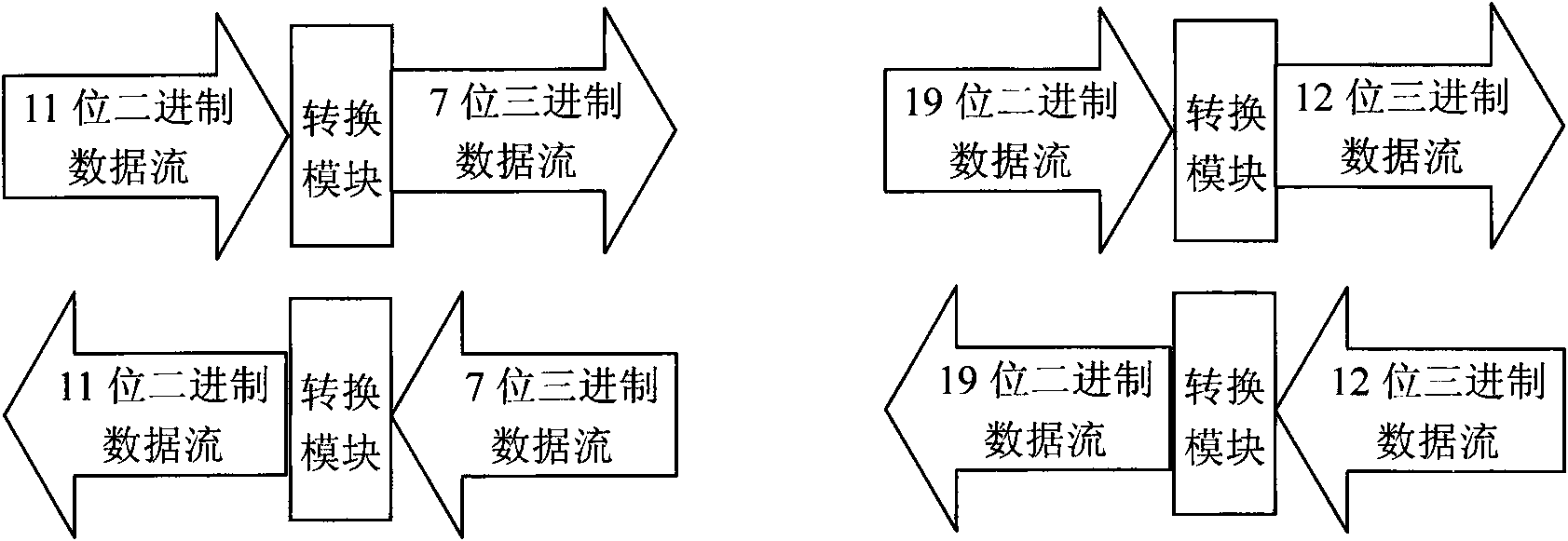

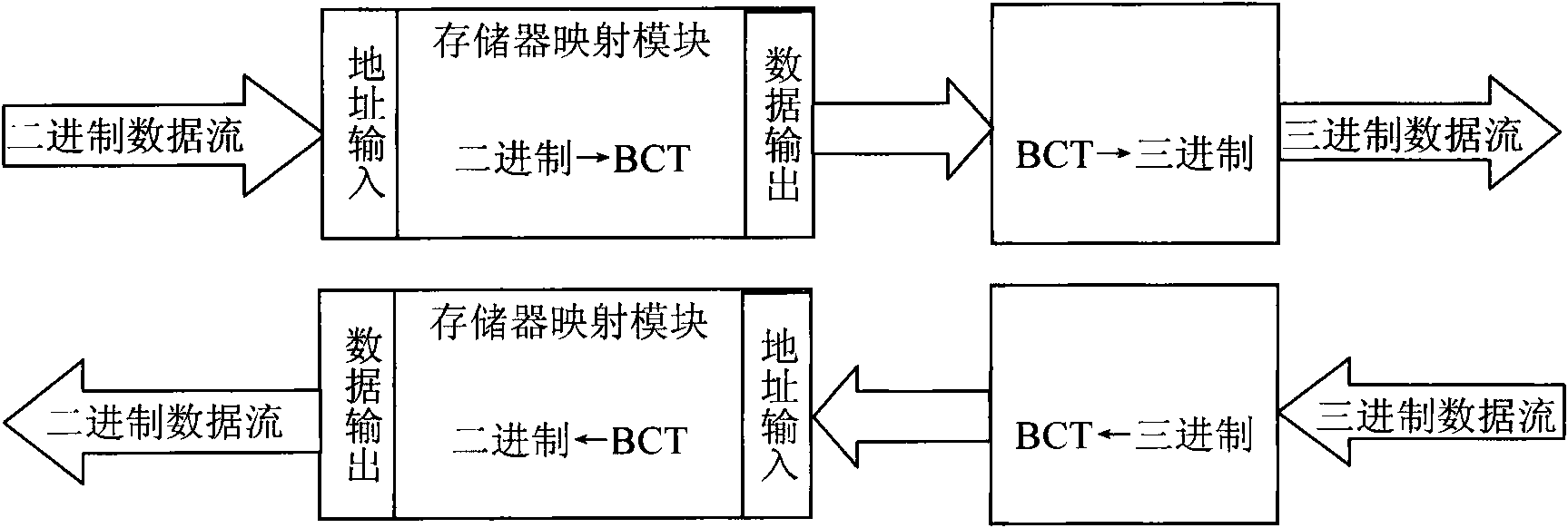

High-efficiency wired communication methods

The invention relates to two types of wired communication methods and systems for occasions with different requirements. The two systems both comprise two parts of physical conversion modules, one part is used for converting binary data flow into ternary data flow for transmitting, and the other part is used for reducing the received ternary data flow into the binary data flow. The two systems carry out the conversion between the binary data flow and the ternary data flow by adopting two conversion formats of 11b7t and 19b12t respectively, respectively save 36.4% and 36.8% of transmission time under equivalent clock rate, and meet the requirements of the occasions with different application requirements on hardware scale. The conversion operations can be carried out through the steps with binary code, 21BCT (Binary Coded Ternary) code, and ternary code. In the conversion step, the conversion link of binary code and the 21BCT code can be implemented through the mode of storage address mapping, , therefore, the method ensures that the hardware circuit is simplified.

Owner:NANJING UNARY INFORMATION TECH

Adaptive Ternary A/D Converter for Use in an Ultra-Wideband Communication System

ActiveUS20110227766A1Preventing numberElectric signal transmission systemsSynchronisation arrangementBroadbandUltra wideband communication systems

In an ultra-wideband communication system, a 1-trit ternary analog-to-digital converter (“ADC”) having dynamic threshold adaption and providing an output in ternary form [+1, 0, −1]. The ternary ADC includes a pair of 1-bit binary ADCs, one being configured in a non-inverting form, and one being configured in an inverting form. Each binary ADC includes an feedback network mechanism, thereby allowing for simultaneous and independent adaptation of the pair of thresholds, compensating for the effects of any DC offset that may be present. The use of a trit-based ternary encoding scheme improves system entropy.

Owner:DECAWAVE

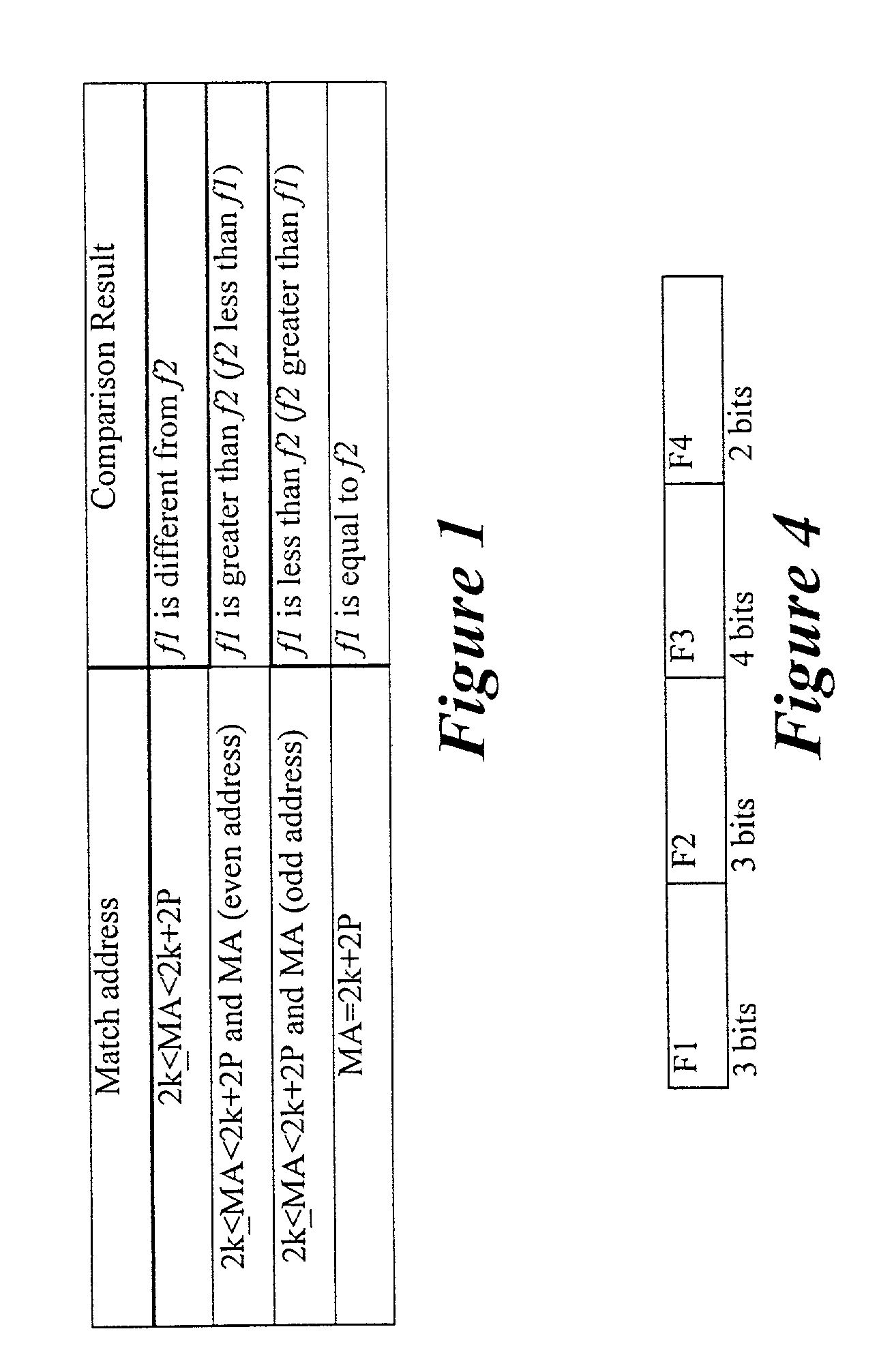

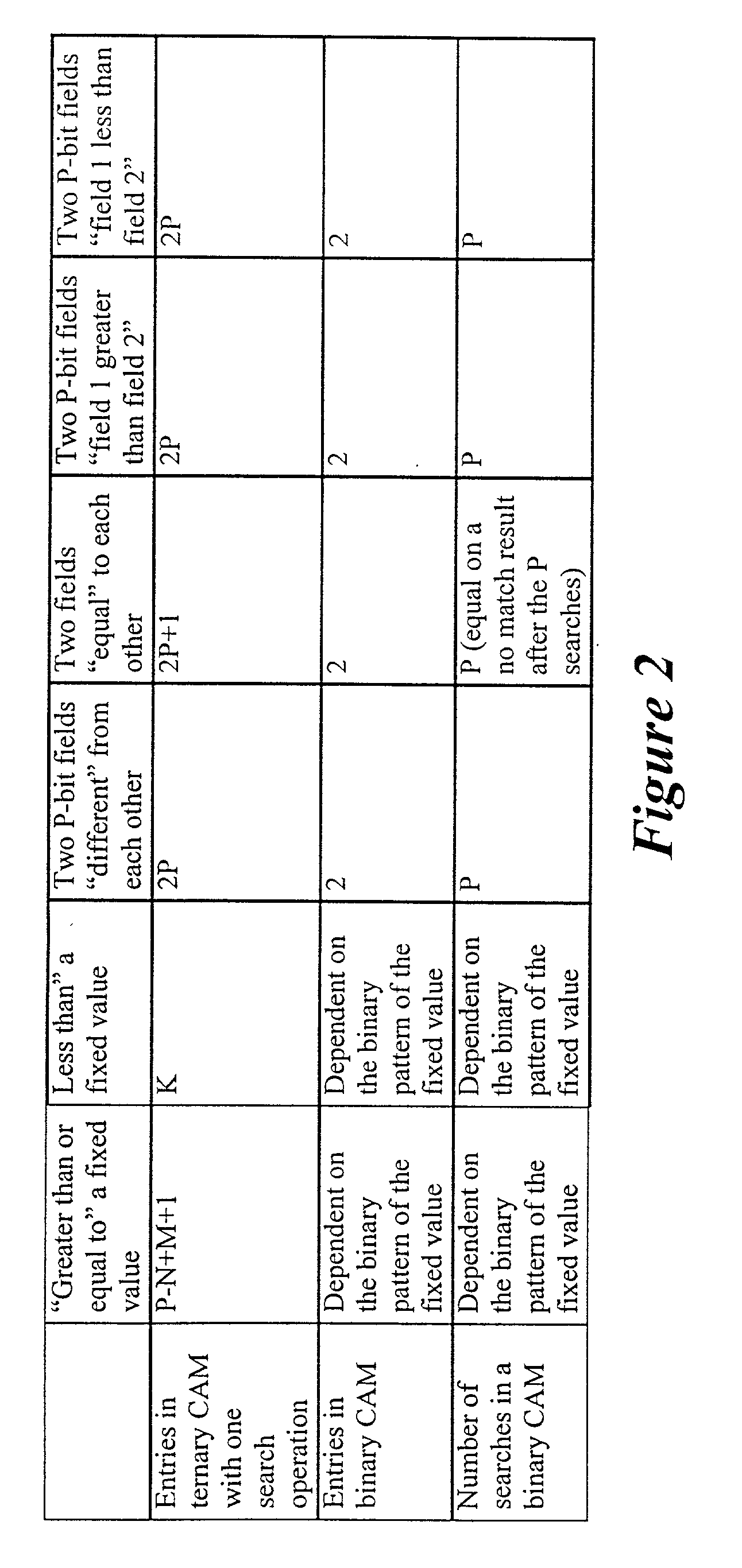

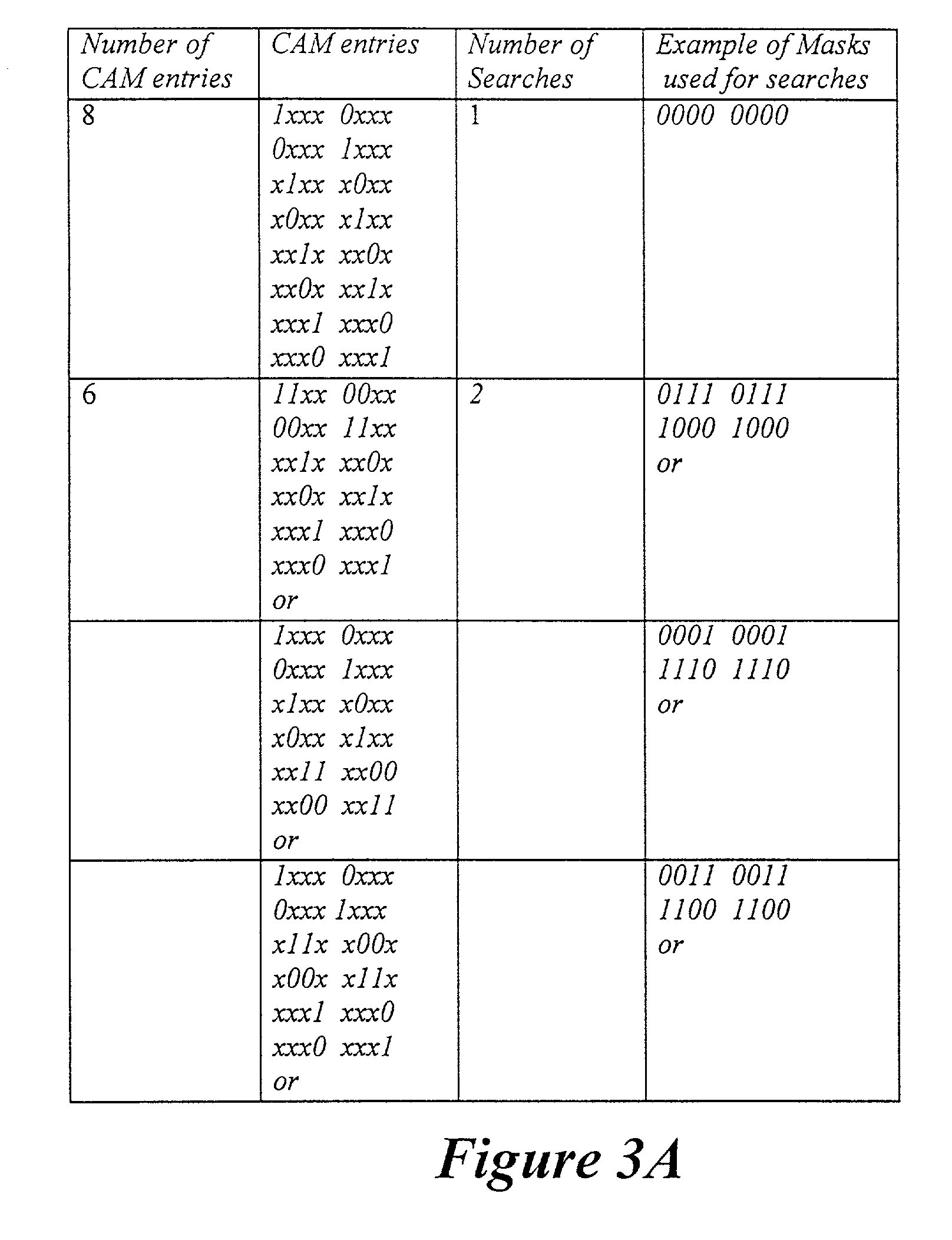

Generating searchable data entries and applications therefore

InactiveUS20010002476A1Data processing applicationsDigital data information retrievalComputer scienceContent-addressable storage

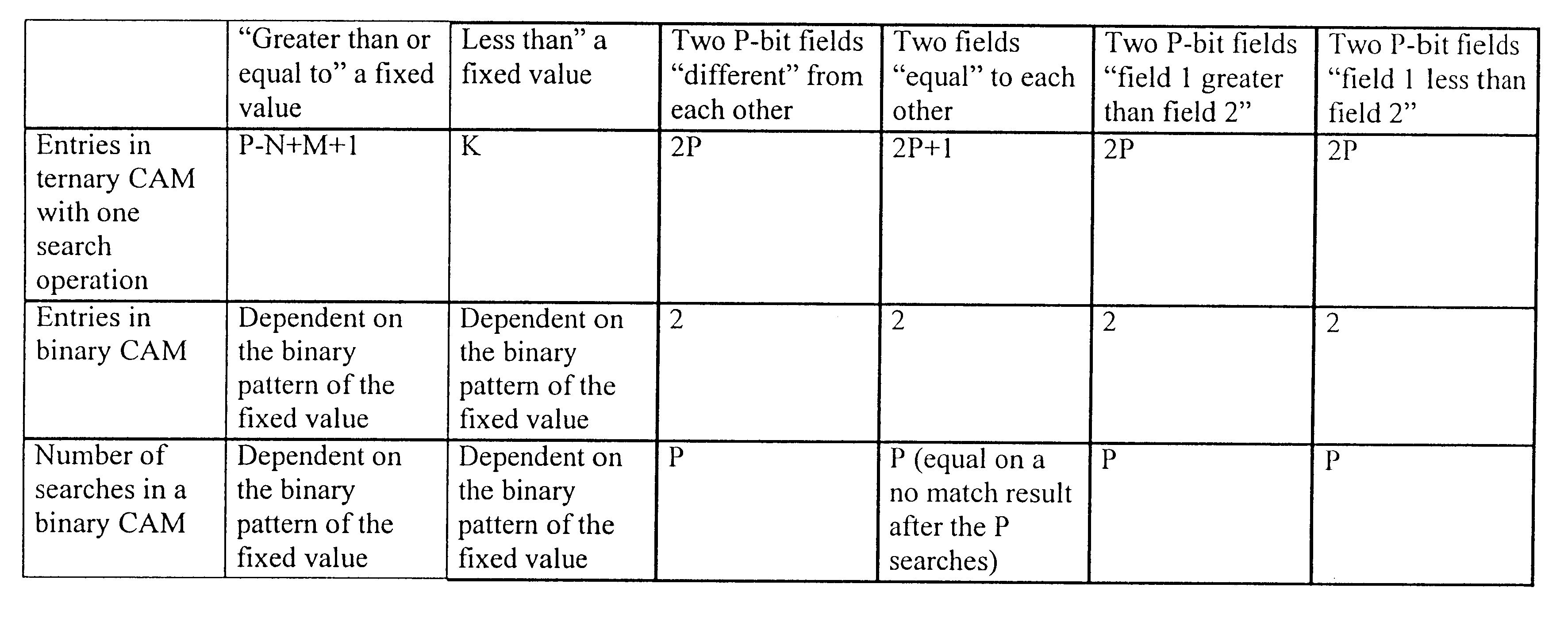

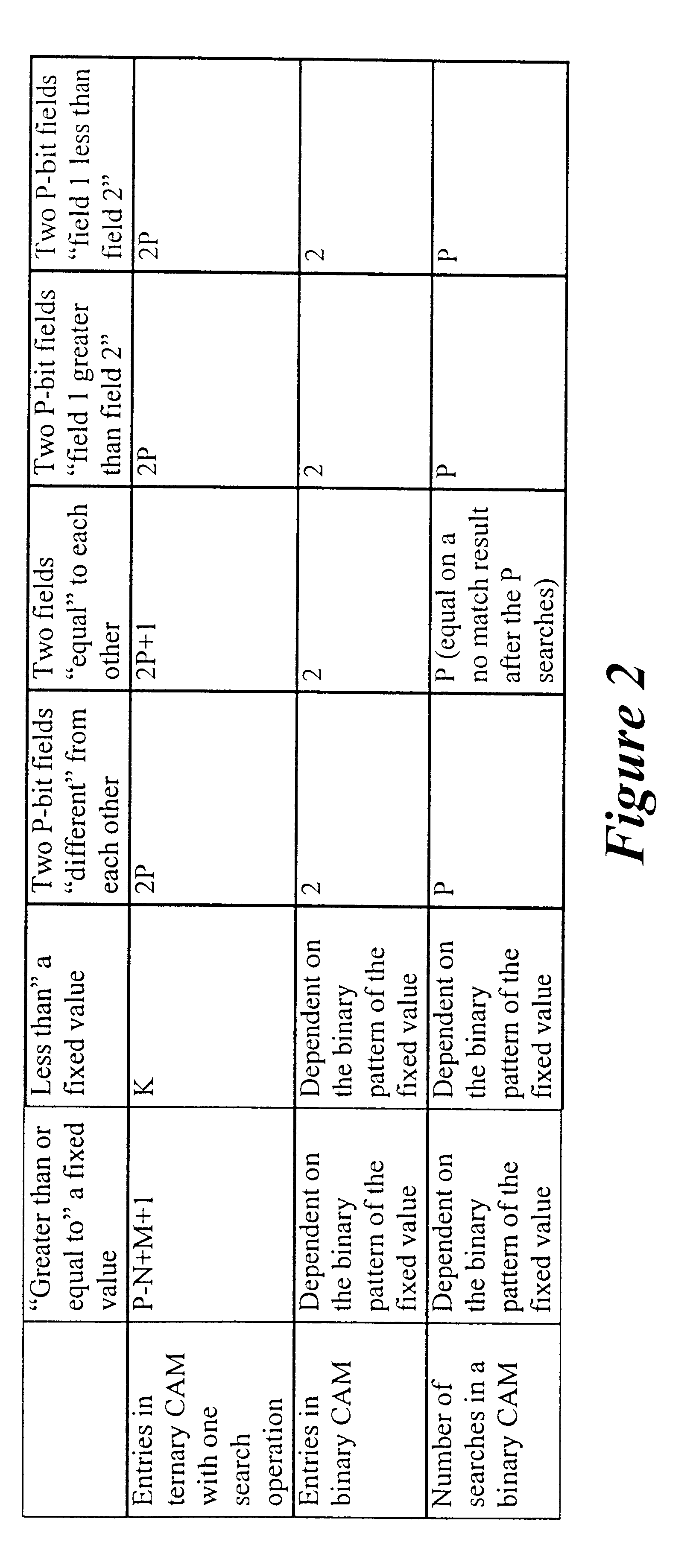

New techniques for generating entries in a content addressable memory (CAM) capable of comparison operations such as "greater than" and "less than" decisions are described. The techniques can be used with binary or ternary CAMs. The number of CAM entries needed to implement such decisions is drastically reduced for both binary and ternary CAMs. In the case of binary CAMs, one or multiple searches are needed to perform the comparisons, while in the case of ternary CAMs a tradeoff between the number of CAM entries and the number of searches can be found. As an example, a method of classifying data networking packets is implemented using the new techniques. A packet classifier based on subfields of a packet header is also described.

Owner:OL SECURITY LIABILITY CO +1

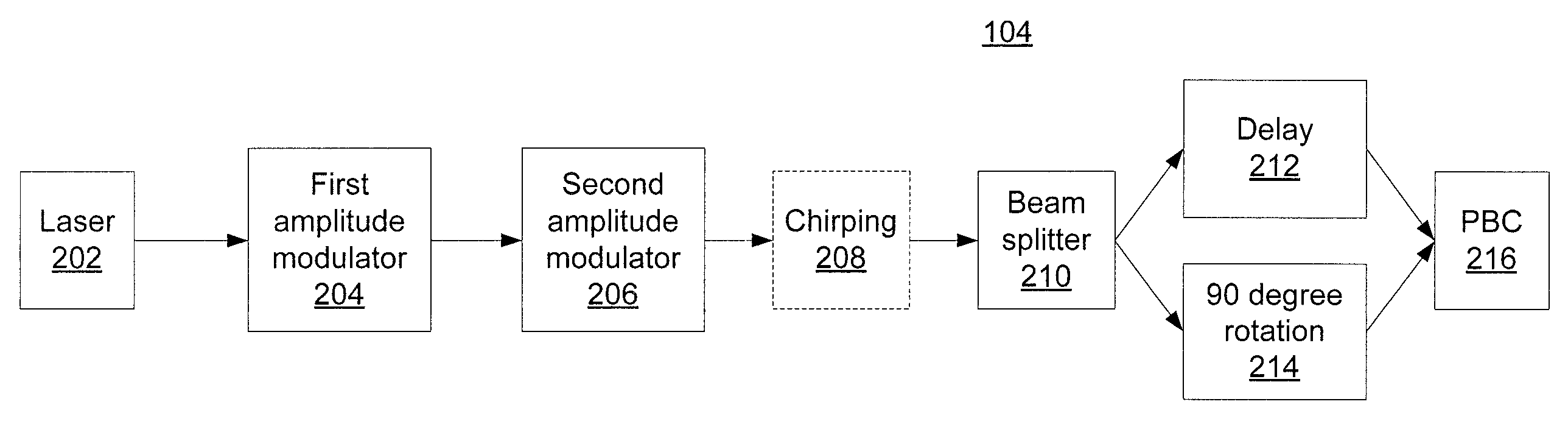

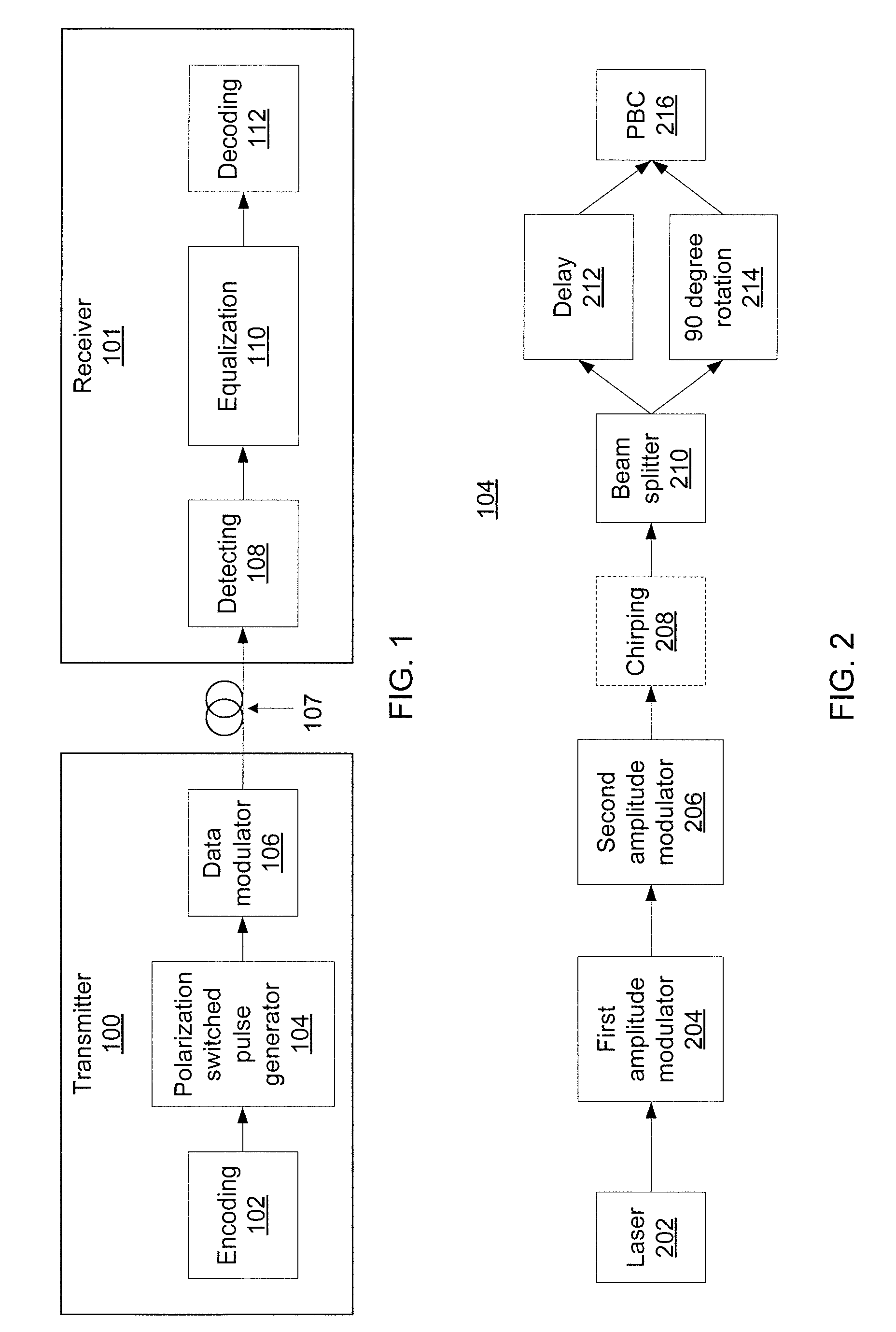

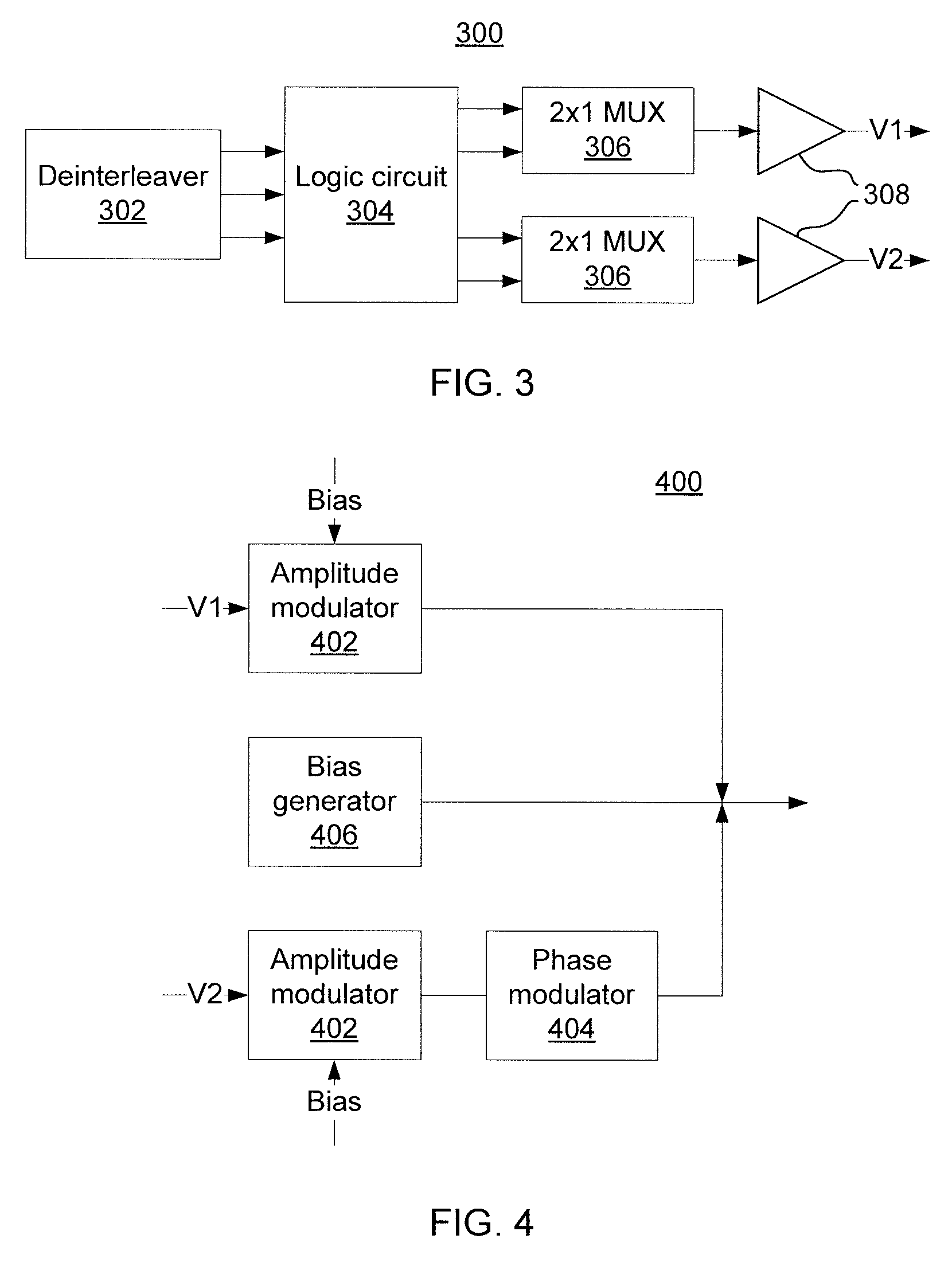

Polarization-switched differential ternary phase-shift keying

ActiveUS9130679B1Phase-modulated carrier systemsElectromagnetic transmissionDifferential phaseCarrier signal

Methods and systems for transmission and reception of ternary phase-shift keyed data that include mapping triplets of binary bits to pairs of ternary symbols, such that three bits of data are encoded across two symbols having three-point constellations; modulating the pairs of ternary symbols onto a carrier; and transmitting the modulated carrier across a transmission medium.

Owner:NEC CORP

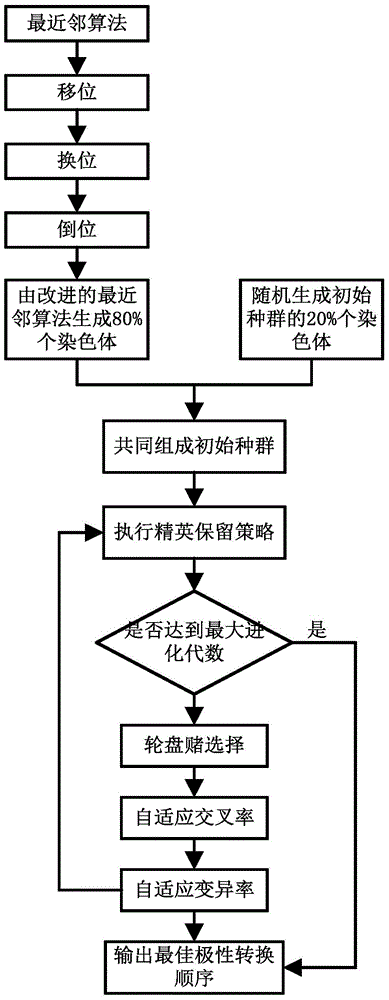

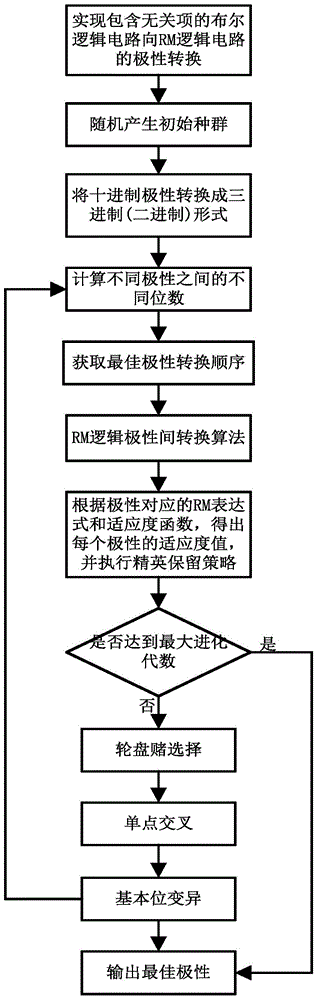

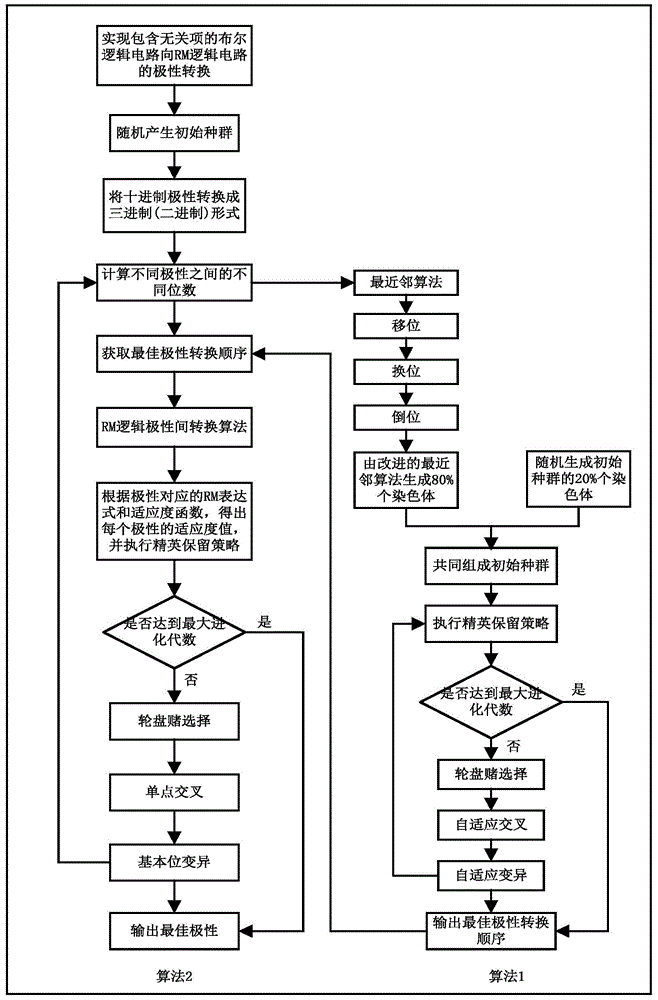

Power consumption optimizing method for RM (Reed-Muller) logical circuit comprising irrelevant items

ActiveCN104881549AFast convergenceNarrow down the search spaceSpecial data processing applicationsSelf adaptiveComputer science

The invention relates to a power consumption optimizing method for an RM (Reed-Muller) logical circuit comprising irrelevant items. The method comprises steps as follows: 1, polarity conversion from irrelevant-item-containing Boolean logic to RM logic is realized; 2, initial population is generated randomly; 3, conversion of decimal polarity to a binary system or a ternary system is completed; 4, different digits among different polarities in a polar set of the population are calculated; 5, the best polarity conversion sequence in each generation of to-be-evaluated polar set is calculated with an improved self-adaption genetic algorithm; 6, polarity conversion is performed on the current polar set according to the sequence obtained in the step 5; 7, the fitness value of each polarity is calculated according to an RM expression and a fitness function of the corresponding polarity, and an elitism preservation strategy is executed; 8, if current evolutionary algebra is smaller than the largest iteration times, steps 9 and 10 are executed, and otherwise, the best polarity is output; 9, selection, intercrossing and mutation operation are executed; 10, operations from the step 4 to the step 7 are circularly executed. The polarity searching efficiency is improved, and the convergence and the robustness of the genetic algorithm are enhanced.

Owner:BEIHANG UNIV

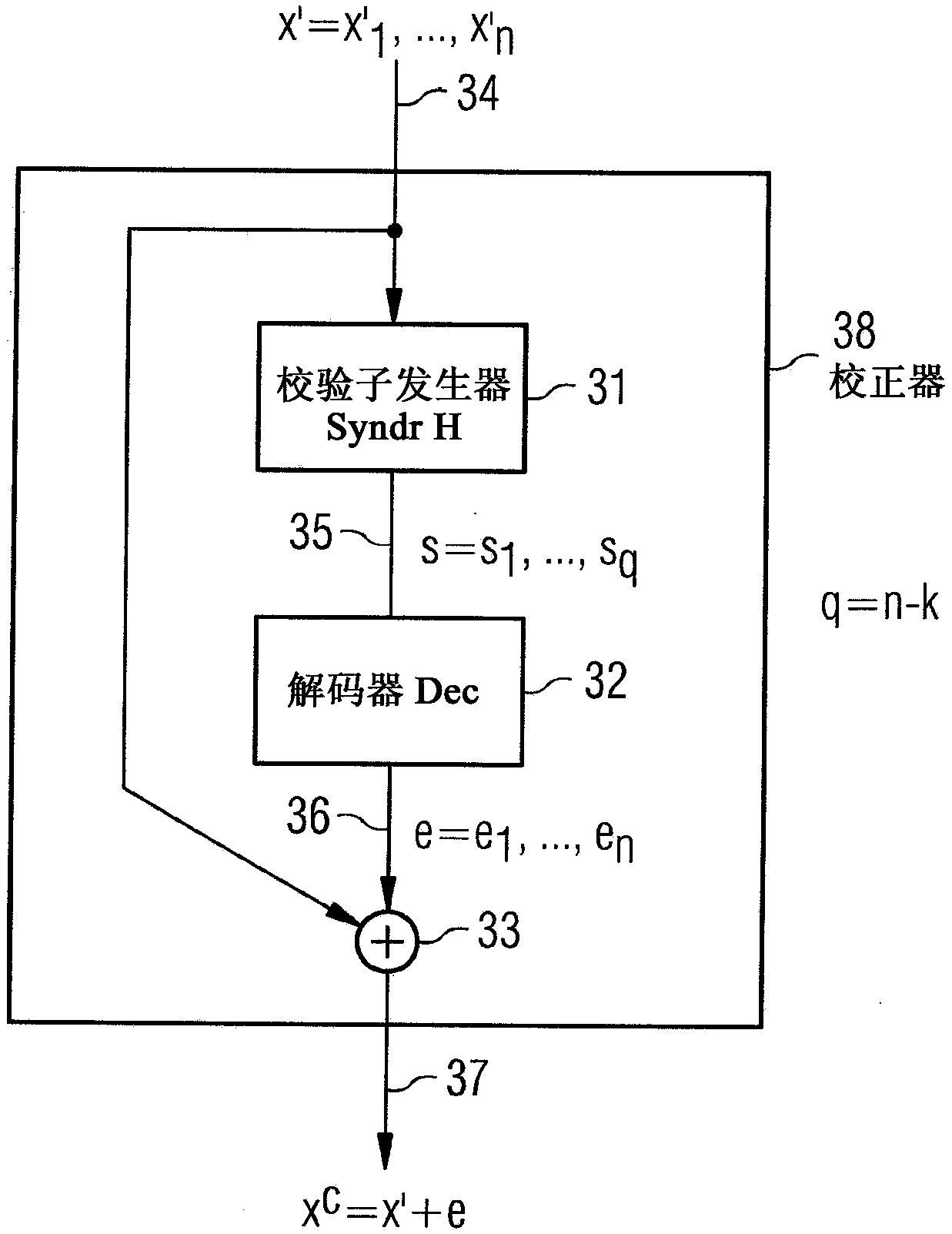

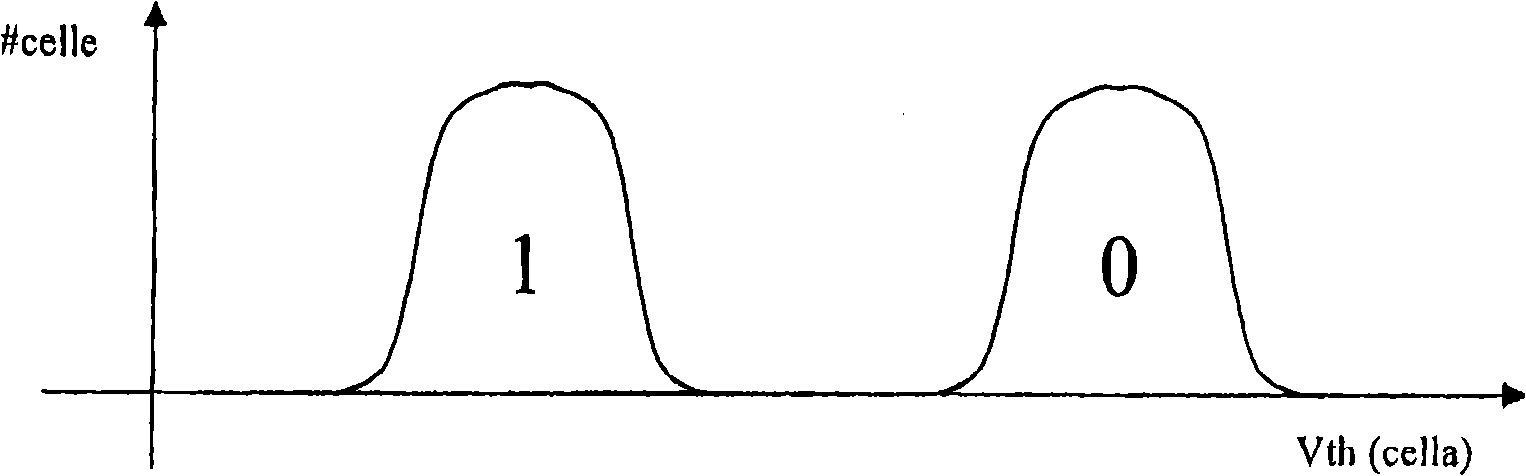

Method and device for correction of ternary stored binary data

ActiveCN103390431AError detection/correctionError correction/detection using linear codesComputer hardwareTernary numeral system

Owner:INFINEON TECH AG

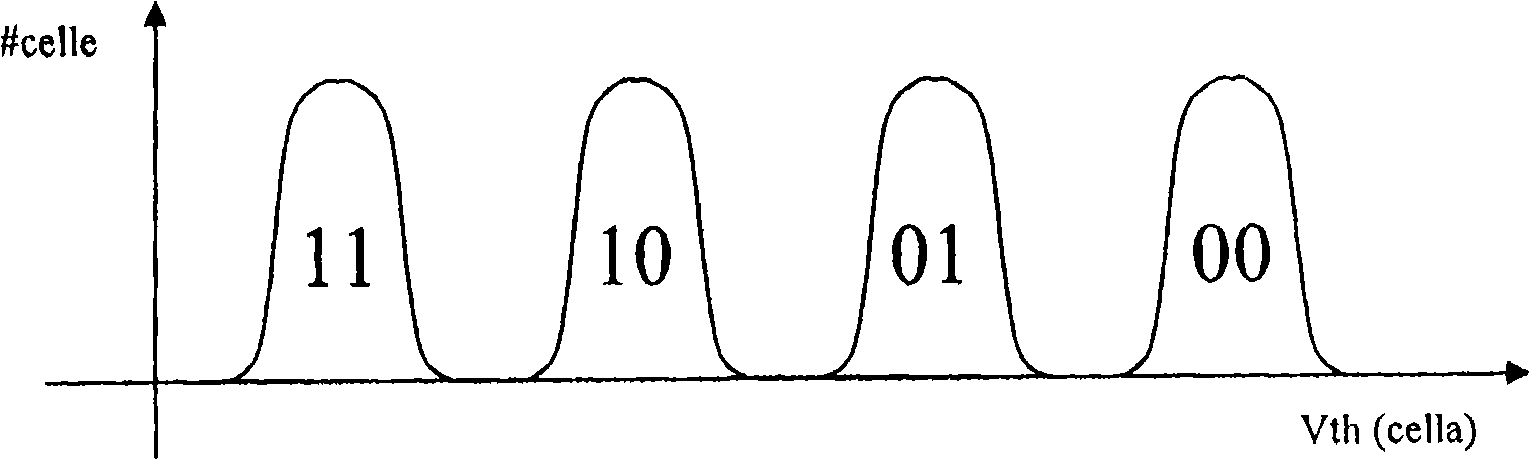

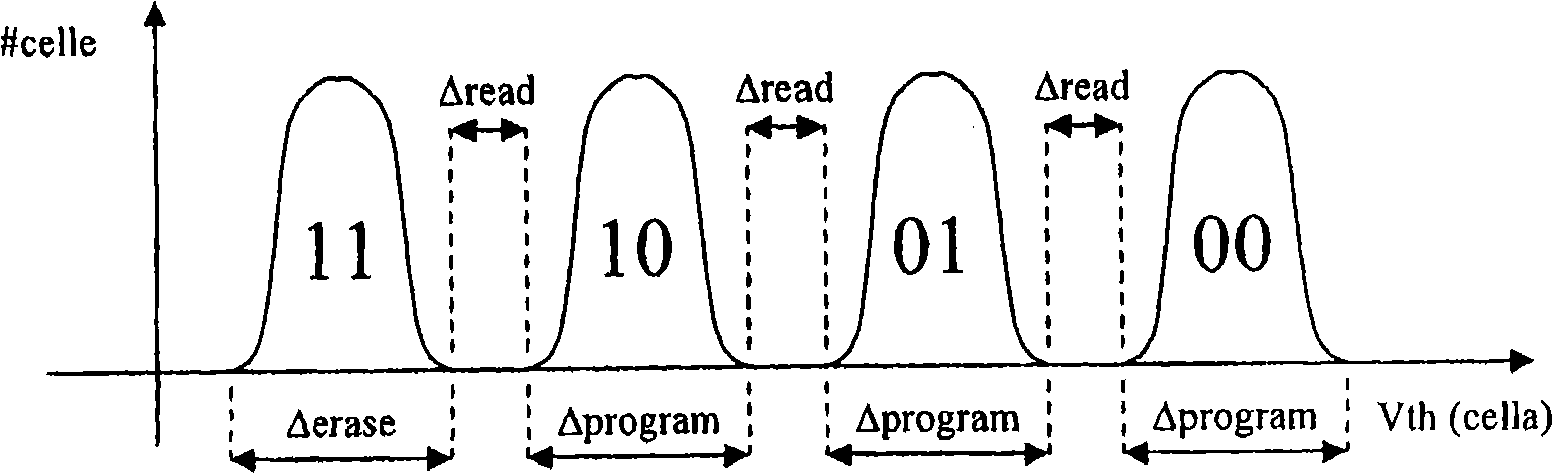

Memory device employing three-level cells and related methods of managing

The invention claims a memory device and related management method. The method adopts a three-level cell, wherein each pair of units stores three-bit strings in advance. Said memory device further includes a coding circuit and a decoding circuit for converting the three-bit string under storage in the write operation into two ternary strings to be written in the corresponding three-level cell, and for the contrary in the read operation. Each cell possibly has three states at most. As a result, the relative distribution of three different thresholds may be comparatively far away from the voltage level having worsened read interference phenomenon and contention phenomenon.

Owner:MICRON TECH INC

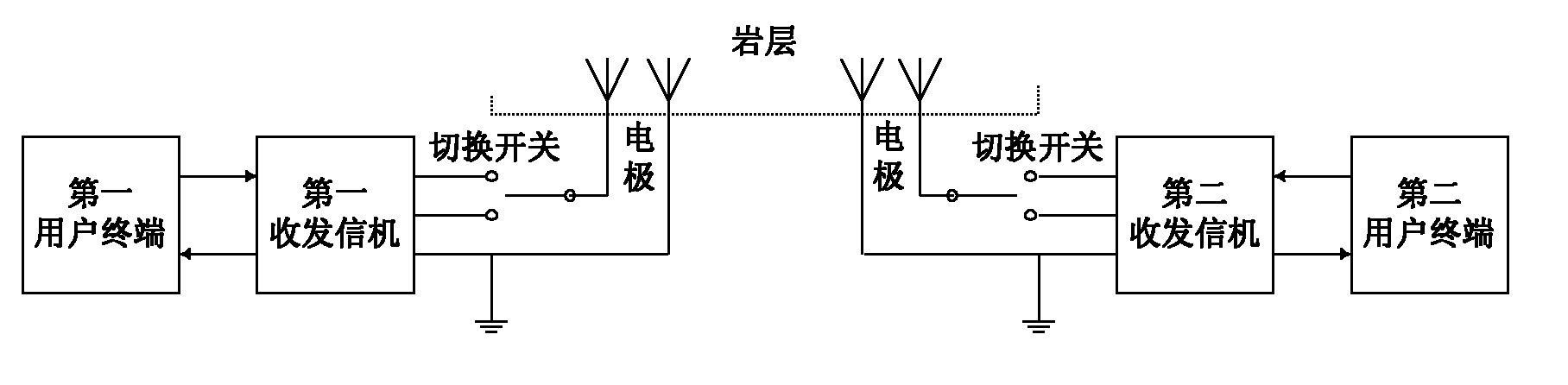

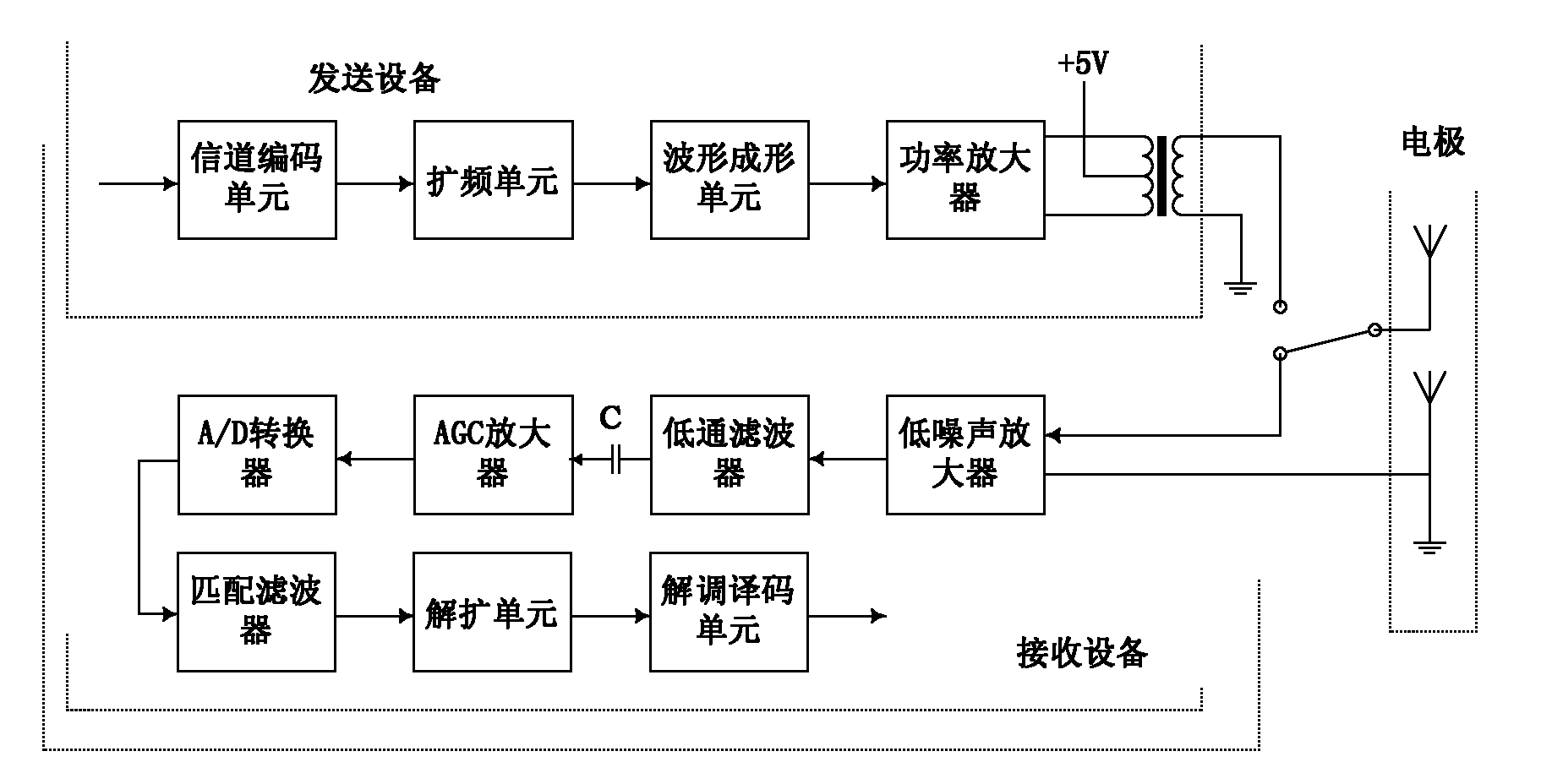

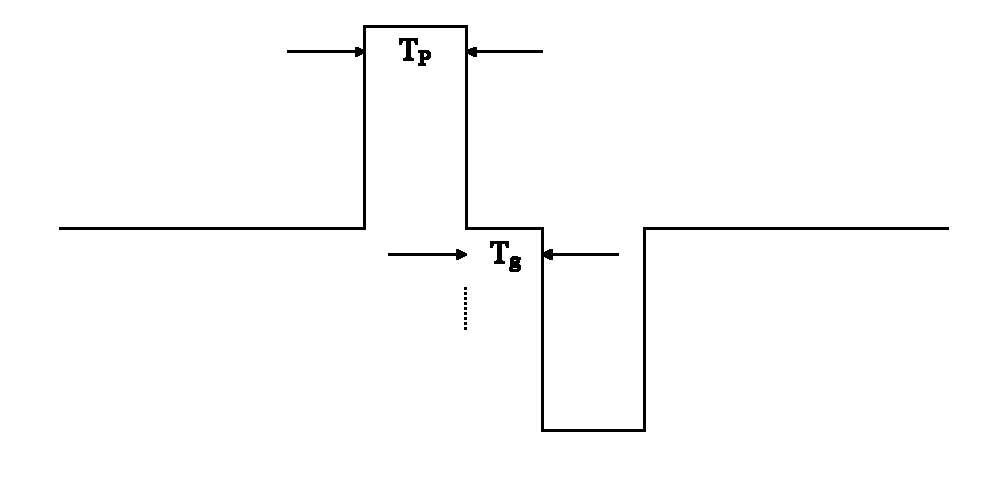

Ultra wideband stratum communication system

InactiveCN101977083ASmall duty cycleHigh peak-to-average power ratioTransmissionUltra-widebandOutput transformer

The invention discloses an ultra wideband stratum communication system which is mainly used for solving the problem that no reliable communication means can be taken when a serious accident occurs in a mine well. The ultra wideband stratum communication system comprises two transceivers, a pair of transmitting and receiving common electrodes and a transmitting and receiving changeover switch, a wireless channel is formed through the electrodes by using a stratum as a transmission medium so as to further form a time division duplex communication system. Each transceiver comprises transmitting equipment and receiving equipment, wherein the transmitting equipment comprise a channel coding unit, an M-element spectrum spreading unit and an E-class power amplifier; the receiving equipment comprise a low noise amplifier, a level-isolating straight-coupling capacitor, an AGC (Automatic Gain Control) amplifier, an A / D (Analog to Digital) converter and a dispreading, demodulating and channel decoding unit. A ternary pseudo random code with chip value of -1 or 0 or 1 is taken as an M-element spectrum spreading code, and a push-pull power amplifier with an output transformer is used as the E-class power amplifier. The invention has the advantages of small signal duty ratio, high peak-to-average power ratio, good error code characteristics and long transmission distance, and can provide a reliable communication means for mine well disaster relief.

Owner:XIDIAN UNIV

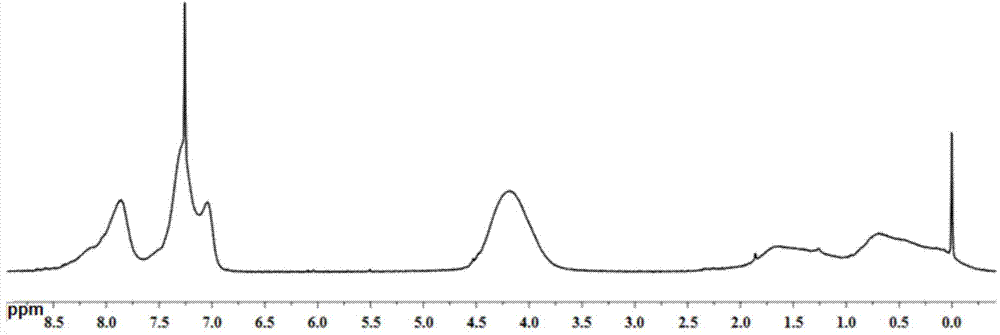

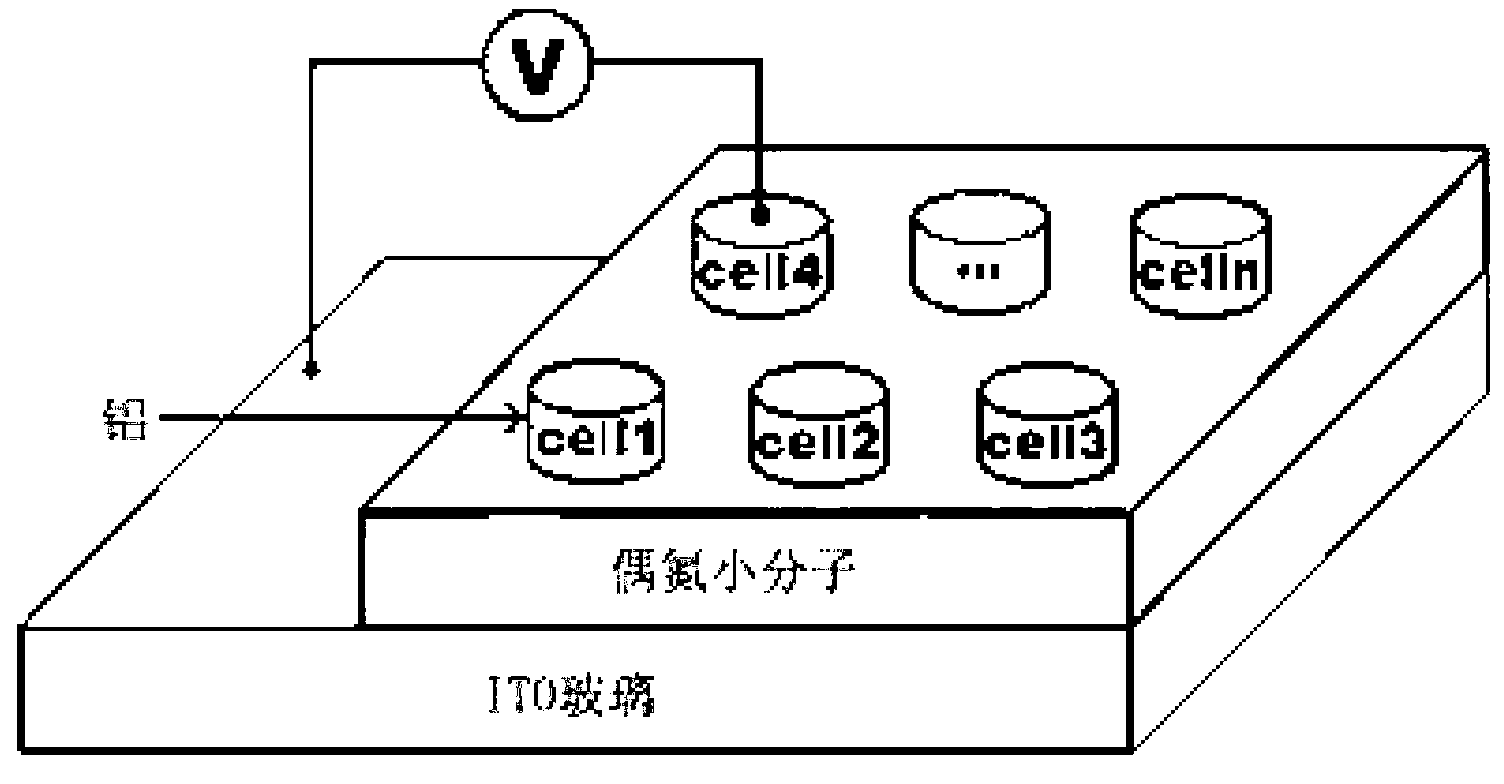

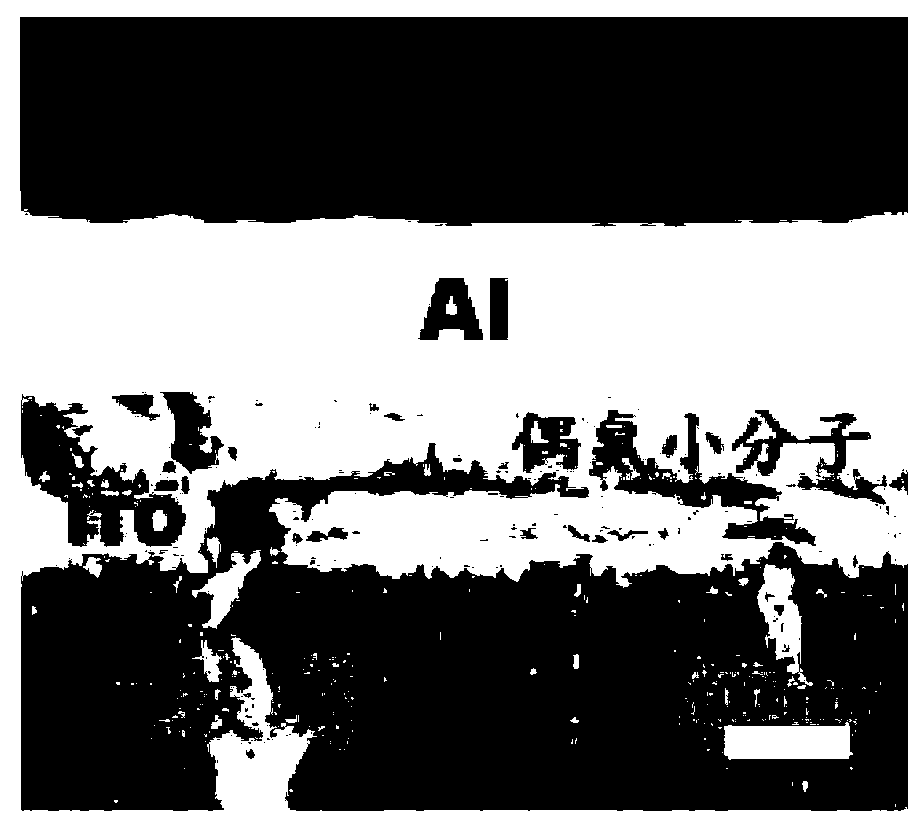

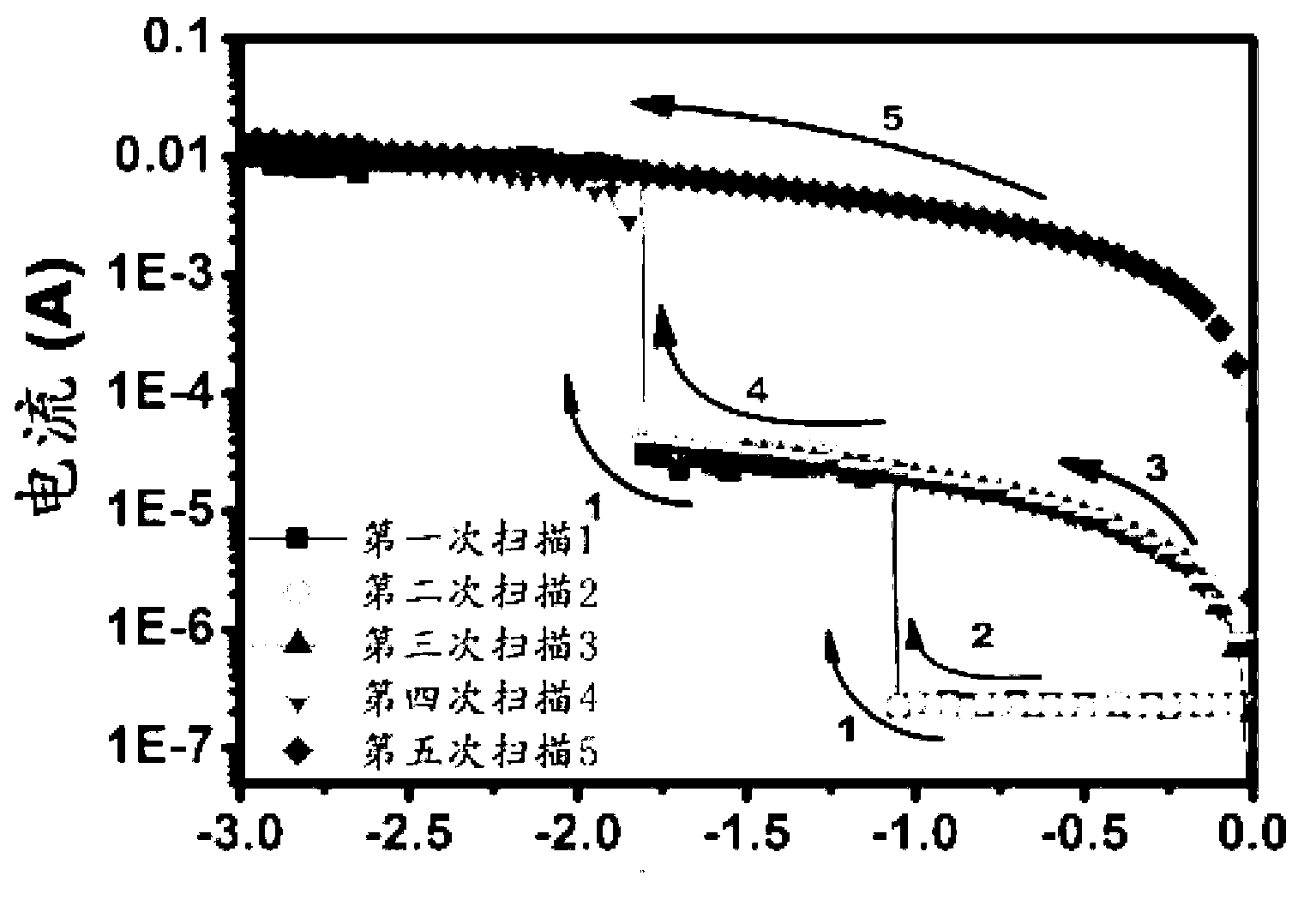

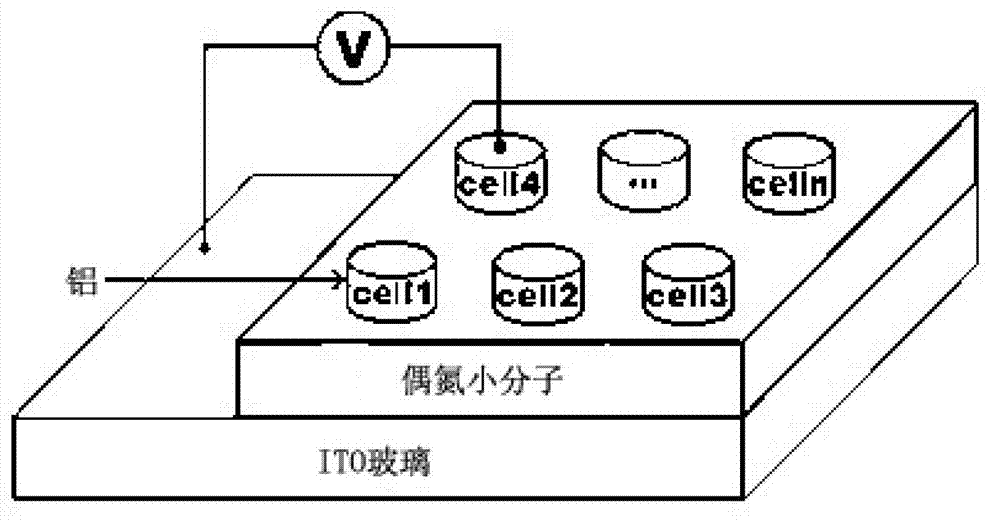

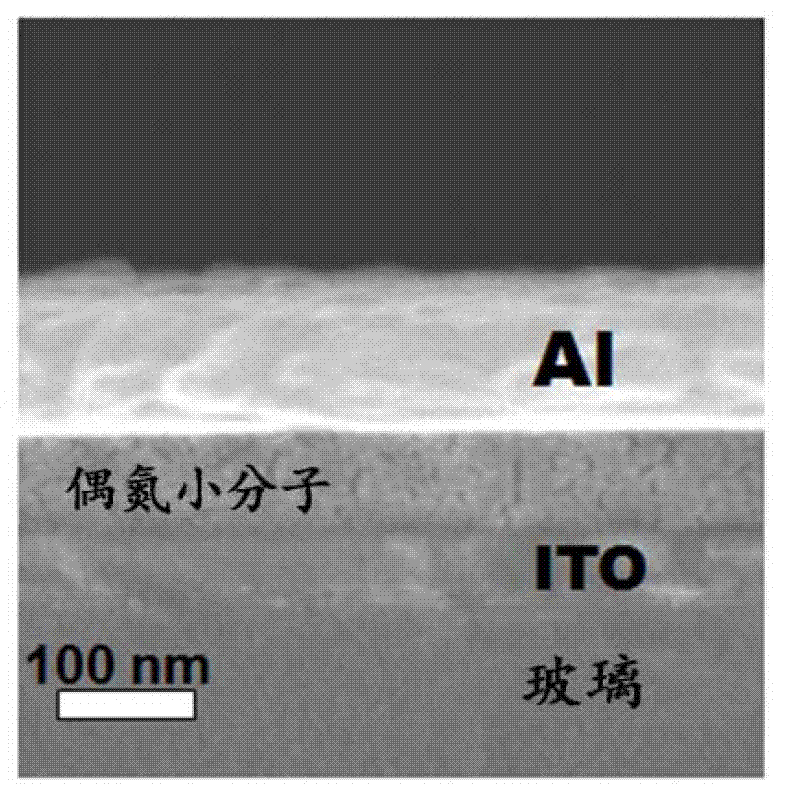

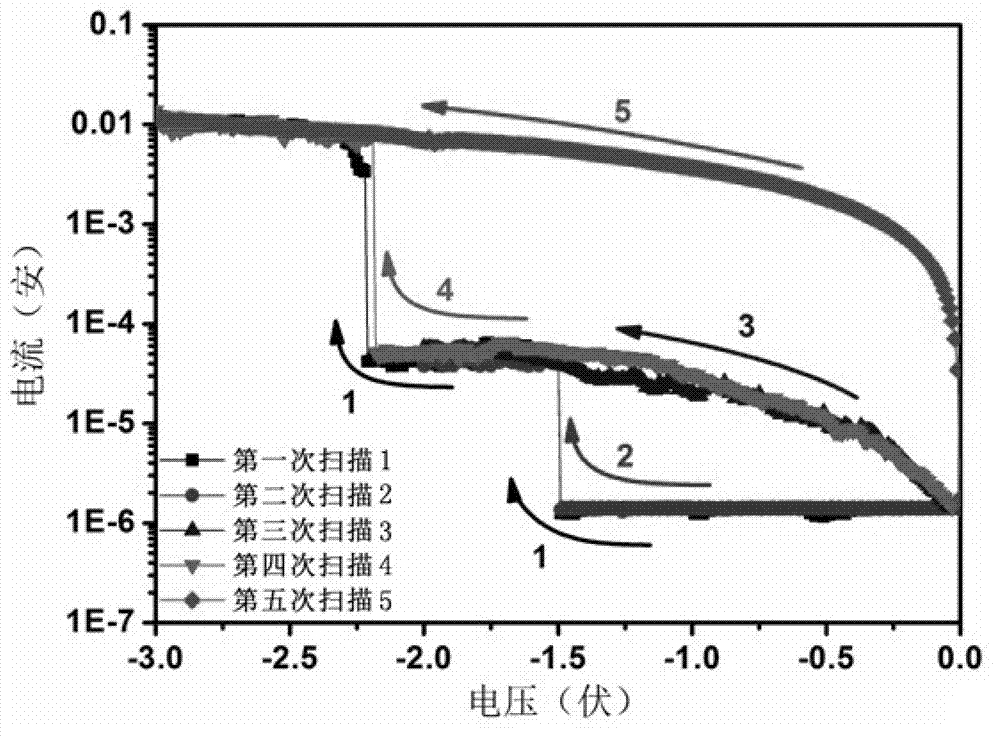

Ternary system electric storage material and preparation and application thereof

InactiveCN103497176AIncrease information storage capacityImprove stabilityOrganic chemistrySolid-state devicesChemical structureElectricity

The invention discloses a ternary system electric storage material and preparation and application of the ternary system electric storage material. The chemical structure general formula of the ternary system electric storage material is , wherein x ranges from 5 to 9, y ranges from 1 to 5, the number-average molecular weight ranges from 11000 to 13000, the molecular weight distribution ranges from 1.4 to 1.6, and R is -Br or -H or -NO2 or -N(CH2CH3)2. The ternary system electric storage material has the high performance of having the ultrahigh electrical information storage intensity, and the information storage capacity of the material is greatly improved. Meanwhile, a ternary system storage device can be obtained based on the ternary system electric storage material, the preparation method is simple and high in efficiency, the obtained ternary system data storage device is high in stability, the data memory space in a unit intensity increases exponentially in comparison with the data memory space based on '0' and '1' binary data storage, and therefore the ternary system electric storage material has great value in ultrahigh density data storage application of the next generation.

Owner:SUZHOU UNIV

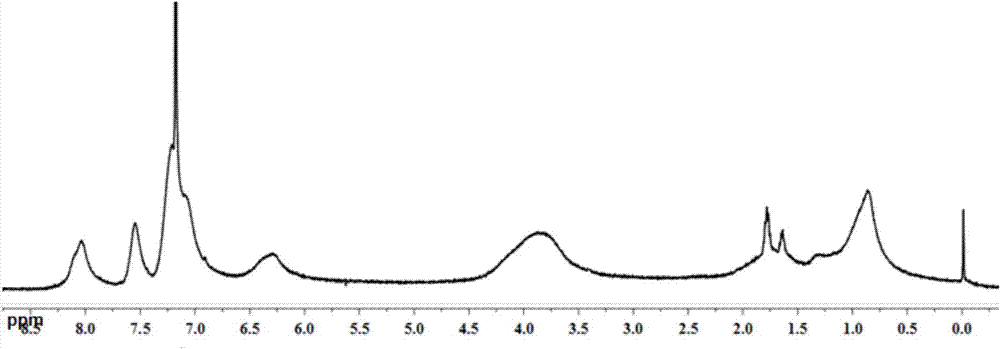

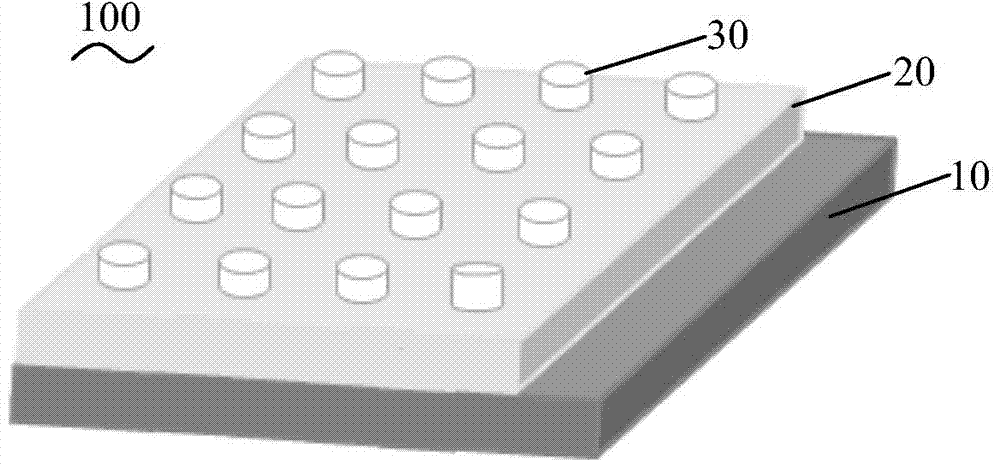

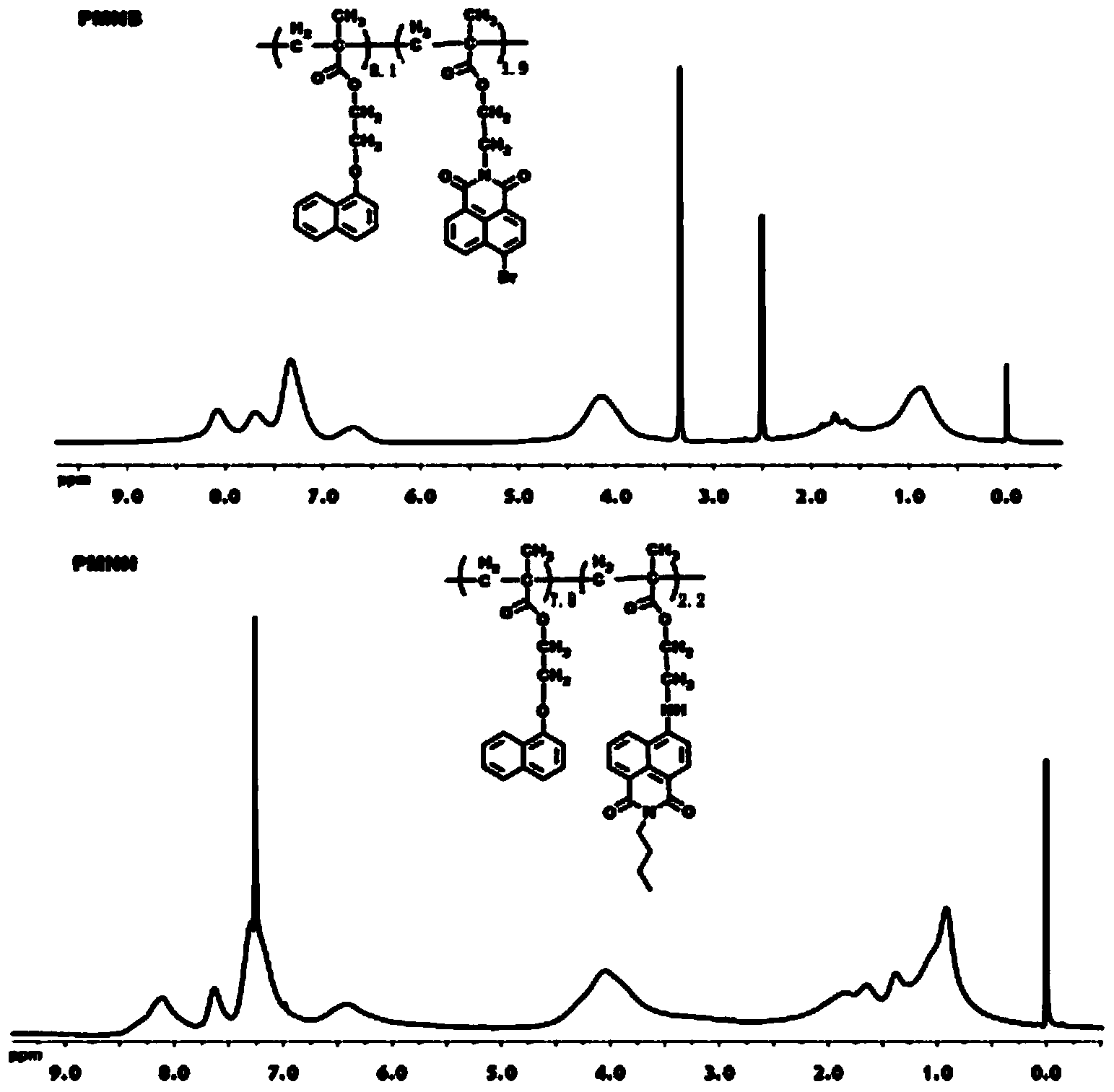

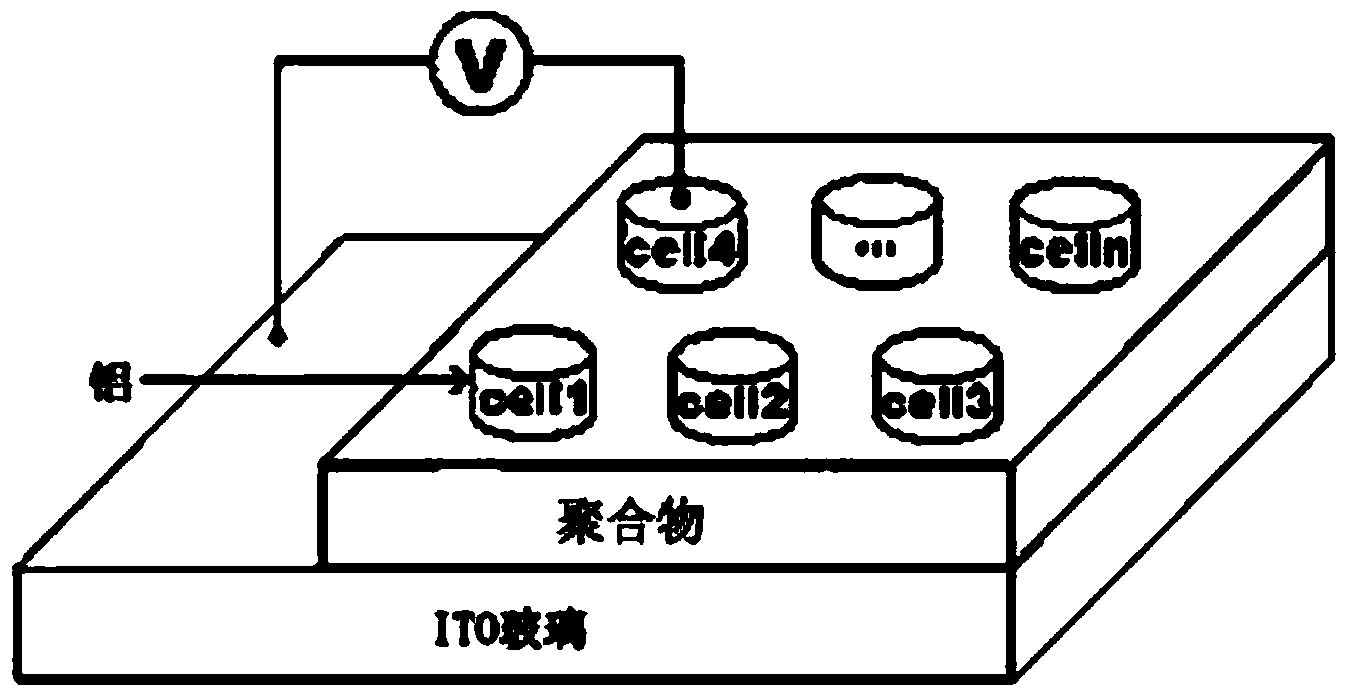

Novel copolymer based on naphthalene nucleus, preparation method thereof and ternary electric storage device prepared therefrom

InactiveCN103554351AThe preparation process is matureImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingOrganic filmElectricity

The invention discloses ternary electric storage materials PMNB and PMNN prepared from a novel copolymer based on a naphthalene nucleus which is used as a functional group, wherein x is not less than 7.5 and less than 10, and y is greater than 0 and not greater than 2.5. The PMNB and PMNN disclosed by the invention are simple in synthesis process; a ternary data storage device with a sandwich structure of bottom electrode / organic film / top electrode is prepared from the PMNB and PMNN, the preparation process is mature, the device has stable performance, a data storage amount in a unit density exponentially grows compared with '0' and '1' binary data storage, and the ternary data storage device has a great value in future ultrahigh-density data storage applications.

Owner:SUZHOU UNIV

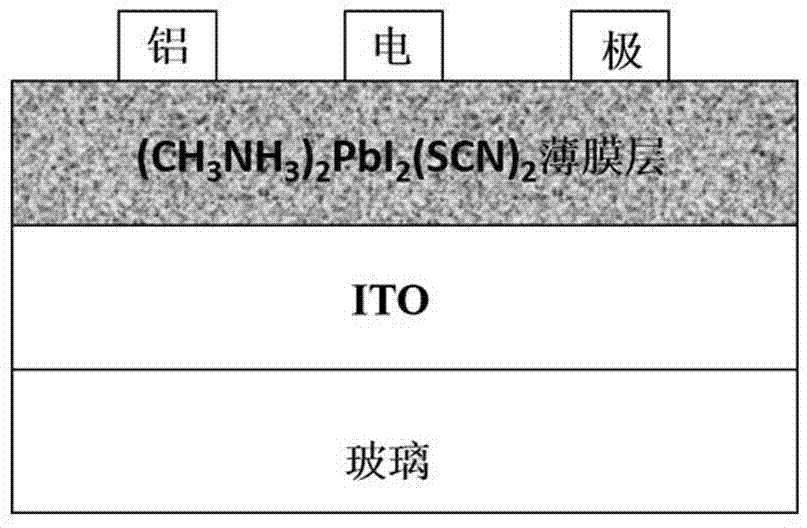

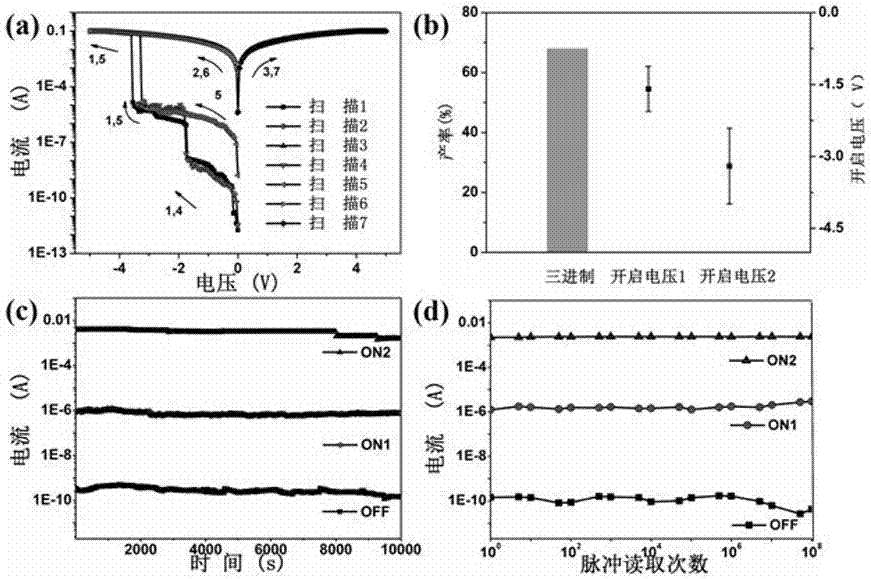

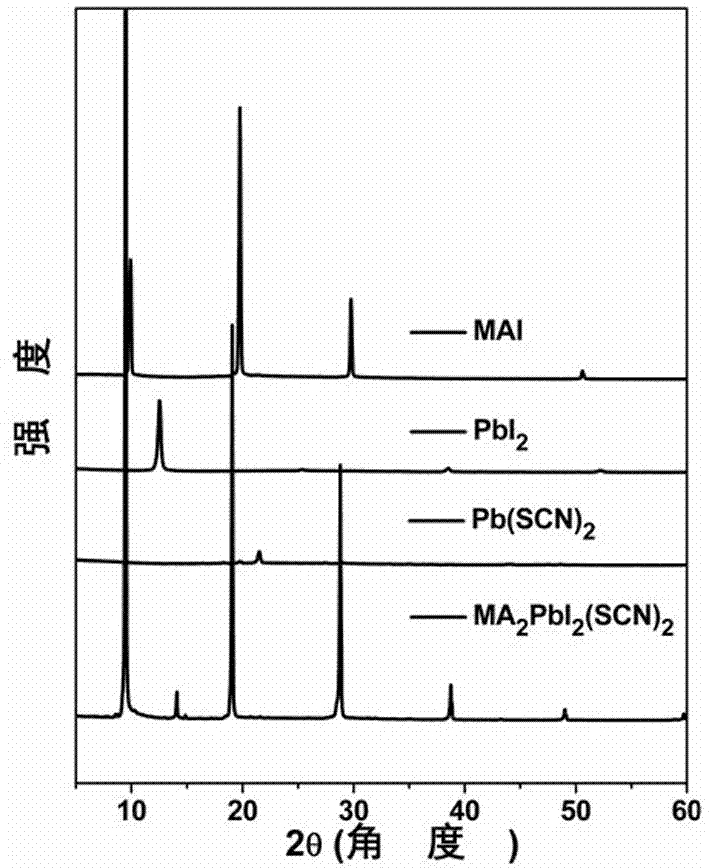

Pseudohalogen induction-based two-dimensional perovskite electric storage device and preparation method therefor

ActiveCN107316939ASolving Manufacturing ComplexitySolve yieldSolid-state devicesSemiconductor/solid-state device manufacturingElectricityPseudohalogen

The invention discloses a pseudohalogen induction-based two-dimensional perovskite (CH<3>NH<3>)<2>PbI<2>(SCN)<2> electric storage device and a preparation method therefor. The preparation method comprises the following steps of dissolving methyl amine iodide into a DMF solvent, and then adding lead thiocyanate into the solution, fully oscillating and preparing into a yellow perovskite solution; coating a substrate with the perovskite solution to prepare an active layer; and next, preparing an electrode on the active layer to obtain the pseudohalogen induction-based two-dimensional perovskite (CH<3>NH<3>)<2>PbI<2>(SCN)<2> electric storage device. The pseudohalogen induction-based two-dimensional perovskite material is formed by organic amine salt and the inorganic metallic compound through a coordination effect so as to prepare the organic electric storage device with the sandwich structure, so that an organic electric storage behavior is realized successfully; meanwhile, the preparation method is simple and the ternary electric storage behavior is high in yield; and therefore, the invention also discloses an application of the two-dimensional perovskite material in the preparation of the electric storage device.

Owner:SUZHOU UNIV

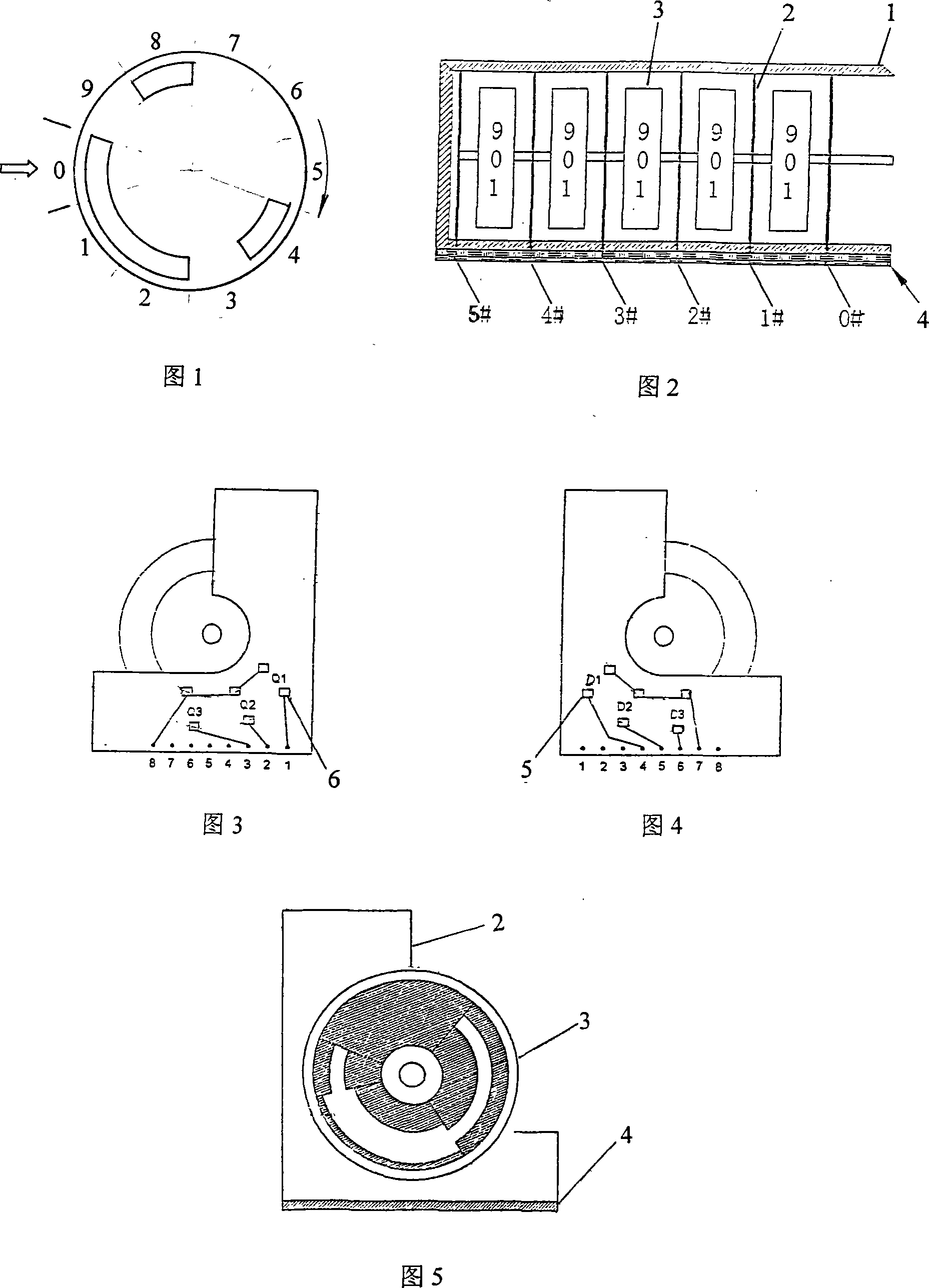

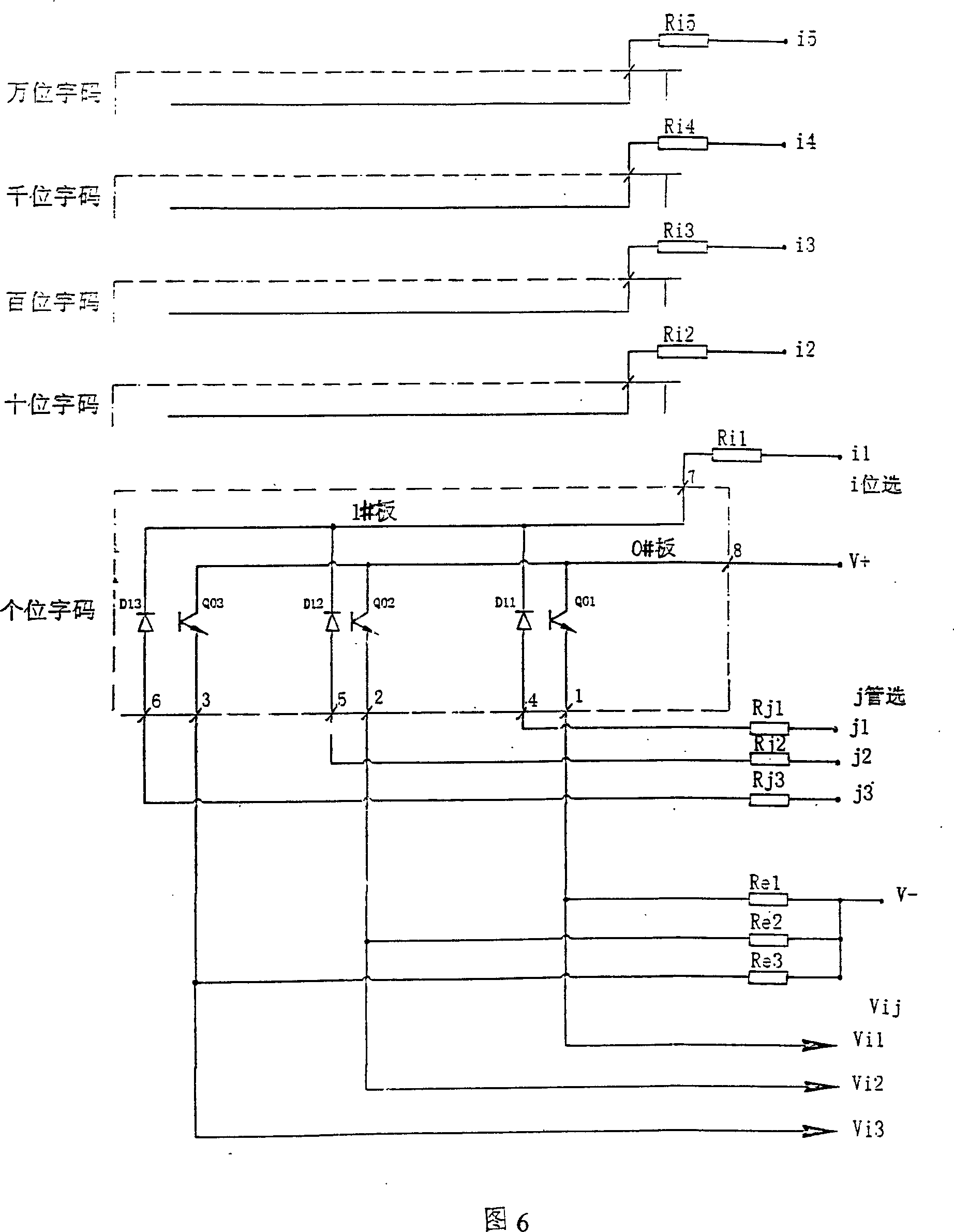

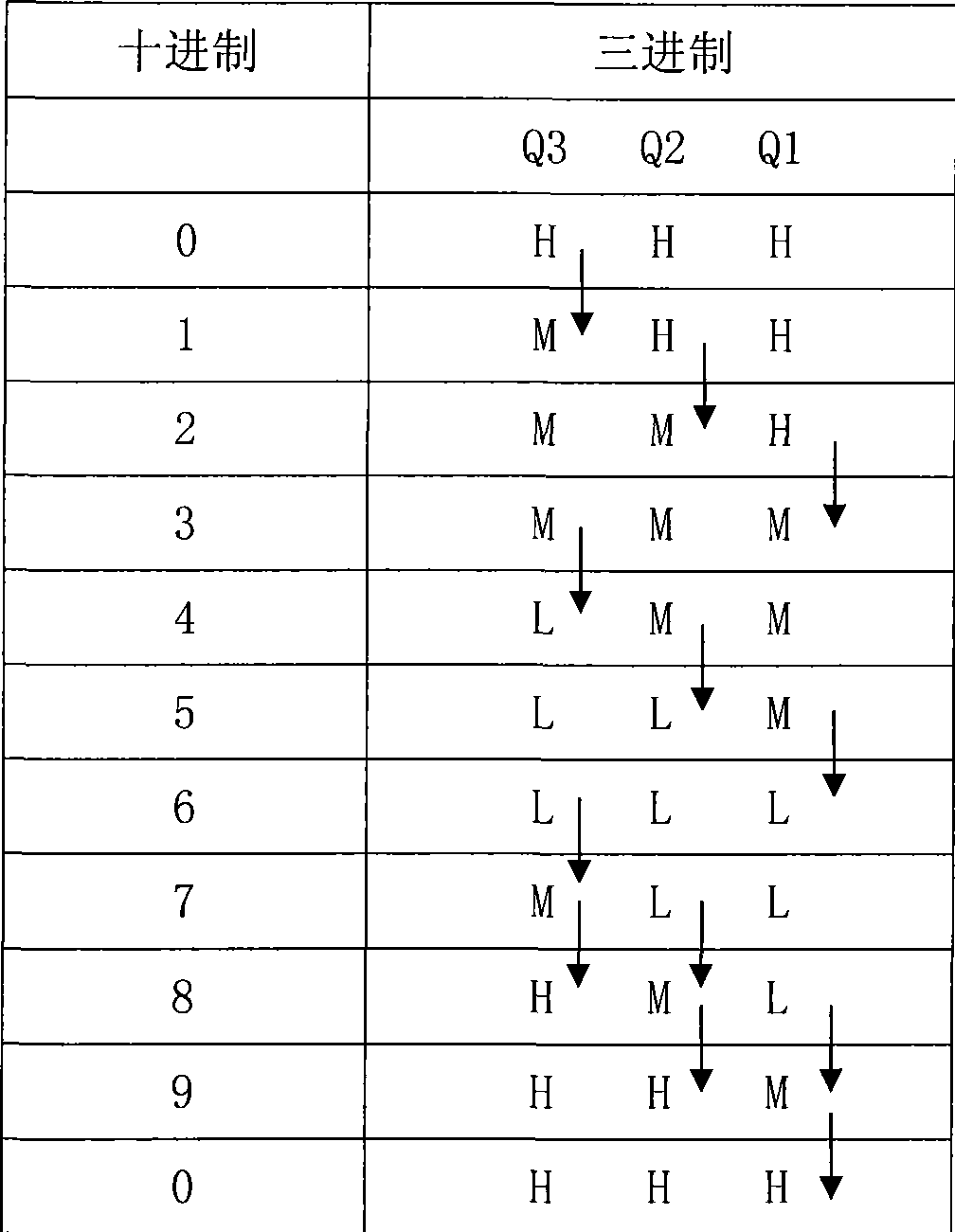

Ternary system clobber-free number wheel code disk sensor

InactiveCN101122480AReduce in quantitySimple structureConverting sensor outputElectricityRadial plane

A ternary non-clobber character wheel dial sensor includes a mechanical counter frame, a mechanical character wheel arranged on a shaft in the frame, flexile printed circuits inserted in the character wheel and a connecting bottom plate. The sensor is characterized in that the radial plane of the character wheel is zoned and coded according a ternary coding method. The left flexible printed circuit of the character wheel is equipped with three light emitting diodes for lighting. The relative position of the right flexible printed circuit is equipped with three receiving triodes for reading. The flexible printed circuit is electrically connected with a microprocessor through the connecting bottom plate bus. The beneficial effects of the invention are that binary code discs are substituted by ternary code discs. No clobber is on any position of a code disc. Compared with a present five bits binary code disc, the quantity of the photodiodes and photo triodes is reduced by two fifths. And the aims of simple structure, convenience, practicality and lowered cost are achieved. The invention can be applied various metering instruments using mechanical counter and absolute code angle displacement sensors.

Owner:上海元上科技股份有限公司

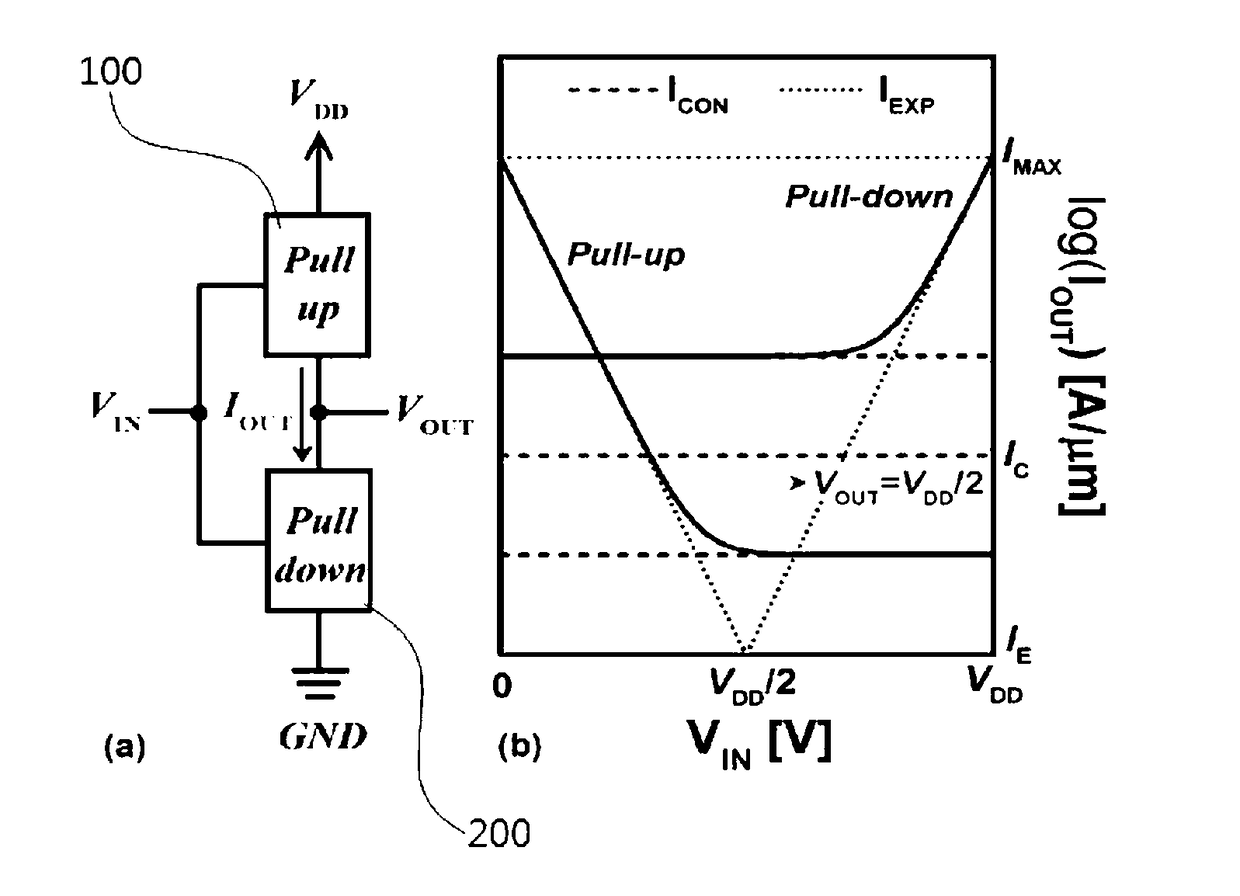

Ternary digit logic circuit

ActiveUS10133550B2Increase bit densityReduce power densityPulse generation by bipolar transistorsPower reduction by control/clock signalEngineeringVoltage source

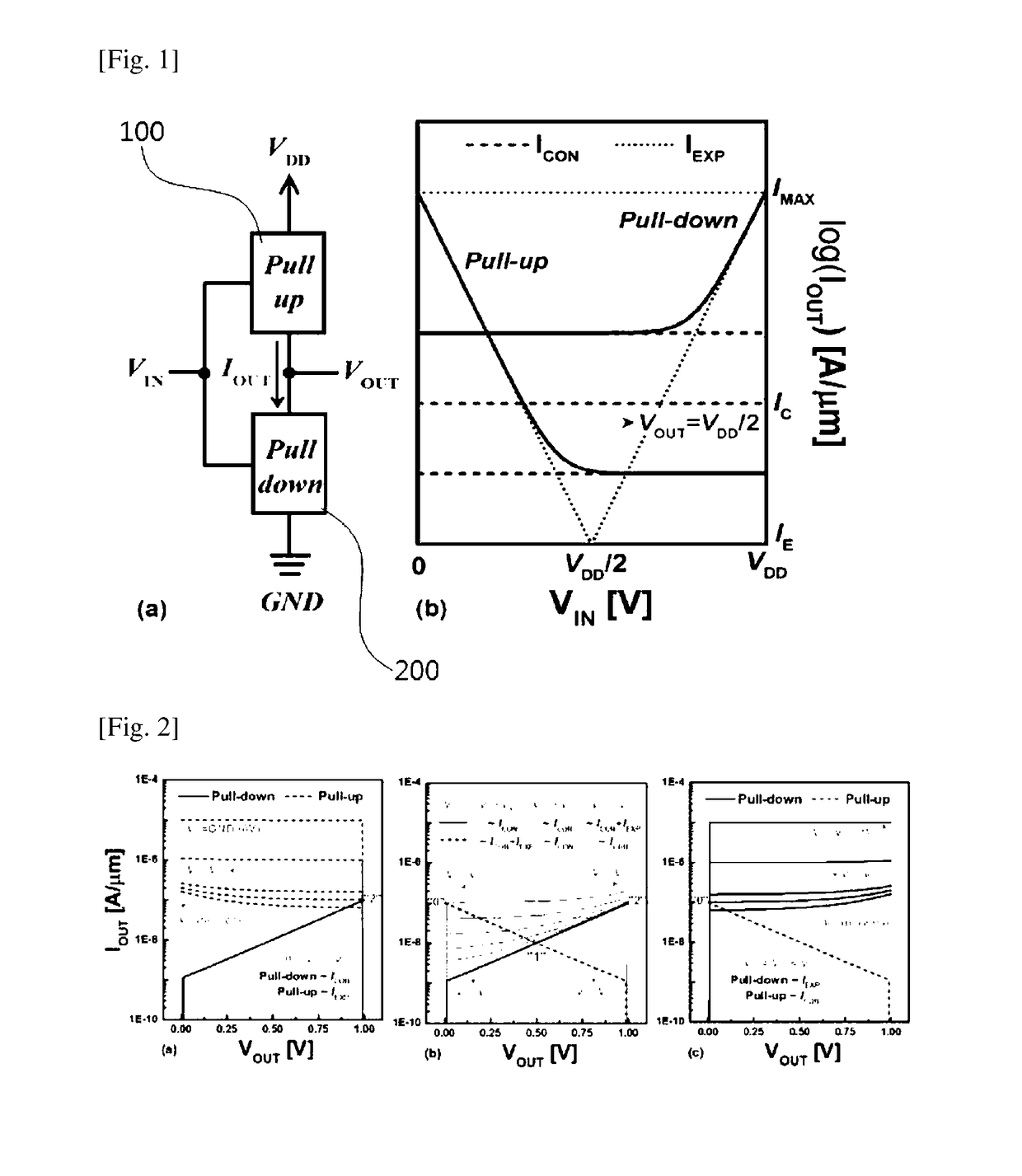

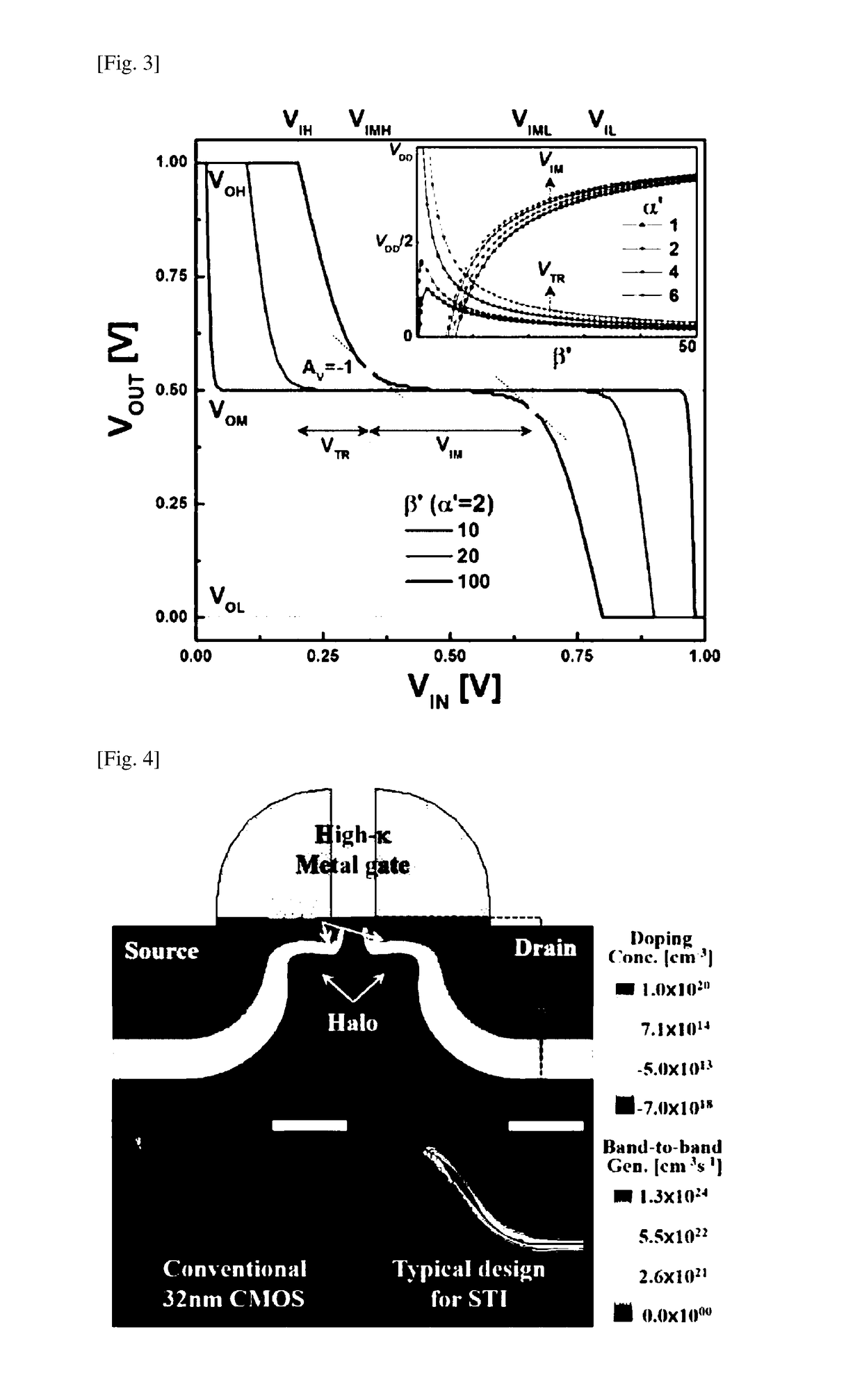

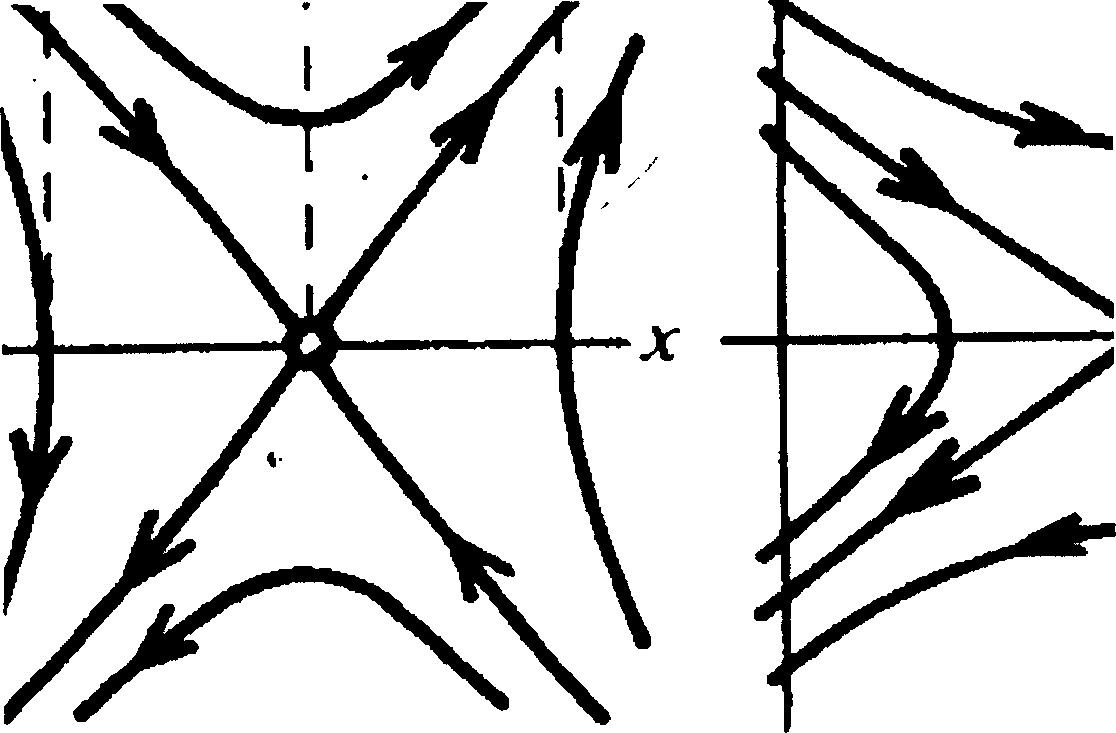

A ternary logic circuit according to the present invention includes a pull-up device (100) and a pull-down device (200) connected in series between power voltage sources (VDD and GND), and an input voltage (VIN) source and output voltage (VOUT) source. When both the pull-up device (100) and the pull-down device (200) are turned off by an input voltage (VIN), both the pull-up device (100) and the pull-down device (200) operate as simple resistors which are affected only by an output voltage (VOUT) and form a ternary digit (“1” state) through voltage division. When only one of the pull-up device (100) or the pull-down device (200) is turned on to allow a current to flow therethrough, VDD (“2” state) or GND (“0” state) is output as the output voltage (VOUT). Accordingly, a bit density can be remarkably increased.

Owner:UNIST ULSAN NAT INST OF SCI & TECH

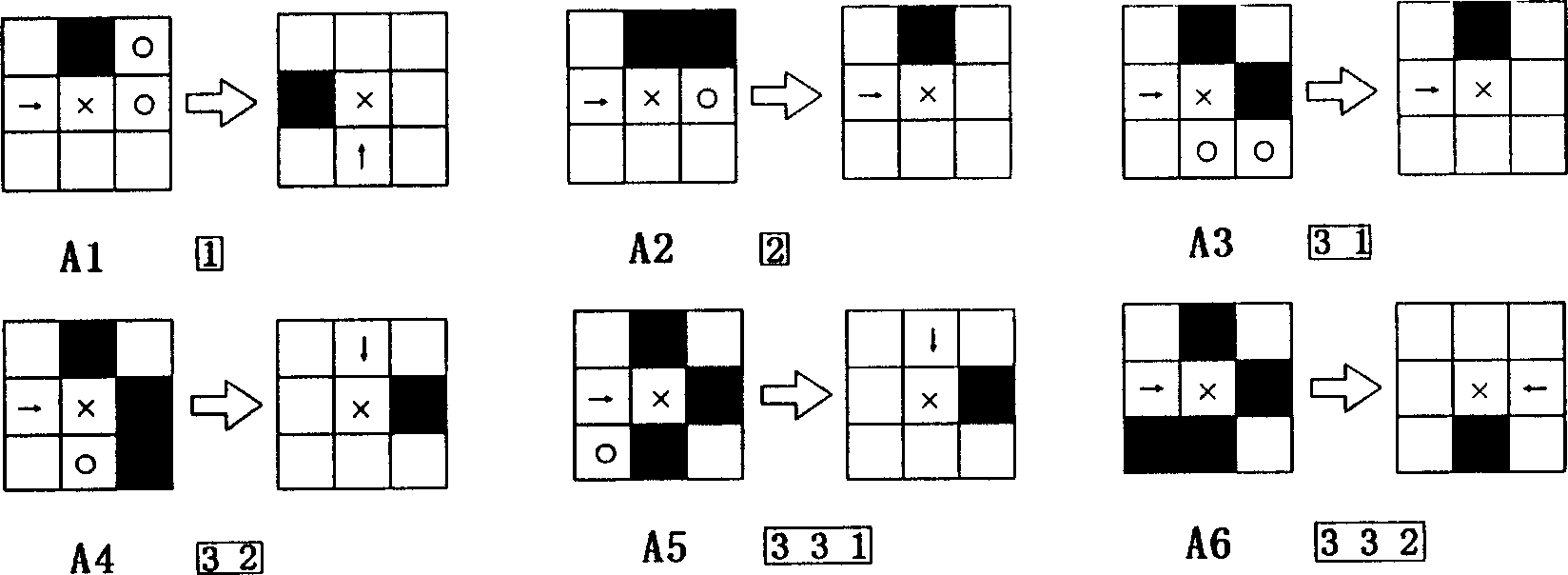

Method for providing format of storing images in high compress performance

InactiveCN1540587AShorten the timeImprove transmission efficiencyImage codingDot matrixImage recording

Based on automaton of demarcating borderline and vertex chain encoding method, image recording, image unit searching, ternary notation coding and image restoration are encoded through vertex chain. Implementing step are: selecting three vertexes 1, 2, 3 on square dot matrix of image, recording corresponding vertexes along a direction so as to obtain record of image unit in method of vertex chain encoding; generating vertex chain coding of image unit by using automaton of demarcating borderline automatically; registering coordinate of starting point of chain coding in ternary notation. Outstanding strongpoint is high compress performance of exceeding all image storage formats in current.

Owner:UNIV OF SHANGHAI FOR SCI & TECH

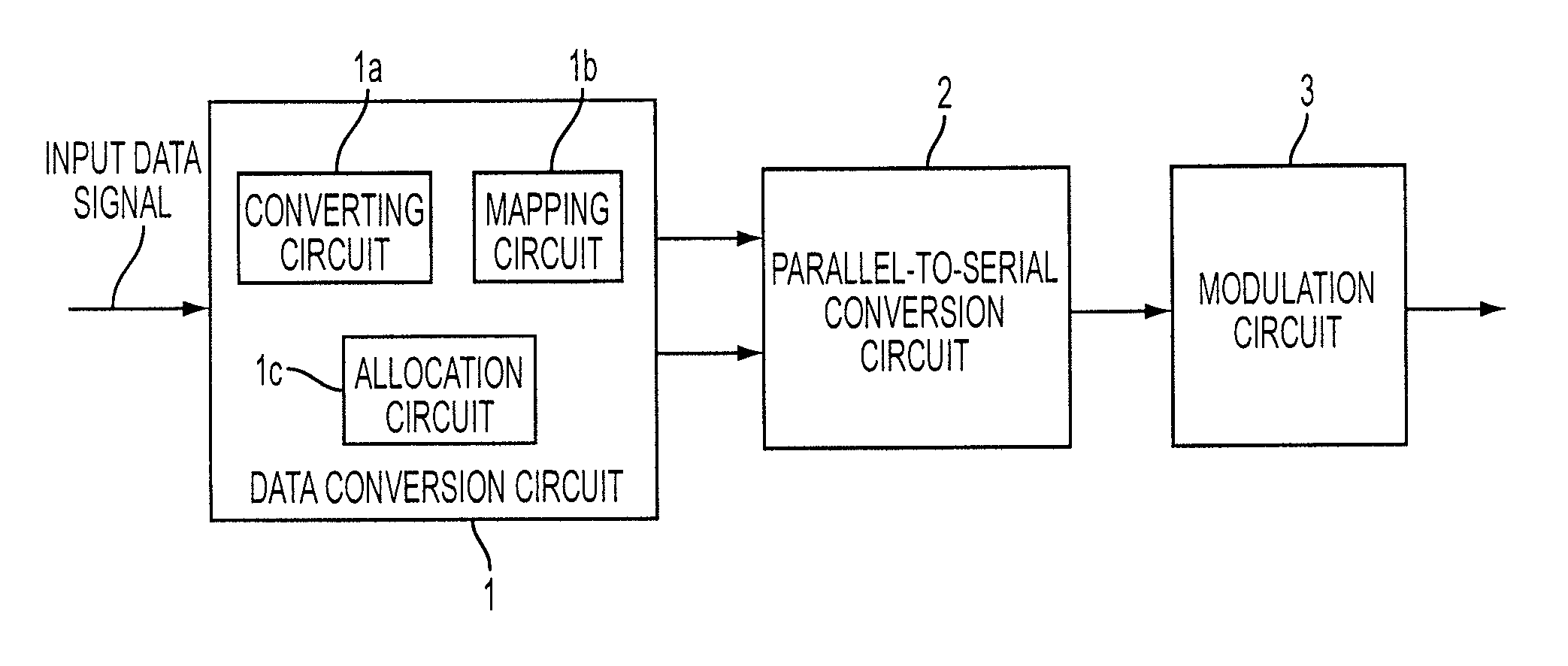

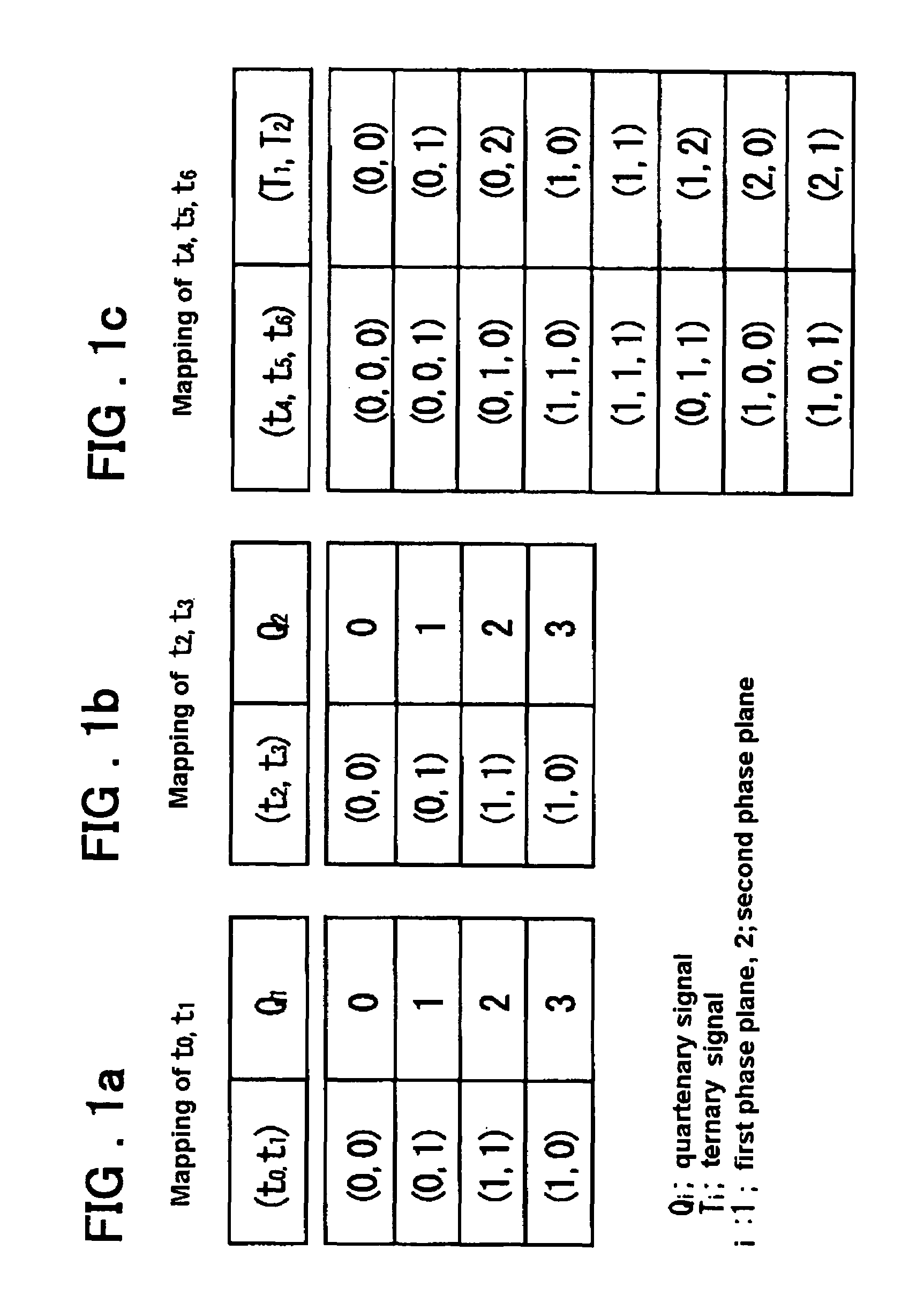

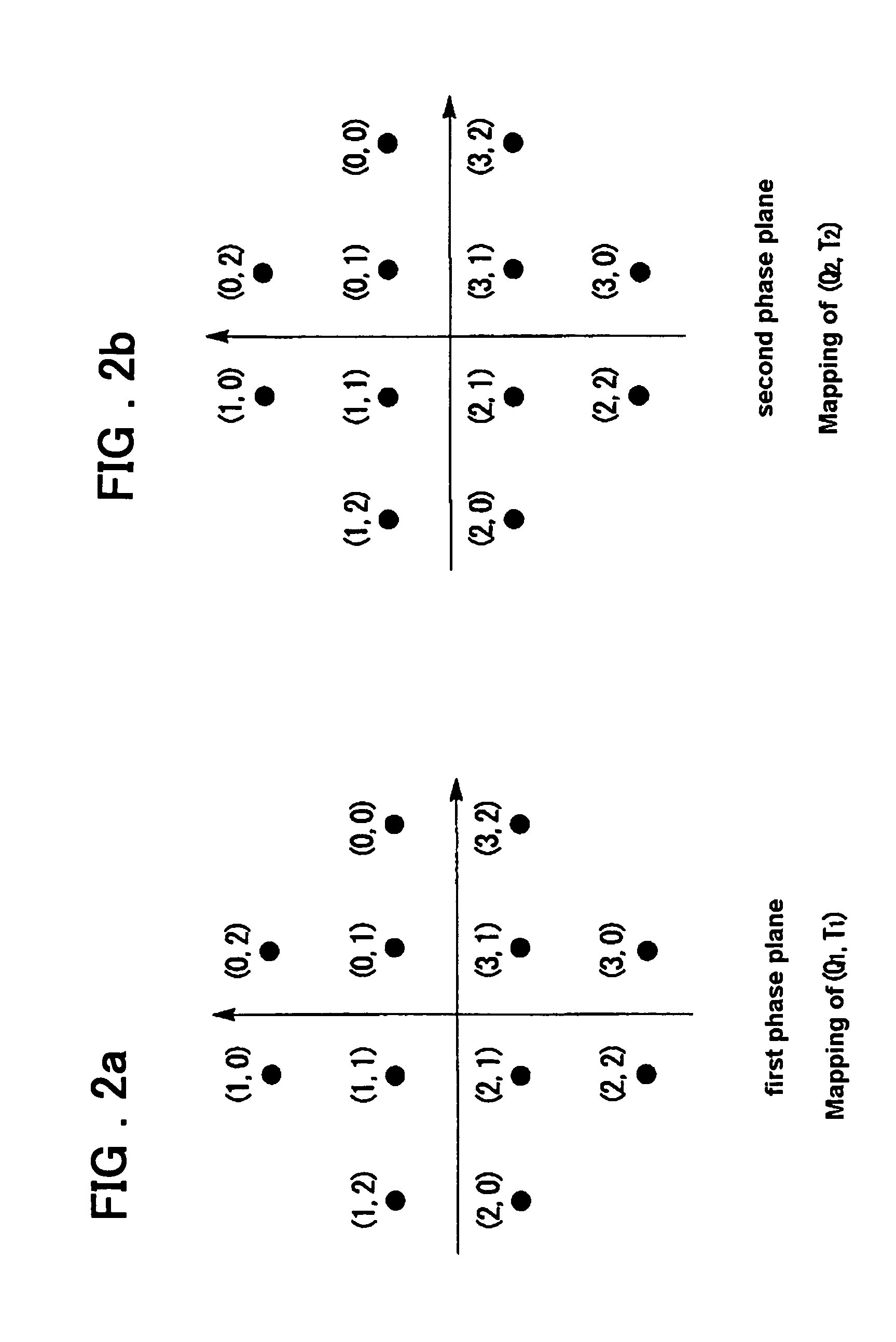

Multi-level modulation method and system

InactiveUS7630453B2Error minimizationReducing the number of bit error against symbol errorsPhase-modulated carrier systemsMultiple carrier systemsFour quadrantsEngineering

Disclosed is a method and a system for performing N-ary modulation in which bit errors may be reduced against symbol error. A binary signal, a bit length thereof being n, is associated with N-ary signals arranged in first and second phase planes respectively for transmission, wherein N is not a number belonging to powers of 2 but is a number belonging to a series beginning from 12 and sequentially doubled, that is, any one of 12, 24, 48, 96, . . . , and wherein n is such that, if the bit length n is 7, 9, 11, 13, . . . , the number N is 12, 24, 48, 96, . . . , respectively, two out of the n bits are allocated for identifying four quadrants of the first phase plane, two out of the remaining (n−2) bits are allocated for identifying four quadrants of the second phase plane. The binary signal of three out of the n bits is converted into two digits of ternary signals (T1, T2). The ternary signals are mapped to the first and second phase planes with rotational symmetry of 90° or with axial symmetry.

Owner:NEC CORP

Azo molecule ternary electricity storage material at center of diaryl ketone and preparation and application thereof

ActiveCN102936208AThe preparation process is matureImprove performanceOrganic chemistrySolid-state devicesElectricityDiaryl ketone

The invention discloses an azo molecule ternary electricity storage material with diaryl ketone as a central radical and preparation and application thereof. A structural formula of azo molecules is as follows. In the formula, DAK is 3, 3'-dibenzoyl, 4, 4'-dibenzoyl or 2, 7-fluorenone; and R is N, N-two C1-C6 linear chain alkyl amino, N, N-diphenyl amino or hydroxyl. The azo molecules are simple in synthetic process, the azo molecules are made into a ternary data storage device of a sandwich structure of bottom electrodes / organic films / top electrodes, manufacturing process is mature, and the device is stable in performance. Compared with binary data storage based on 0 and 1, data storage content in unit intensity is increased exponentially, and the azo molecule ternary electricity storage material has enormous value in ultrahigh density data storage application in the future.

Owner:SUZHOU UNIV

Ternary electric memory material of azo chromophore of imide framework, as well as preparation and application of ternary electric memory material

InactiveCN102924461AThe preparation process is matureImprove performanceOrganic chemistrySolid-state devicesOrganic filmImide

The invention discloses a ternary electric memory material of azo chromophore based on imide framework, as well as preparation and application of the ternary electric memory material. The azo chromophore adopts the following structural formula: in the formula, Ar is shown in the specification, and R adopts N,N-bisCl-C6 alkylphenyl, N,N-diphenyl aminophenyl or para hydroxybenzene. The synthesis technology of the azo chromophore is simple, the para hydroxybenzene is made into a ternary data memory with a sandwich structure of bottom electrode / organic film / upper electrode, the manufacture technology is mature, the performance of the memory is stable, the data memory capacity in unit density is exponentially increased compared with binary data memory based on 0 and 1, and the material has huge value in the super-high density data memory application in the future.

Owner:SUZHOU UNIV

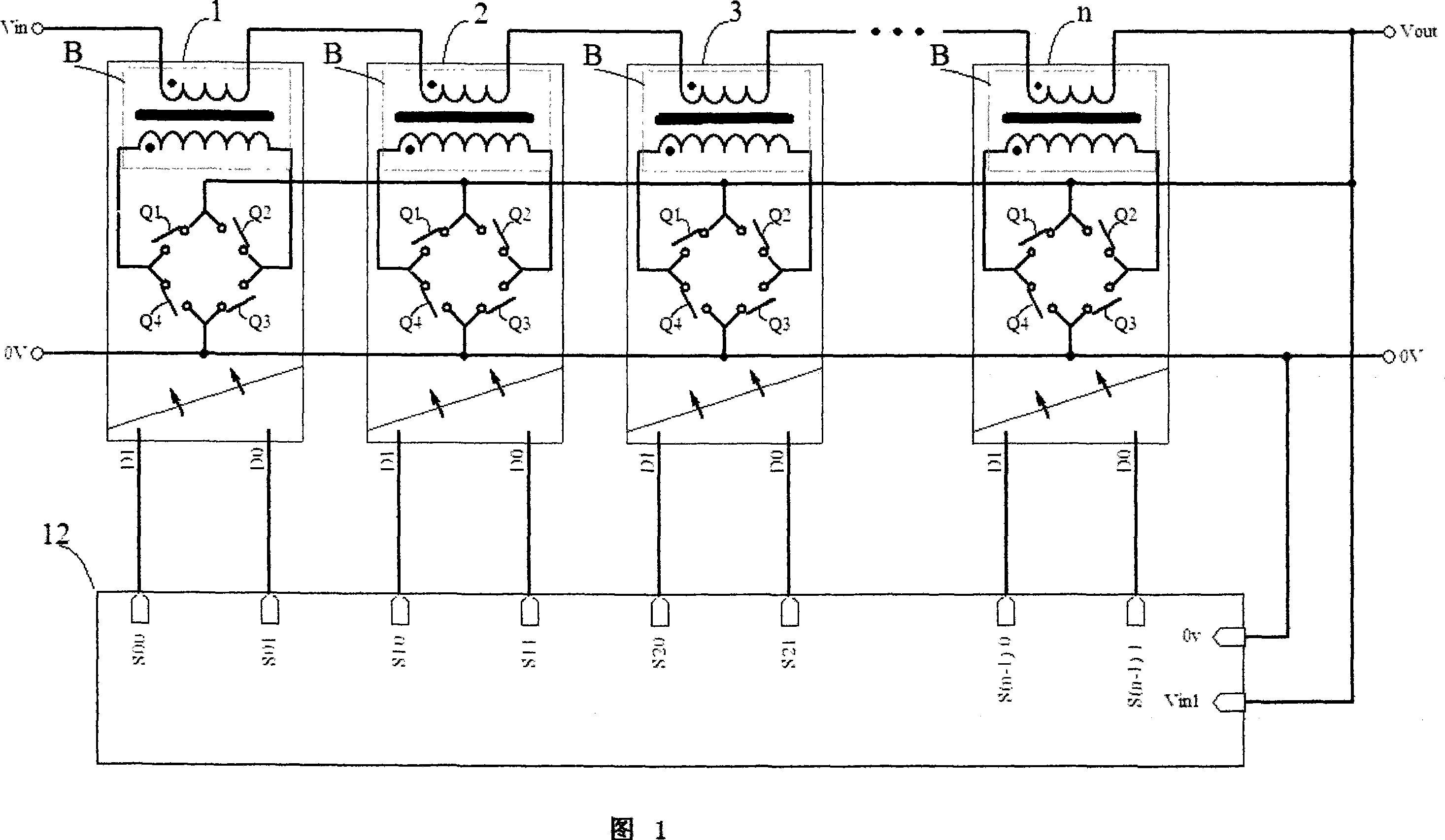

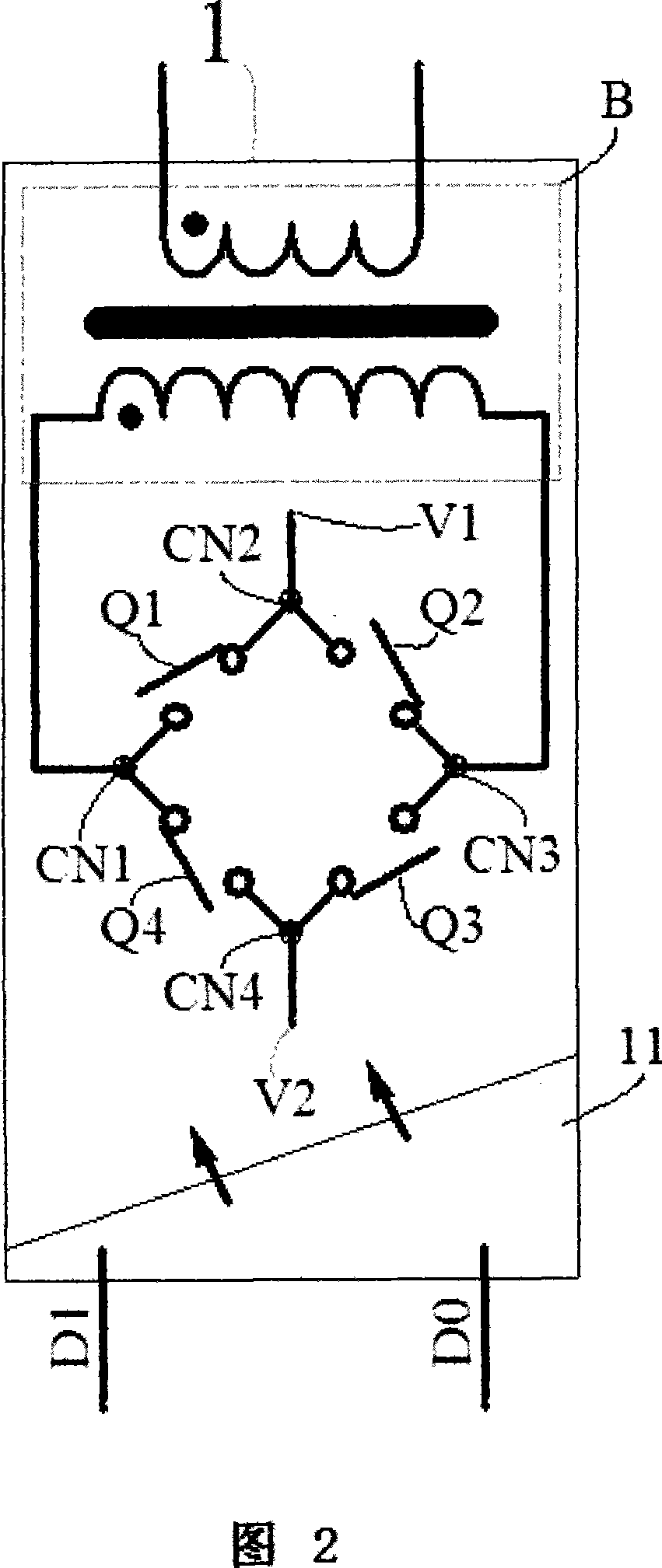

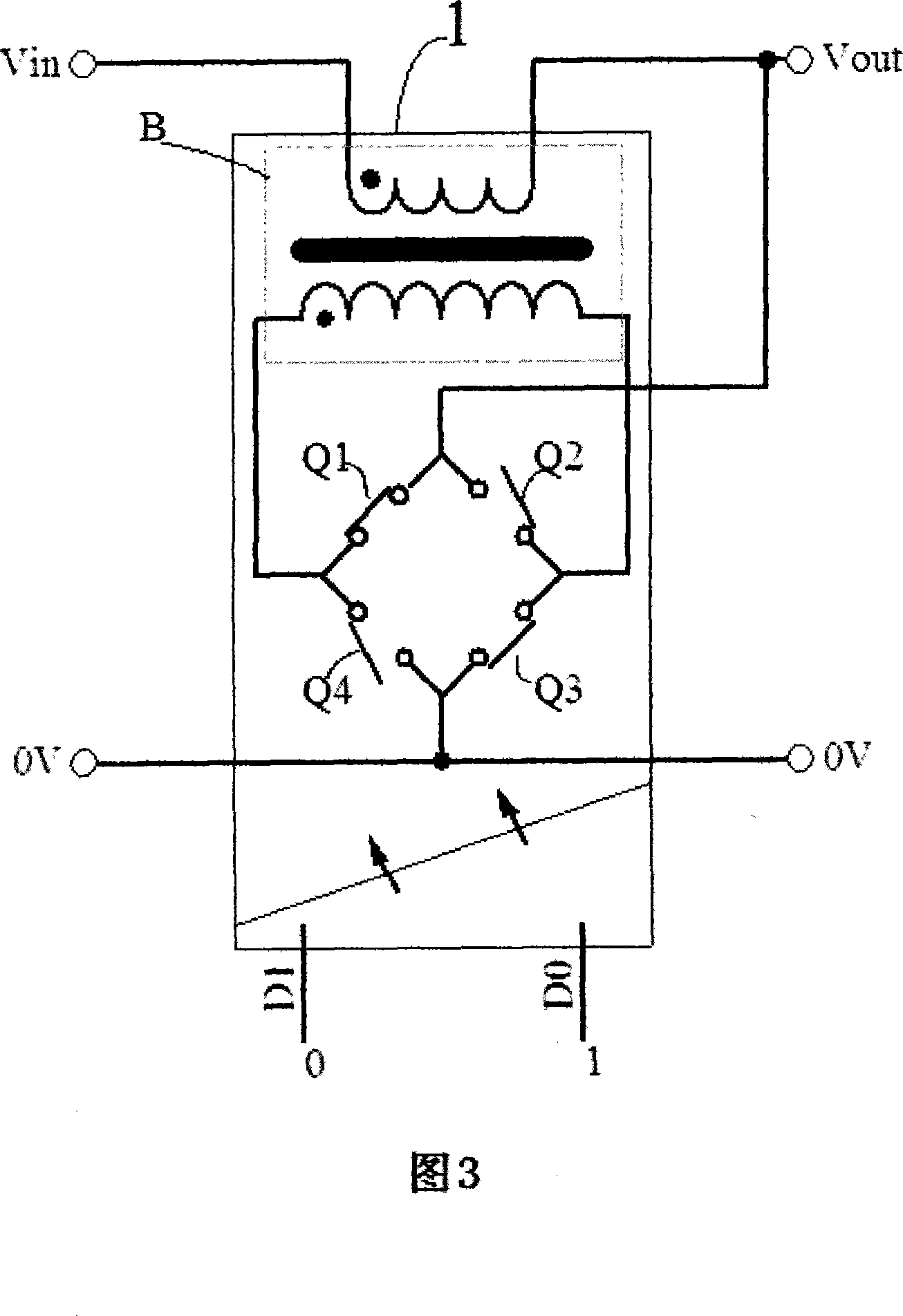

Ternary digital compensation type AC regulated power supply

InactiveCN101059701AReduce in quantityHigh voltage regulation accuracyElectric variable regulationTransformerAlternating current

As aforementioned n ternary voltage regulating circuits are arranged, as (1-n), wherein the turns ratio between the secondary and the first of the first transformer (B) is K, while the second is 31K, the third is 32K, as like, the n-th is 3n-1K, and the switch (Q1-Q4) only closes one group of (Q1, Q3), (Q1, Q2), or (Q3, Q4), (Q2, Q4). Therefore, a voltage regulator with n bits of ternary digit alternative-current stabilizer is provided. Assuming the values of m-th digit signal is Sm-1, the regulating input voltage is Vout, therefore, the output voltage Vs of the regulator is Vs=VoutK(10S0+31S1+32S2+...+3n-1Sn-1)(Sm-1=-1, 0, +1).

Owner:曾旭华

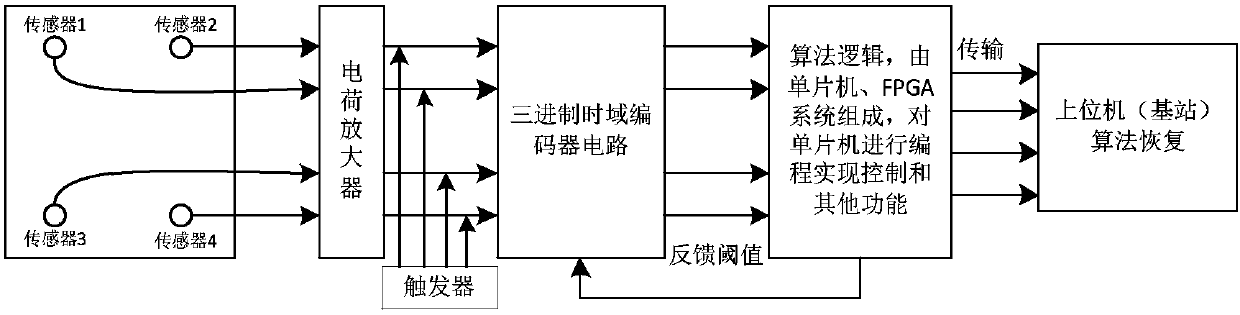

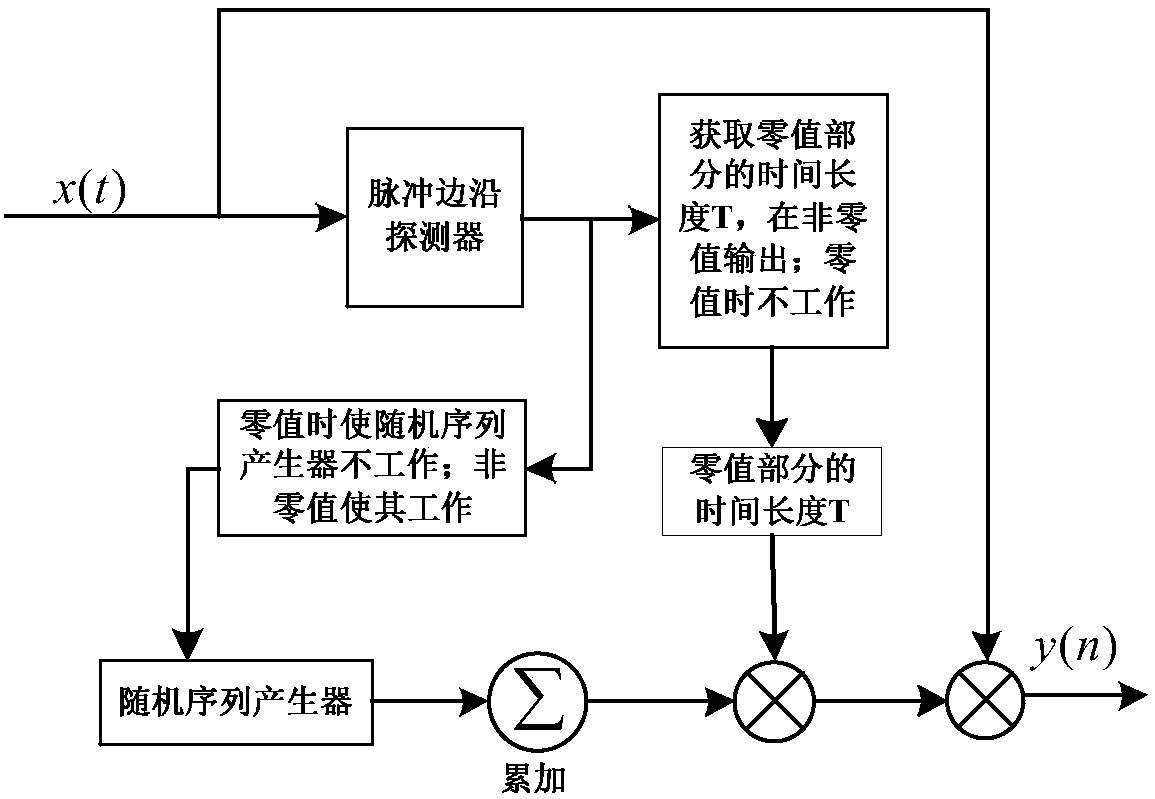

Impact monitoring-orientated digital asynchronous compressive sampling system and method

ActiveCN107561979AValid encodingSignificant amplitude jumpProgramme controlComputer controlTime domainData transmission

The invention provides an impact monitoring-orientated digital asynchronous compressive sampling system and method. According to the system and method of the invention, as for the time-domain sparseness and crest obviousness of impact monitoring signals, compressive sampling can be effectively performed on the impact monitoring signals. The system comprises three main parts, namely a time-domain ternary (-1,0,1) encoder module, an arithmetic logic module and a signal recovery module. According to the system and method of the present invention, change quantities in the impact monitoring signalscan be effectively captured; the impact monitoring signals are first subjected to ternary coding; and ternary coded information is subjected to compressive sampling, so that a small number of sampling points are obtained to recover original signals, and therefore, the storage pressure of data transmission can be decreased. Compared with a traditional analog compressive sampling method, the methodof the present invention is realized by digital circuits, so that the influence of noise interference and nonlinear factors in circuit systems can be decreased, and reconstruction accuracy can be improved. According to the method of the present invention, a time-division work scheme is adopted, so that the power consumption of the system can be effectively reduced.

Owner:XIAMEN UNIV

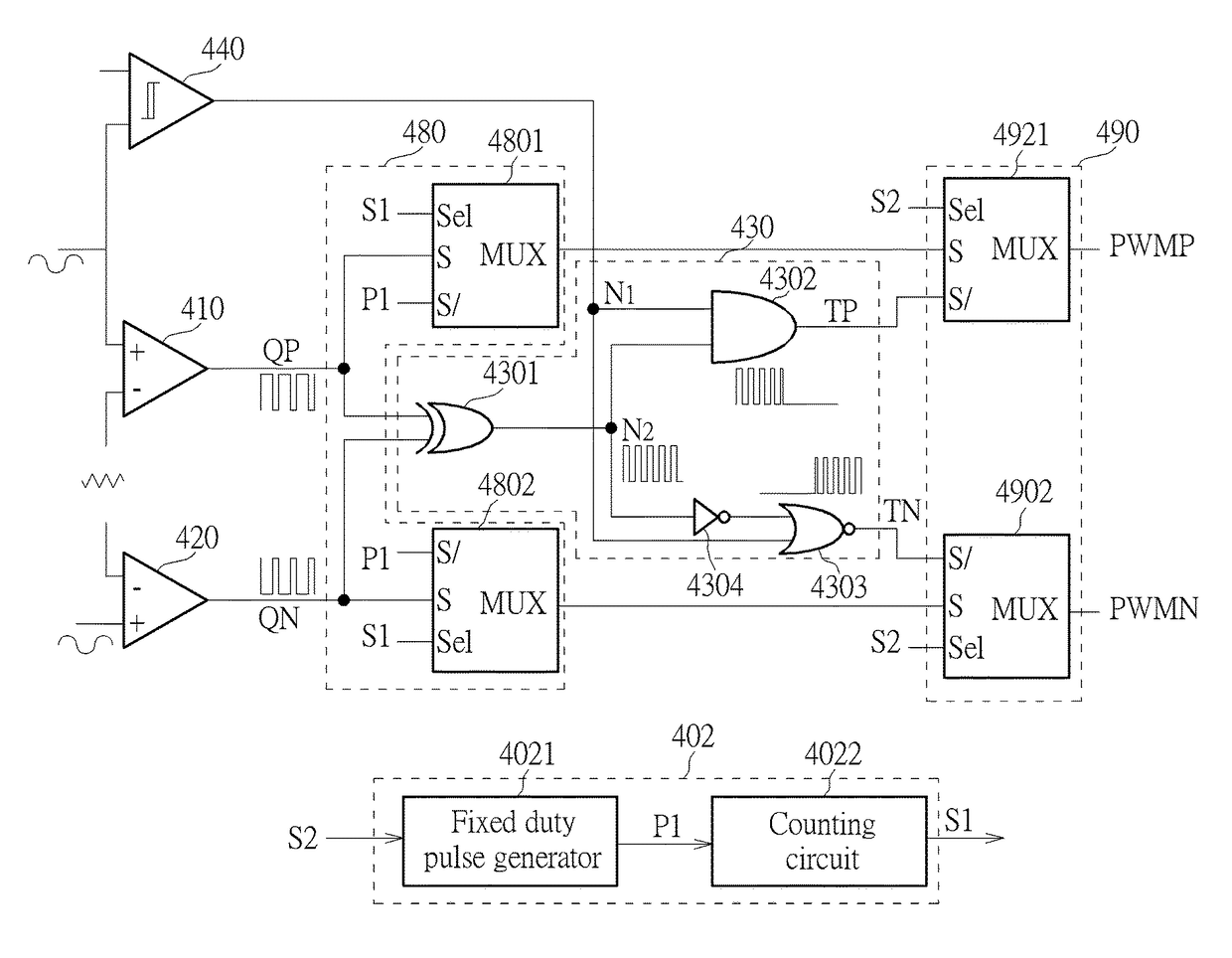

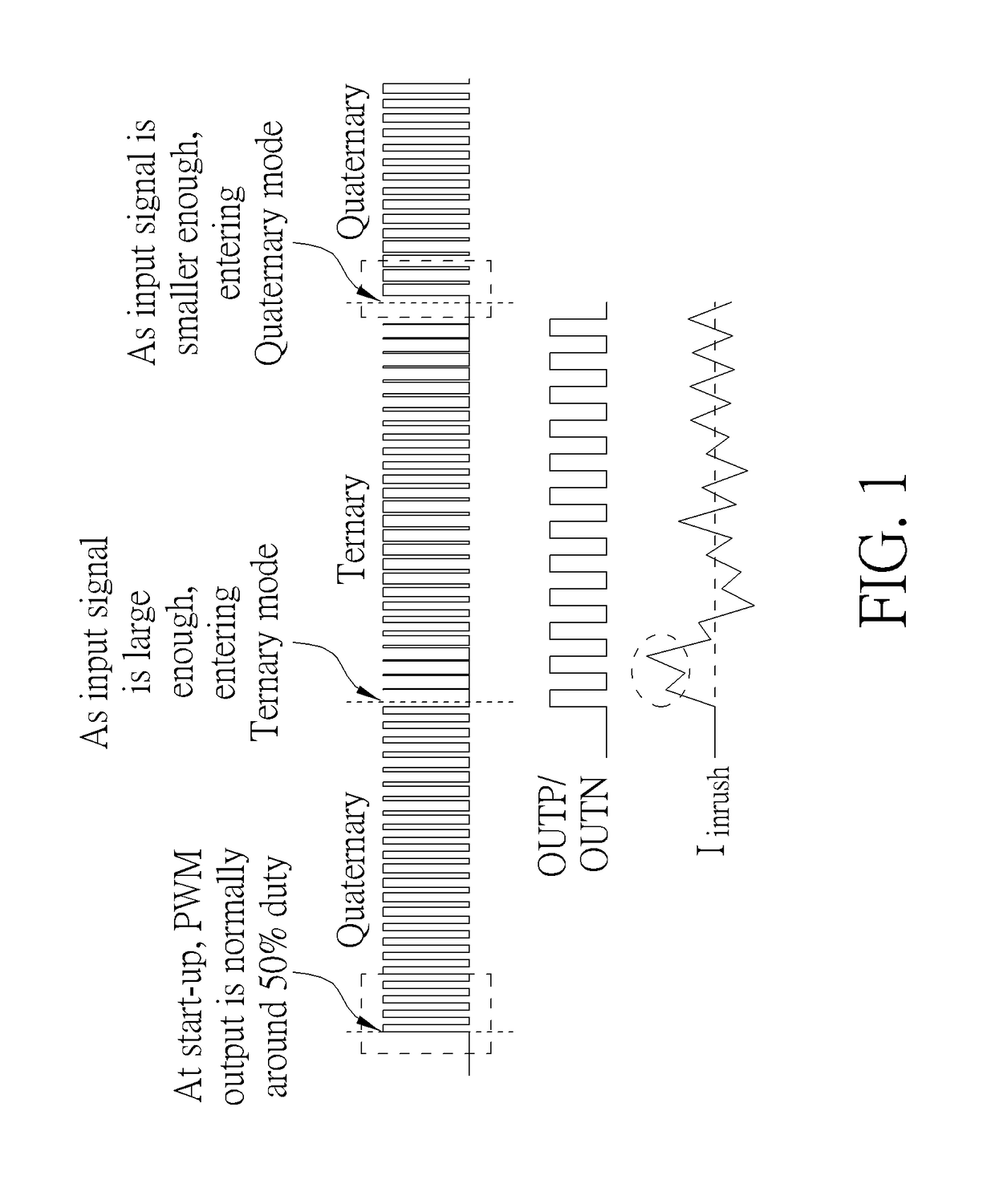

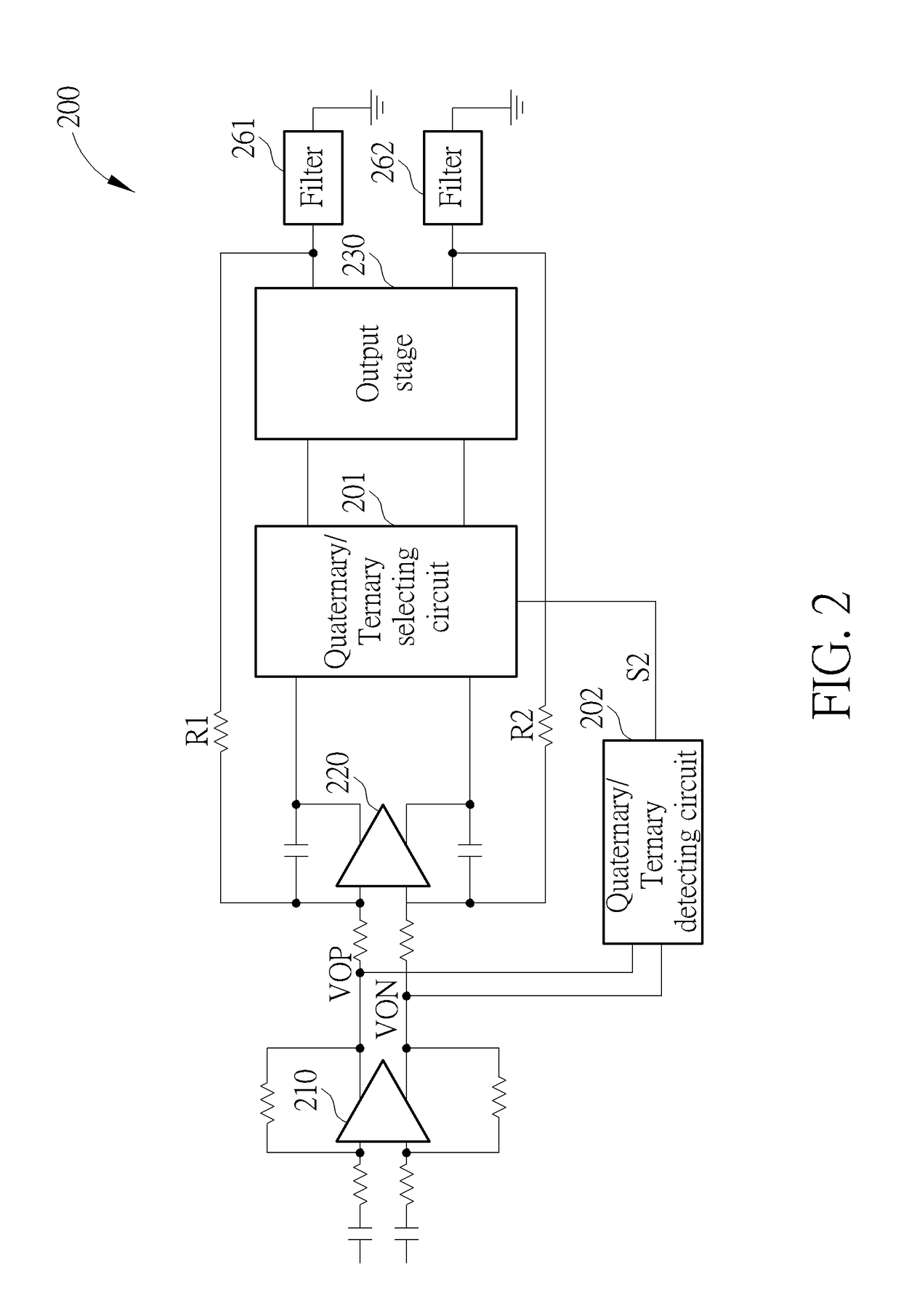

Quaternary/ternary modulation selecting circuit and associated method

A quaternary / ternary modulation selecting method of an audio amplifier includes: generating a ternary signal and a quaternary signal; generating a plurality of pulses with limited duty cycles; and selecting one of the quaternary signal, the ternary signal and the plurality of pulses for an output stage of the audio amplifier.

Owner:ELITE SEMICON MEMORY TECH INC

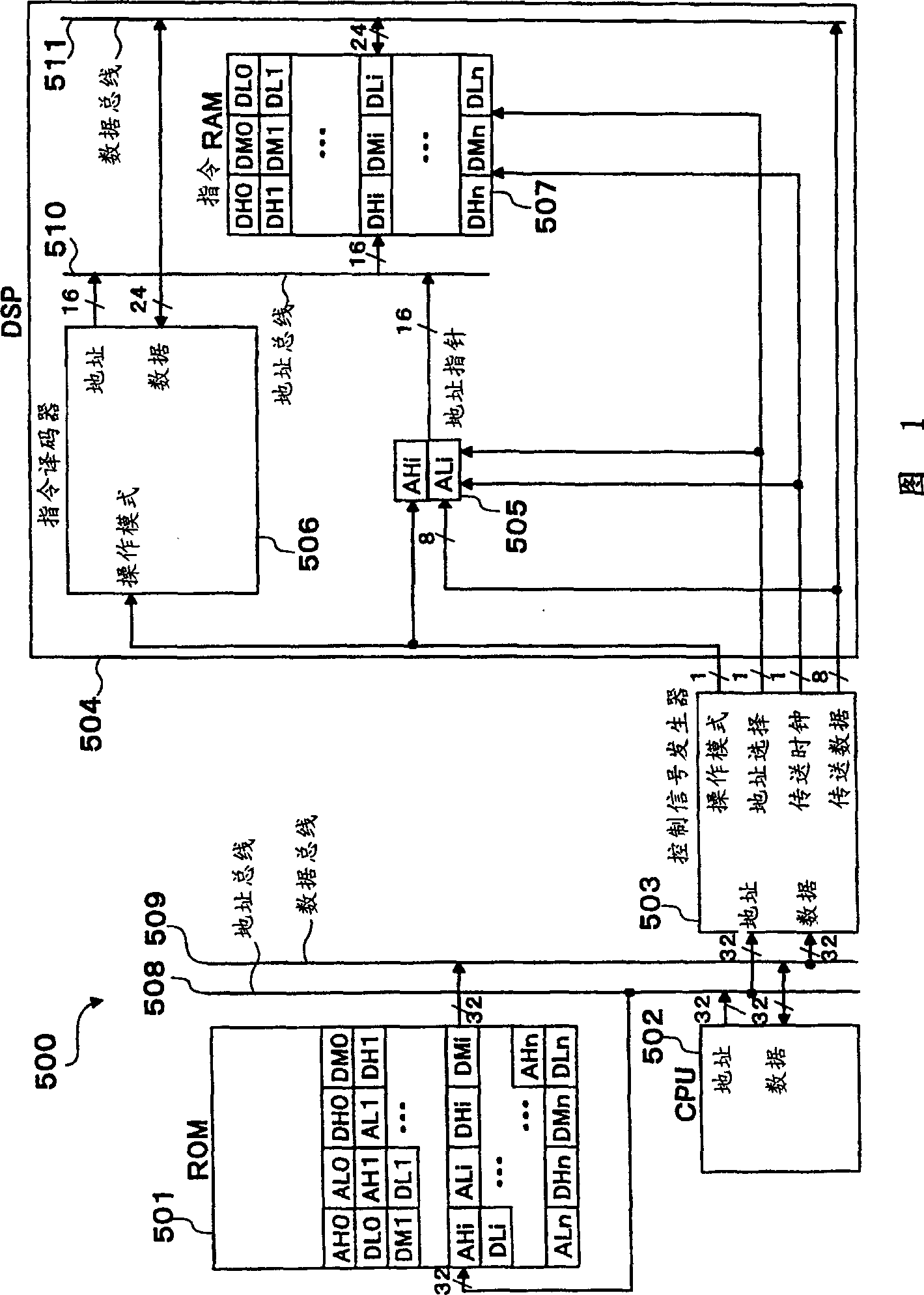

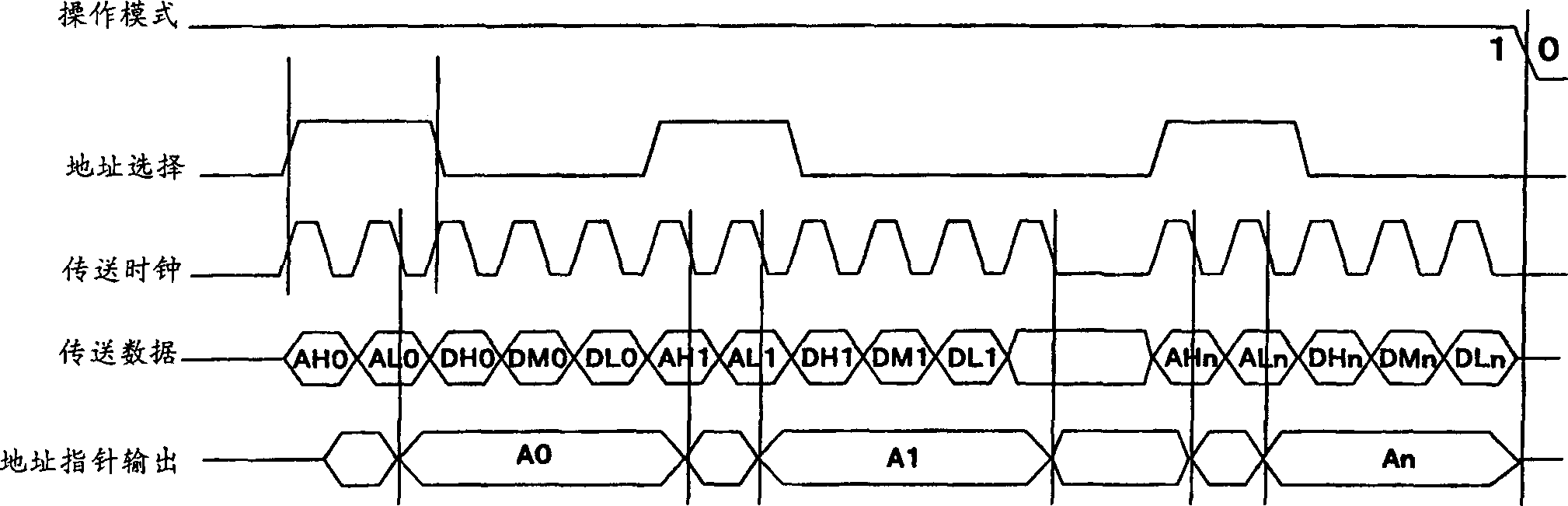

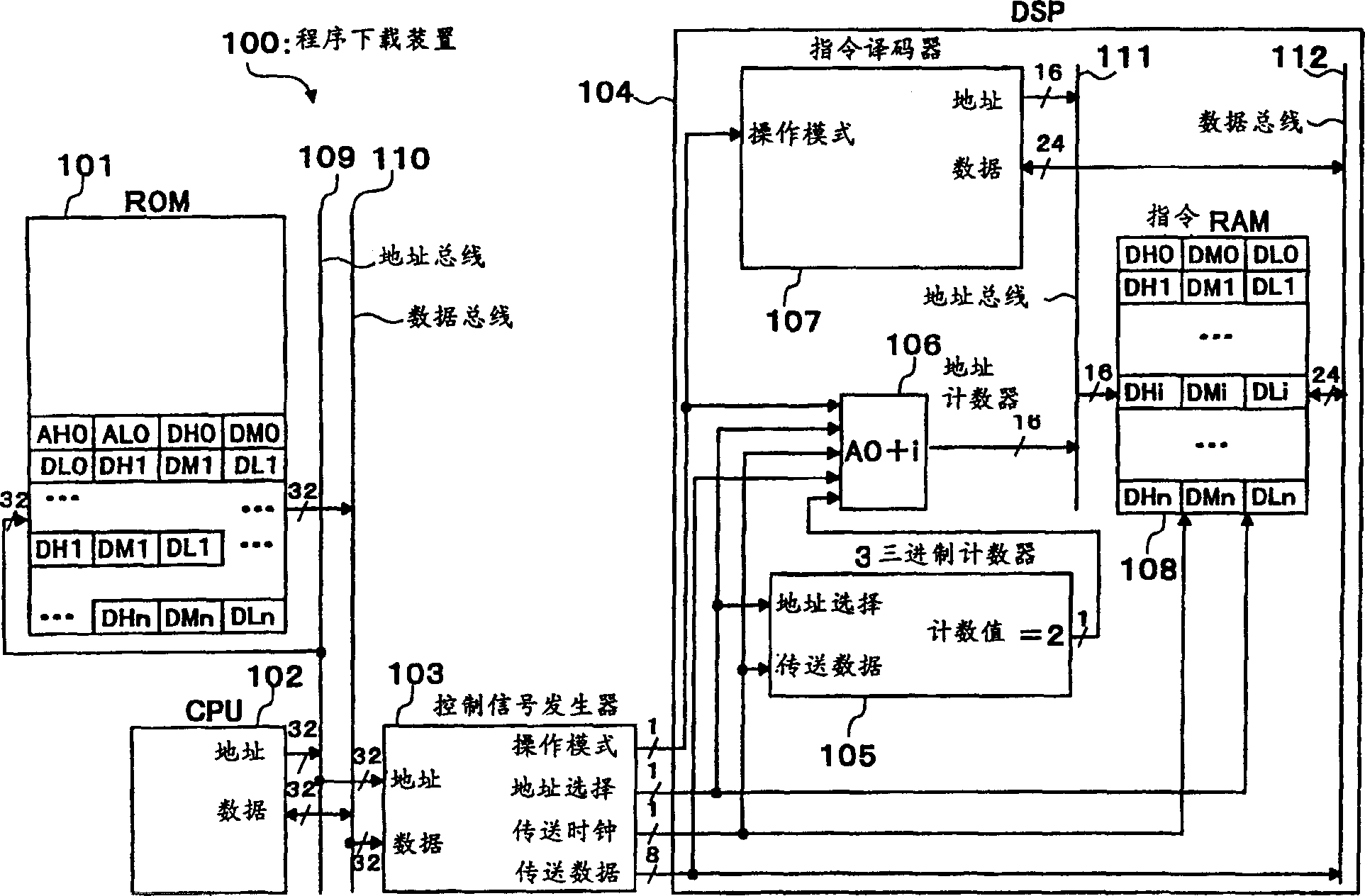

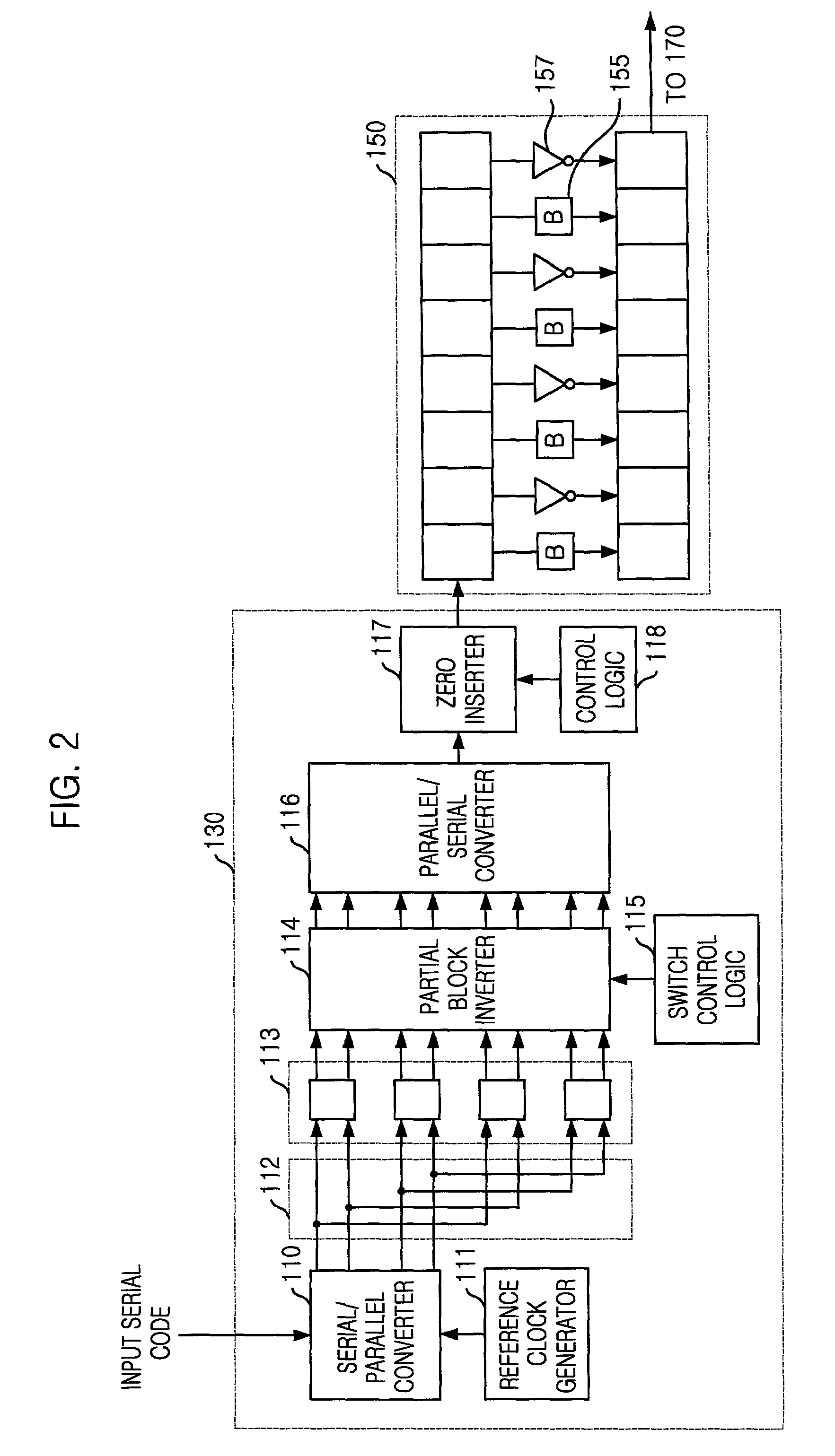

Program downloading device and program downloading method

InactiveCN1302402AReduce Program MemoryProgram download time suppressionLink editingProgram loading/initiatingControl signalByte

When a CPU (102) with a control signal generating unit (103) stores the program and address initial values 'AHO' and 'ALO' of a DSP (104) in a ROM (101) and transfers the program to an instruction RAM (108) of the DSP (104) with the stored address intial value placed at its first position, a ternary counter (105) which counts several times according to the data length (for instance, 3 bytes) of the instruction RAM (108) carries out counting in accordance with the clock signal generated by the control signal generating unit (103). After an address counter (106) is loaded with the address initial value of the ROM (101), the address counter (106) increases the address value every count-up of the ternary counter (105) and outputs the address value to the instruction RAM (108).

Owner:PANASONIC CORP

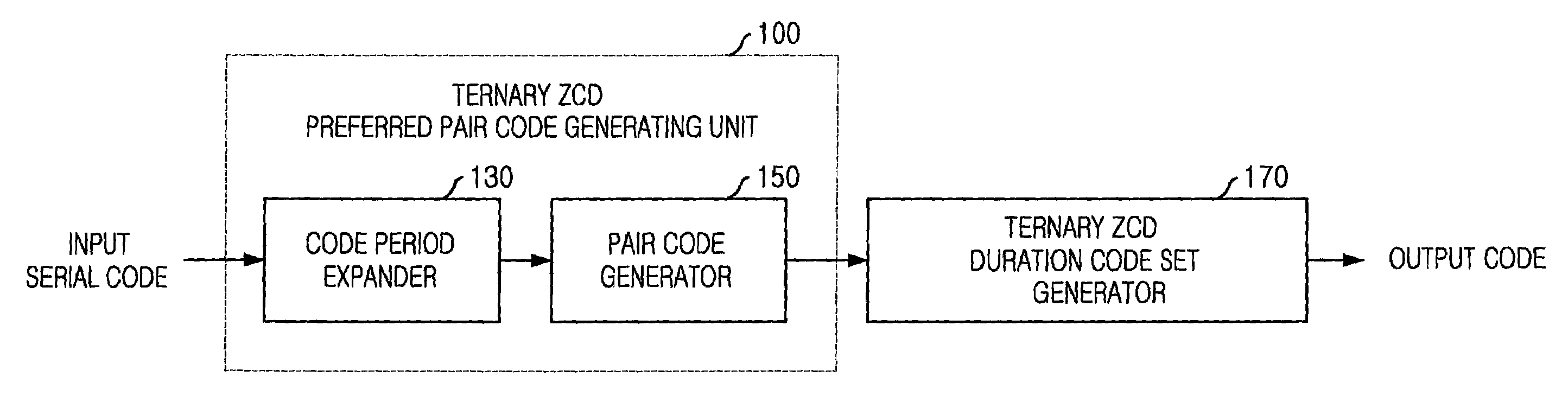

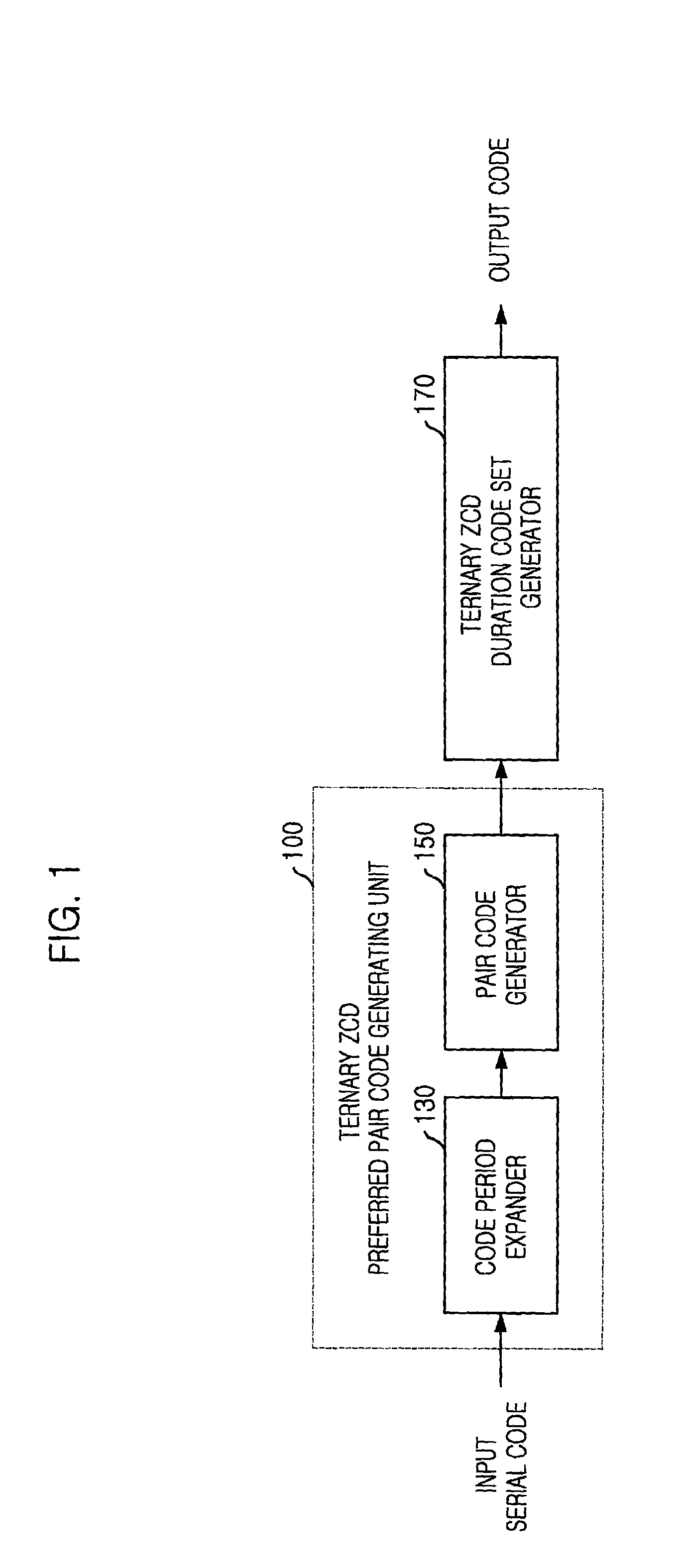

Apparatus for generating ternary spreading codes with zero correlation duration and method therefor

Ternary spreading codes in which side lobes near a peak of auth-correlation and cross-correlation are zero for a duration equal to or less than (0.75N+1) chips for a N chip period code are generated. The ternary spreading codes of the present invention is generated by (a) generating ternary zero correlation duration preferred pair codes, in which the zero correlation duration of (0.75N+1) chips is retained, by expanding a N chip period of a code, N being a natural number; and (b) generating a plurality of ternary zero correlation duration code sets having zero correlation characteristic equal to or less than (0.75N+1) chips by shifting the generated ternary zero correlation duration preferred pair codes in chips.

Owner:ELECTRONICS & TELECOMM RES INST

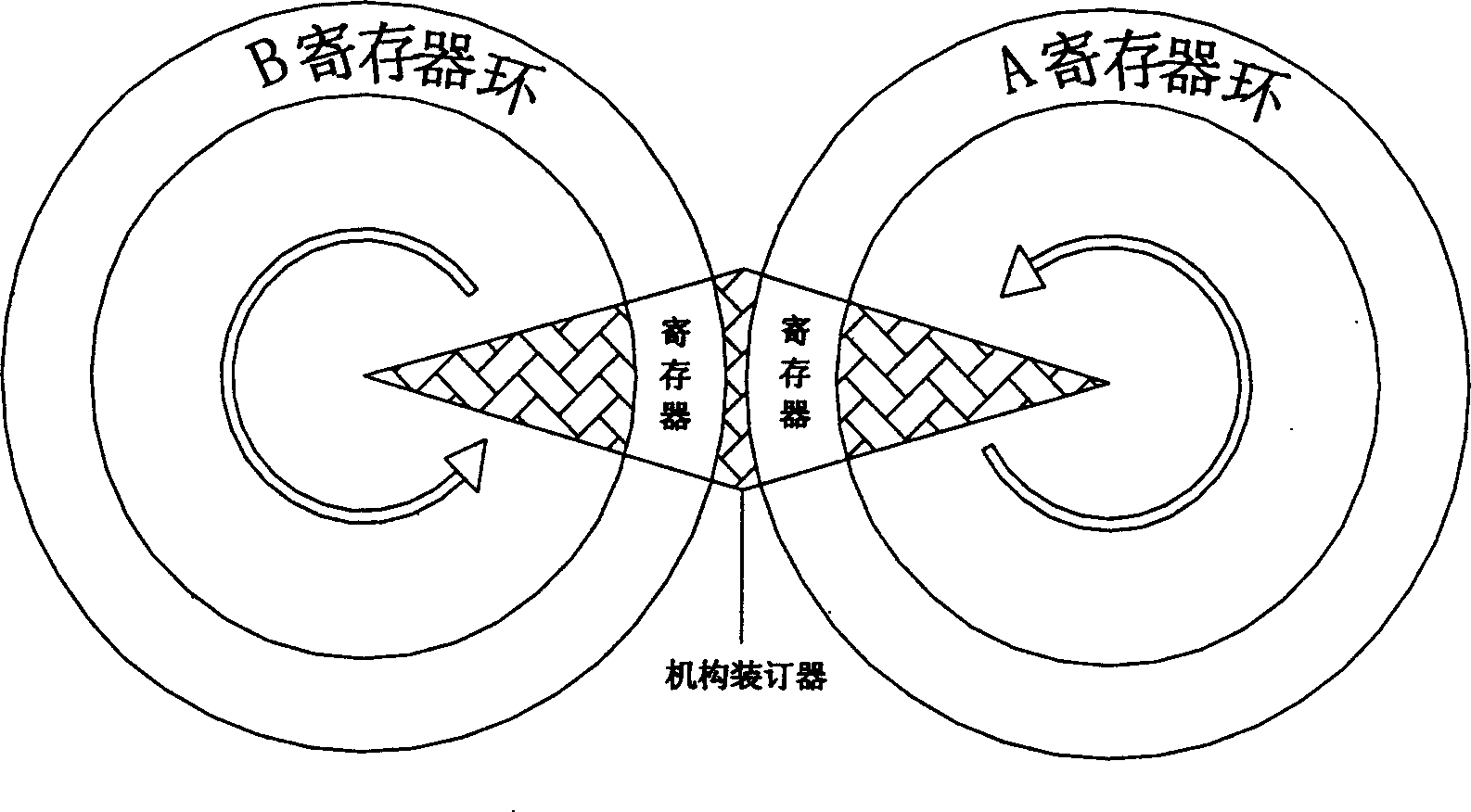

Cipher mechanical solidifying method used for important system safety guaranted

InactiveCN1556514ARealize positive code conductionRealize functionCoding/ciphering apparatusProcessor registerComputer science

The invention relates to a cipher mechanical solidifying and checking method used for safety assurance of a high-consequence system, including the steps: 1, constructing a cipher mechanism virtual machine; 2, starting up and running the virtual machine to reduplicatively execute mechanical solidification; 3, regulating and recording ternary numerical values of registers installed on the register rings at all layers; 4, according to the ternary numerical values, completing the mechanical solidification of the cipher in layers; where the cipher is a group of A and B combinations, representing the movements of gear sets A and B, respectively. It can conveniently implement multilayer and multitooth-bit mechanical solidification of an arbitrary cipher, implement the functions of correct-code turn-on and code-error instantly locking for an arbitrary cipher, and be used in safety assurance of a high-consequence system.

Owner:SHANGHAI JIAO TONG UNIV