Power consumption optimizing method for RM (Reed-Muller) logical circuit comprising irrelevant items

A logic circuit and optimization method technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problem of RM logic circuit power consumption optimization, etc., to achieve obvious advantages, speed up the convergence speed, and reduce the search space Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

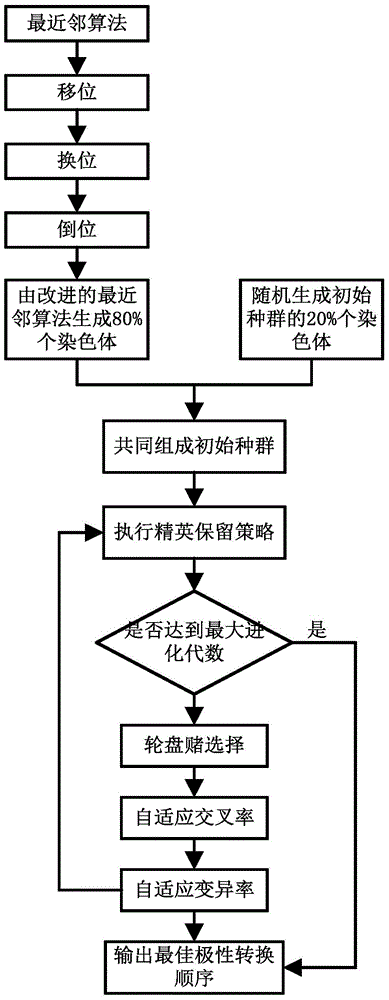

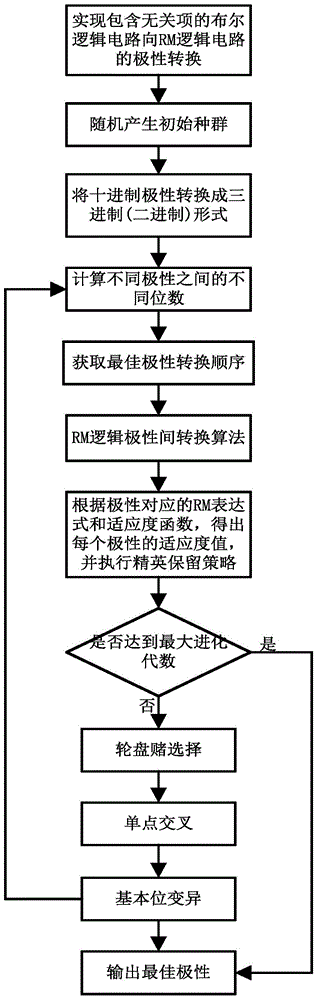

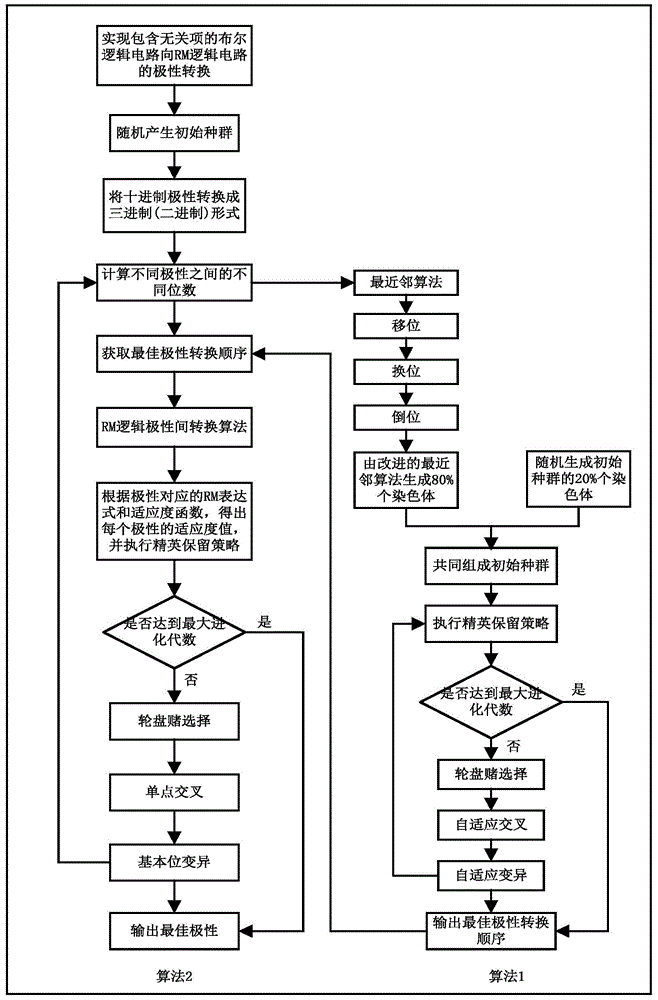

[0042] according to figure 1 , figure 2 and image 3 Shown, the specific embodiment of the present invention is as follows:

[0043] In the present invention, the RM logic circuit power consumption optimization comprising irrelevant items is mainly composed of figure 1 and figure 2 The two-part algorithm shown is Algorithm 1 and Algorithm 2, figure 1 In order to use the improved adaptive genetic algorithm to solve the optimal polarity switching order of the polarity set to be evaluated in each generation, figure 2 Optimal polarity for searching RM logic circuits containing irrelevant terms;

[0044] in, figure 1 and figure 2 The main implementation steps of the shown algorithm are as follows:

[0045] Step 1: Realize the polarity conversion from a Boolean logic circuit containing irrelevant items to an RM logic circuit;

[0046] Step 2: Generate randomly figure 2 The initial population of genetic algorithm in, wherein, described initial population is the polarit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More