Patents

Literature

126 results about "Macro instruction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A Macro instruction is a line of computer program coding that results in one or more lines of program coding in the target programming language, sets variables for use by other statements, etc.. In the mid-1950s, when assembly language programming was commonly used to write programs for digital computers, the use of macro instructions was initiated for two main purposes: to reduce the amount of program coding that had to be written by generating several assembly language statements from one macro instruction and to enforce program writing standards, e.g. specifying input/output commands in standard ways. Macro instructions were effectively a middle step between assembly language programming and the high-level programming languages that followed, such as FORTRAN and COBOL. Two of the earliest programming installations to develop "macro languages" for the IBM 705 computer were at Dow Chemical Corp. in Delaware and the Air Material Command, Ballistics Missile Logistics Office in California.

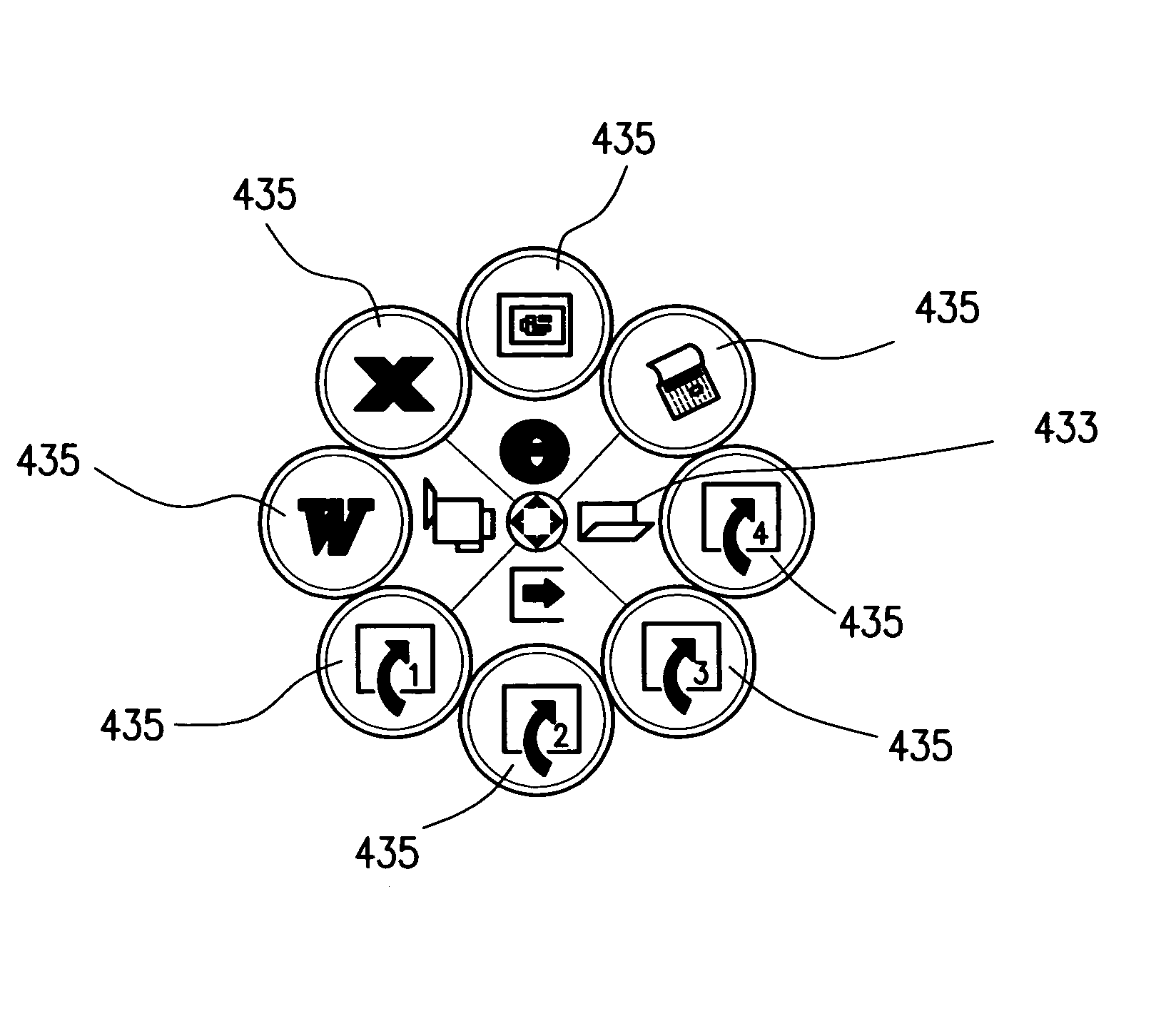

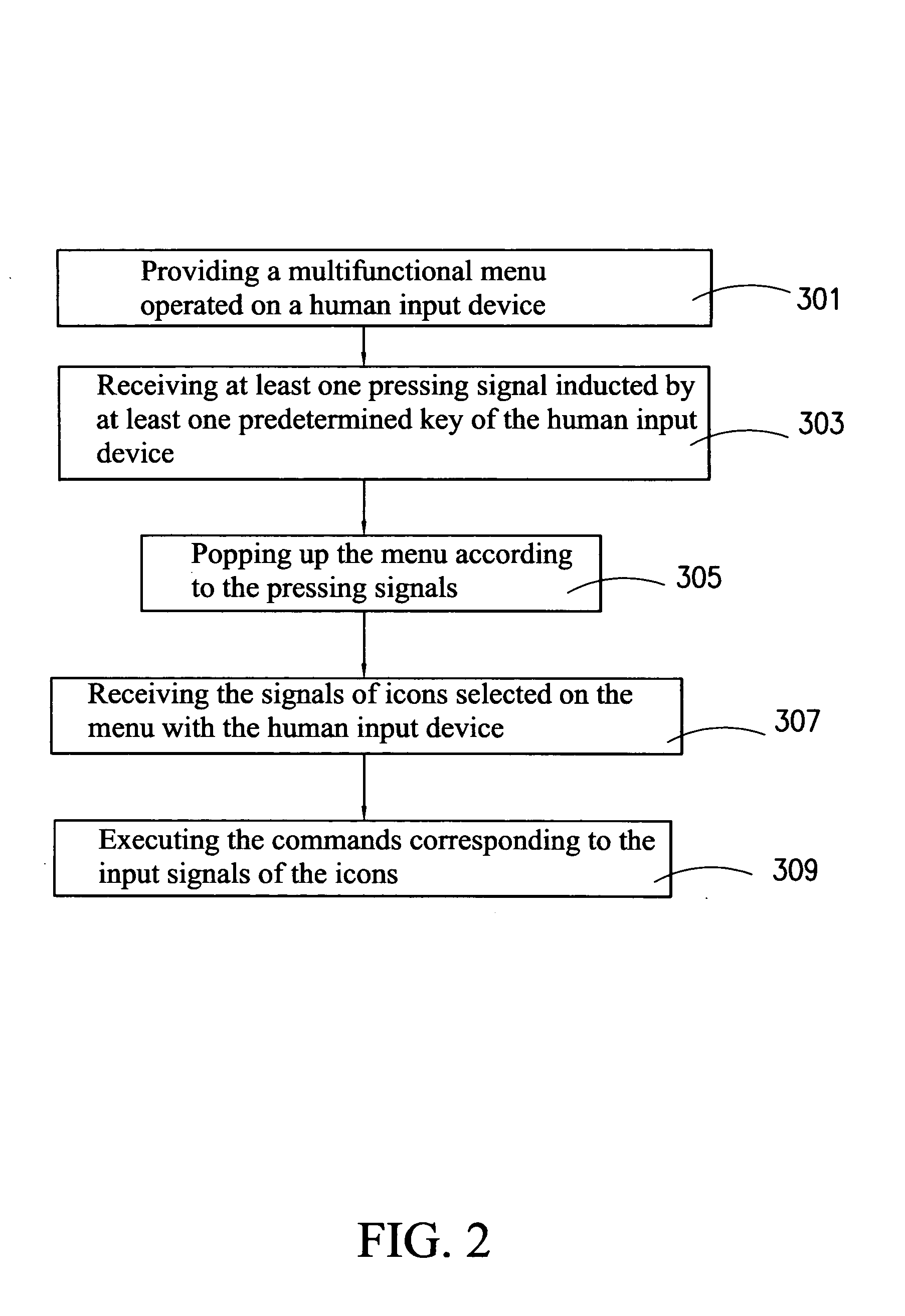

Method to process multifunctional menu and human input system

InactiveUS20050039140A1Simple and tidyIntuitive displayCathode-ray tube indicatorsInput/output processes for data processingHuman–machine interfaceOperational system

The processing method to deal with a multifunctional menu of a human input device is applied on a window operating system having plural window application programs. The menu operated on a human input device includes an auto-scroll menu to indicate scrolling function and a multifunctional menu so as to operate plural window application programs in a human interface mode. The multifunctional menu includes macro instruction icons, instruction icons corresponding to the macro instruction icons and a first switching icon for switching to the auto-scroll menu. The auto-scroll menu includes a second switching icon used on the auto-scroll menu for switching to the multifunctional menu.

Owner:BEHAVIOR TECH COMPUTER

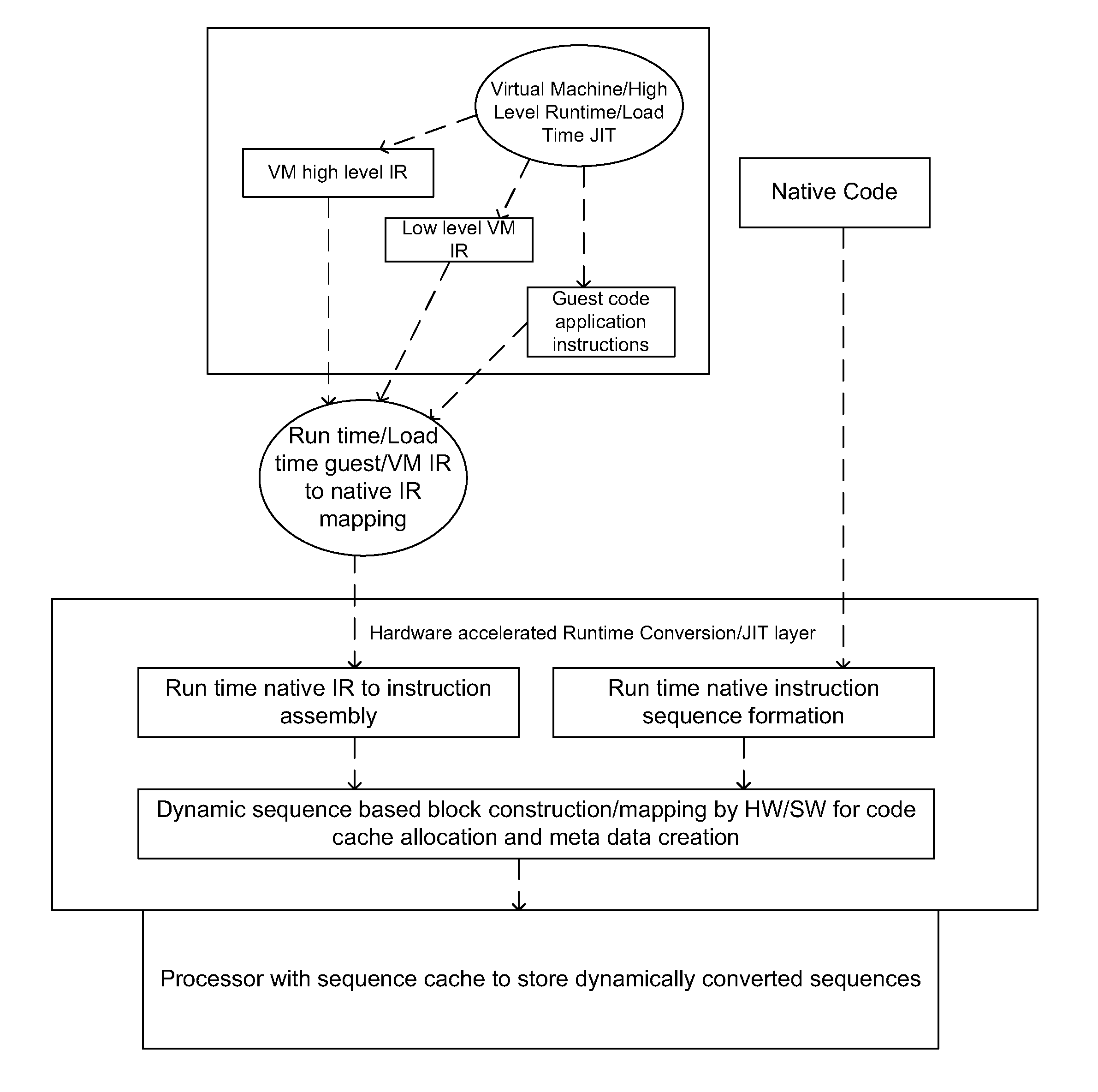

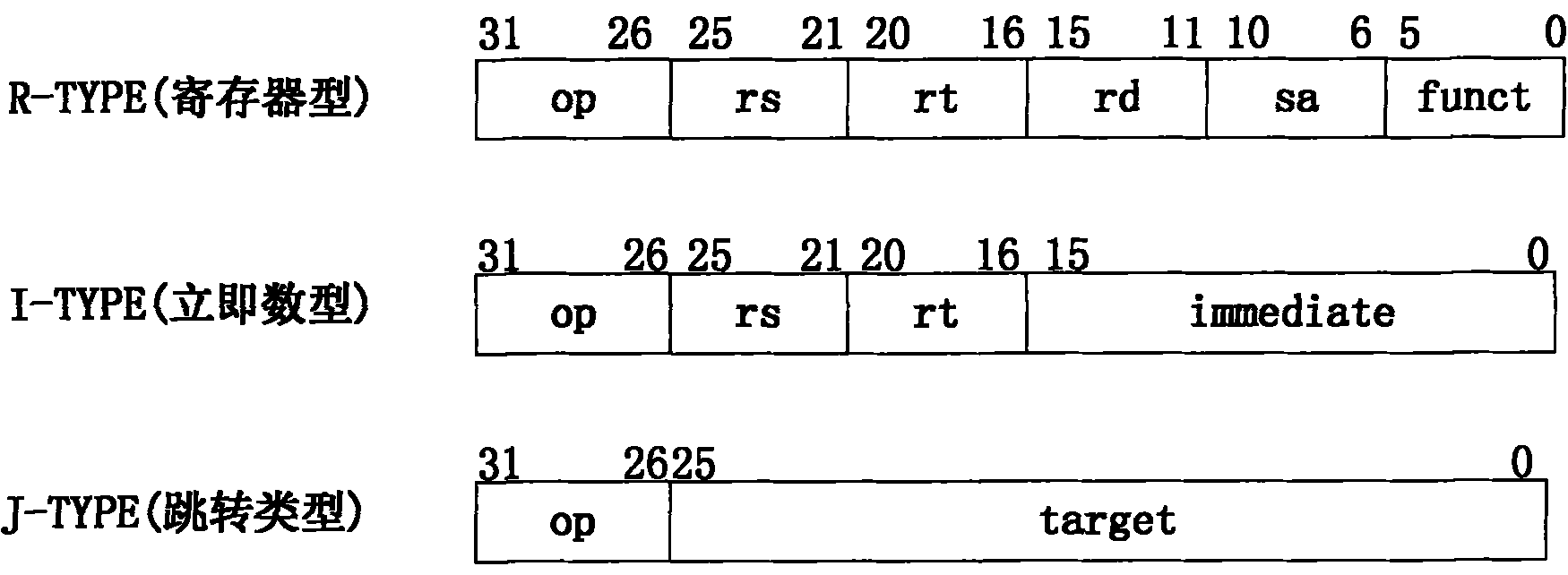

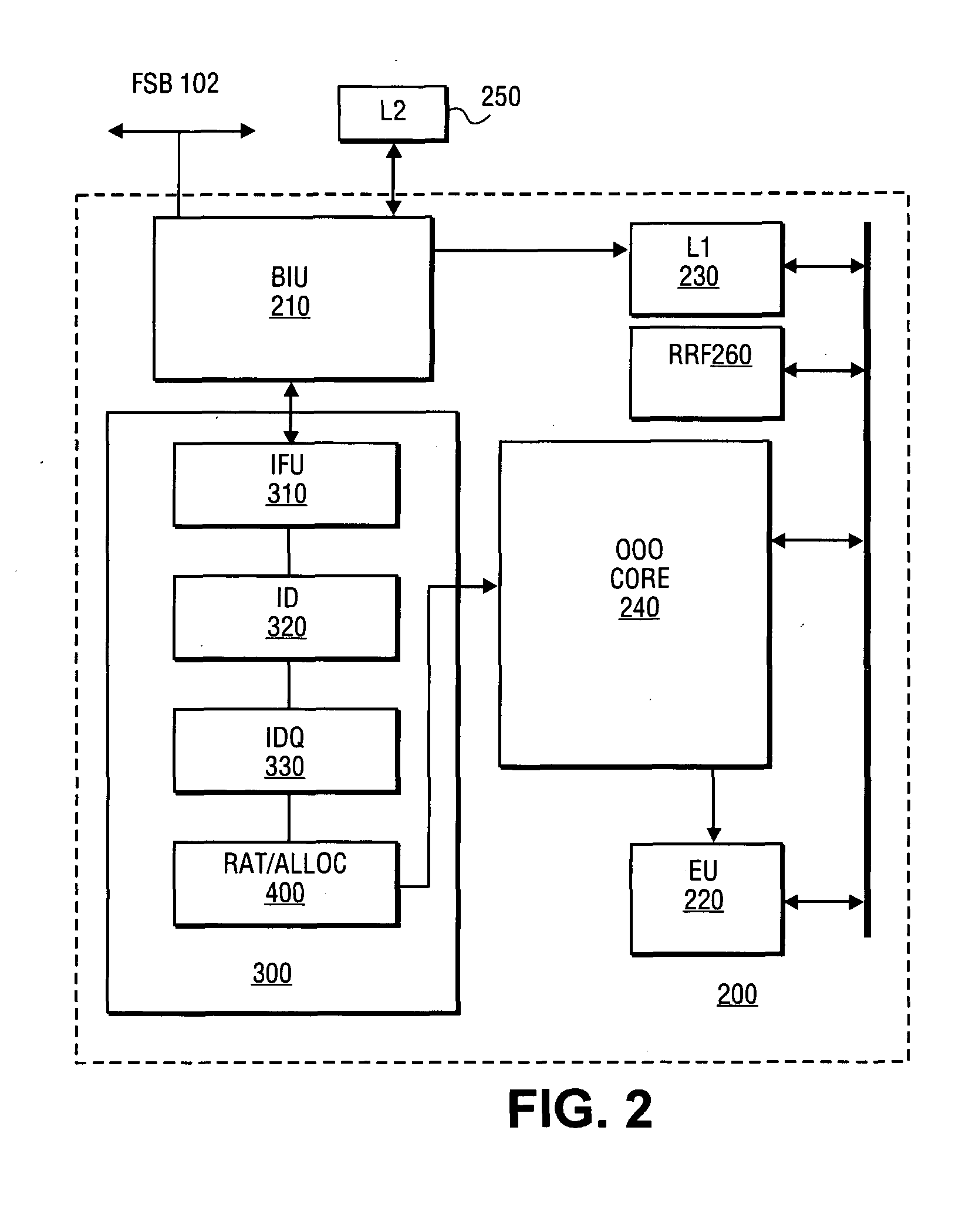

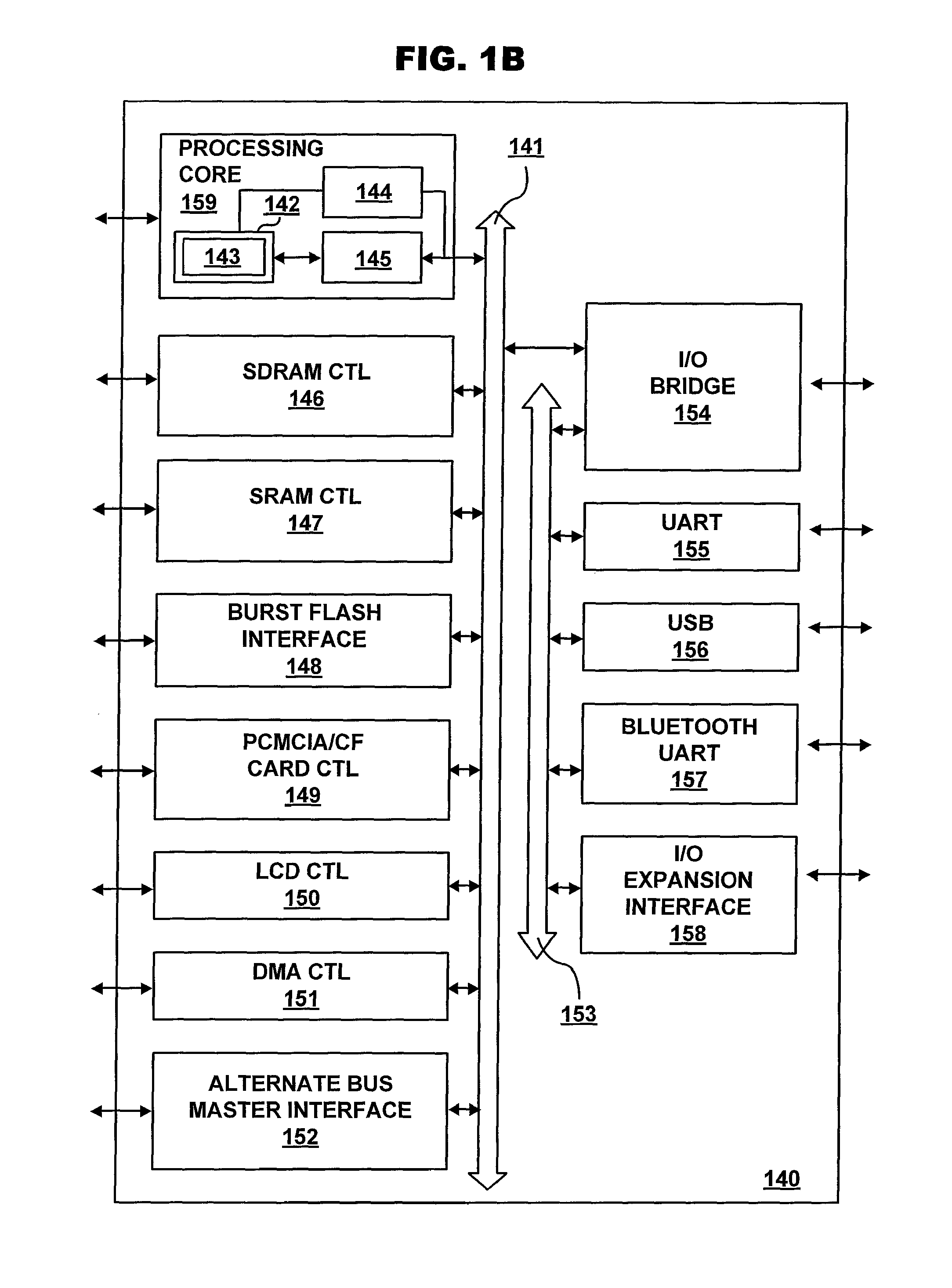

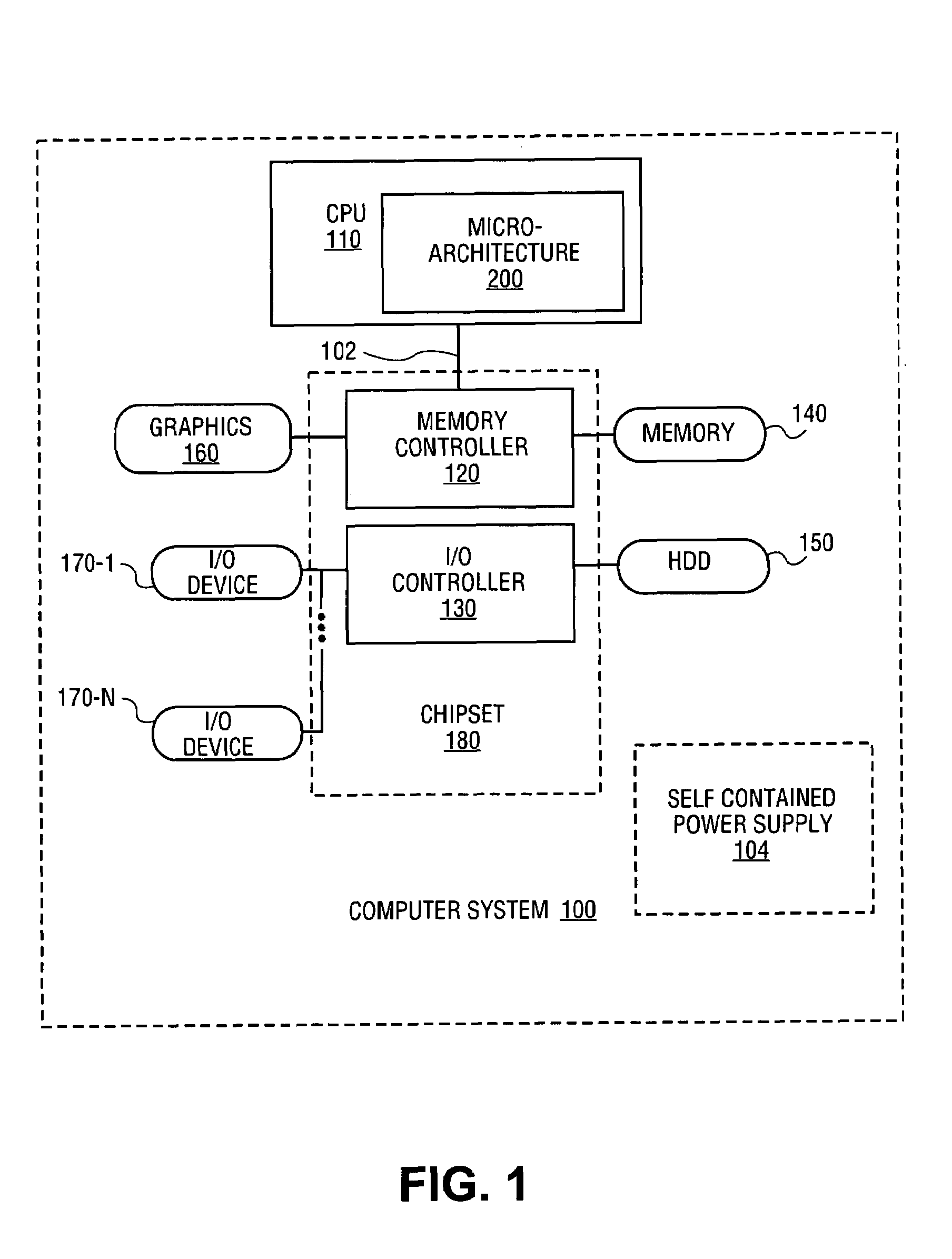

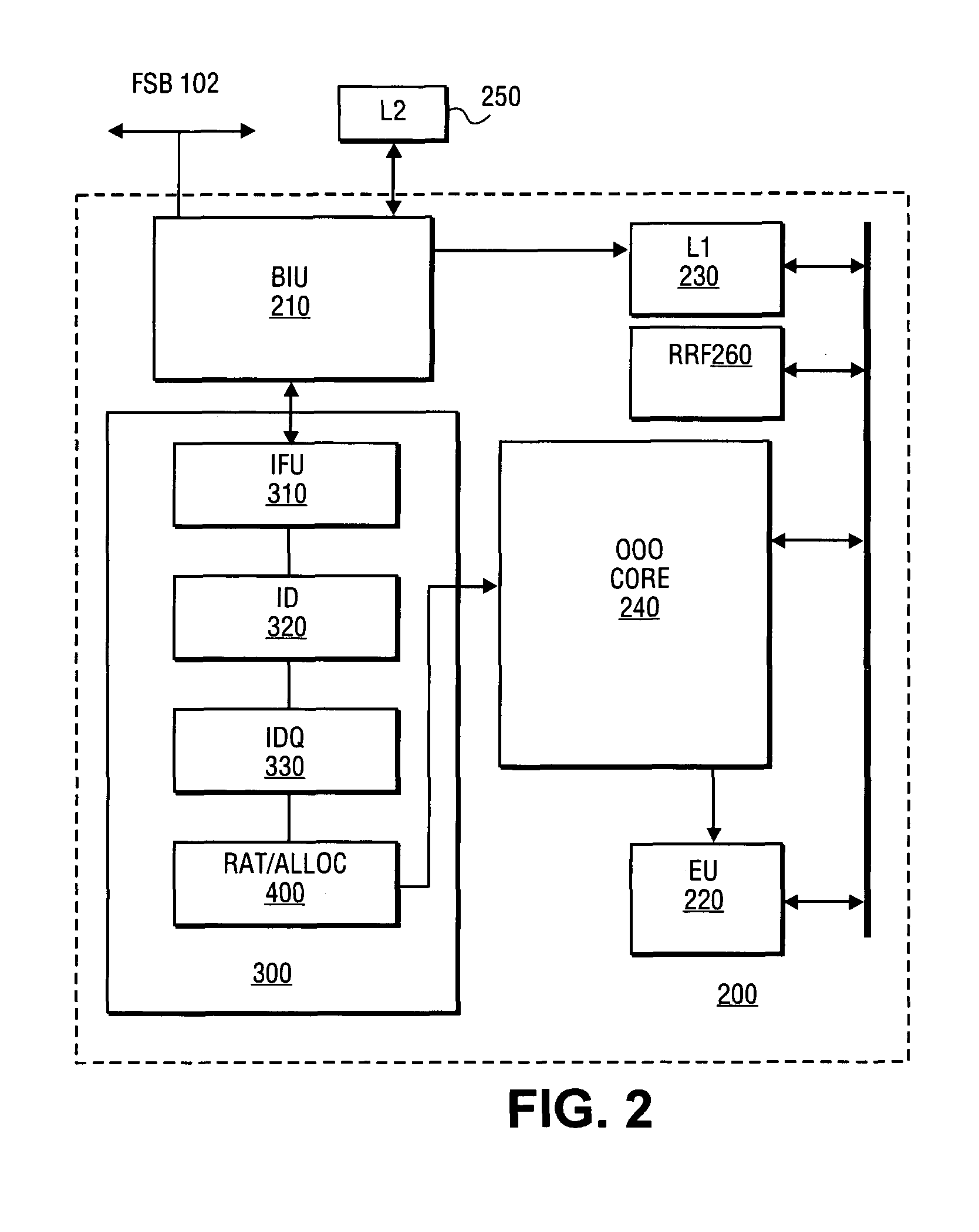

An allocation and issue stage for reordering a microinstruction sequence into an optimized microinstruction sequence to implement an instruction set agnostic runtime architecture

InactiveUS20160026486A1Concurrent instruction executionSoftware simulation/interpretation/emulationVirtualizationMacro instruction

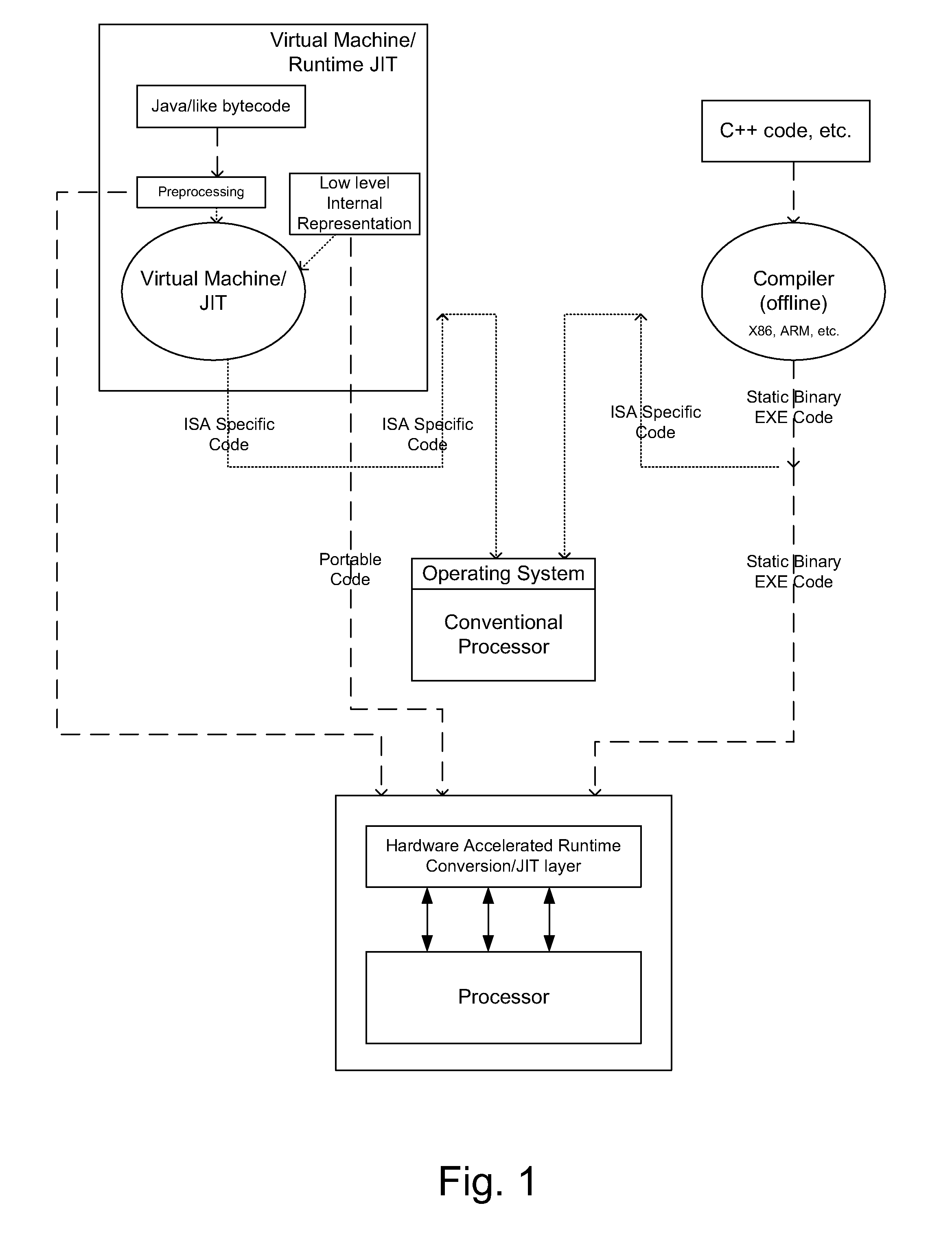

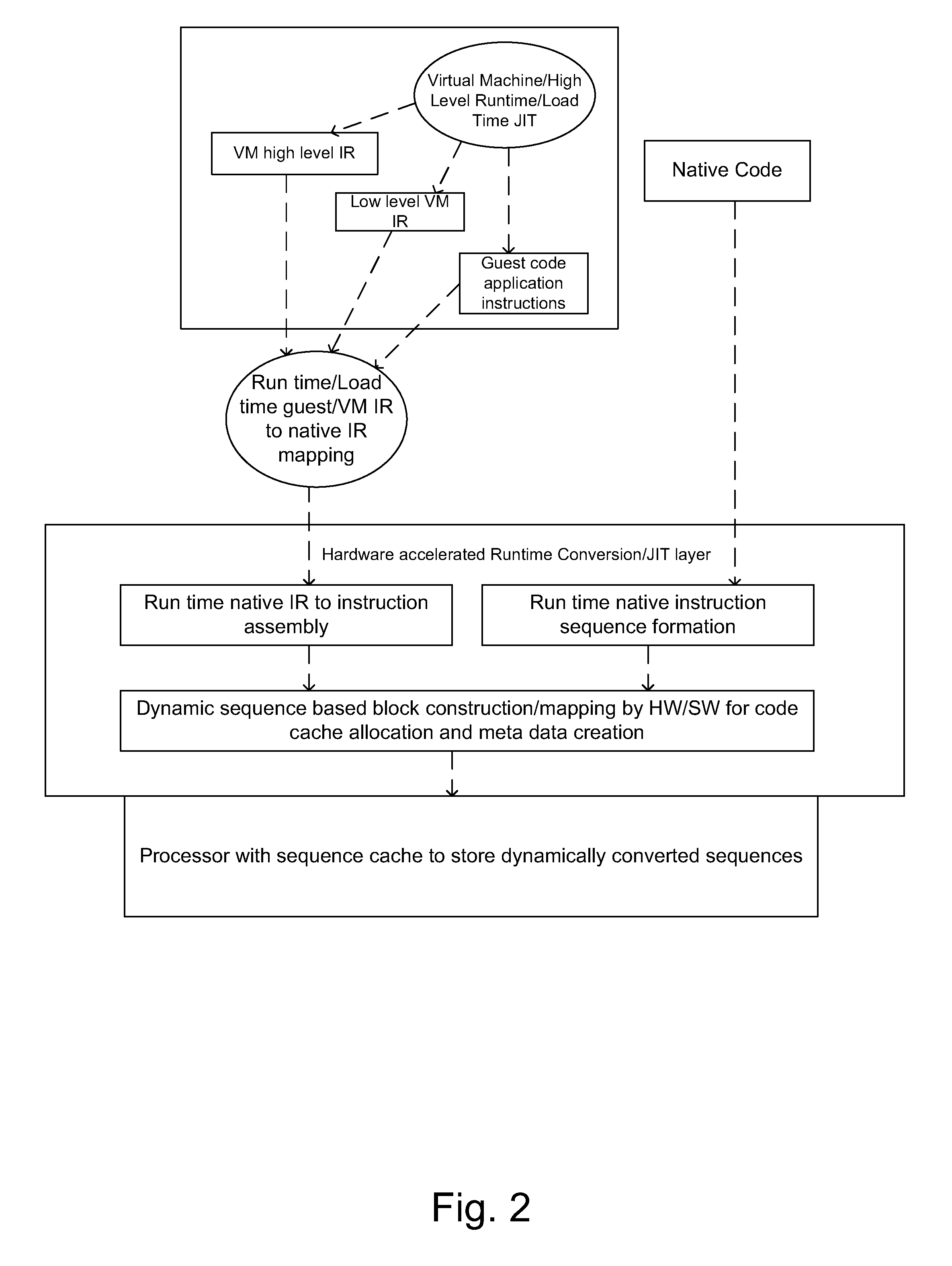

A system for an agnostic runtime architecture. The system includes a system emulation / virtualization converter, an application code converter, and a system converter wherein the system emulation / virtualization converter and the application code converter implement a system emulation process, and wherein the system converter implements a system conversion process for executing code from a guest image. The system converter further comprises an instruction fetch component for fetching an incoming microinstruction sequence, a decoding component coupled to the instruction fetch component to receive the fetched macro instruction sequence and decode into a microinstruction sequence, and an allocation and issue stage coupled to the decoding component to receive the microinstruction sequence perform optimization processing by reordering the microinstruction sequence into an optimized microinstruction sequence comprising a plurality of dependent code groups. A microprocessor pipeline is coupled to the allocation and issue stage to receive and execute the optimized microinstruction sequence. A sequence cache is coupled to the allocation and issue stage to receive and store a copy of the optimized microinstruction sequence for subsequent use upon a subsequent hit on the optimized microinstruction sequence, and a hardware component is coupled for moving instructions in the incoming microinstruction sequence.

Owner:INTEL CORP

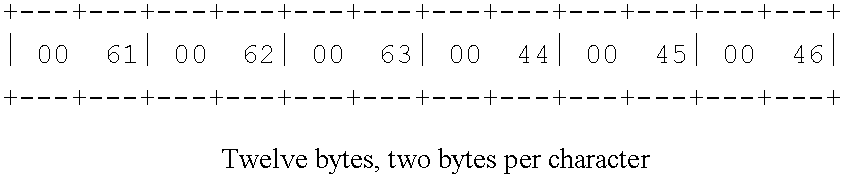

Data structure for creating, scoping, and converting to unicode data from single byte character sets, double byte character sets, or mixed character sets comprising both single byte and double byte character sets

InactiveUS6400287B1Creates delayIndividual digits conversionSpecial data processing applicationsThree levelMacro instruction

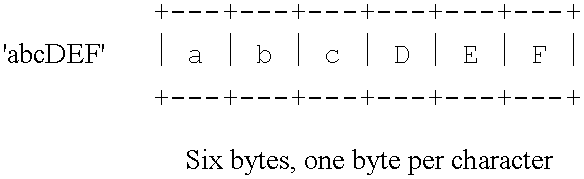

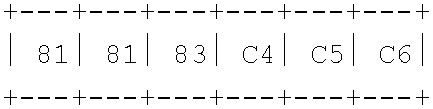

A data structure for specifying the types of constants whose character values are to be converted to Unicode; for specifying which code page or pages are used for specifying the character encodings used in the source program for writing the character strings to be converted to Unicode; and that can be used to perform conversions from SBCS, mixed SBCS / DBCS, and pure DBCS character strings to Unicode. A syntax suitable for specifying character data conversion from SBCS, mixed SBCS / DBCS, and pure DBCS representation to Unicode utilizes an extension to the conventional constant subtype notation. In converting the nominal value data to Unicode, currently relevant SBCS and DBCS code pages are used, as specified by three levels or scopes derived from either global options, from local AOPTIONS statement specifications, or from constant-specific modifiers. Global code page specifications apply to the entire source program. These global specifications allow a programmer to declare the source-program code page or code pages just once. These specifications then apply to all constants containing a request for conversion to Unicode. Local code page specifications apply to all subsequent source-program statements. These local specifications allow the programmer to create groups of statements containing Unicode conversion requests, all of which use the same code page or code pages for their source-character encodings. Code page specifications that apply to individual constants allow a detailed level of control over the source data encodings to be used for Unicode conversion. The conversion of source data to Unicode may be implemented inherently to the translator (assembler, compiler, or interpreter) wherein it recognizes and parses the complete syntax of the statement in which the constant or constants is specified, and performs the requested conversion. Alternatively, an external function may be invoked by a variety of source language syntaxes which parses as little or as much of the source statement as its implementation provides, and returns the converted value for inclusion in the generated machine language of the object program. Alternatively, the conversion may be provided by the translator's macro instruction definition facility.

Owner:IBM CORP

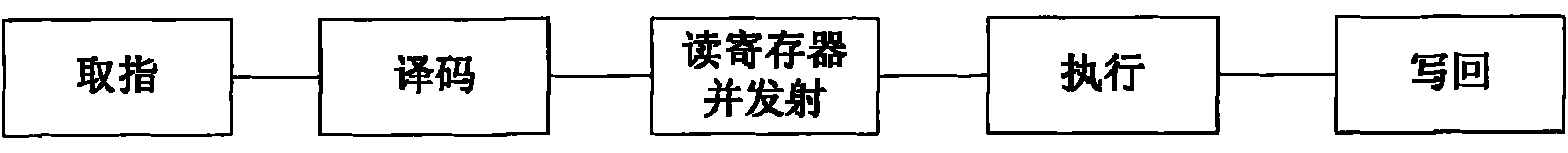

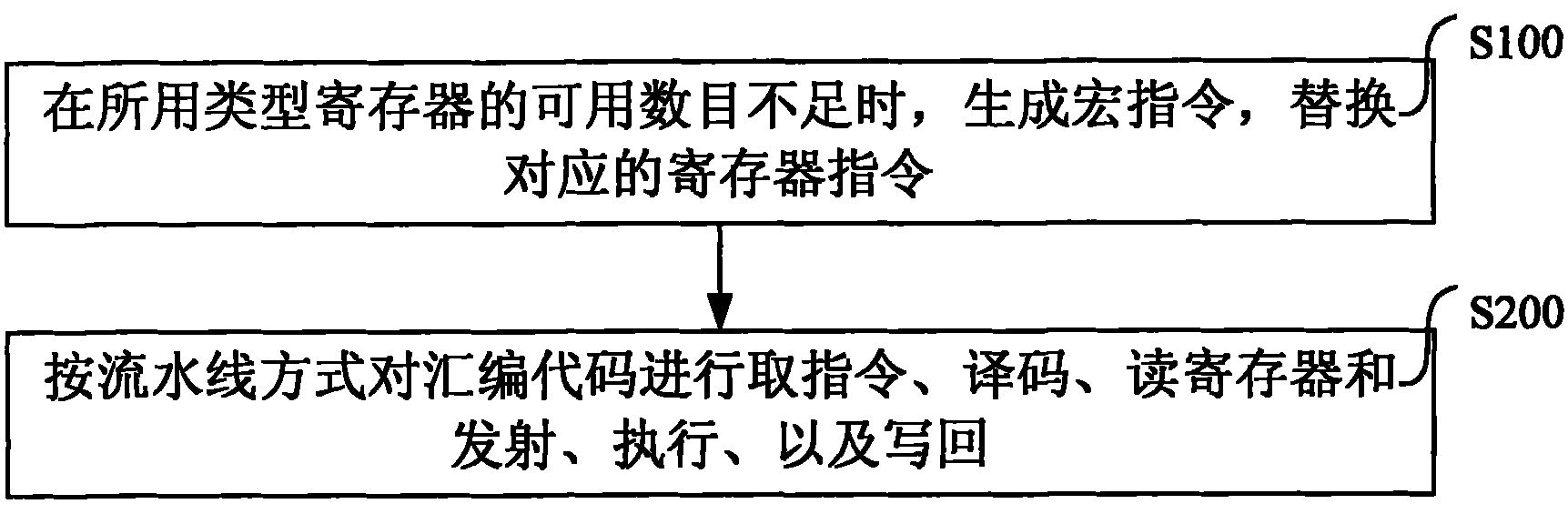

Method and system for executing register type instruction in RISC (Reduced Instruction-Set Computer) processor

ActiveCN101916180AImprove performanceEasy to implementConcurrent instruction executionProduction lineProcessor register

The invention relates to a method and a system for executing a register type instruction in a RISC (Reduced Instruction-Set Computer) processor. The method comprises the following steps of: 1. if the condition that the available number of used type registers is insufficient when a register type instruction in an assembly code is executed is discovered, generating a macroinstruction corresponding to the register type instruction and replacing the register type instruction by using the macroinstruction; 2. carrying out instruction extraction, decoding, register reading, emission, execution and back-writing on the assembly code in a production line way; when decoding, recognizing whether the current instruction is the macroinstruction or the register type instruction; as for the register type instruction, adding a mark site for indicating the operand type into a register number and generating a complete register number; and when reading the register, reading the register corresponding tothe register number in a type register file appointed by the mark site of the complete register number of the current instruction. The invention can improve the program running performance without the limitation of the number of the specific type physical registers in the processor.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

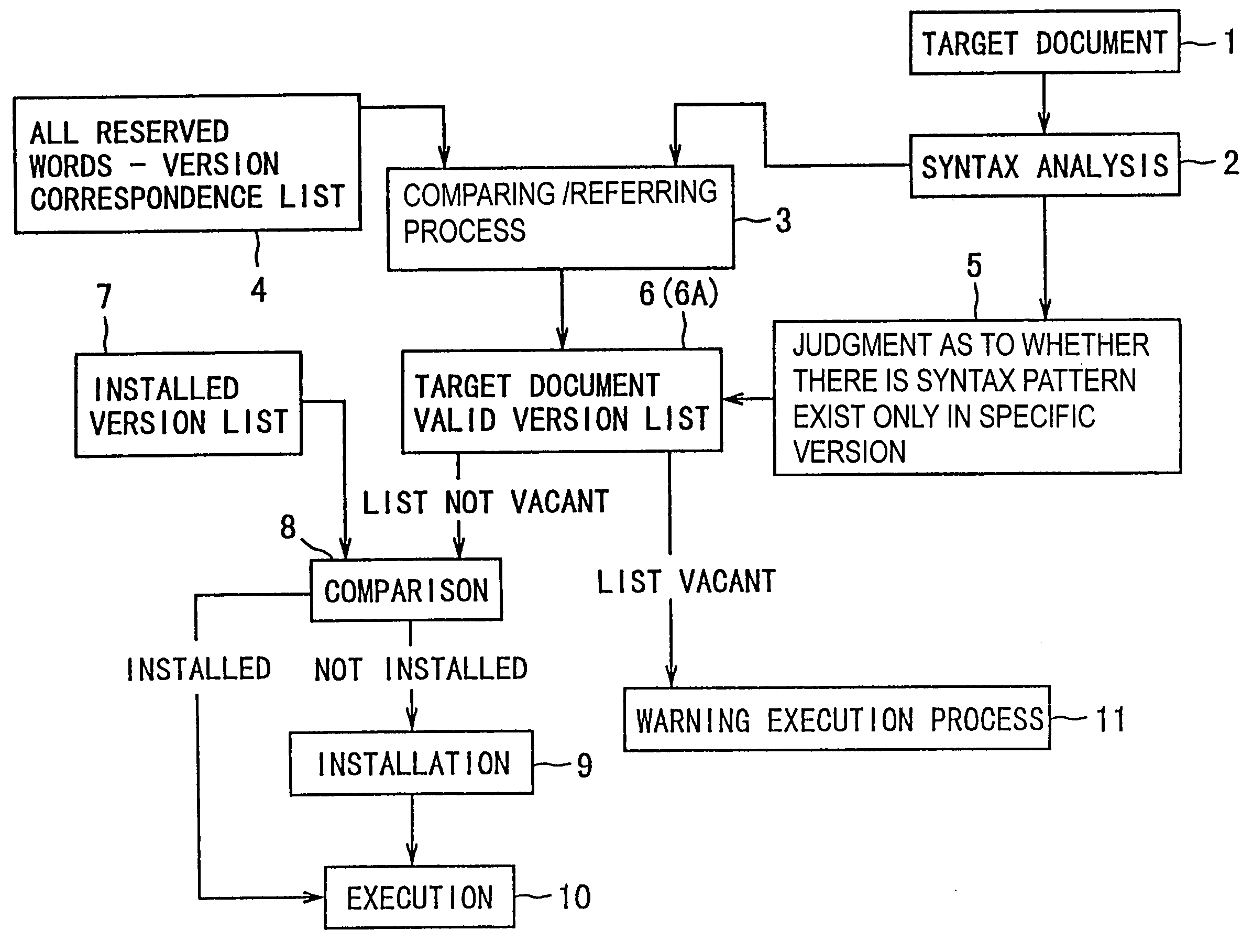

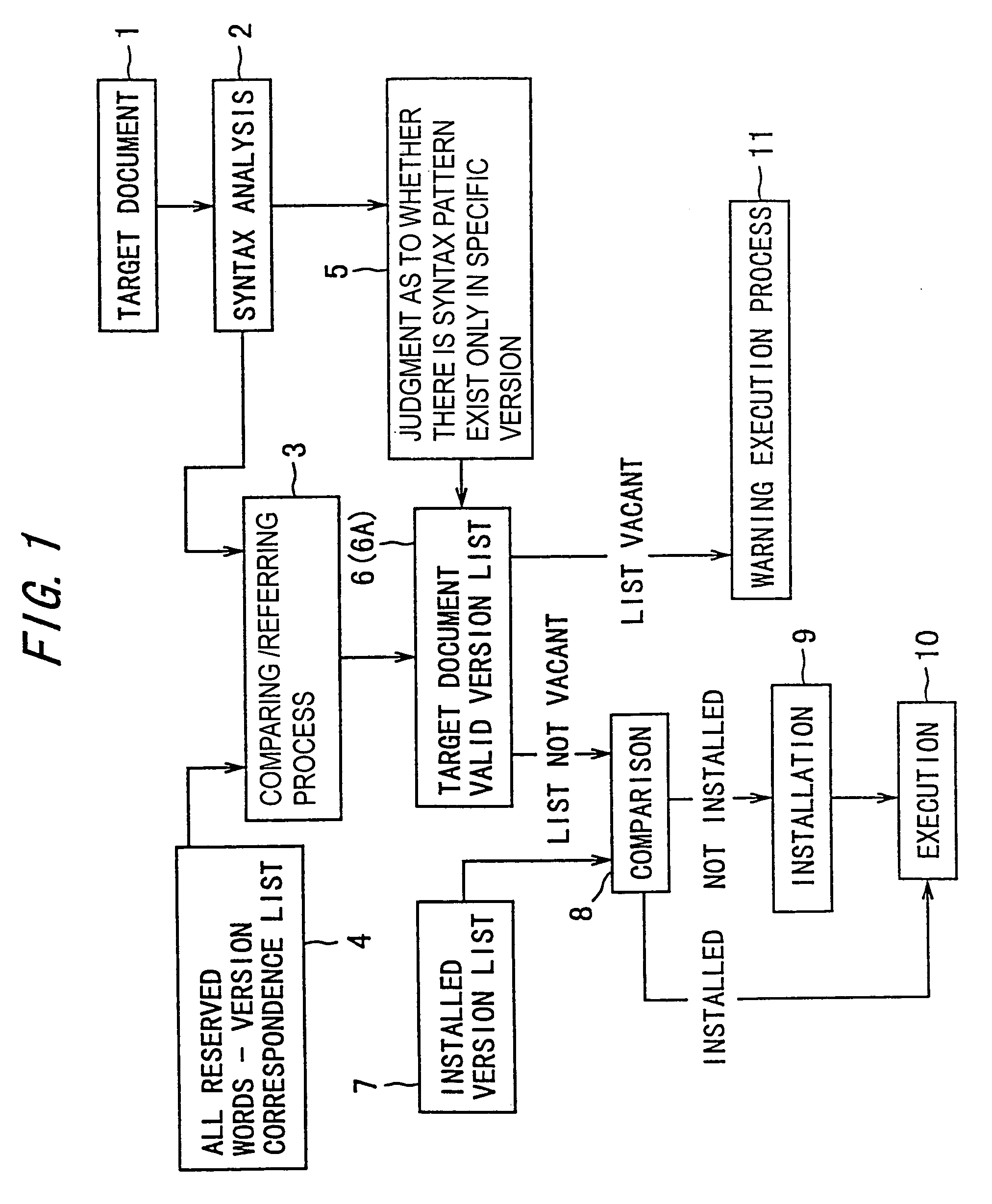

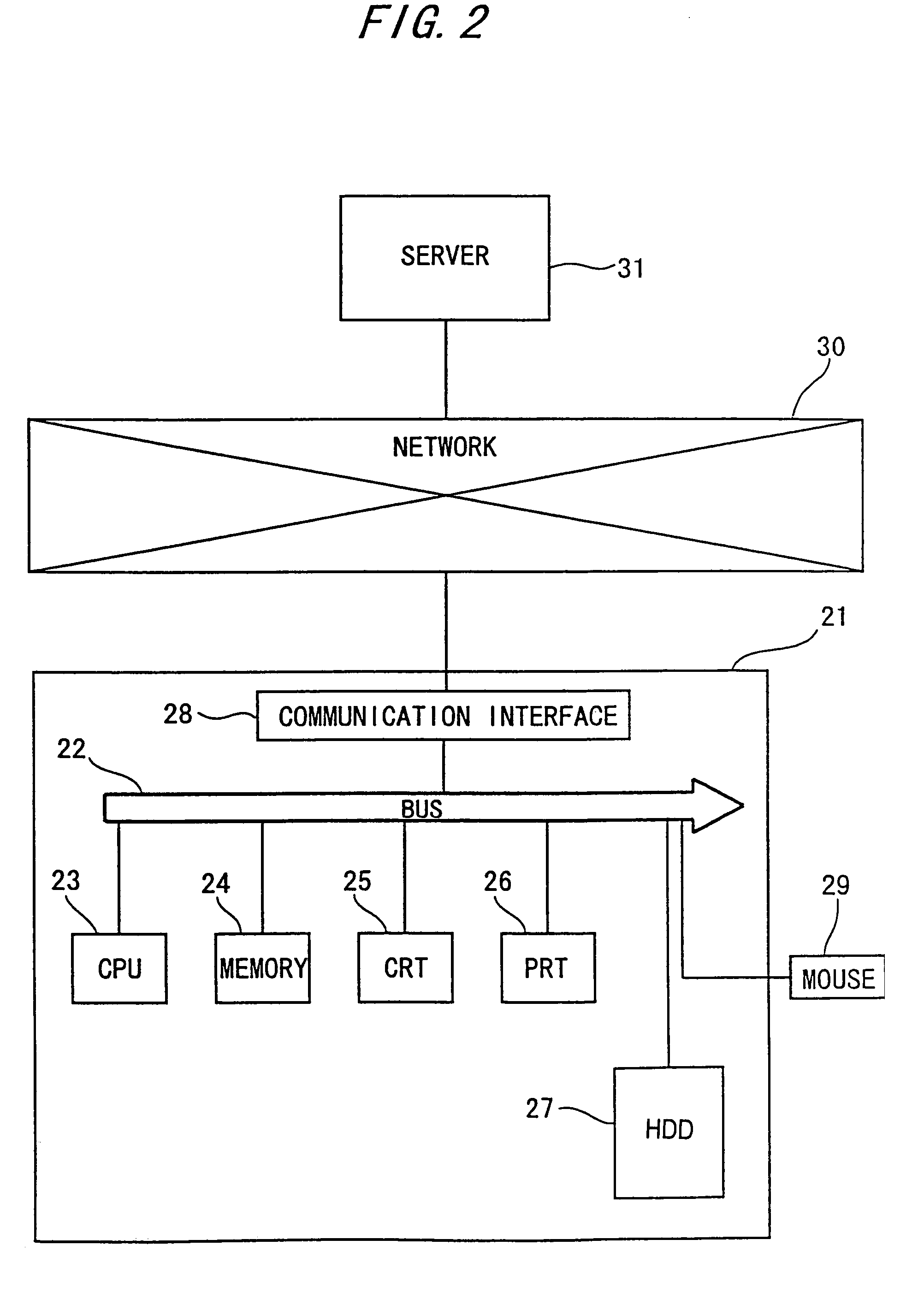

Installation method, activation method, execution apparatus and medium of application program

Without letting a user execute a cumbersome judgment of a version, an application program of the most suitable version is installed for data file automatically, thus an automatic activation of the application becomes possible. Firstly, a document file of a readout target is analyzed, a feature point as reserved word of macro instruction is extracted, and a version of an application suited for the document file is distinguished by an extracted feature point. Secondly, it is judged whether an application program of the version distinguished mentioned above is installed already. When found not being installed based on this judgment result, an application program of the version is newly installed.

Owner:FUJITSU LTD

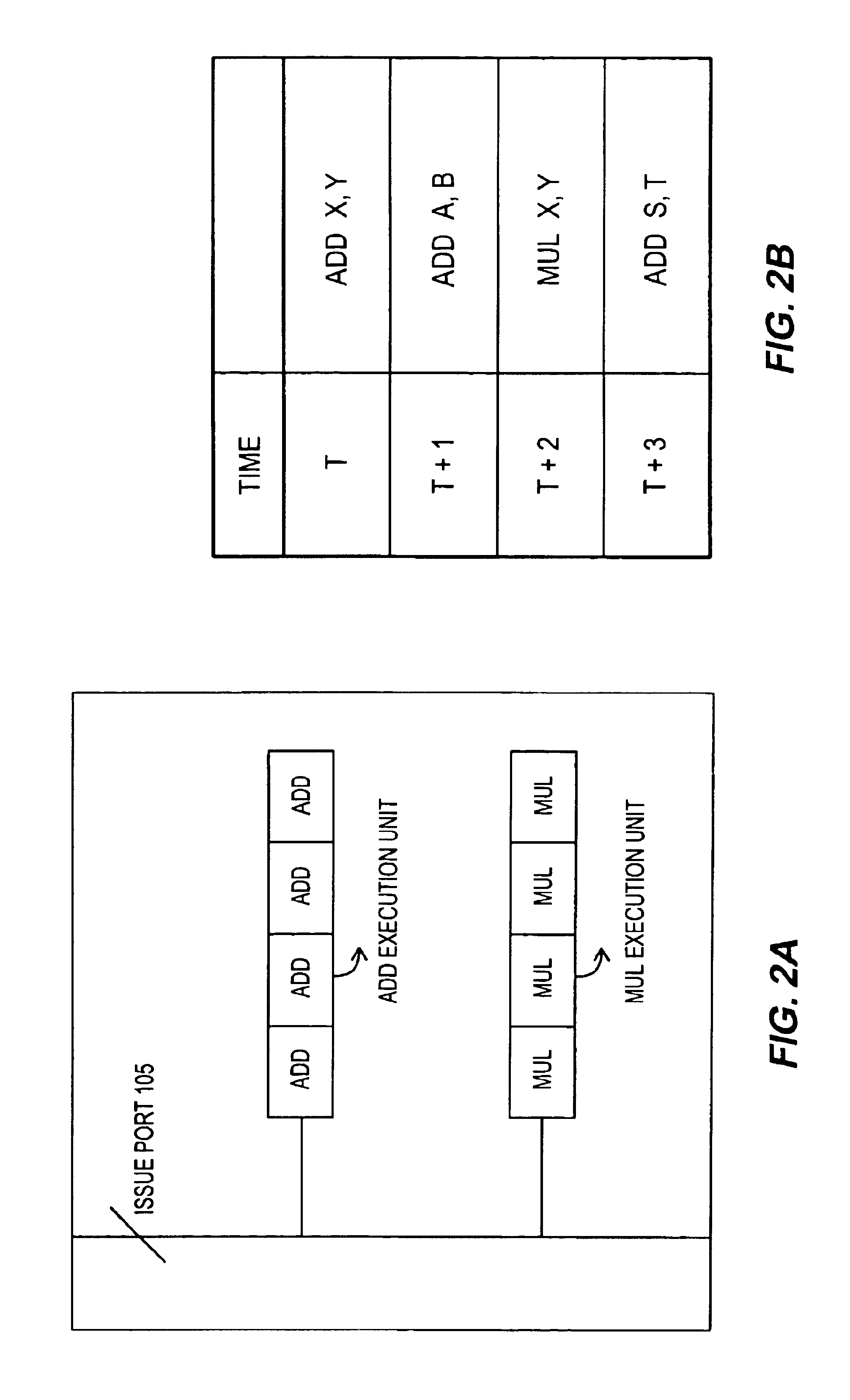

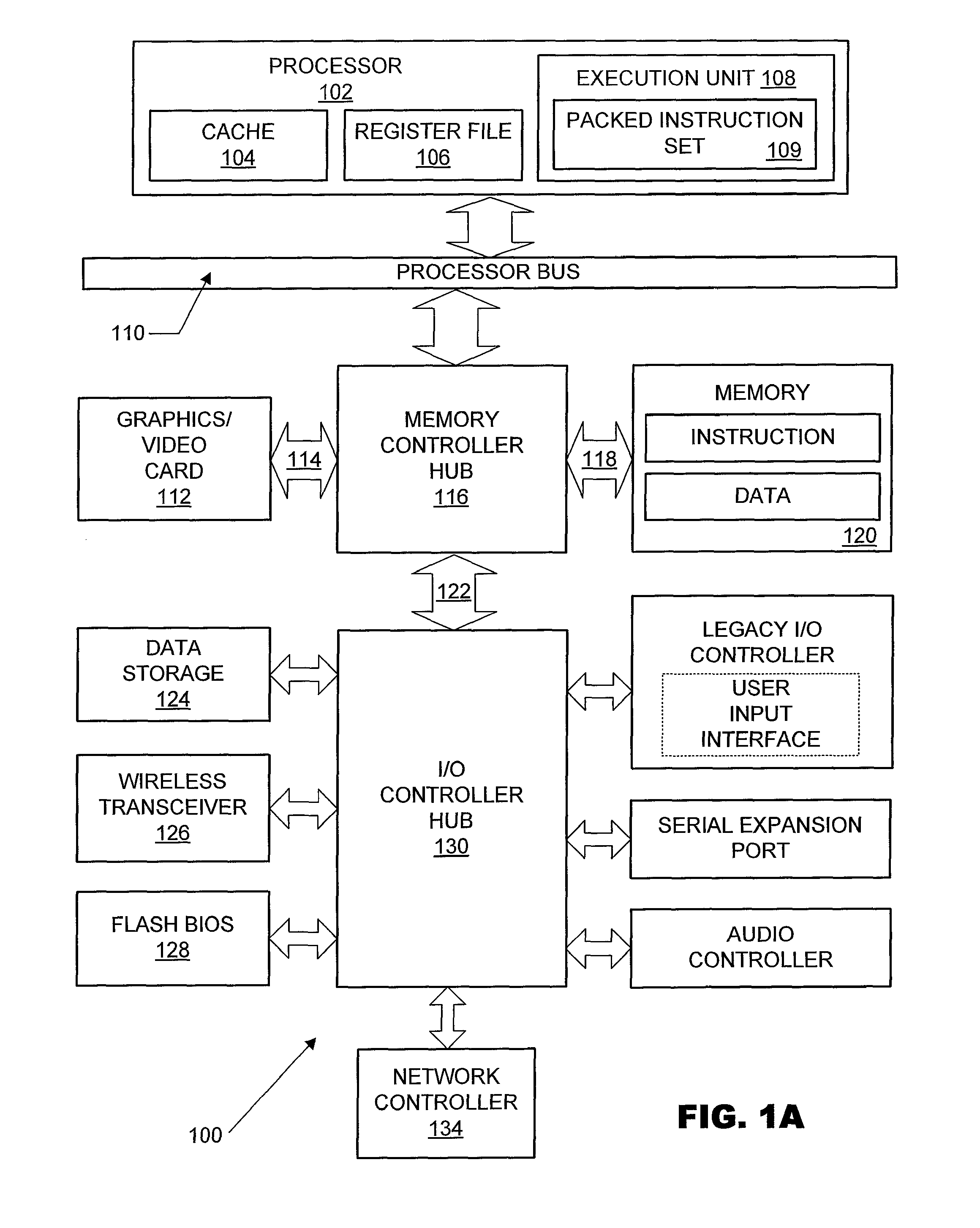

Staggering execution of a single packed data instruction using the same circuit

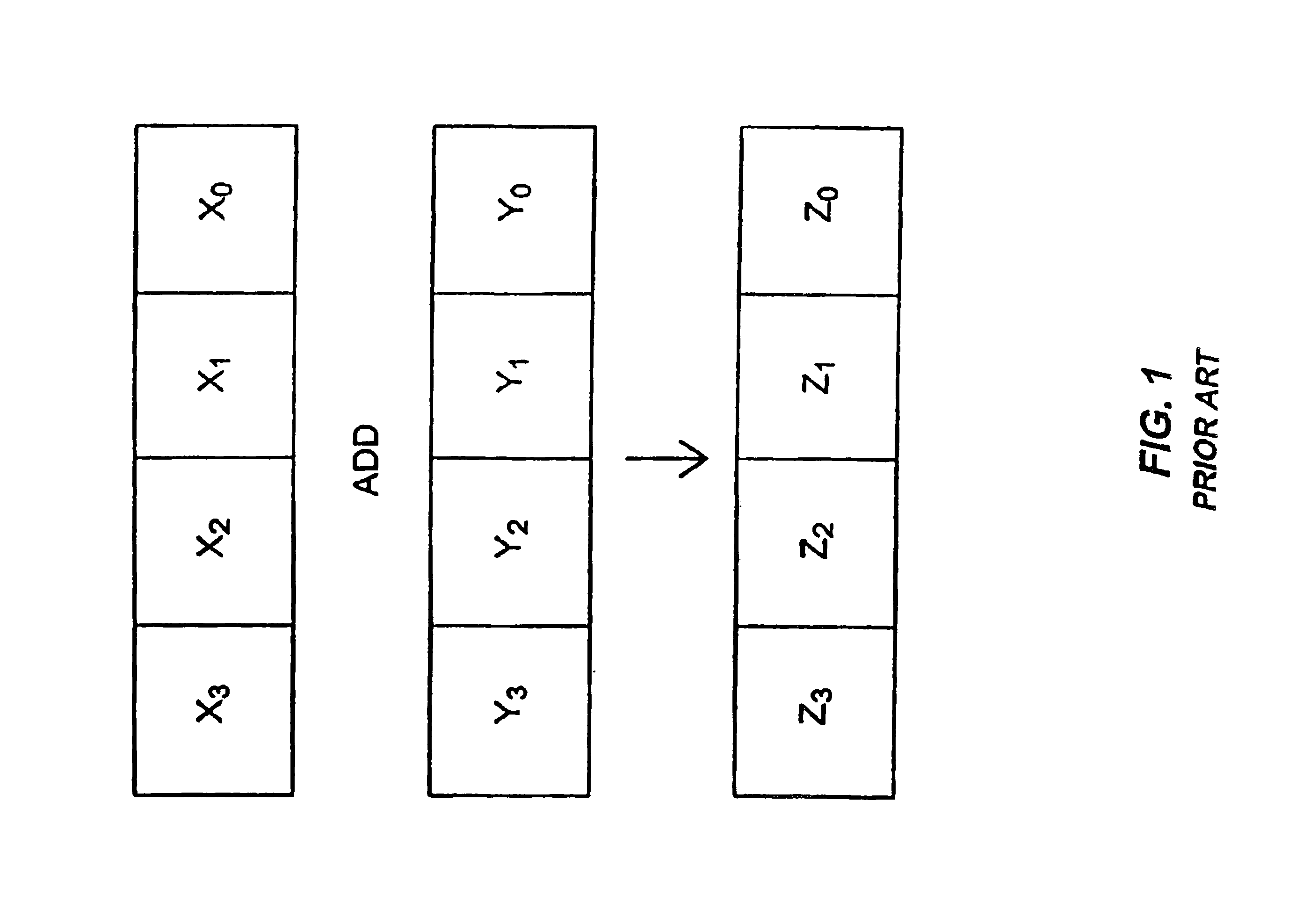

InactiveUS6925553B2Digital computer detailsSpecific program execution arrangementsProcessor registerData operations

A method and apparatus are disclosed for staggering execution of an instruction. According to one embodiment of the invention, a macro instruction specifying an operation, and specifying a first and a second data operand in first and second registers, respectively, is received. The macro instruction is then split into a first micro instruction and a second micro instruction, the first micro instruction specifying the operation on a first corresponding segment including a first portion of the first data operand and a first portion of the second data operand, and the second micro instruction specifying the operation on a second corresponding segment including a second portion of the first data operand and a second portion of the second data operand. The first and second micro instructions are then executed.

Owner:INTEL CORP

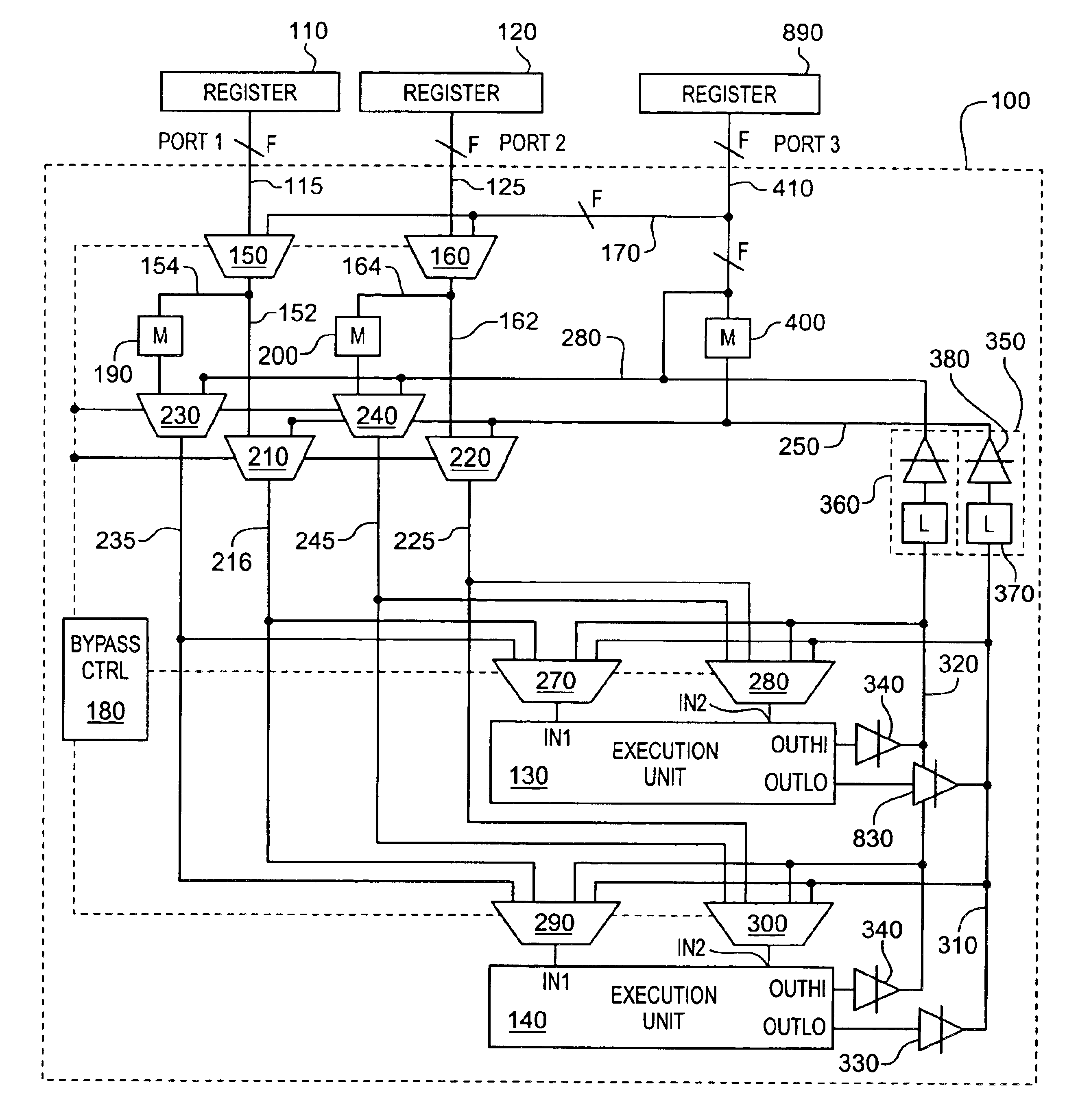

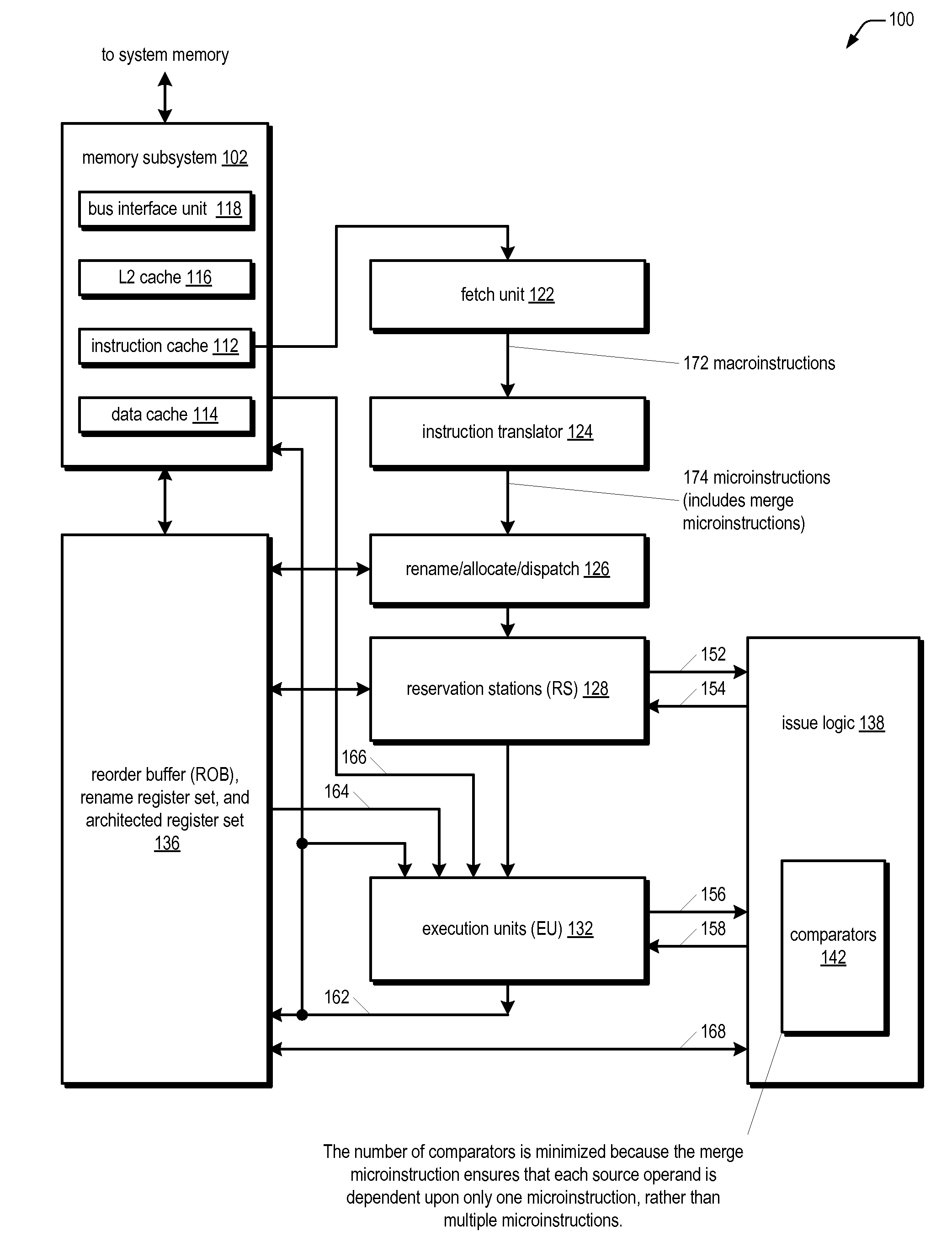

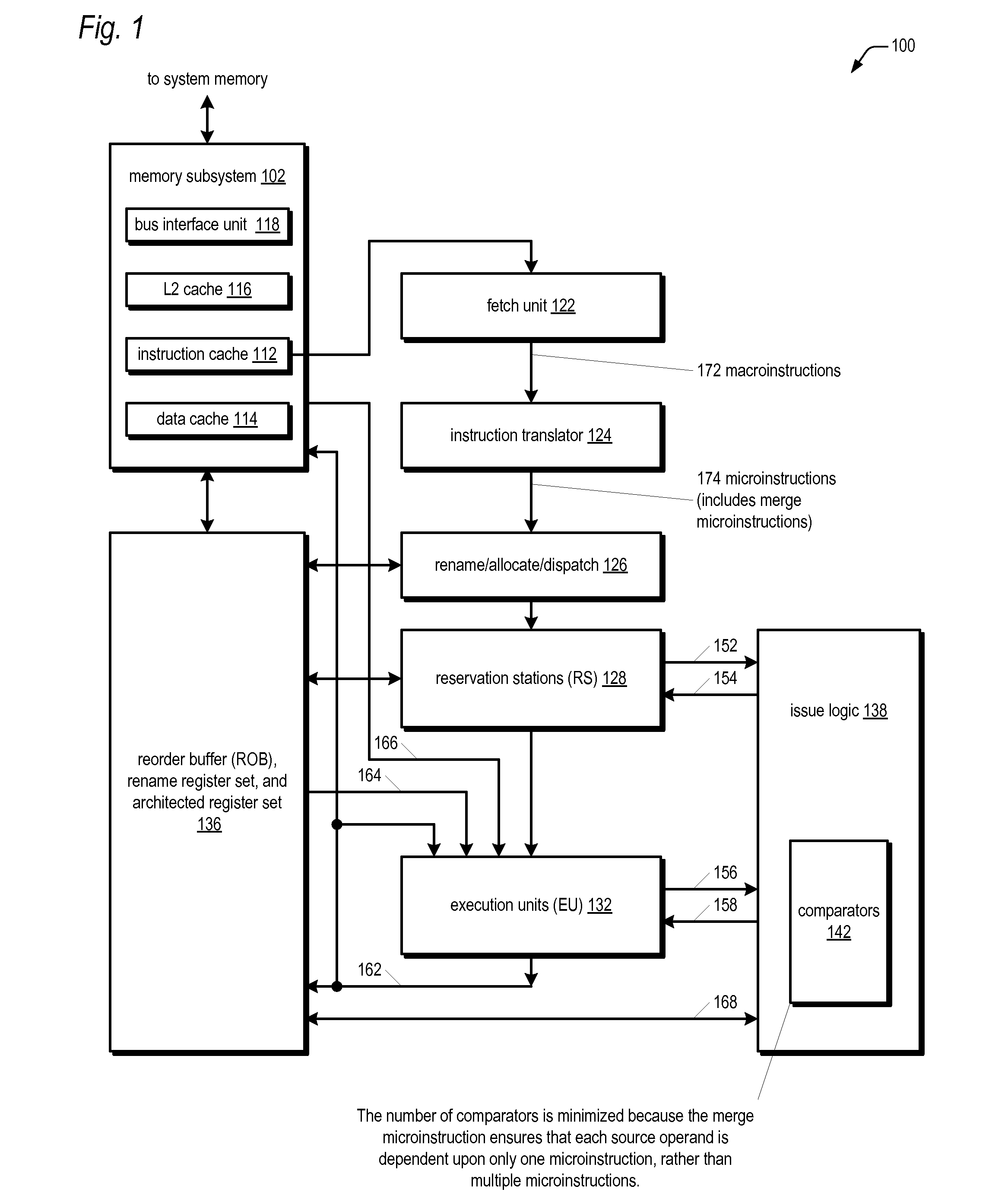

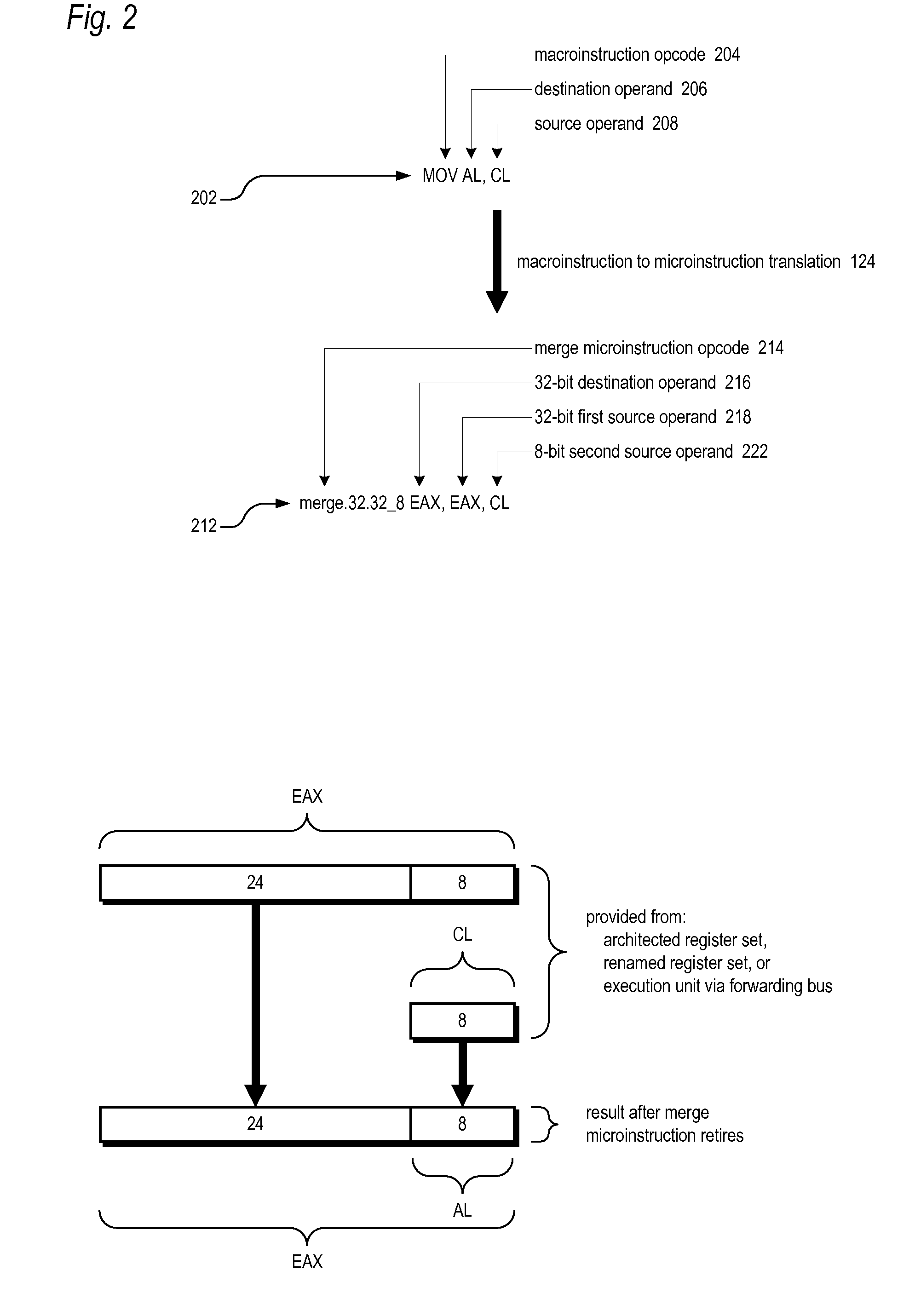

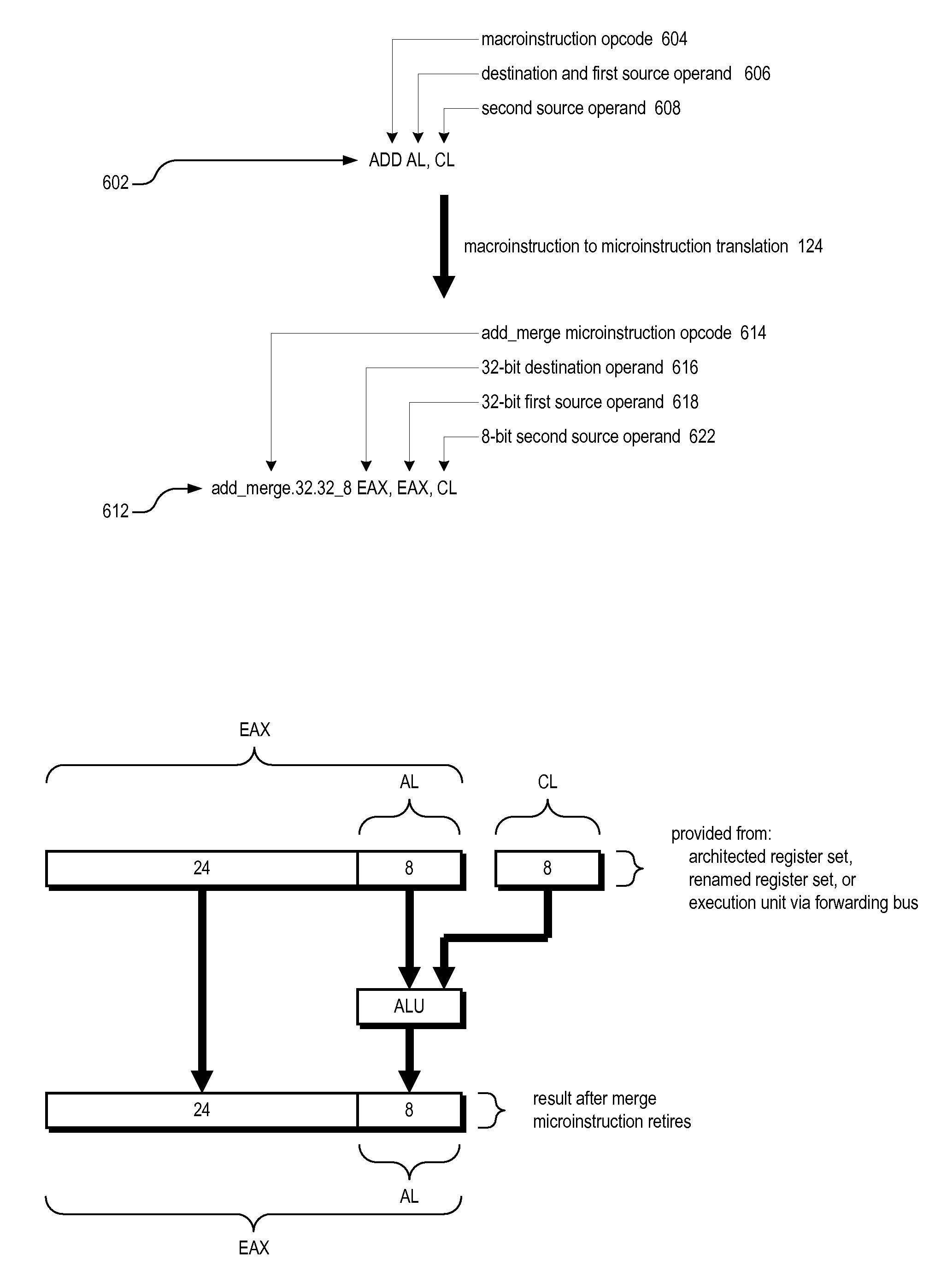

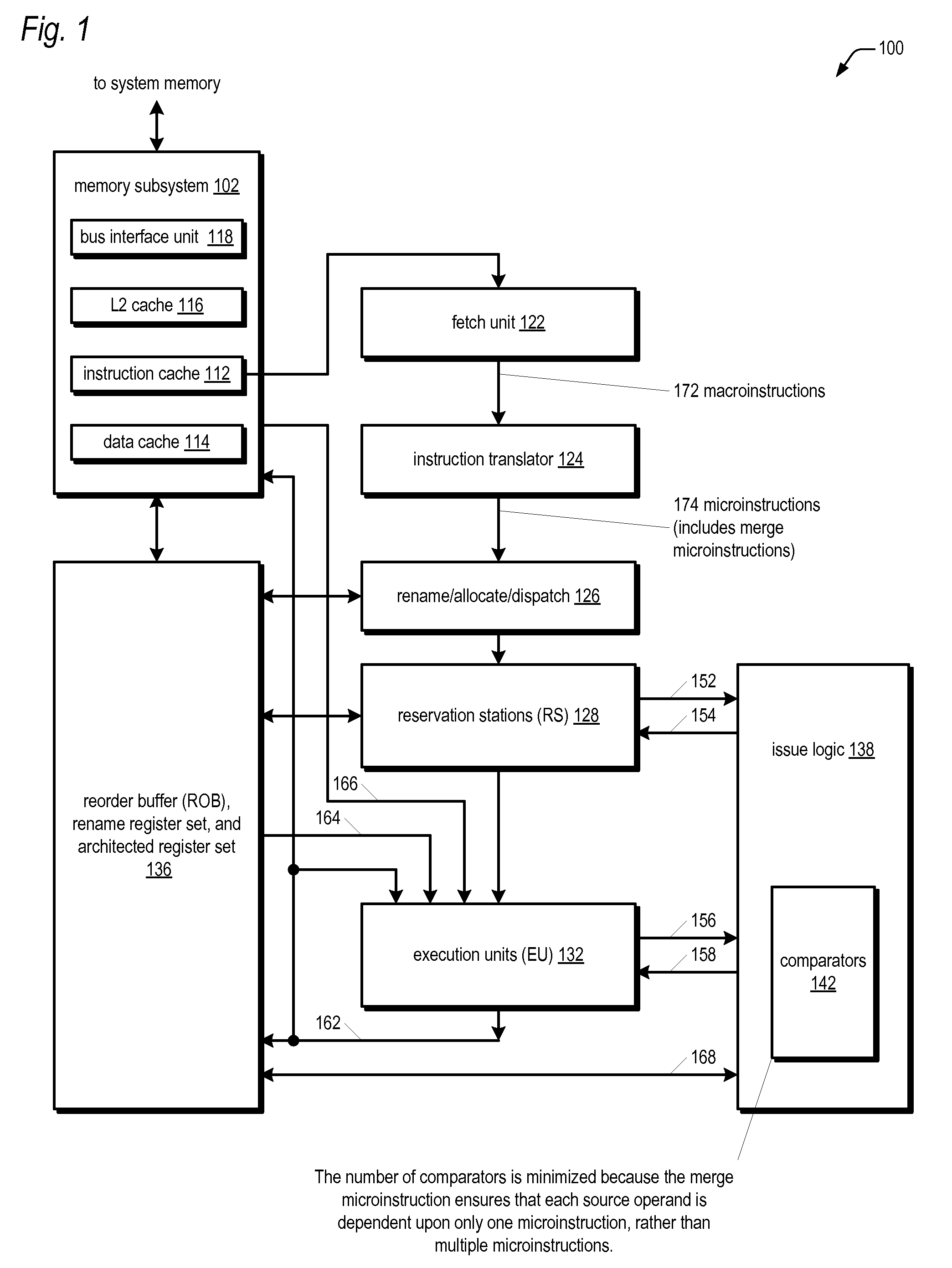

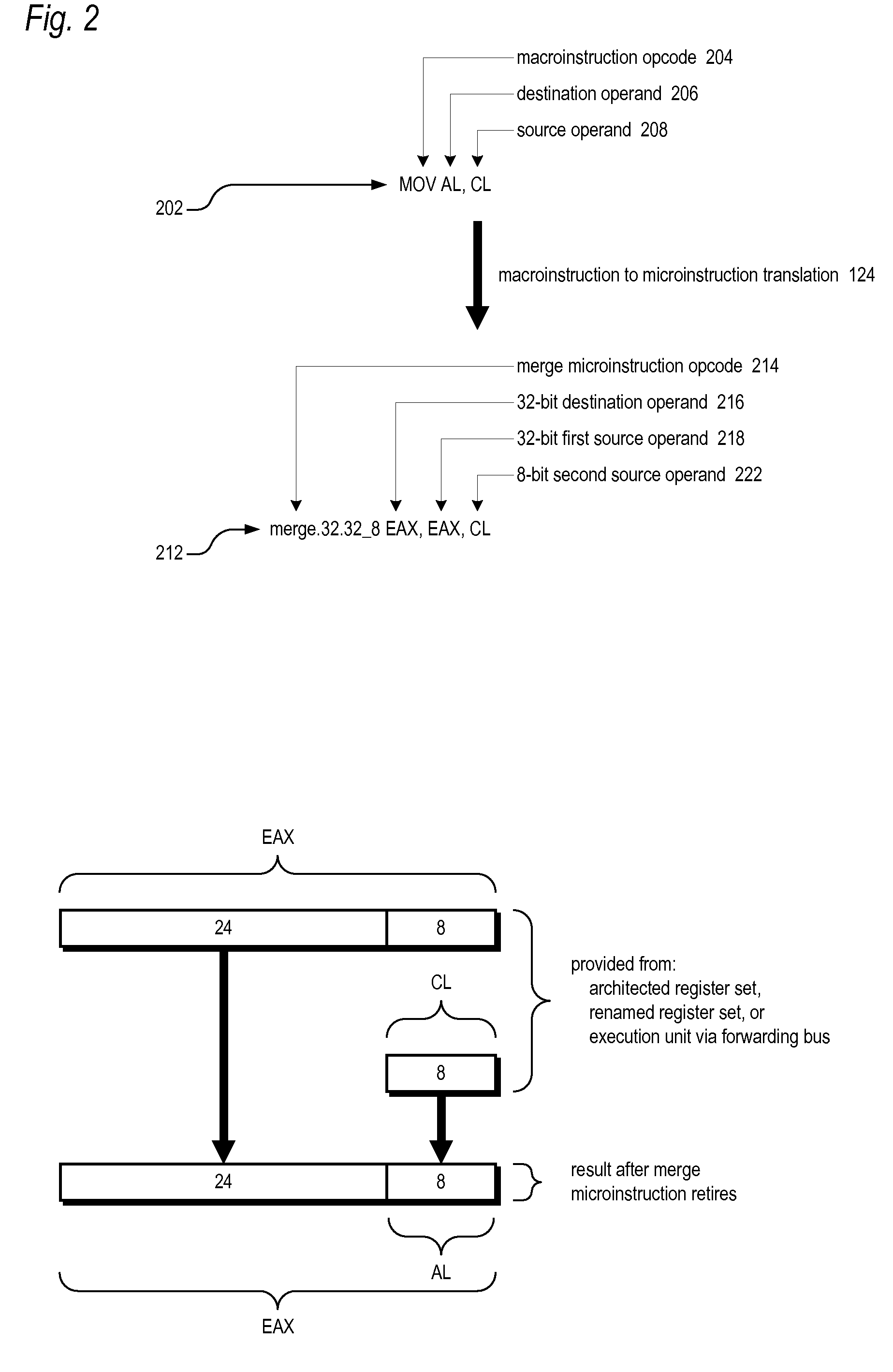

Merge microinstruction for minimizing source dependencies in out-of-order execution microprocessor with variable data size macroarchitecture

ActiveUS20090254735A1Runtime instruction translationDigital computer detailsGeneral purposeComputer architecture

A microprocessor processes a macroinstruction that instructs the microprocessor to write an 8-bit result into only a lower 8 bits of an N-bit architected general purpose register. An instruction translator translates the macroinstruction into a merge microinstruction that specifies an N-bit first source register, an 8-bit second source register, and an N-bit destination register to receive an N-bit result. The N-bit first source register and the N-bit destination register are the N-bit architected general purpose register. An execution unit receives the merge microinstruction and responsively generates the N-bit result to be subsequently written to the N-bit architected general purpose register even though the macroinstruction only instructs the microprocessor to write the 8-bit result into the lower 8 bits of the N-bit architected general purpose register. Specifically, the execution unit directs the 8-bit result into the lower 8 bits of the N-bit result and directs the upper N-8 bits of the N-bit first source register into corresponding upper N-8 bits of the N-bit result.

Owner:VIA TECH INC

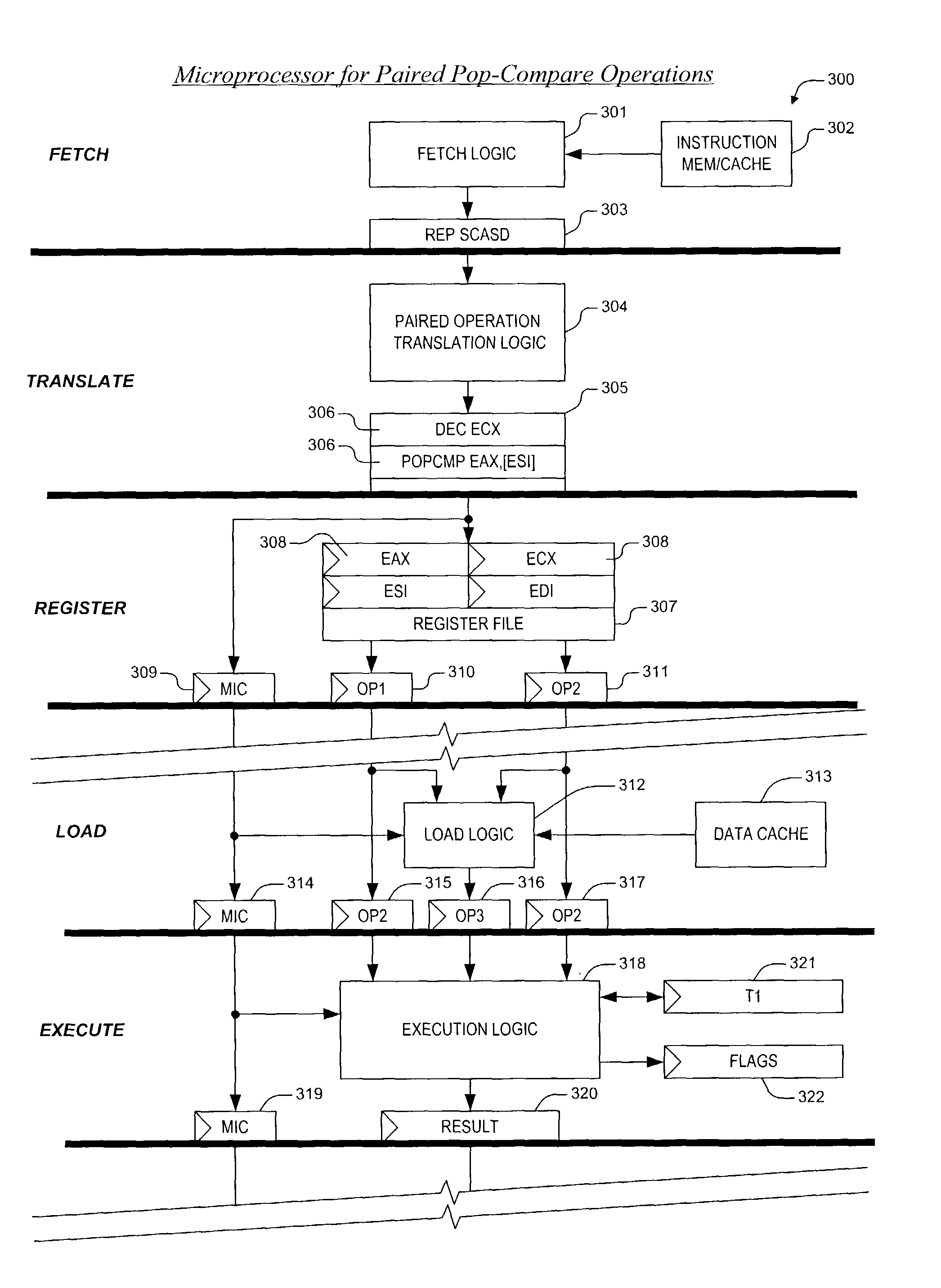

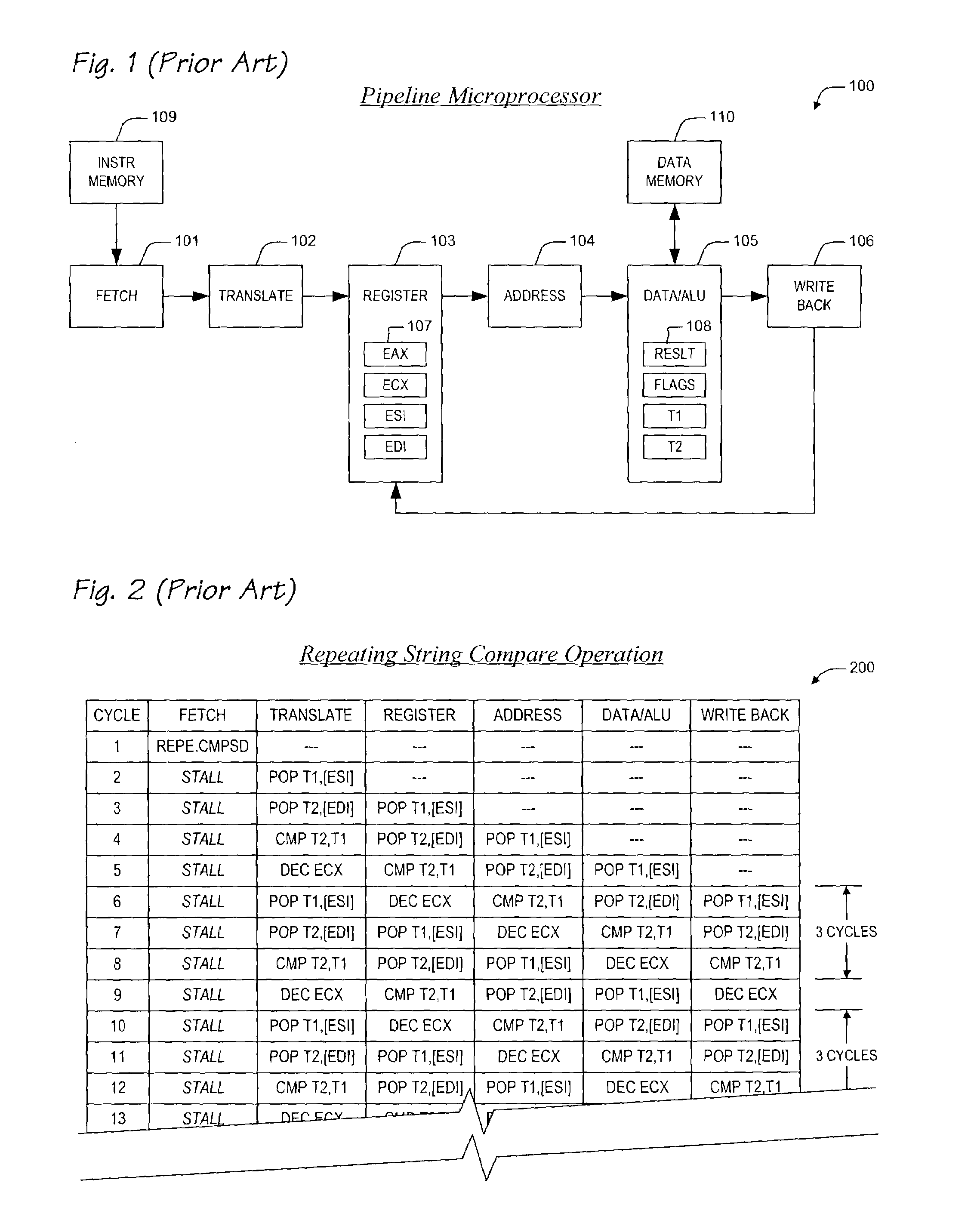

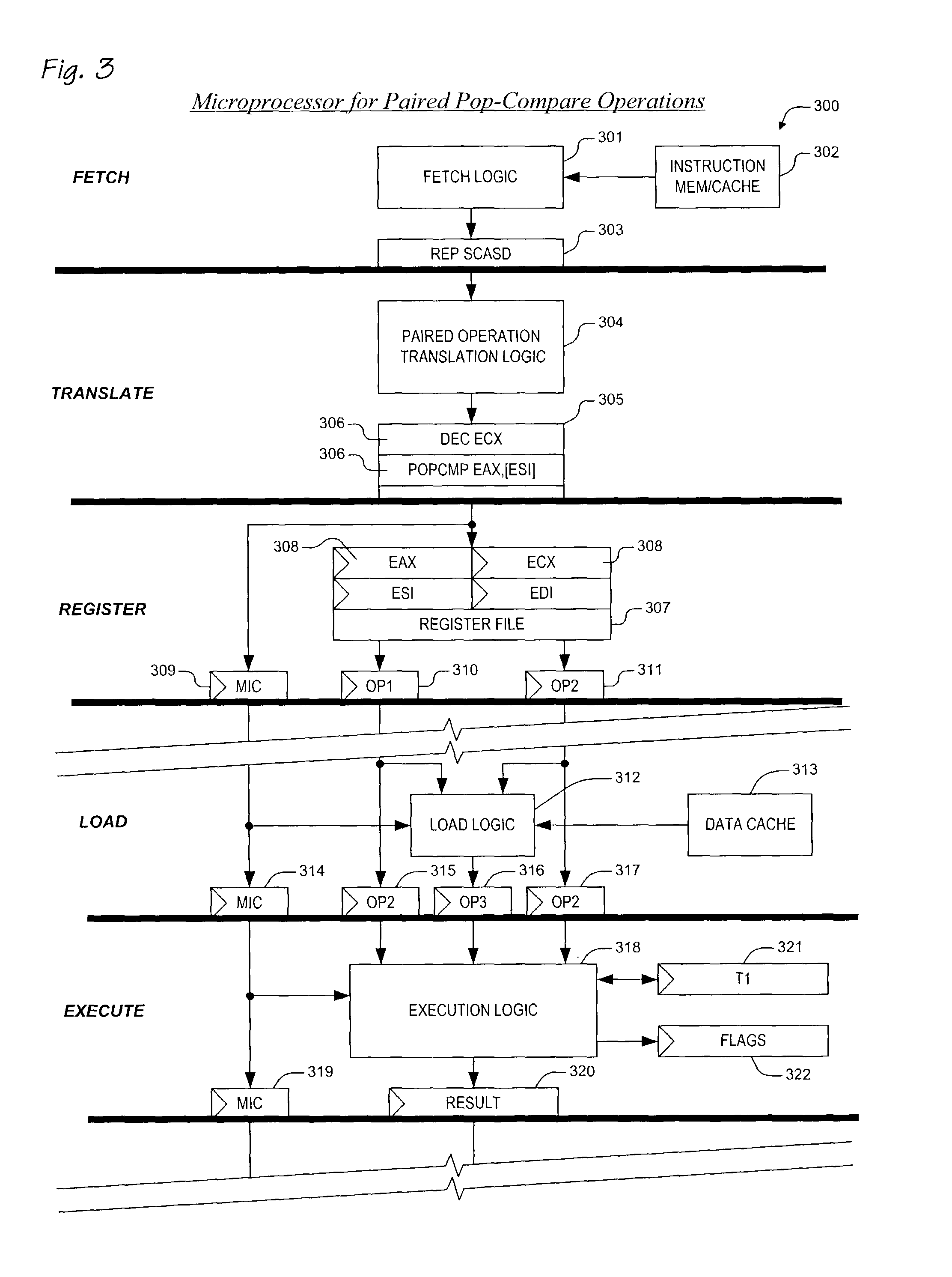

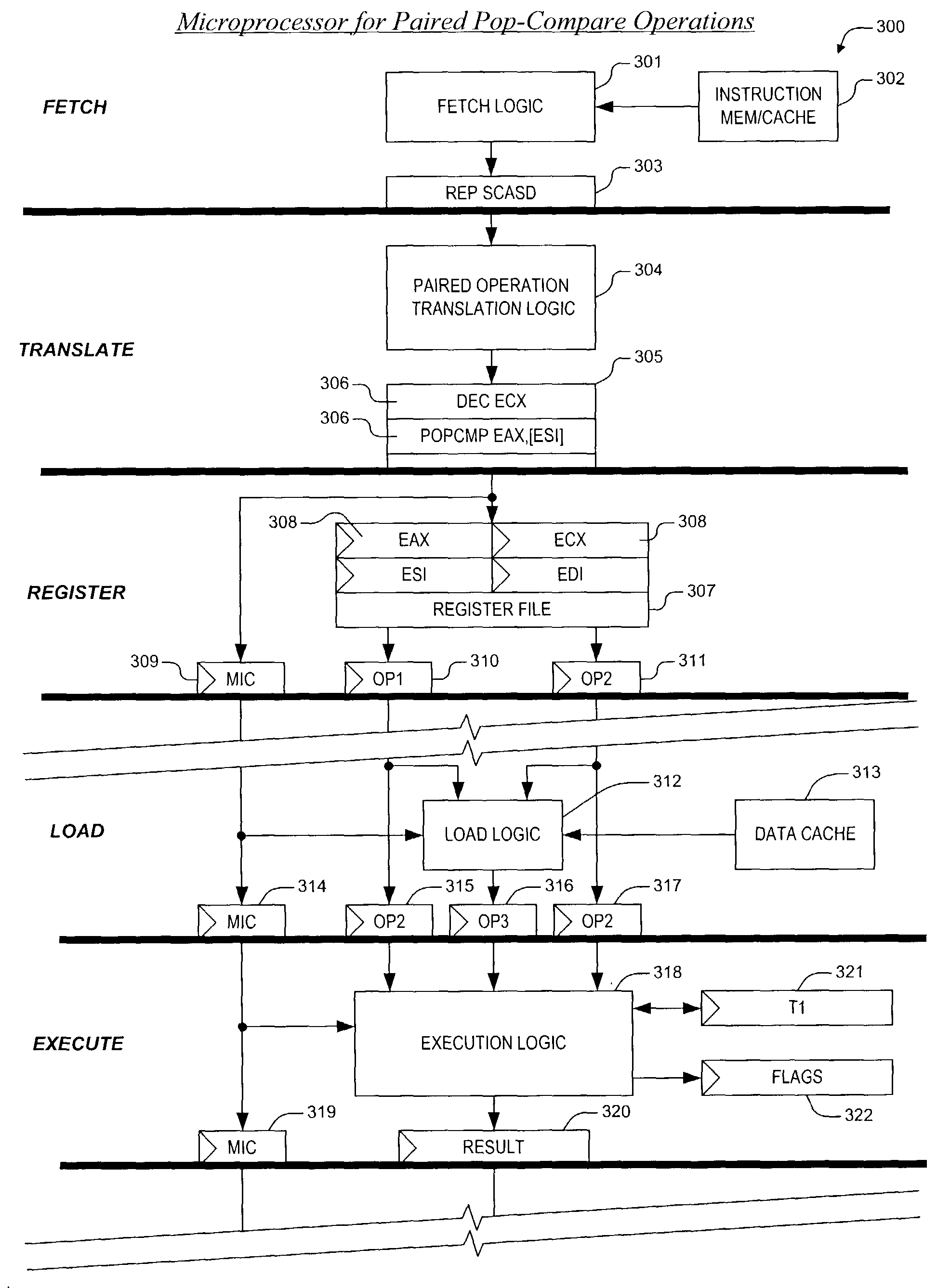

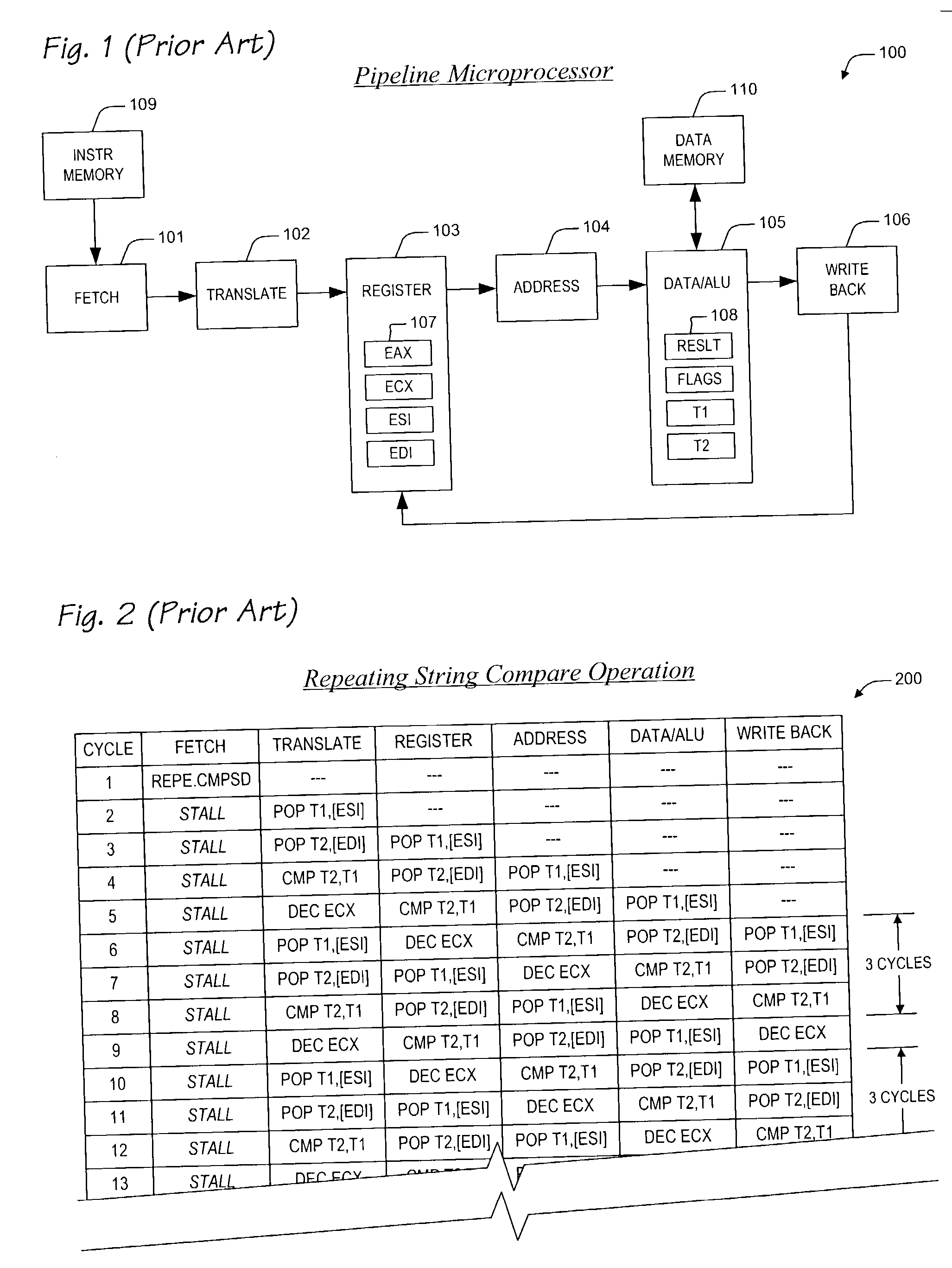

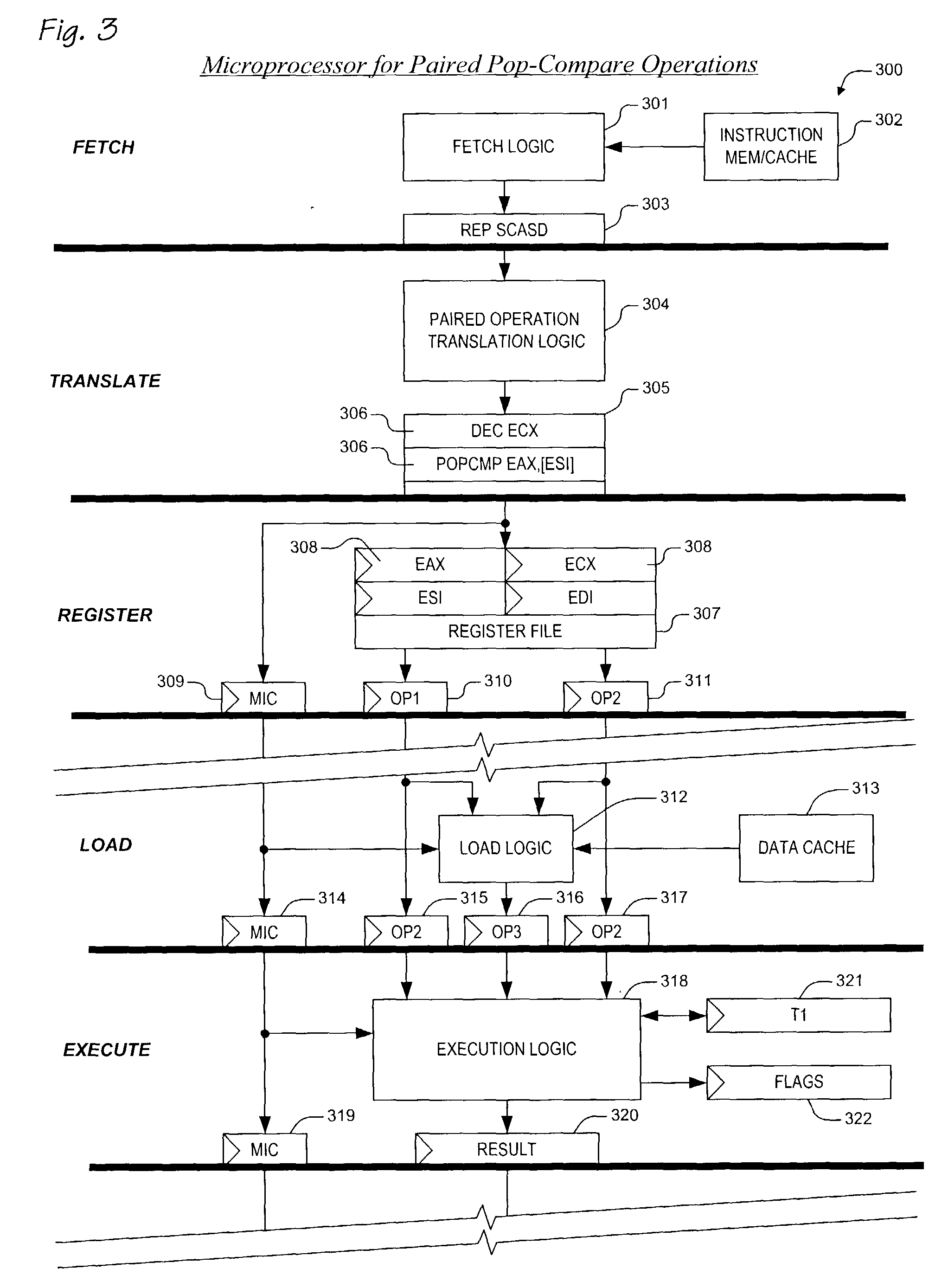

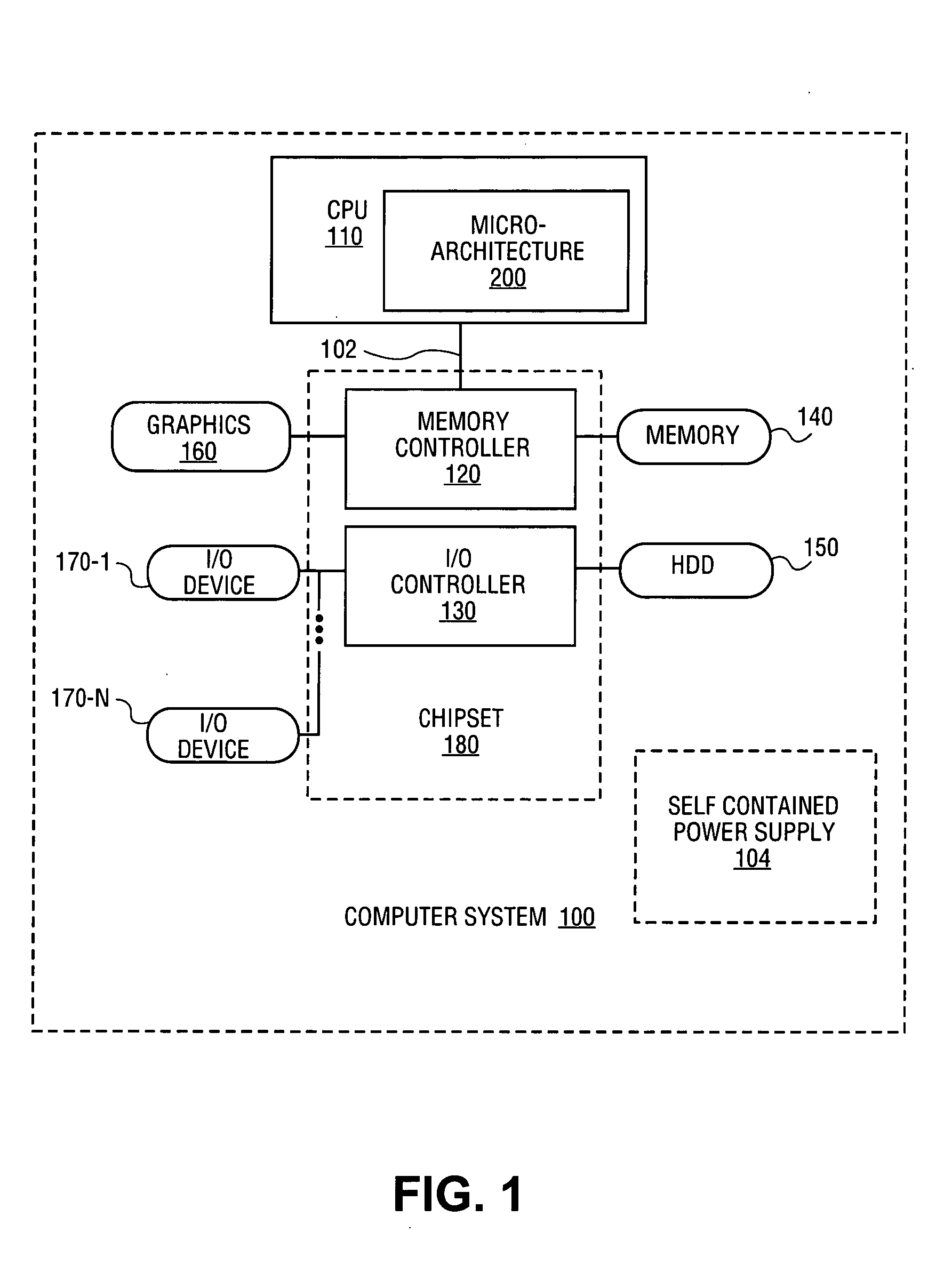

Pop-compare micro instruction for repeat string operations

ActiveUS6931517B1Runtime instruction translationDigital computer detailsString operationsProcessor register

A microprocessor apparatus is provided for performing a pop-compare operation. The microprocessor apparatus includes paired operation translation logic, load logic, and execution logic. The paired operation translation logic receives a macro instruction that prescribes the pop-compare operation, and generates a pop-compare micro instruction. The pop-compare micro instruction directs pipeline stages in a microprocessor to perform the pop-compare operation. The load logic is coupled to the paired operation translation logic. The load logic receives the pop-compare micro instruction, and retrieves a first operand from an address in memory, where the address is specified by contents of a register. The register is prescribed by the pop-compare micro instruction. The execution logic is coupled to the load logic. The execution logic receives the first operand, and compares the first operand to a second operand.

Owner:IP FIRST

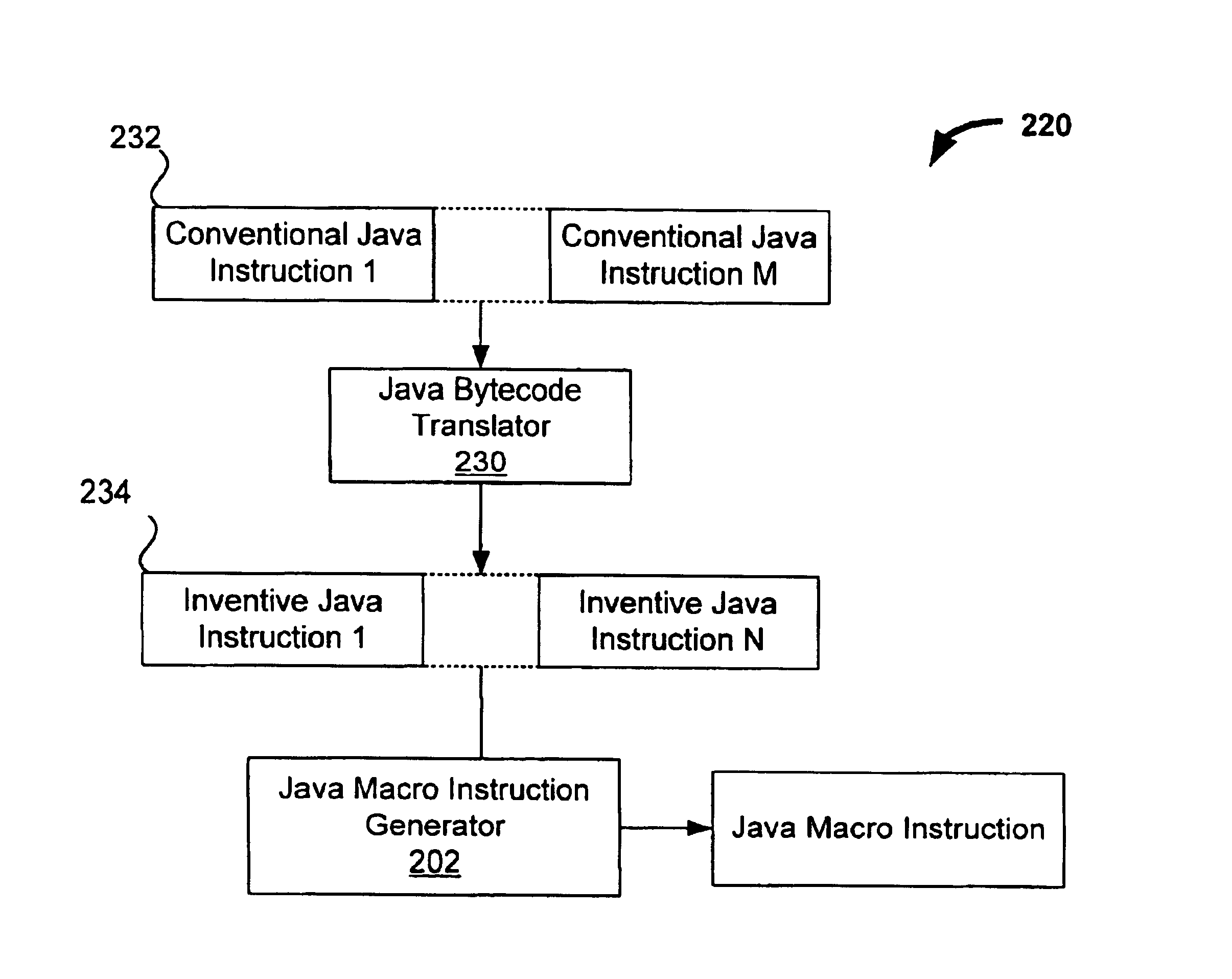

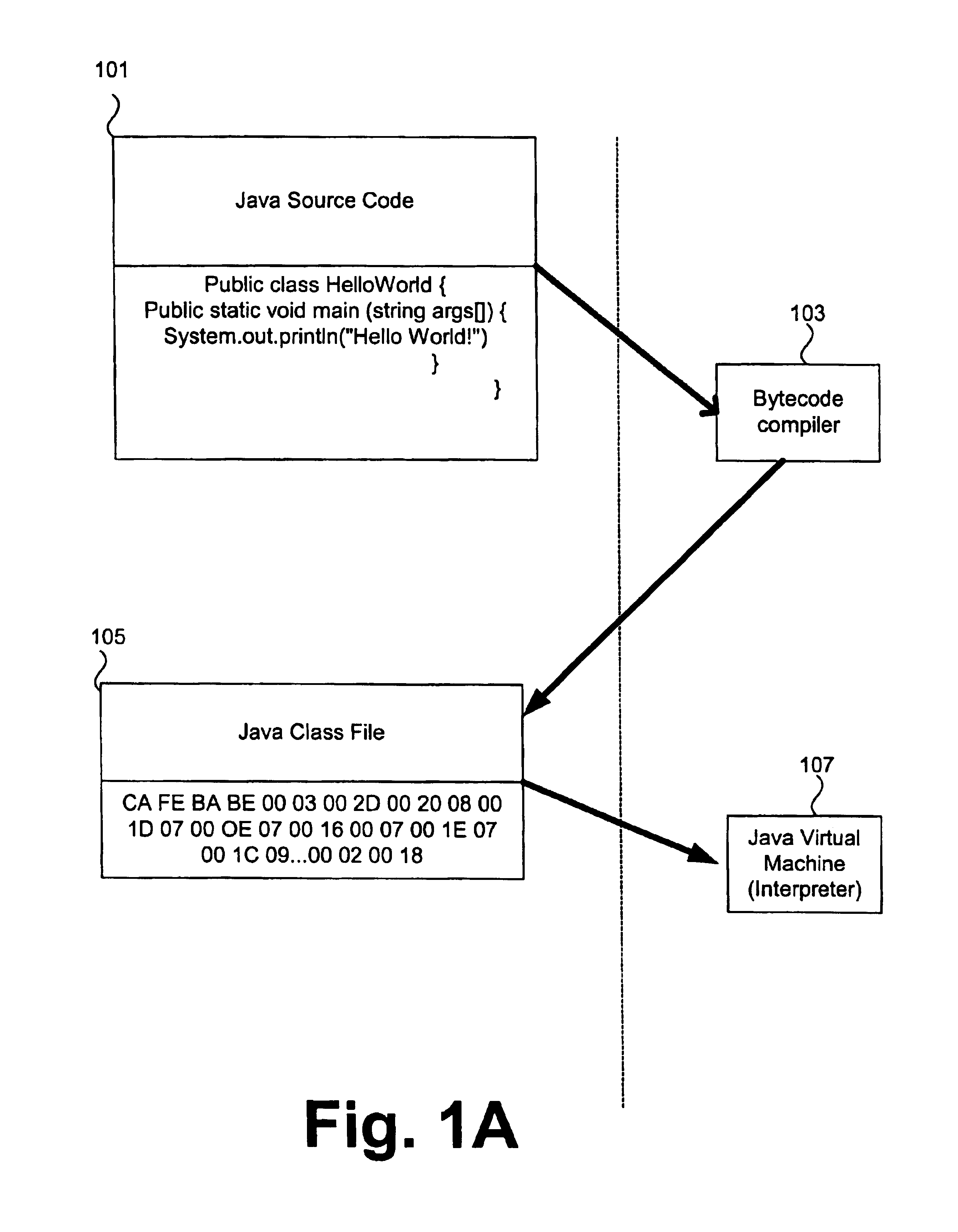

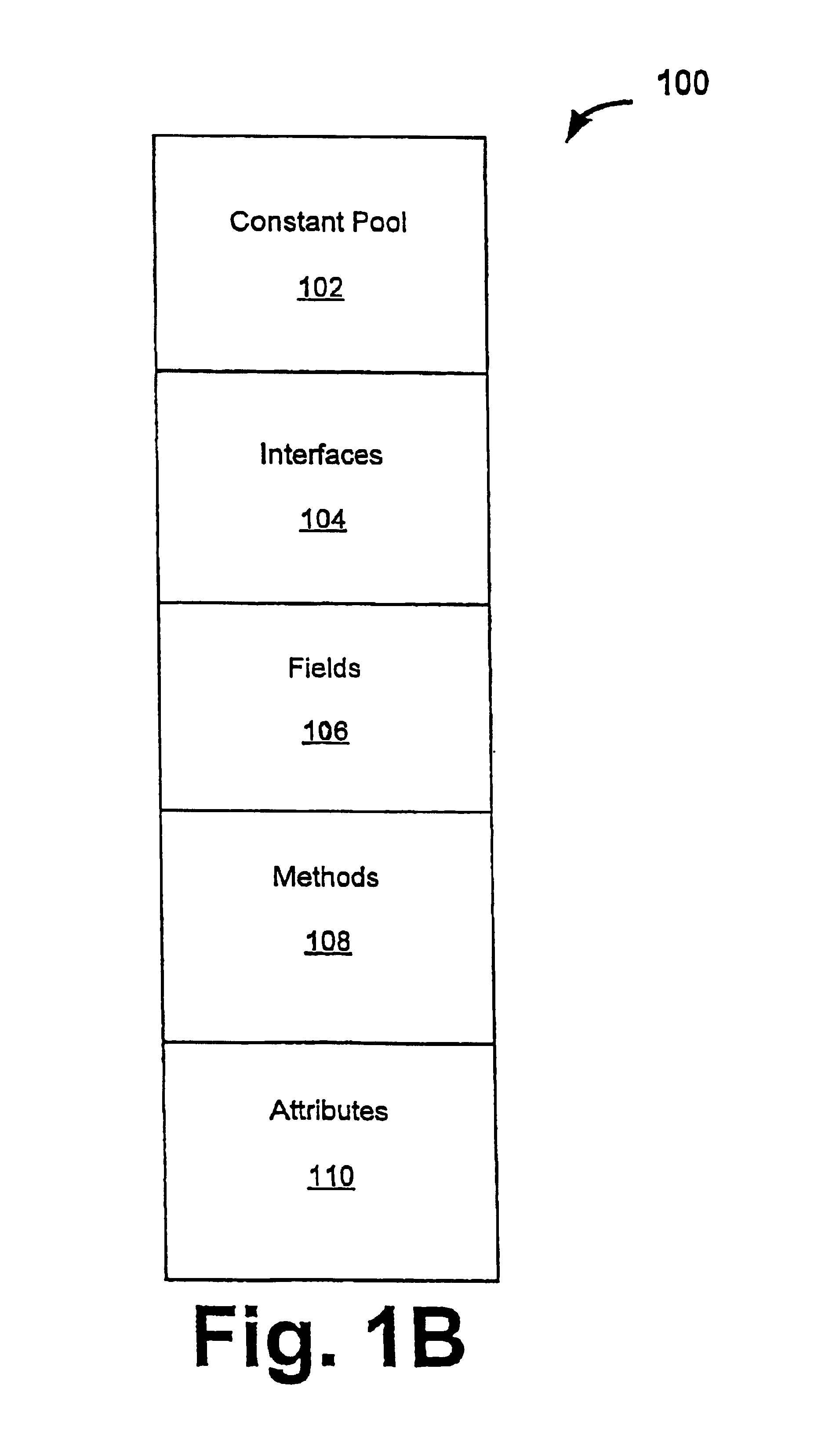

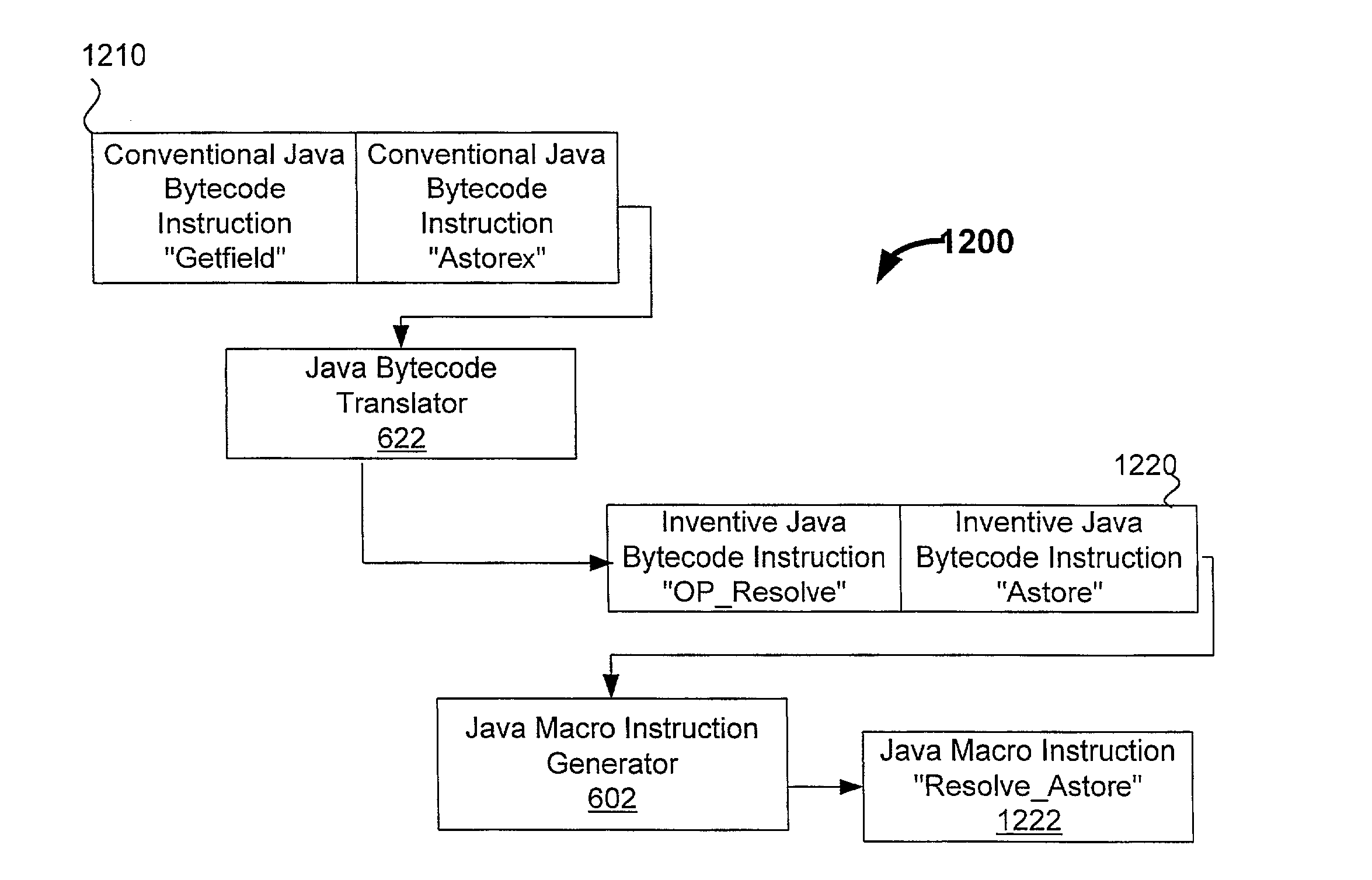

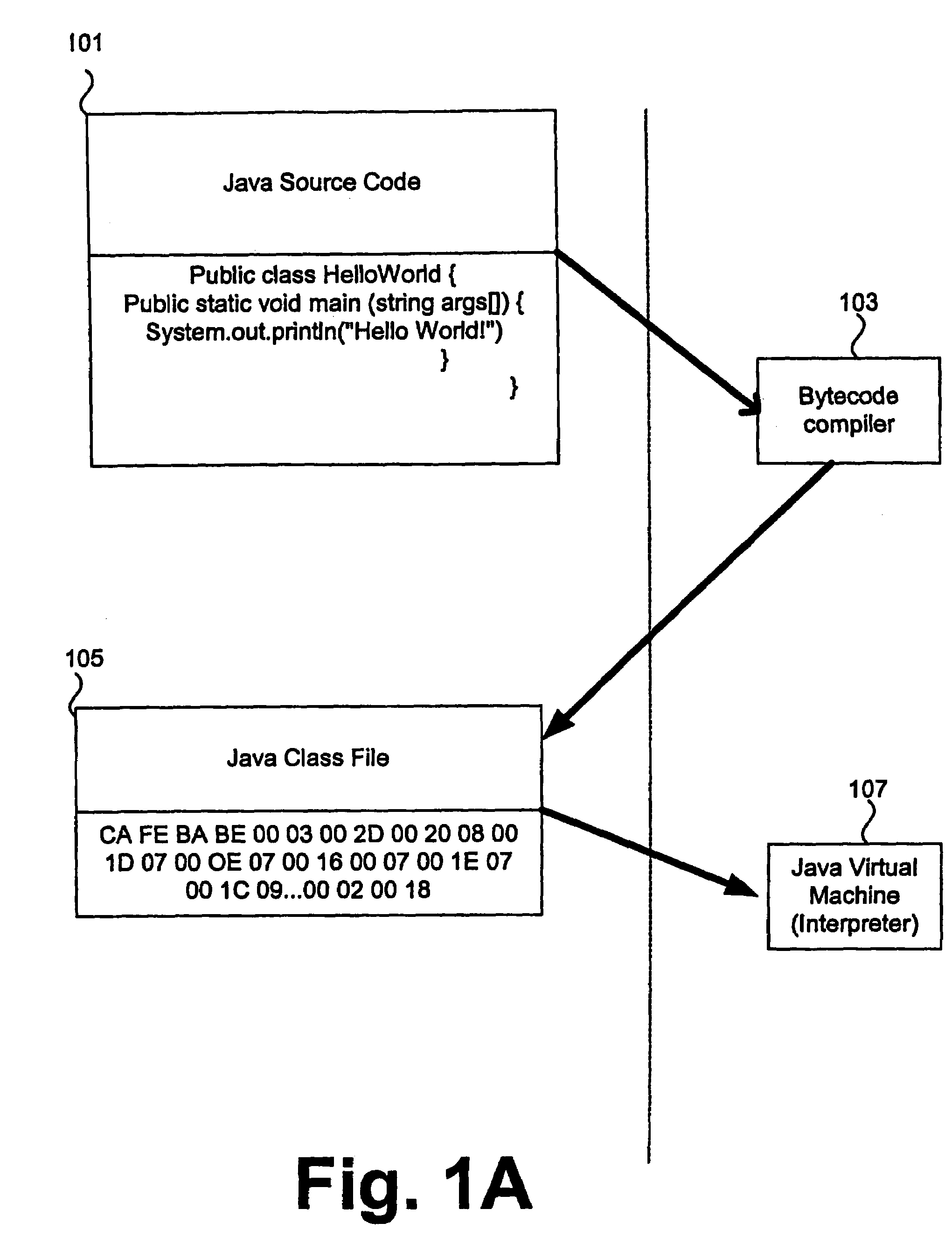

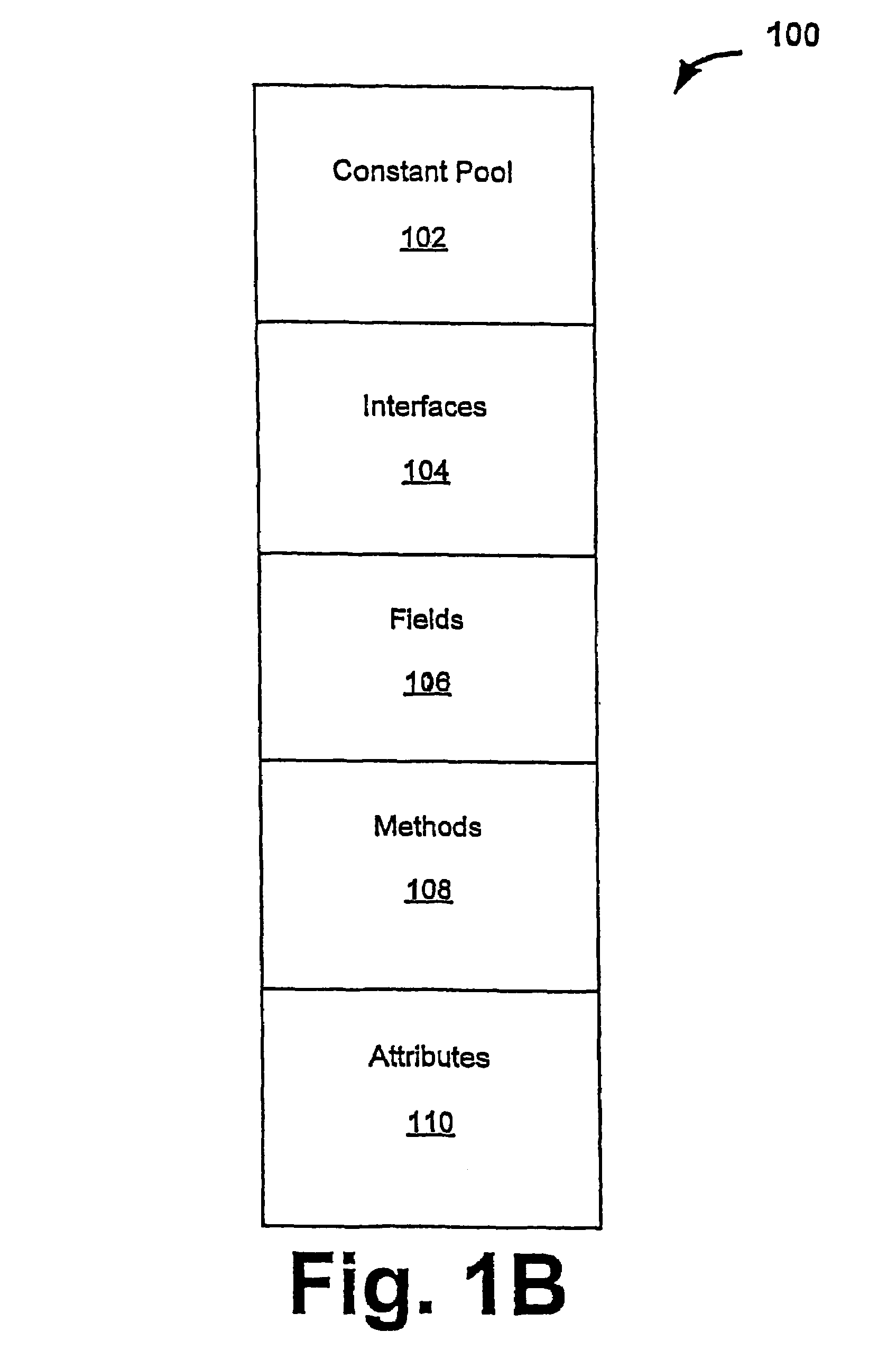

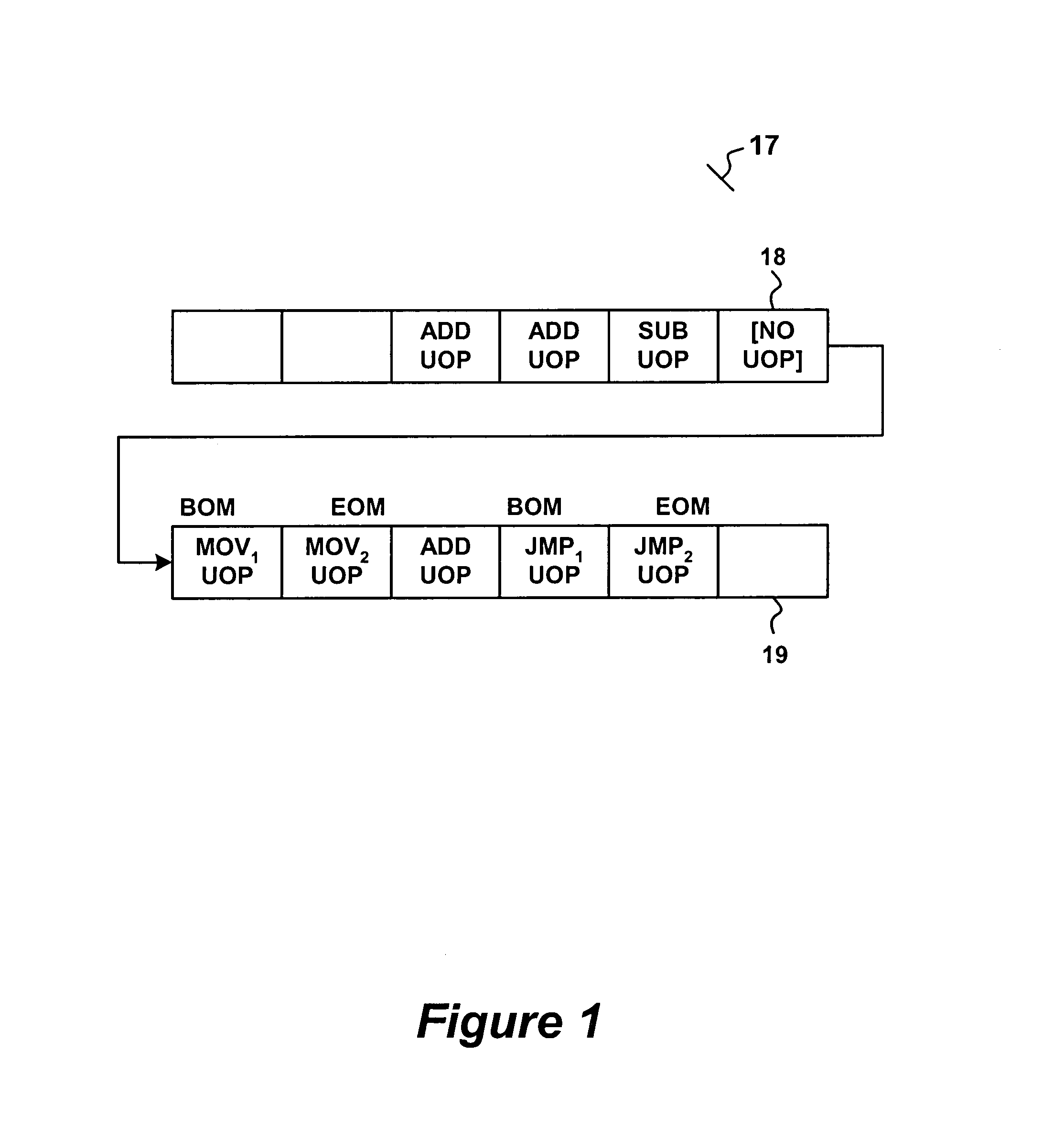

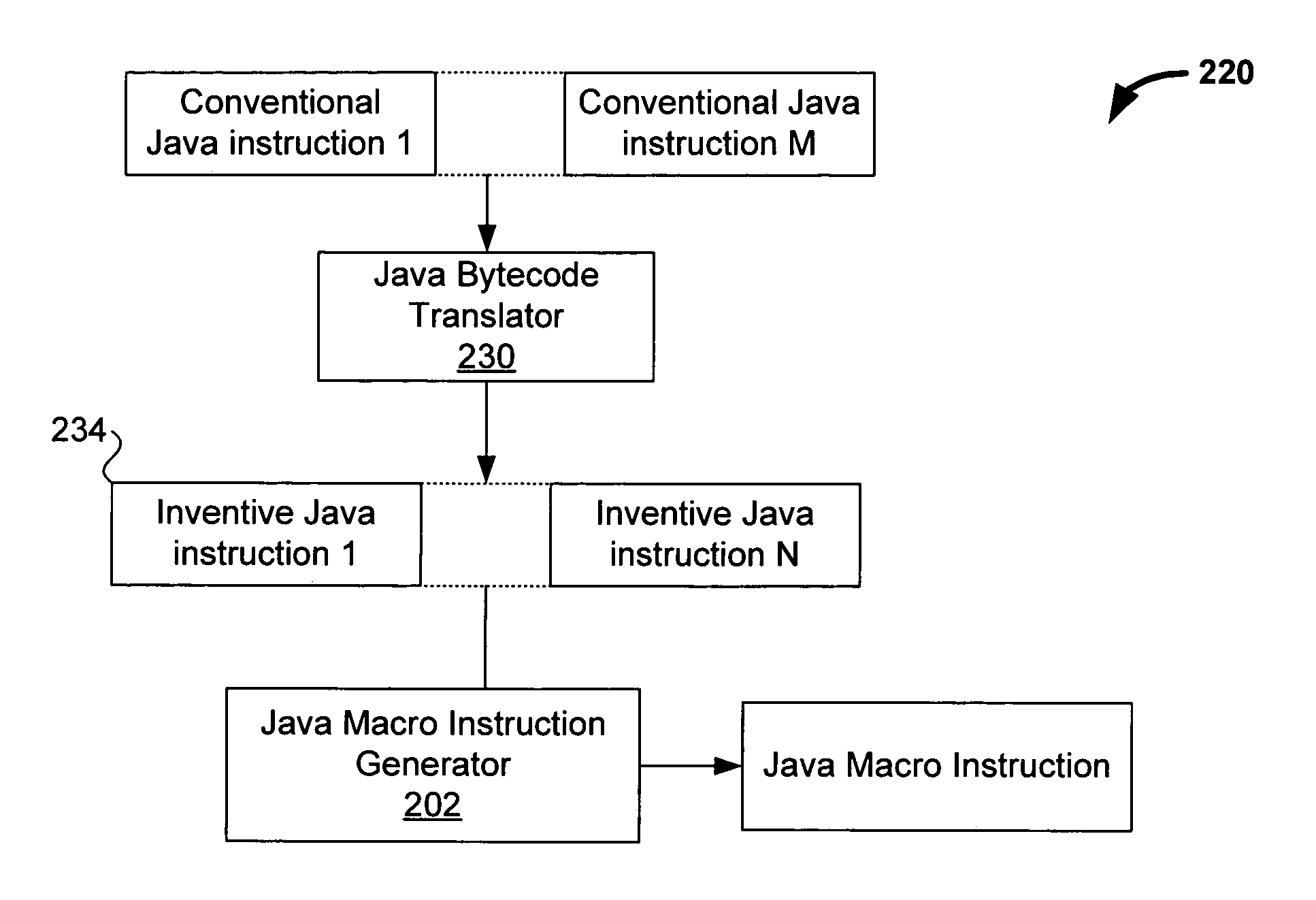

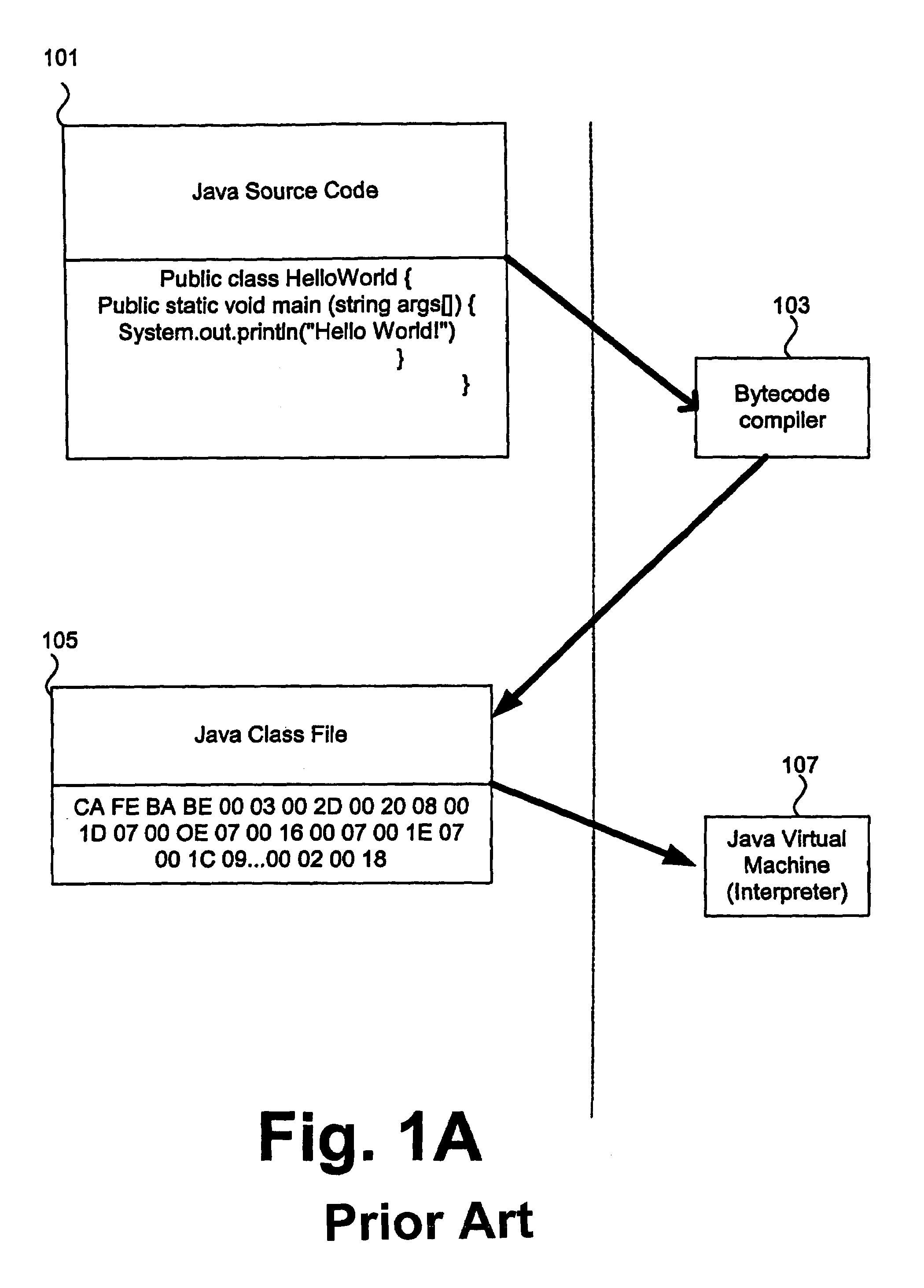

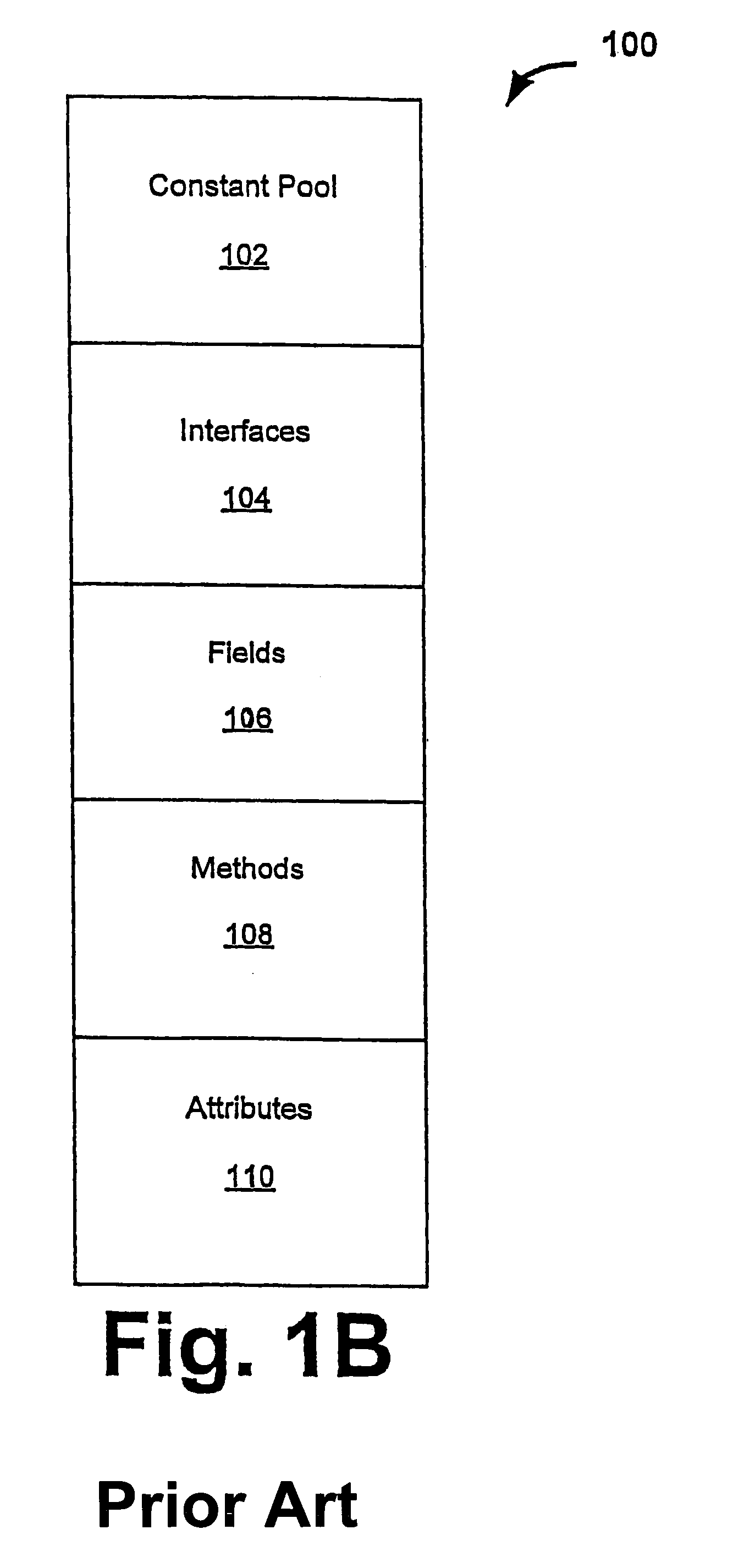

Frameworks for generation of Java macro instructions in Java computing environments

InactiveUS6988261B2Efficient executionReduce in quantitySoftware engineeringSpecific program execution arrangementsLimited resourcesLocal variable

Techniques for generation of Java™ macro instructions suitable for use in Java™ computing environments are disclosed. As such, the techniques can be implemented in a Java™ virtual machine to efficiently execute Java™ instructions. As will be appreciated, a Java™ macro instruction can be substituted for two or more Java™ Bytecode instructions. This, in turn, reduces the number of Java™ instructions that are executed by the interpreter. As a result, the performance of virtual machines, especially those operating with limited resources, is improved. A Java™ macro instruction can be generated for conventional Java™ instruction sequences or sequences of Java™ instruction that are provided in a reduced set of instruction. In any case, sequences that are frequently encountered can be replaced by a Java™ macro instruction. These sequences are typically encountered when Java™ objects are instantiated, during programming loops, and when a local variables are assigned a value.

Owner:ORACLE INT CORP

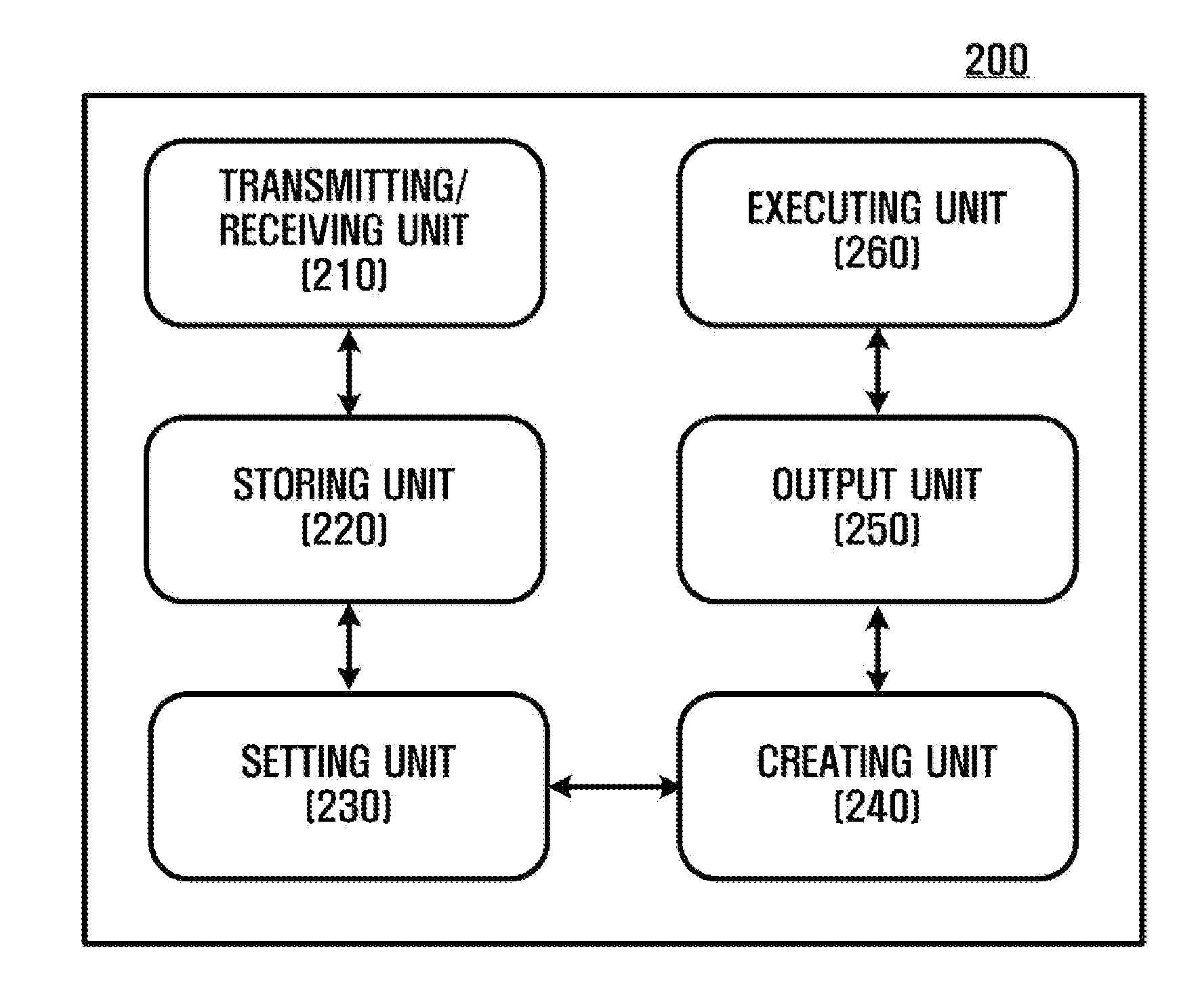

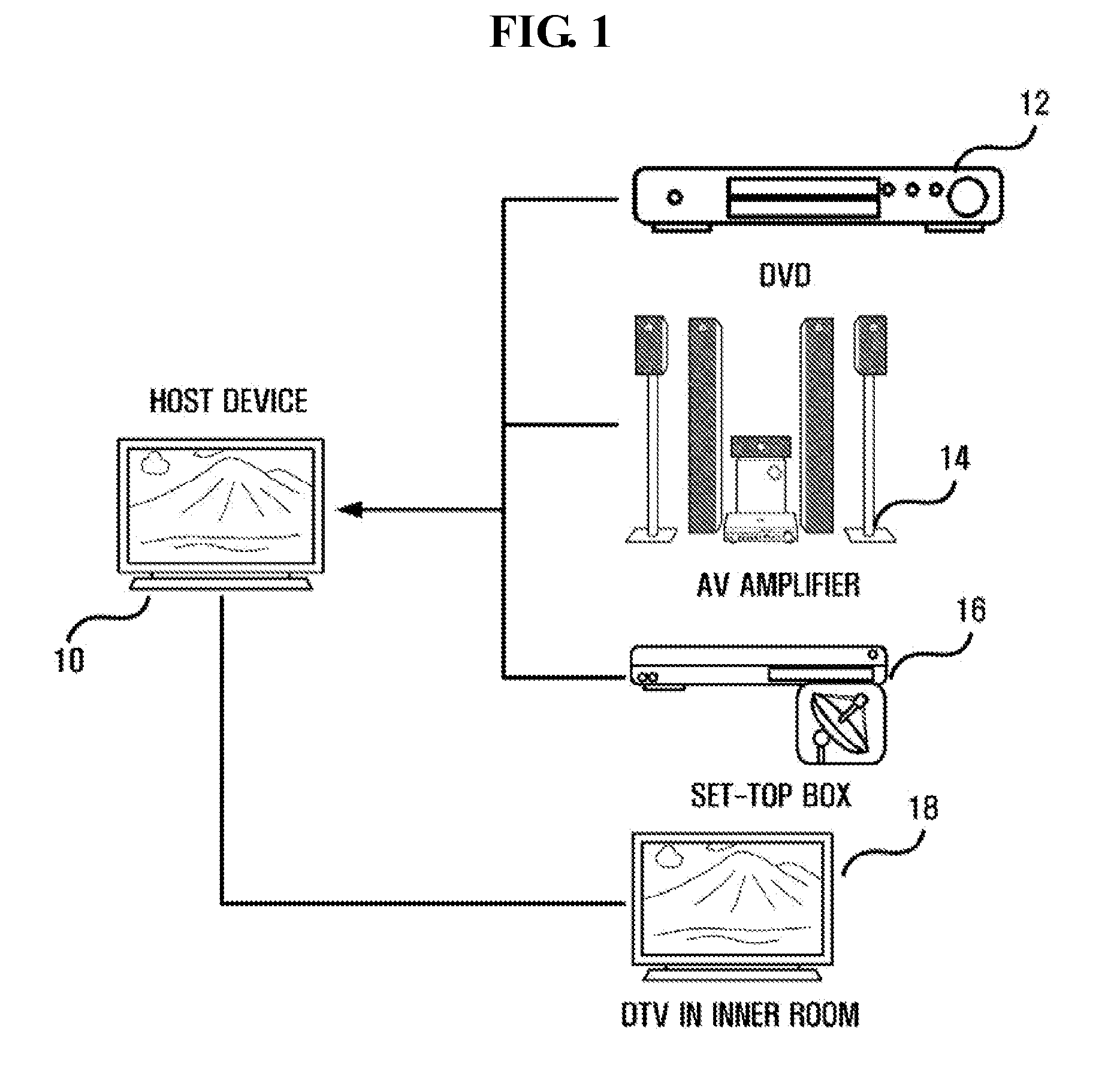

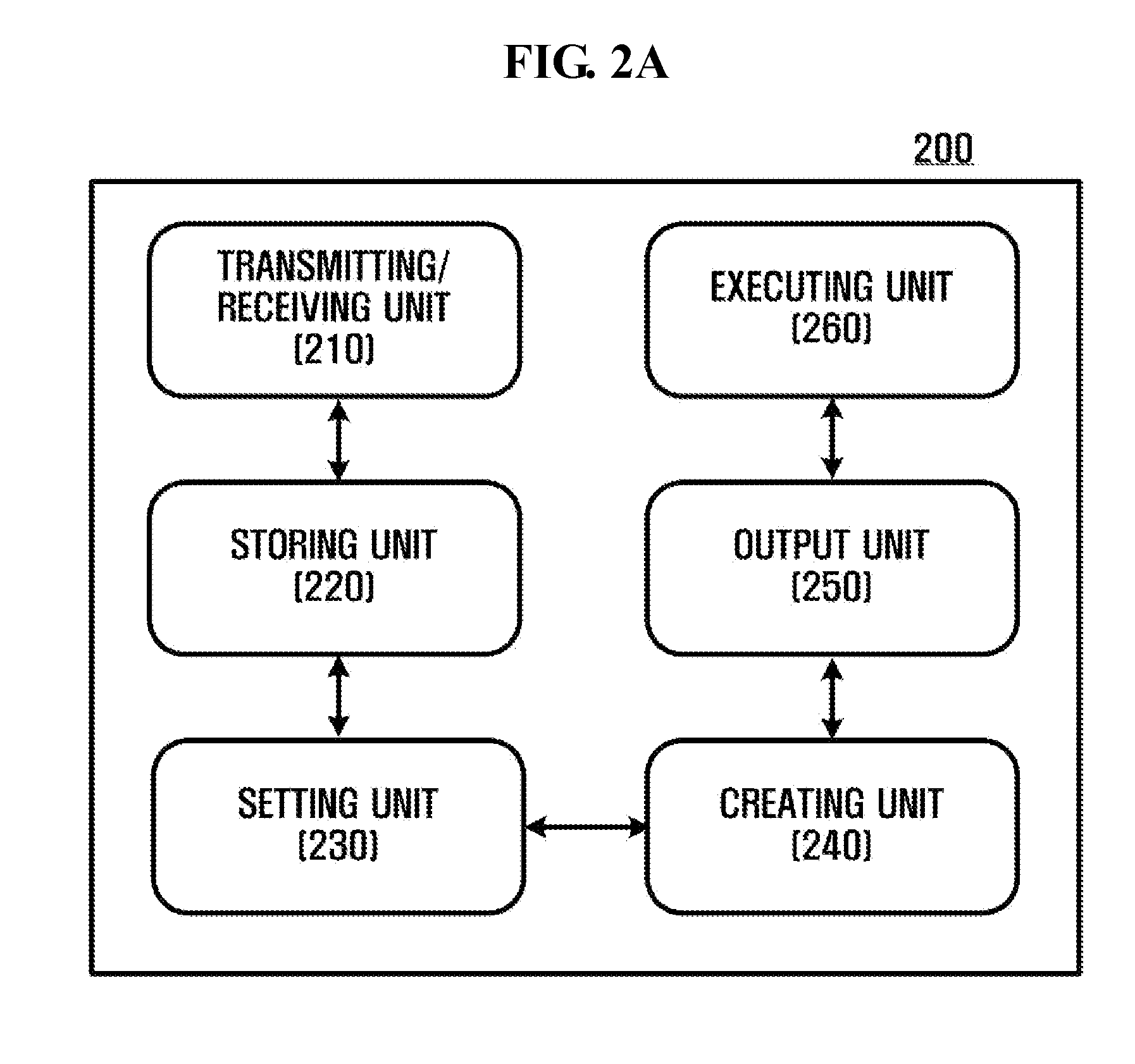

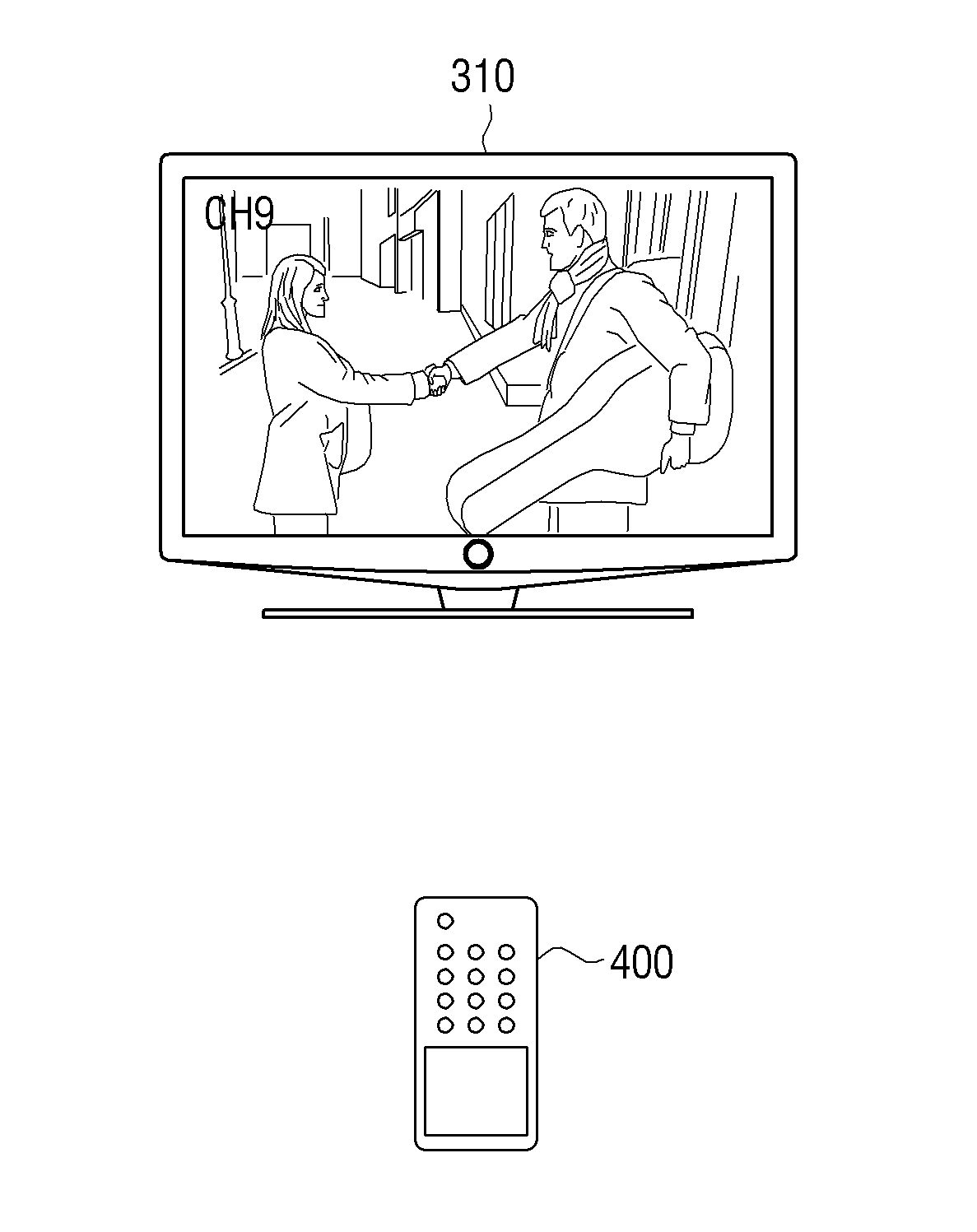

Apparatus and method for operating macro command and inputting macro command

InactiveUS20080228289A1Television system detailsColor television detailsComputer hardwareControl signal

Disclosed is provided an apparatus and a method for operating a macro command and inputting a macro command, wherein the apparatus including a storing unit storing control signals received from a control device for selecting of a menu item of a host device, a creating unit creating the macro command combined with the control signals, and an executing unit reading the macro command and executing functions corresponding to the respective menu item of the host device according to a combination sequence of the control signals included in the read macro command.

Owner:SAMSUNG ELECTRONICS CO LTD

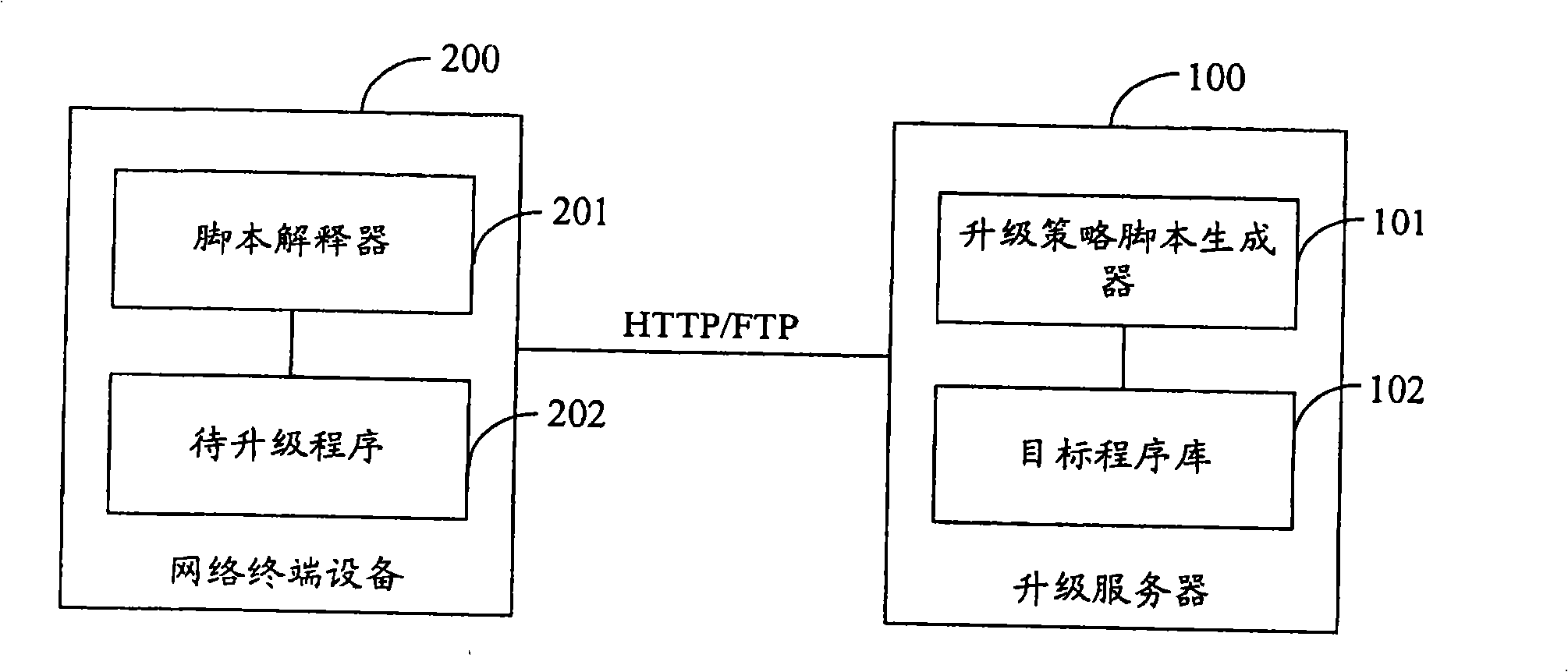

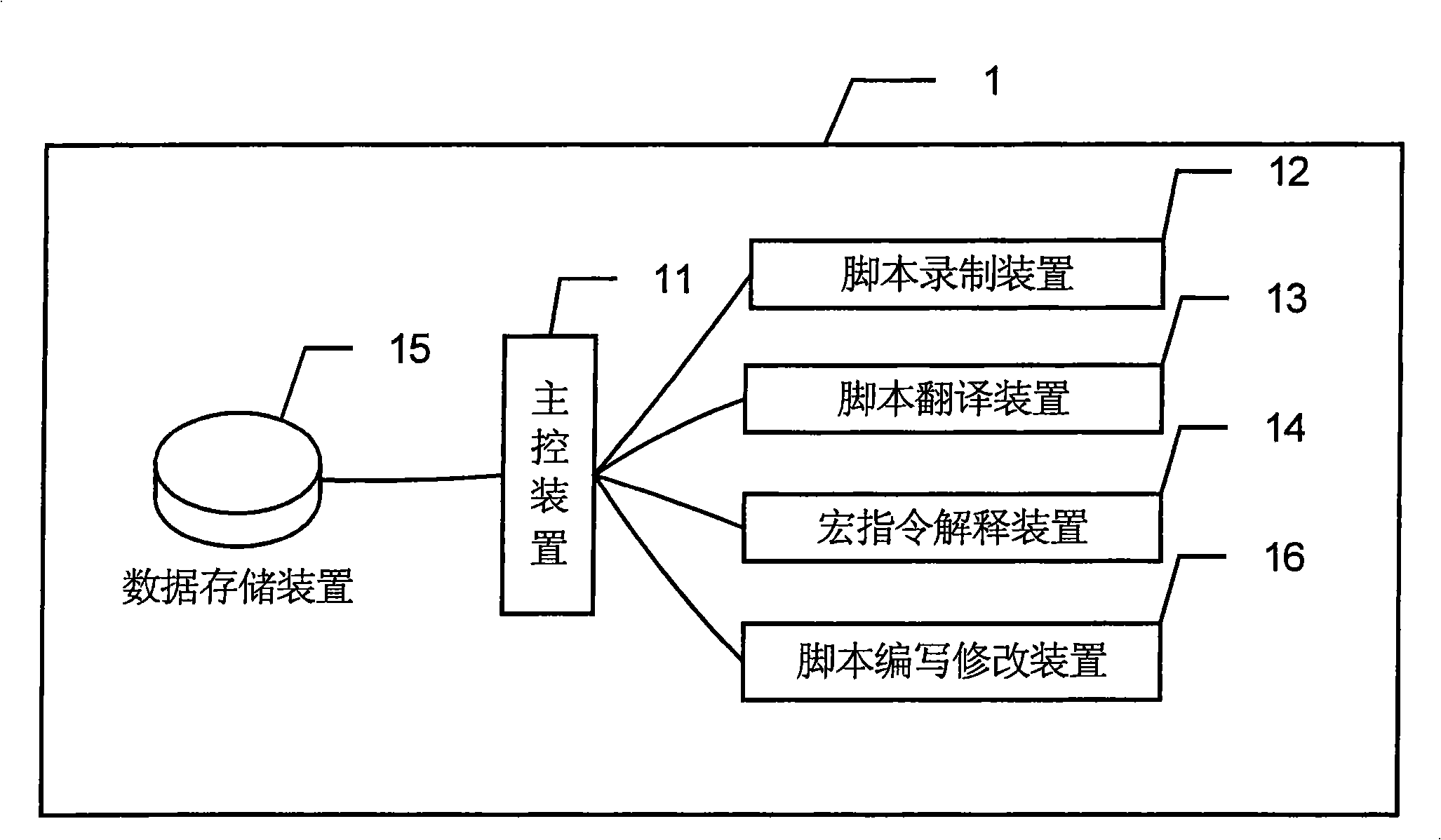

Multi-terminal mode script device and data processing method and automatization test system

InactiveCN101316201ALow costImprove scalabilitySoftware testing/debuggingData switching networksBasic serviceMacro instruction

The invention relates to a script device, a data processing method and an automated testing system based on a multi-terminal mode. The script device communicates with a basic service terminal and includes a master control device, a macroinstruction interpretation device, a script translation device and a data storage device; the script translation device acquires an instruction set script from the data storage device by the master control device and translates script instructions into macroinstruction or operation at a basic service terminal one by one; the macroinstruction interpretation device restores the macroinstruction generated by the script translation device into the operation adapted to the terminal mode of the basic service terminal by communicating with the basic service terminal by the master control device. The same set of the scripts of the invention can adapt to the application program interface of different terminal modes, and the user only needs to maintain one set of the scripts after a test case is designed so as to realize the tests on various terminal modes.

Owner:INDUSTRIAL AND COMMERCIAL BANK OF CHINA

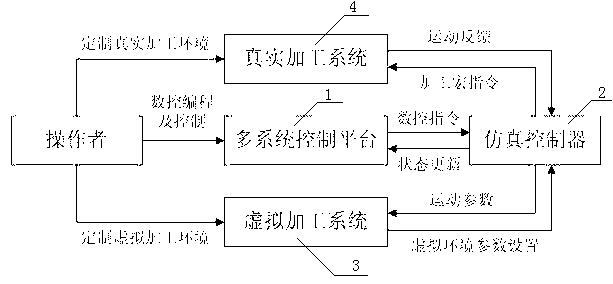

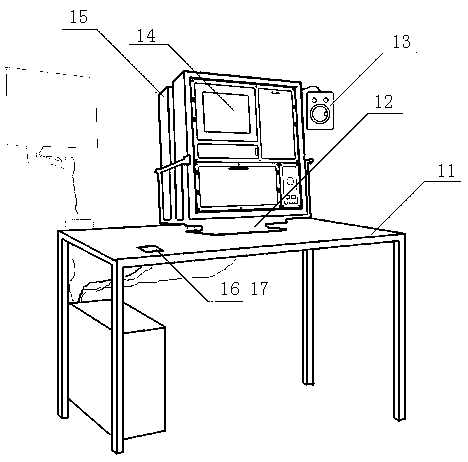

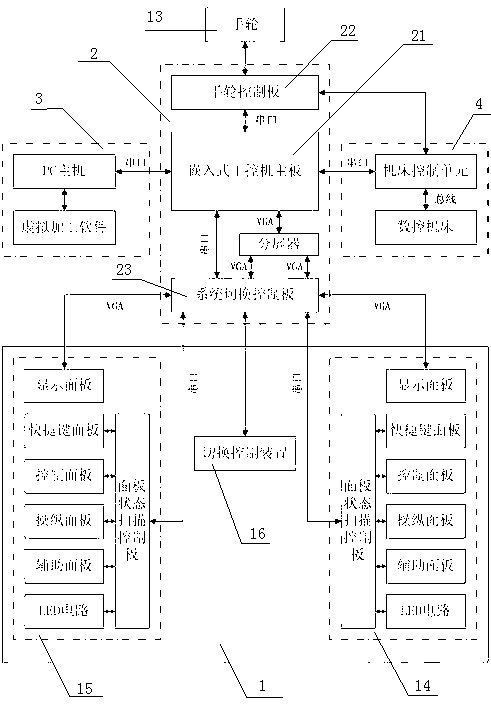

Method and system for simulating multisystem synchronous numerical-control processing

InactiveCN103236217ALearn about the training experienceSolve repair machining simulation problemsEducational modelsVirtual machiningControl system

The invention relates to a method and a system for simulating multisystem synchronous numerical-control processing, and belongs to the field of simulating training of numerical-control processing. The method comprises the following steps of customizing a virtual processing environment by a virtual processing system by an operator, and customizing a real processing environment by a real processing system; selecting a numerical-control system panel through a multisystem control platform to carry out numerical-control programming and controlling, encoding a numerical-control instruction, sending to a simulation controller, and enabling the simulation controller to simulate and calculate; on one hand, sending movement parameters of a cutter to the virtual processing system to complete virtual processing; and on the other hand, sending a processing macro instruction to the real processing system, so as to control a machine tool to complete the practical processing of blanks or repairing pieces. The method and the system have the advantages that the design concept is advanced, the function is practical, the cost is low, the deployment is convenient, the system compatibility is good, the group training method is flexible and variable, the processing process is visual and accurate, the human-computer interaction is good, the operation reality of a user is high, the user experience can be obviously changed, and the like.

Owner:PLA ARMORED FORCE TECH COLLEGE

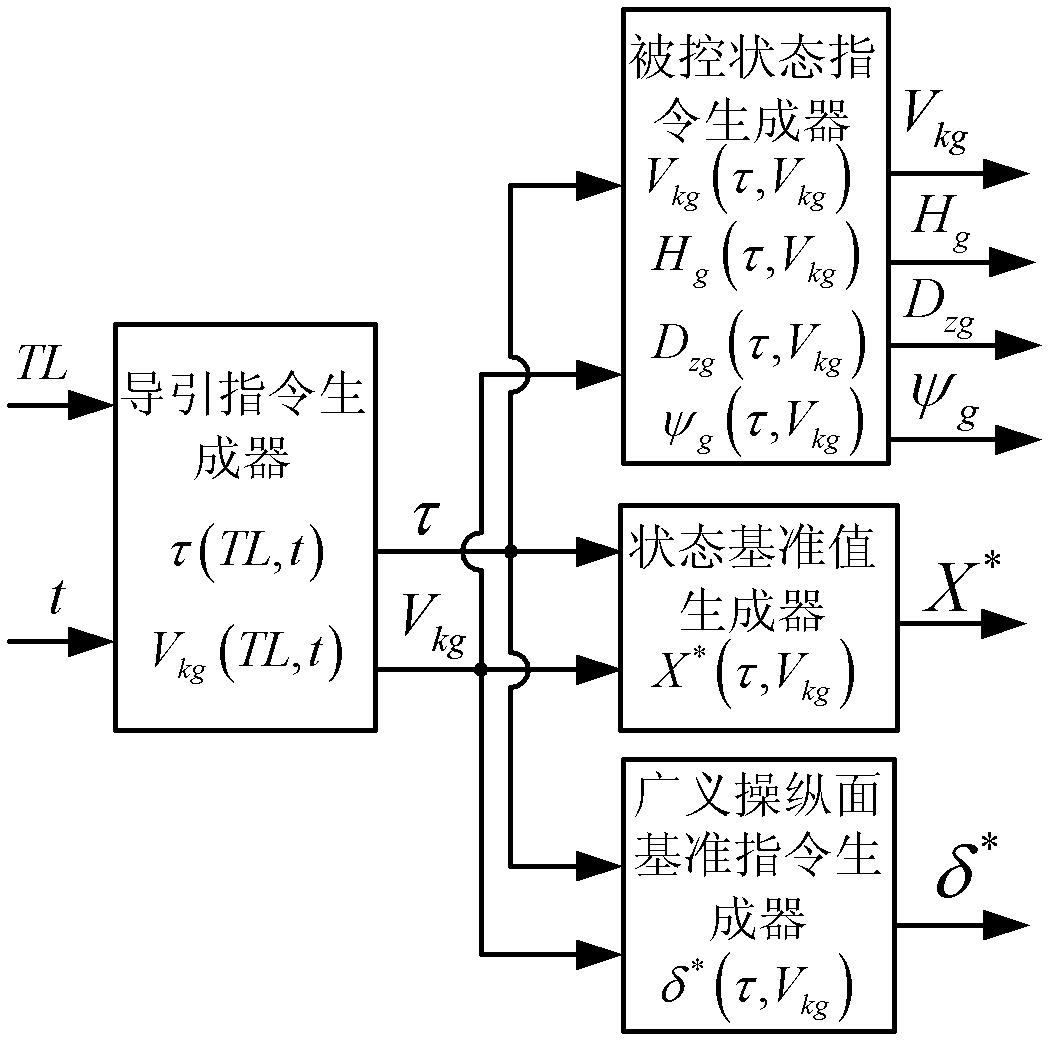

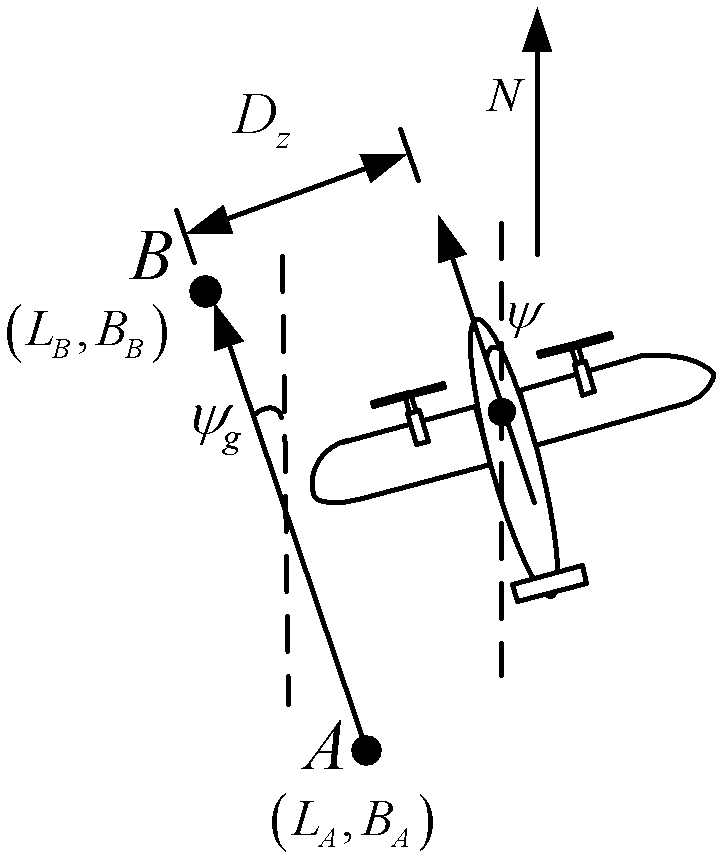

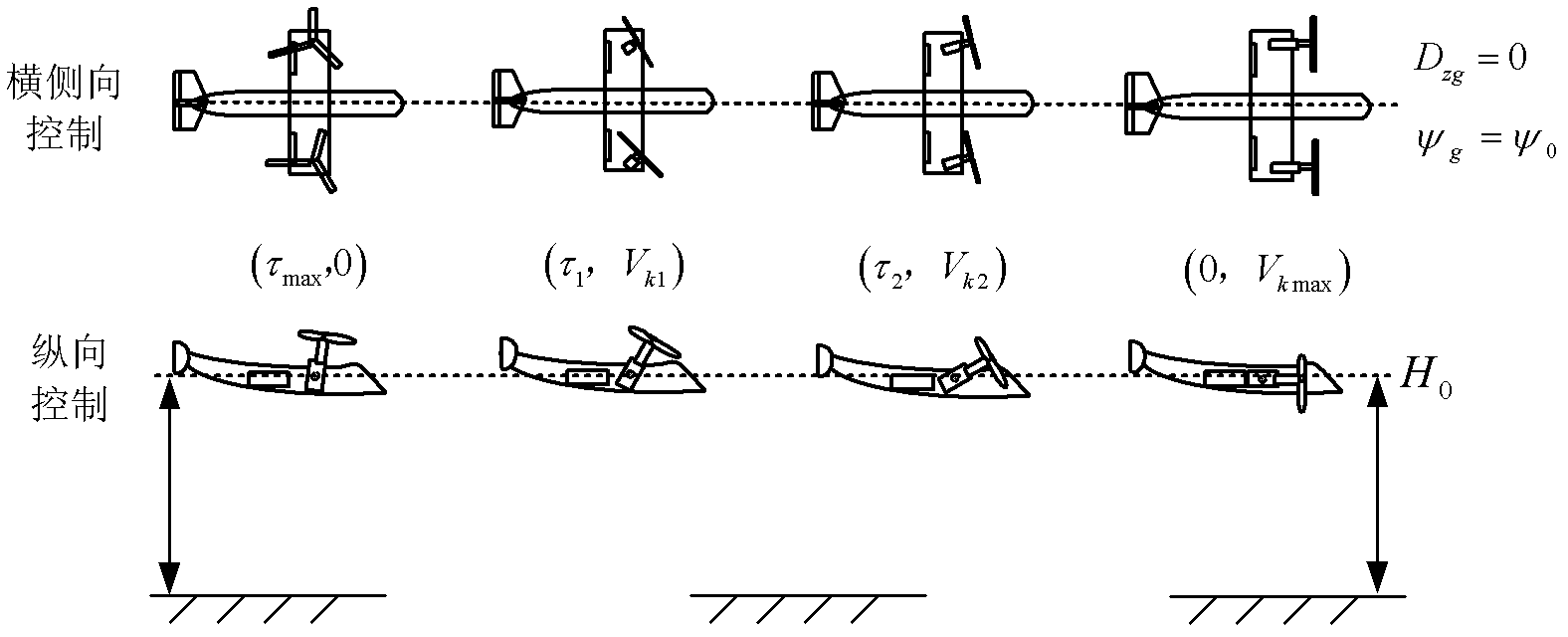

A generalized instruction generator and instruction generation method for variable flight mode unmanned aerial vehicle

InactiveCN102289207AReasonable conversion strategySmooth transition strategySimulator controlVehicle position/course/altitude controlControl vectorCurve fitting

The invention provides a macro instruction generator for an unmanned aerial vehicle with a variable flying mode and an instruction generation method for the macro instruction generator. The instruction generator comprises a guide instruction generator, a controlled state instruction generator, a state reference value generator and a macro control surface reference instruction generator. Balancing of a mode conversion process is equivalent to the balancing of various combined states in a sequence consisting of tilt angles and desired pitching angles; and in a specific tilt angle and desired pitching angle combined state, iterative optimization balancing is instructed by a cost function, so that balanced values of a state vector and a control vector of the macro control surface are changed stably along with the tilt angle and an air speed instruction. All inner functions of the guide instruction generator, the controlled state instruction generator, the state reference value generator and the macro control surface reference instruction generator are established by adopting a segmental curve fitting method according to a balanced result sequence. The iterative optimization balancing and the curve fitting are realized efficiently and accurately by using matrix laboratory (matlab) math software.

Owner:BEIHANG UNIV

Pop-compare micro instruction for repeat string operations

ActiveUS20050177705A1Runtime instruction translationDigital computer detailsString operationsOperand

A microprocessor apparatus is provided for performing a pop-compare operation. The microprocessor apparatus includes paired operation translation logic, load logic, and execution logic. The paired operation translation logic receives a macro instruction that prescribes the pop-compare operation, and generates a pop-compare micro instruction. The pop-compare micro instruction directs pipeline stages in a microprocessor to perform the pop-compare operation. The load logic is coupled to the paired operation translation logic. The load logic receives the pop-compare micro instruction, and retrieves a first operand from an address in memory, where the address is specified by contents of a register. The register is prescribed by the pop-compare micro instruction. The execution logic is coupled to the load logic. The execution logic receives the first operand, and compares the first operand to a second operand.

Owner:IP FIRST

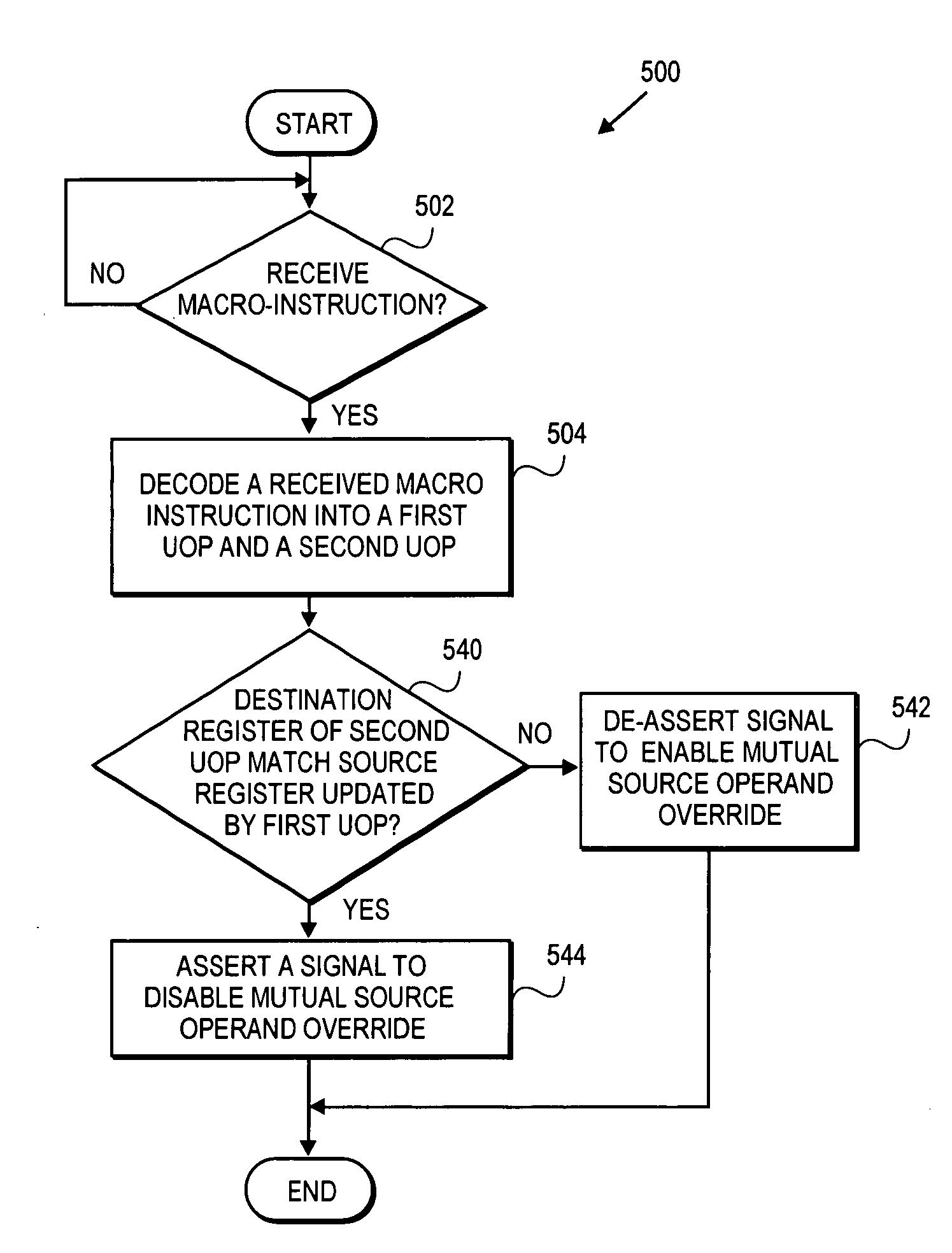

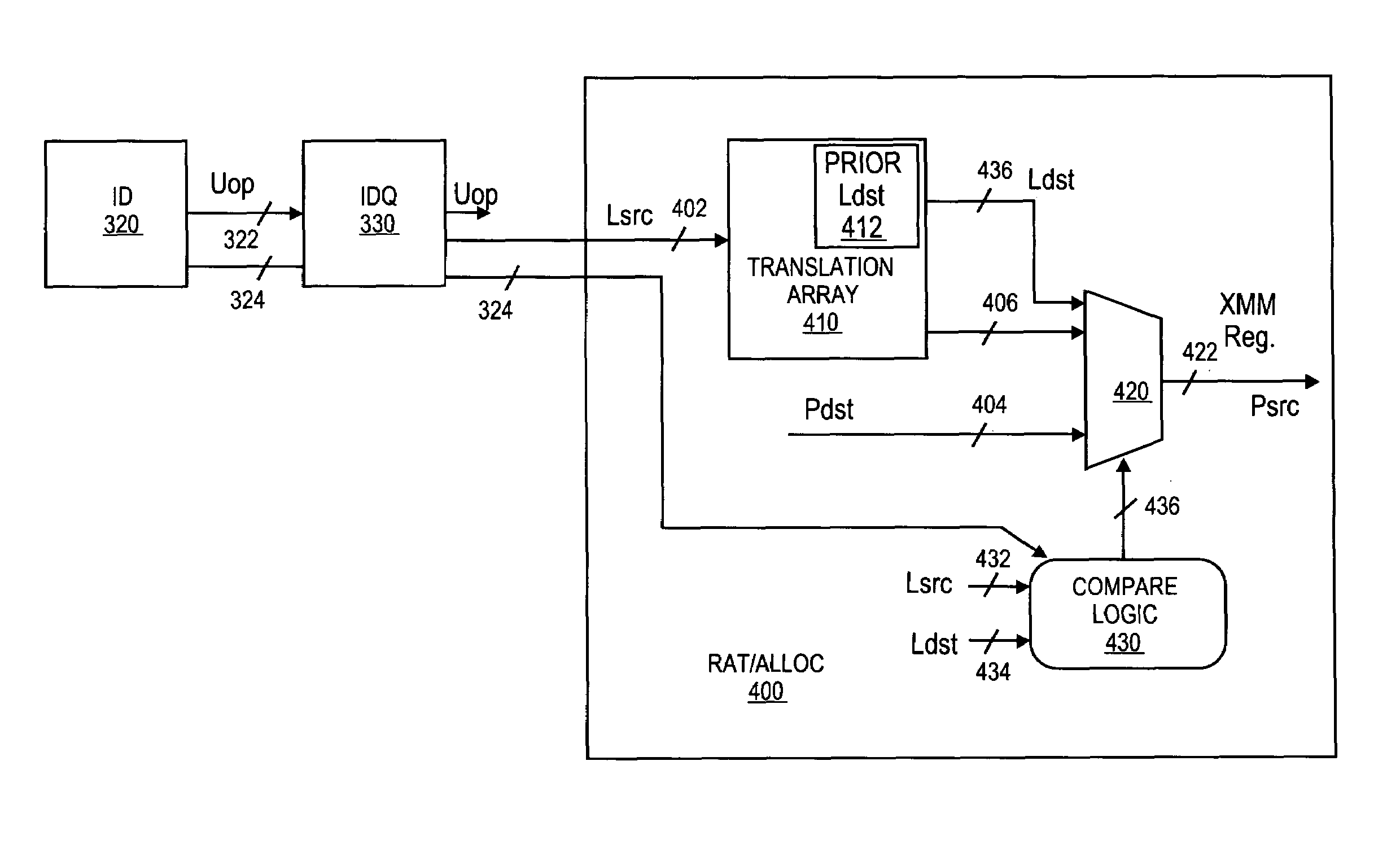

Apparatus and method for two micro-operation flow using source override

InactiveUS20050027967A1Improve performanceImprove efficiencyInstruction analysisRuntime instruction translationProgramming languageMicro-operation

A method and apparatus for a two micro-operation flow using source override. In one embodiment, the method includes the identification of a macro-instruction having one or more streaming single instruction multiple data extension type operands. Once received, the macro-instruction is decoded into a first micro-operation (uOP) and a second uOP. Once decoded, a signal is asserted to disable source operand override logic if the first micro-operation updates a logical destination register that matches a logical source register of the micro-operation. Otherwise, the mutual source override is active and executed by a register alias table (RAT) when uOP with matching logic source and destination register are detected in a same clock cycle. In doing so, macro-instructions having 128-bit operands may be processed using, for example, two uOPs (one for the lower half and one for the upper half) in a 64-bit implementation, while preserving the atomicity of the original instruction.

Owner:INTEL CORP

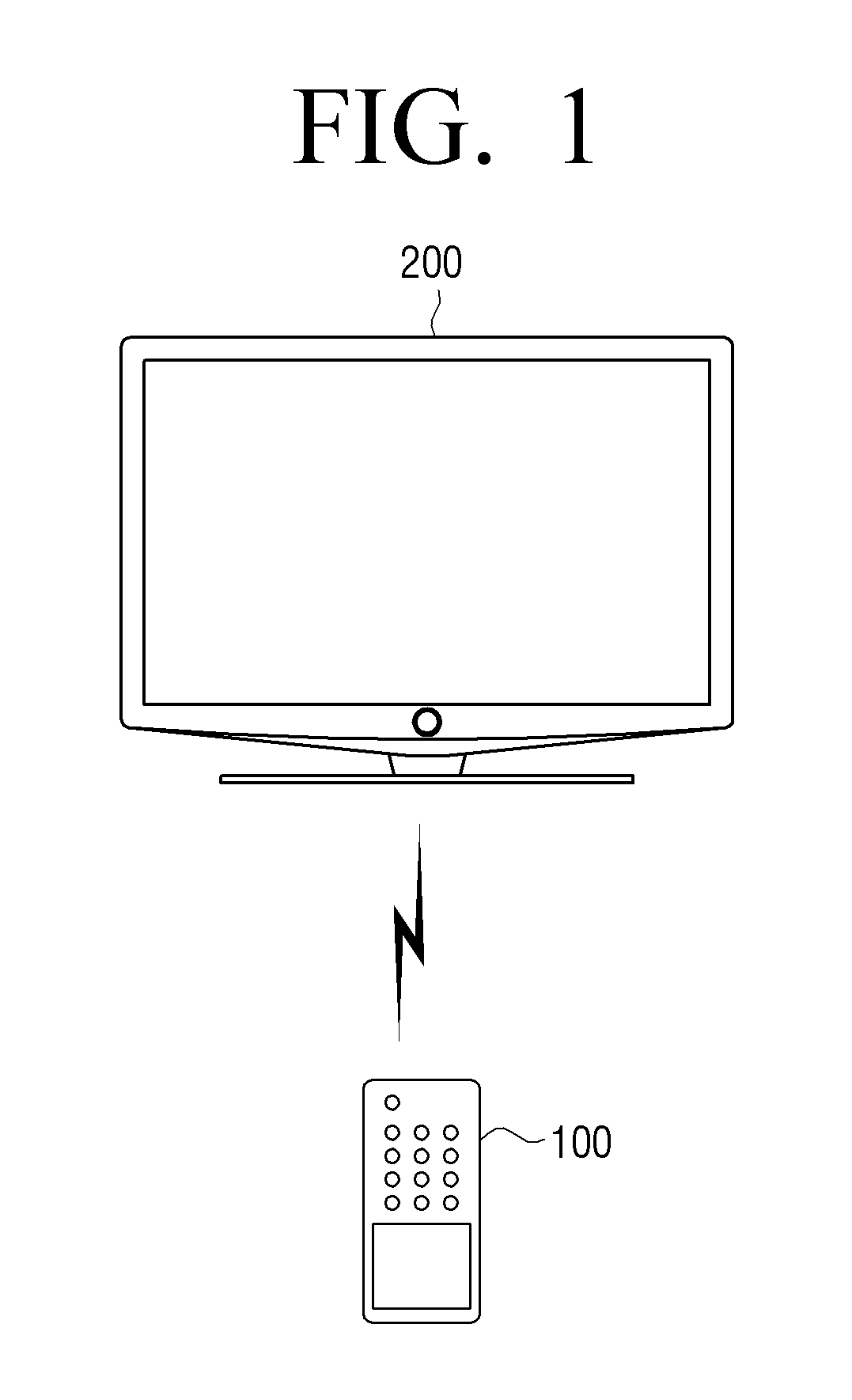

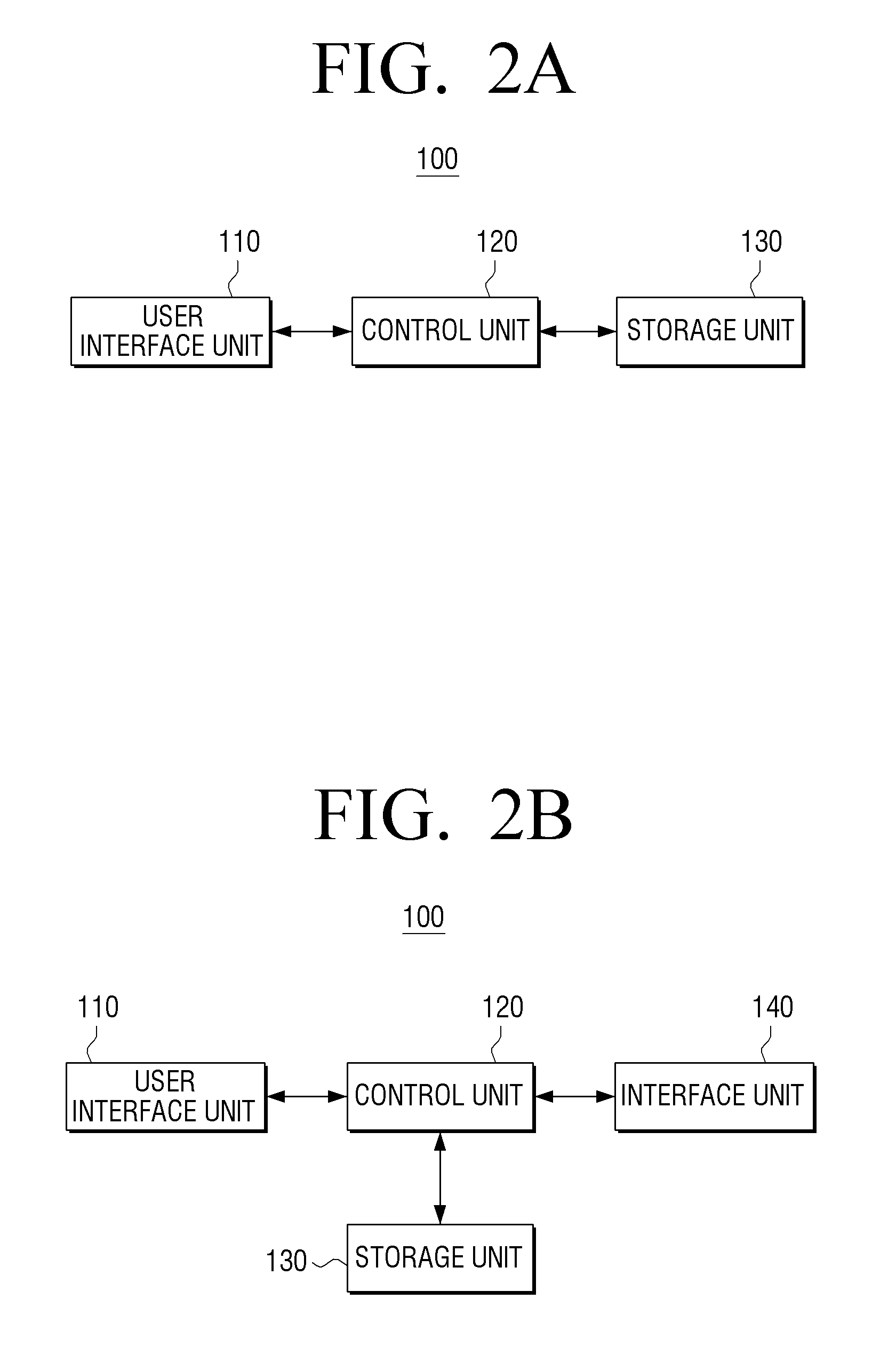

Remote controller apparatus, broadcast receiving apparatus and method for controlling the same

ActiveUS20130070154A1Improve convenienceAvoid failureTelevision system detailsTelemetry/telecontrol selection arrangementsMacro instructionBroadcasting

A remote controller apparatus for controlling a broadcast receiving apparatus is provided, in which the remote controller apparatus includes a storage unit, a user interface unit which sequentially receives at least one control instruction relating to controlling the broadcast receiving apparatus, an interface unit which transmits the at least one control instruction received via the user interface unit to the broadcast receiving apparatus, and which receives status information relating to the broadcast receiving apparatus based on the at least one control instruction, and a control unit causes the status information to be stored by the storage unit, and if the instruction relating to setting macro functionality is received via the user interface unit, generates a macro instruction relating to controlling the broadcast receiving apparatus based on the status information and causes the generated macro instruction to be stored by the storage unit.

Owner:SAMSUNG ELECTRONICS CO LTD

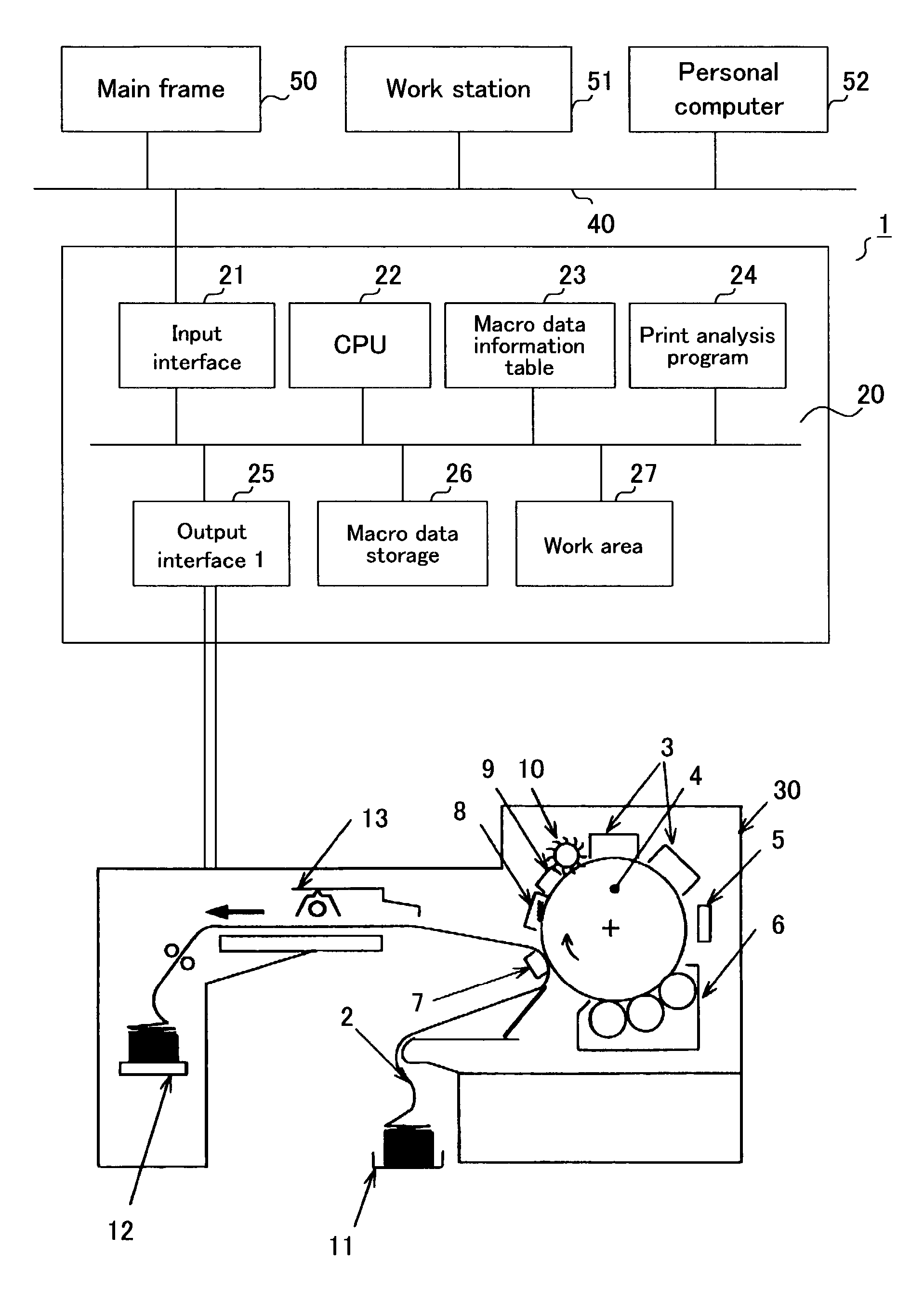

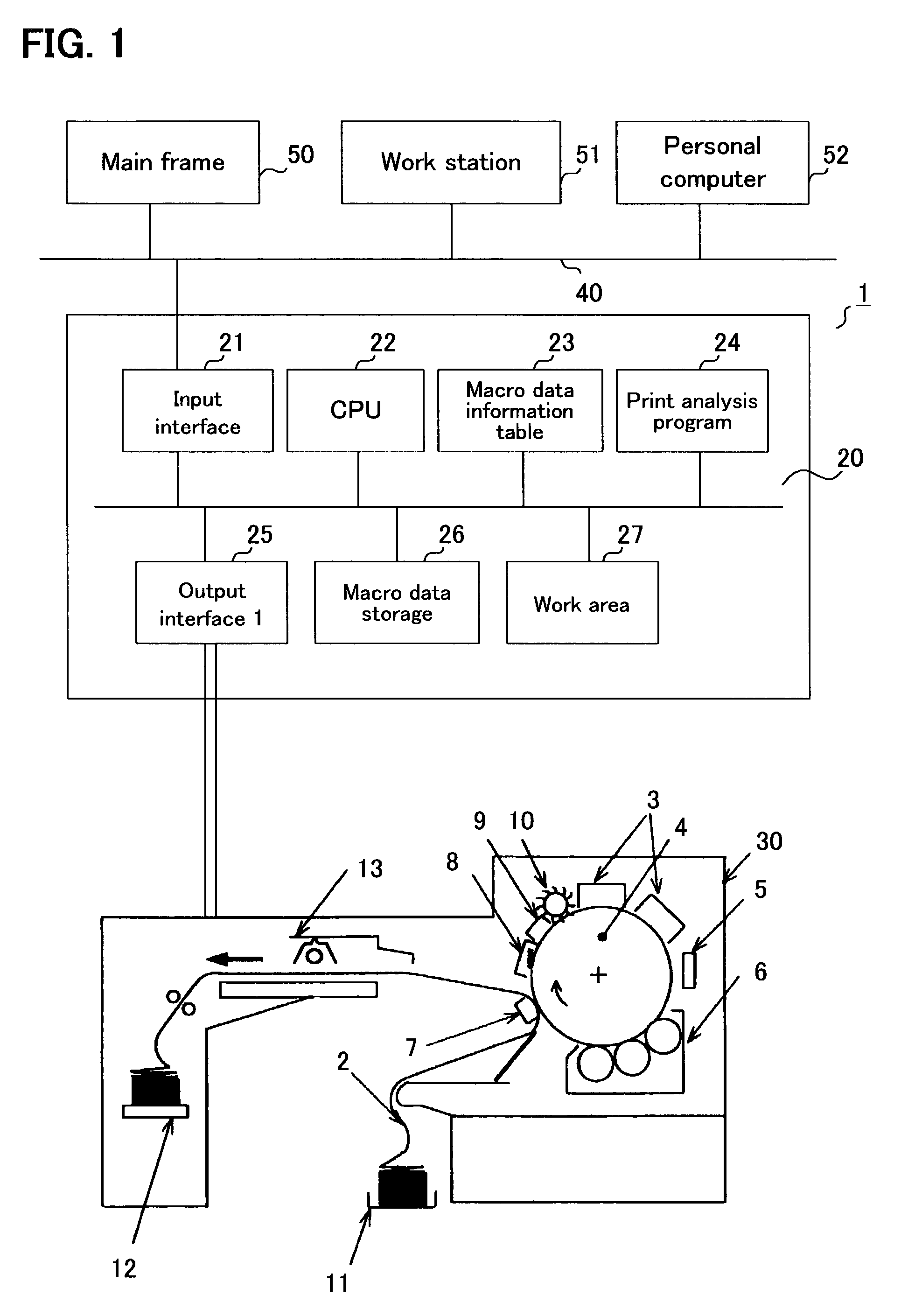

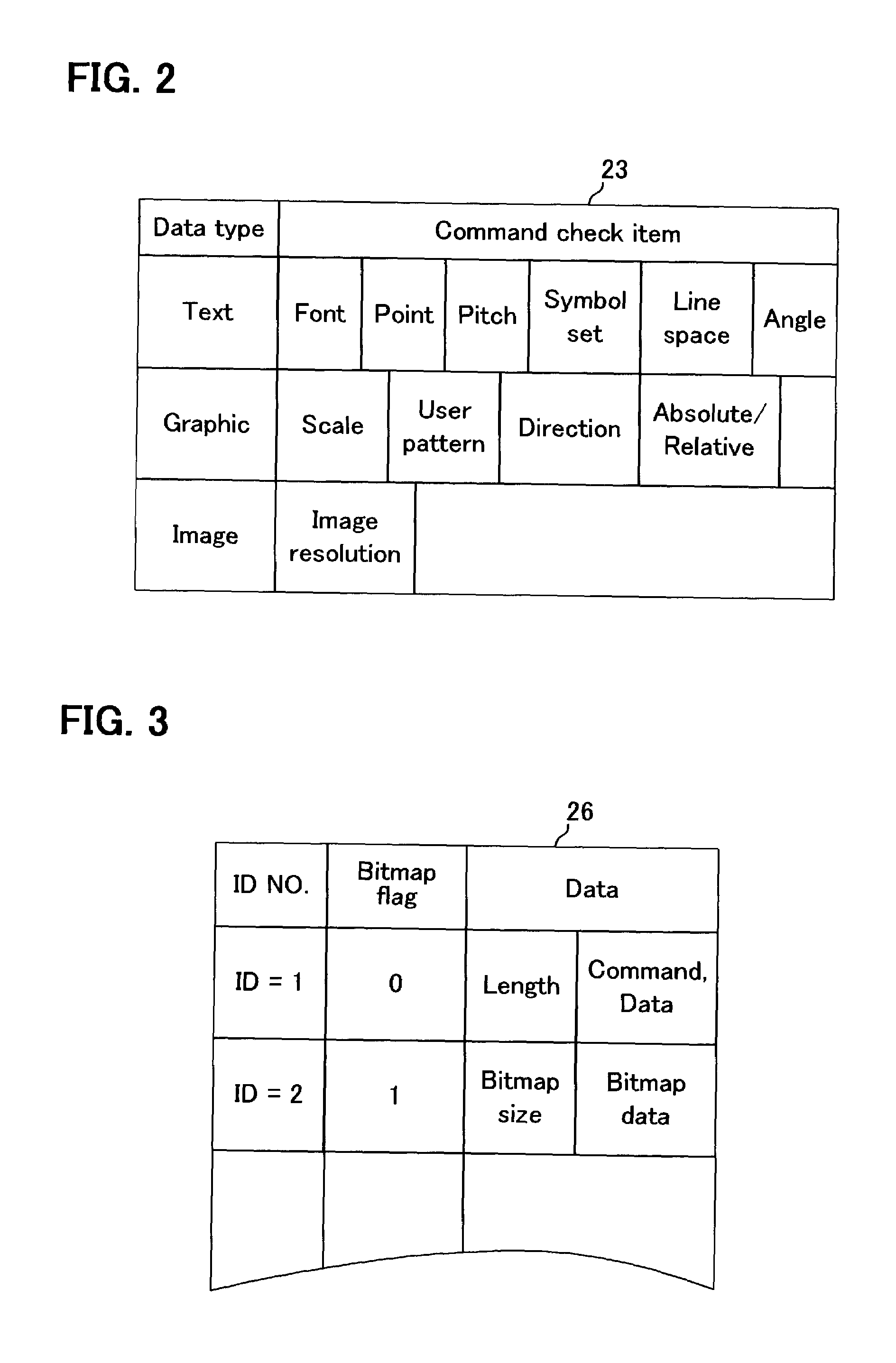

Print controller, print control method and printer including determination to store macro as instruction or bitmap

InactiveUS7164484B2High speed machiningEasy to determineDigital computer detailsVisual presentation using printersMacro instructionComputer science

A printer controller obtains high-speed bitmap generation processing while maintaining flexibility in macro definition when generating bitmap data from a macro-formed data. A processing unit calls macro data from a memory storing macro data to generate bitmap data. The processing unit determines effectiveness of bitmapping the macro instruction, to store into memory the bitmap data only when the bitmapped data is determined effective. Even in case of macro definition having degree of freedom, the data can be retained in a bitmap form. This enables to omit command analysis and expansion next time or after in macro control having flexibility in macro definition.

Owner:FUJIFILM BUSINESS INNOVATION CORP

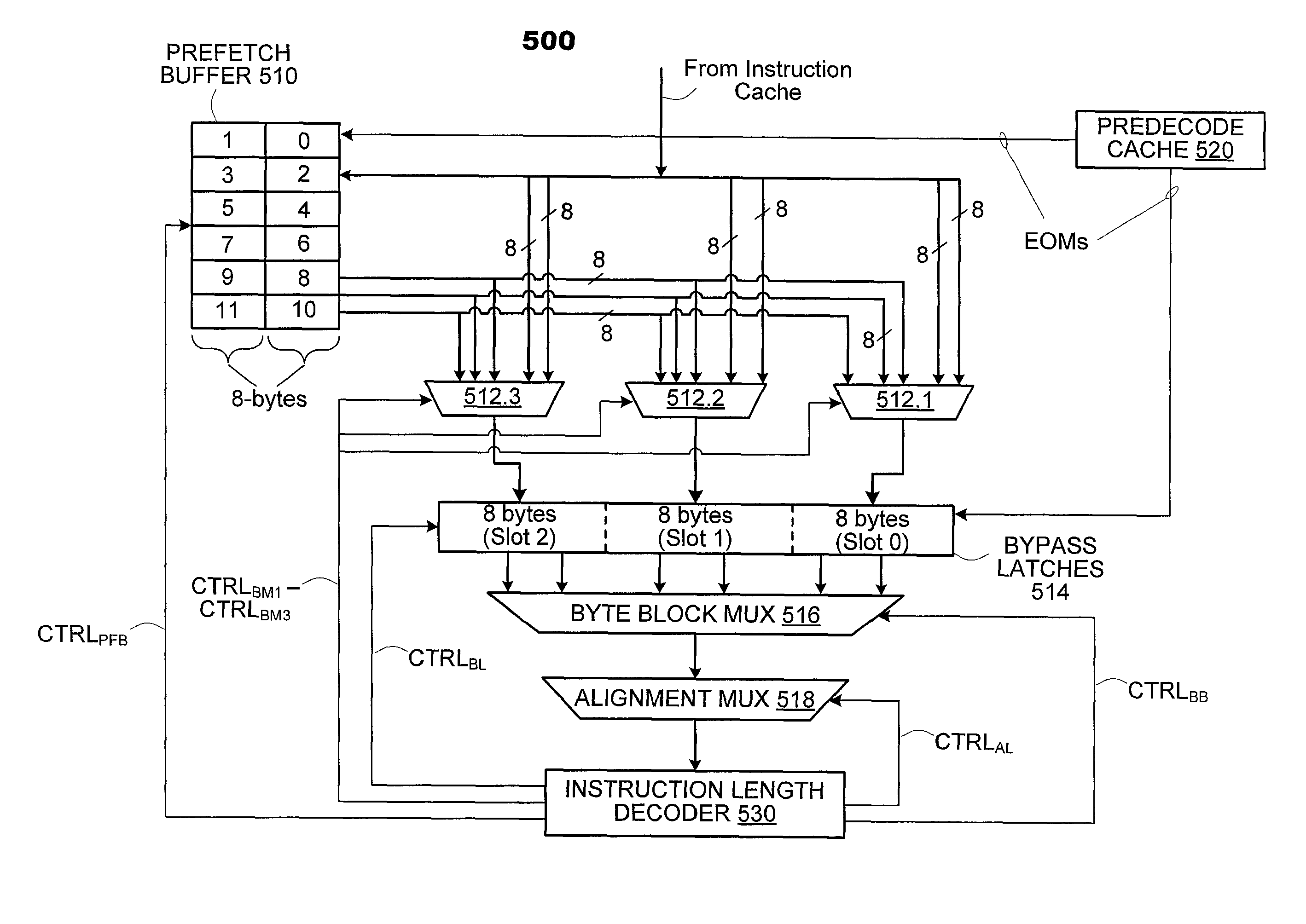

Instruction and logic to length decode X86 instructions

ActiveUS8930678B2Runtime instruction translationDigital computer detailsMultiplexerParallel computing

Techniques to increase the consumption rate of raw instruction bytes within an instruction fetch unit. An instruction fetch unit according to embodiments of the present invention may include a prefetch buffer, a set of bypass multiplexers, an array of bypass latches, a byte-block multiplexer, an instruction alignment multiplexer, a predecode cache, and an instruction length decoder. Raw instruction bytes may be steered from the bypass latches into macro-instructions for consumption by the instruction length decoder, which may generate micro-instructions from the macro-instructions. Embodiments of the present invention may de-couple a latency for reading raw instruction bytes from the prefetch buffer from consuming raw instruction bytes by the instruction length decoder.

Owner:INTEL CORP

Frameworks for generation of Java macro instructions for storing values into local variables

InactiveUS7039904B2Efficient executionReduce in quantitySoftware engineeringSoftware simulation/interpretation/emulationLimited resourcesLocal variable

Techniques for generation of Java macro instructions suitable for use in Java computing environments are disclosed. As such, the techniques can be implemented in a Java virtual machine to efficiently execute Java instructions. As will be appreciated, a Java macro instruction can be substituted for two or more Java Bytecode instructions. This, in turn, reduces the number of Java instructions that are executed by the interpreter. As a result, the performance of virtual machines, especially those operating with limited resources, is improved. A Java macro instruction can be generated for conventional Java instruction sequences or sequences of Java instruction that are provided in a reduced set of instruction. In any case, sequences that are frequently encountered can be replaced by a Java macro instruction. These sequences are typically encountered when Java objects are instantiated, during programming loops, and when a local variables are assigned a value.

Owner:ORACLE INT CORP

Merge microinstruction for minimizing source dependencies in out-of-order execution microprocessor with variable data size macroarchitecture

ActiveUS7937561B2Runtime instruction translationDigital computer detailsGeneral purposeComputer architecture

A microprocessor processes a macroinstruction that instructs the microprocessor to write an 8-bit result into only a lower 8 bits of an N-bit architected general purpose register. An instruction translator translates the macroinstruction into a merge microinstruction that specifies an N-bit first source register, an 8-bit second source register, and an N-bit destination register to receive an N-bit result. The N-bit first source register and the N-bit destination register are the N-bit architected general purpose register. An execution unit receives the merge microinstruction and responsively generates the N-bit result to be subsequently written to the N-bit architected general purpose register even though the macroinstruction only instructs the microprocessor to write the 8-bit result into the lower 8 bits of the N-bit architected general purpose register. Specifically, the execution unit directs the 8-bit result into the lower 8 bits of the N-bit result and directs the upper N-8 bits of the N-bit first source register into corresponding upper N-8 bits of the N-bit result.

Owner:VIA TECH INC

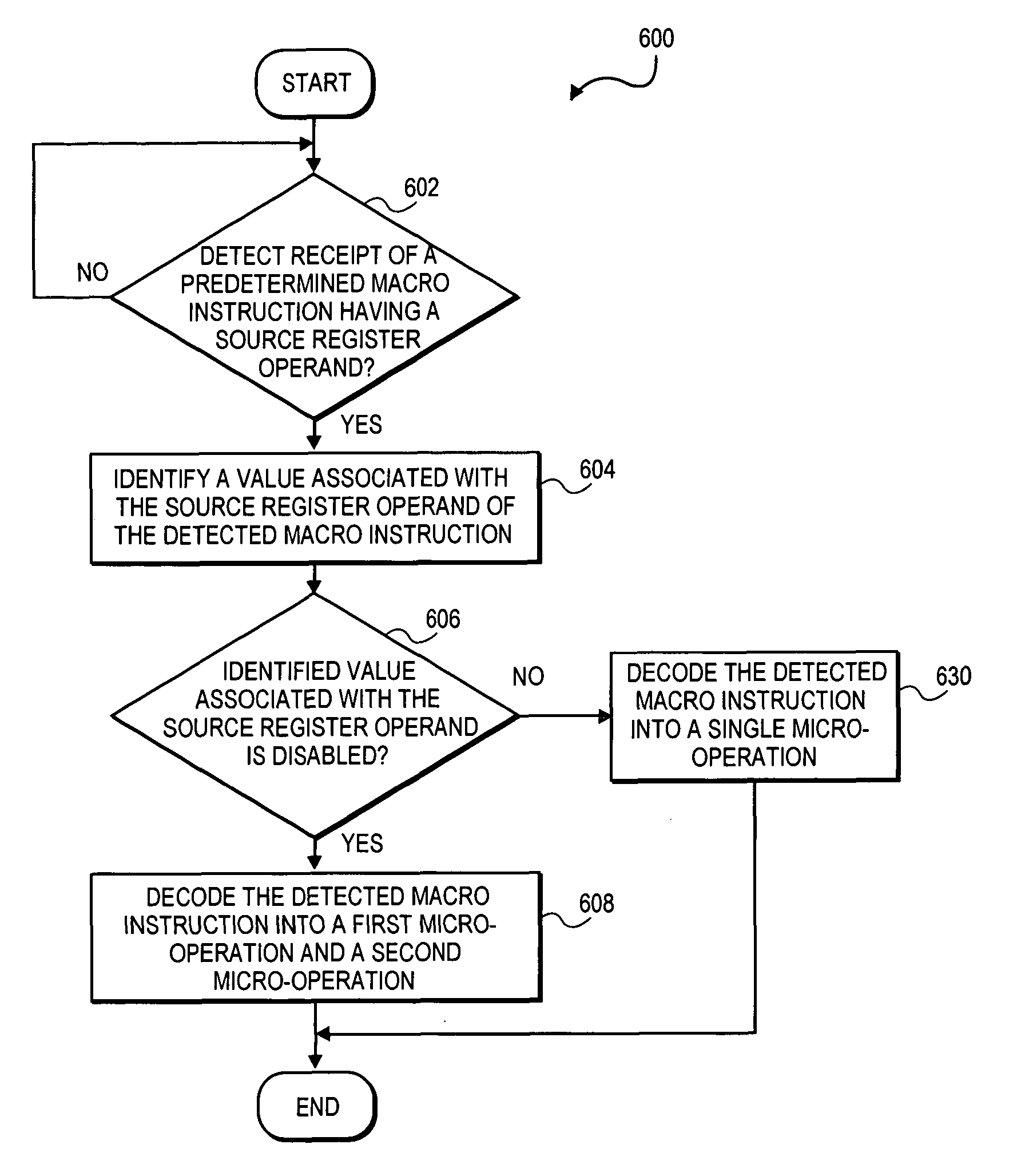

Apparatus and method for redundant zero micro-operation removal

InactiveUS20050027964A1Improve performanceImprove efficiencyInstruction analysisRuntime instruction translationMicro-operationExecution unit

A method and apparatus for redundant zero micro-operation removal. In one embodiment, the method includes the identification of a predetermined macro-instruction. Once identified, a value associated with a source register operand of the identified macro-instruction is determined. Once determined, the identified macro-instruction is decoded into a first macro operation and a second micro-operation if the determined value is not set. Otherwise, the identified macro-instruction is decoded into a single micro-operation if the determined value is set. Accordingly, the method described prevents the generation of redundant micro-operations that use valuable resources, such as allocation slots, as well as execution units within the processor core.

Owner:INTEL CORP

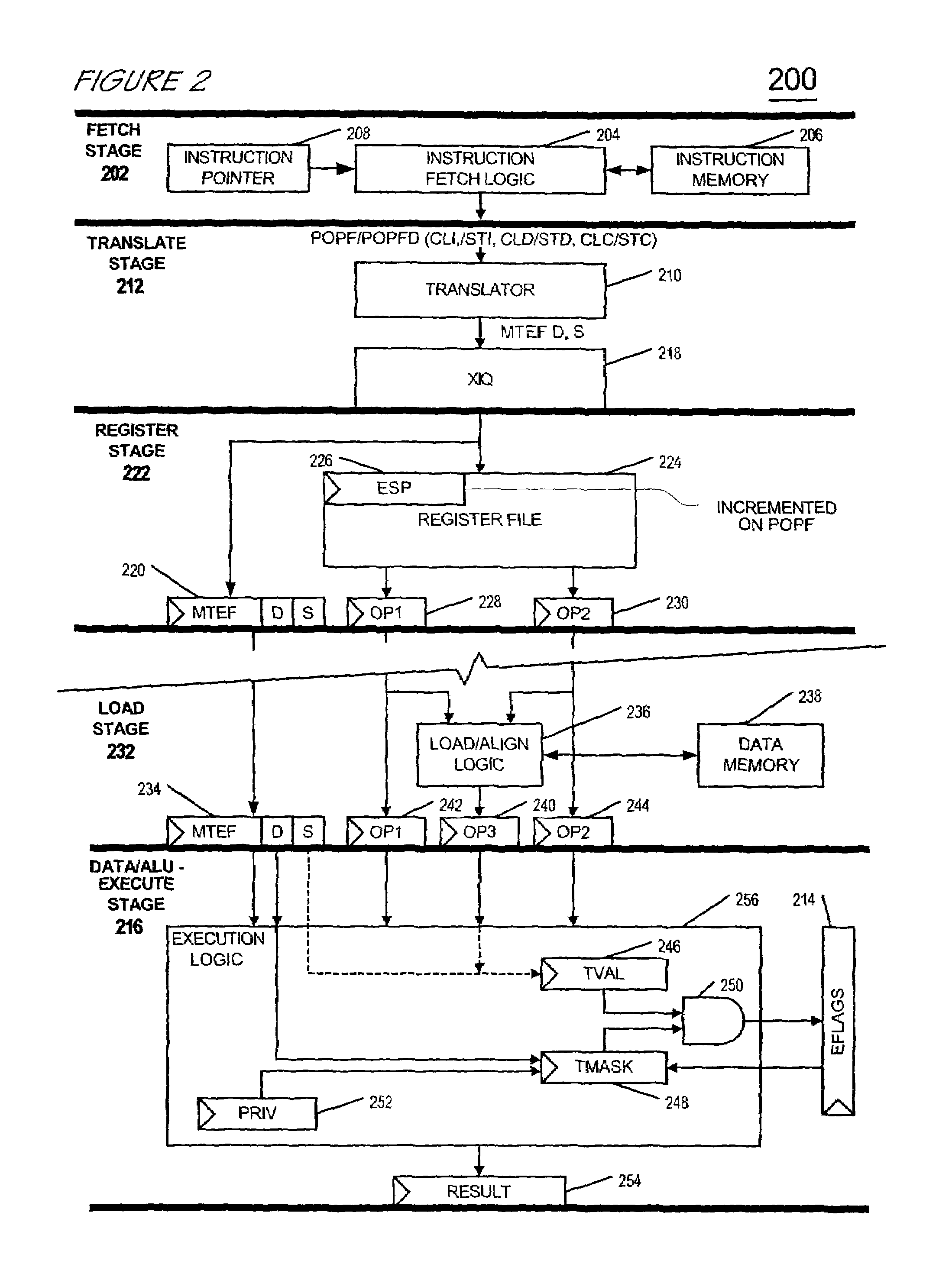

Apparatus and method for masked move to and from flags register in a processor

ActiveUS7058794B2Reduce delaysRuntime instruction translationGeneral purpose stored program computerProcessor registerMacro instruction

Owner:IP FIRST

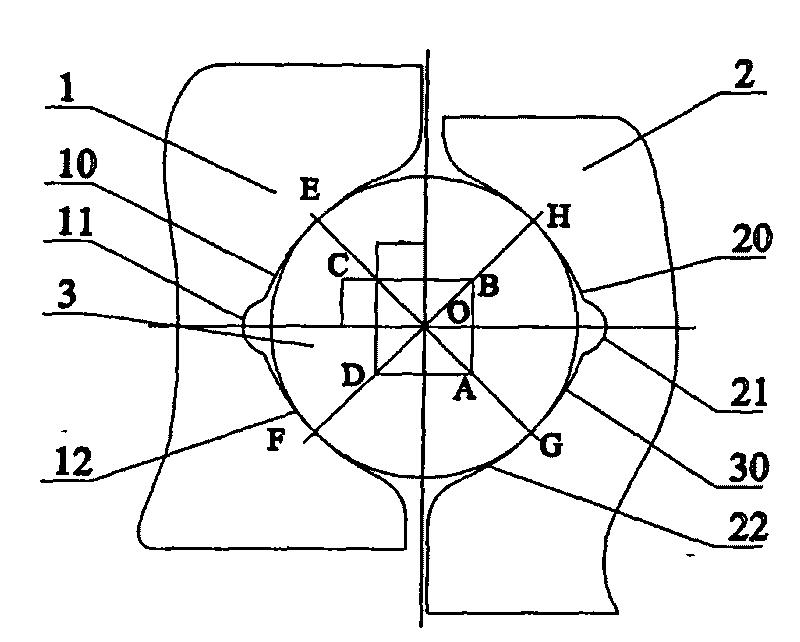

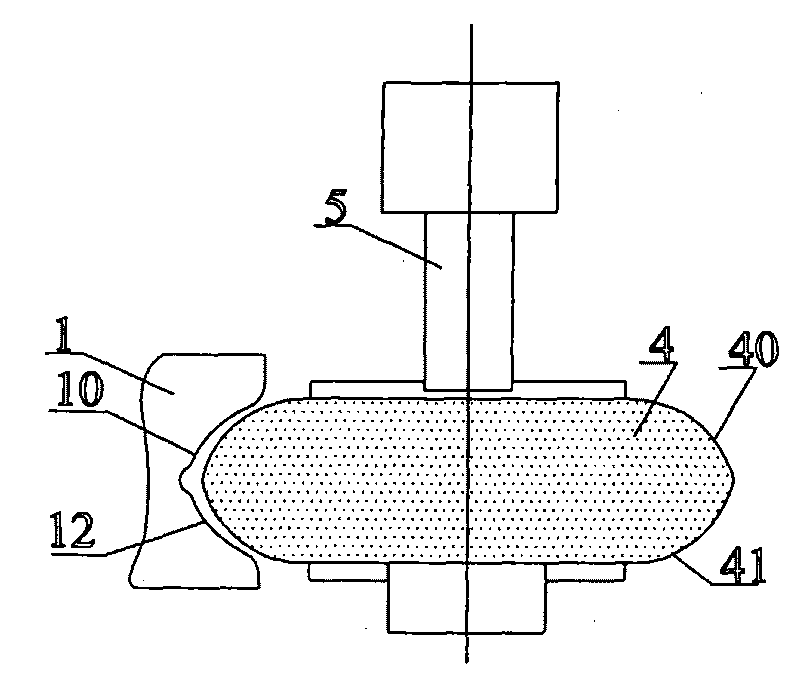

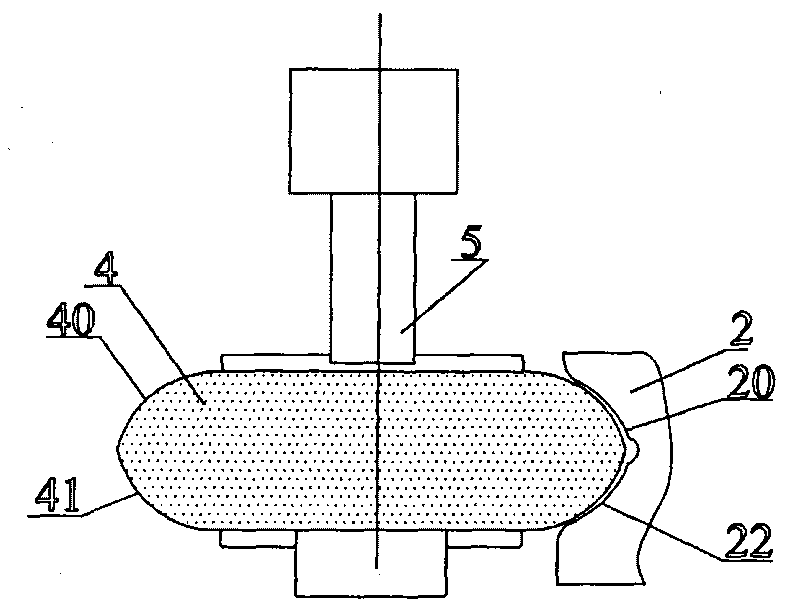

Grinding wheel dressing method used for slewing support roller path grinding

InactiveCN101712139AGood processing needsMeet the needs of trimming functionAbrasive surface conditioning devicesLinear motionEngineering

The invention relates to a processing method used for dressing a grinding wheel, in particular to a grinding wheel dressing method used for slewing support double circular roller path grinding, relating to the field of metal processing. In the dressing method, the rotation motion of the grinding wheel is taken as the main motion to form a principle axis S axis; the horizontal and vertical feeding linear motion of the grinding wheel is driven by the horizontal motion mechanism and the vertical motion mechanism of the grinding wheel to substitute the circular interpolating motion of the grinding wheel to form an X axis and a Z axis; the rotation of the diamond pen is driven by the diamond pen rotation motion mechanism to form a C axis; and the dressing of the whole grinding wheel is realized through the micro-segment dressing of the processing station after discretization, thus being capable of meeting the requirements of multispecies standard grinding wheel dressing functions and having the advantages of stable processing and stable accuracy; in the method, a macro instruction programming method is applied, and is a program compiling mode in which variables can be used for arithmetic operation, logic operation and function mixed operation, thus greatly simplifying program quantity and strengthening the processing and adaptive capabilities of the machine tool.

Owner:NANJING GONGDA CNC TECH

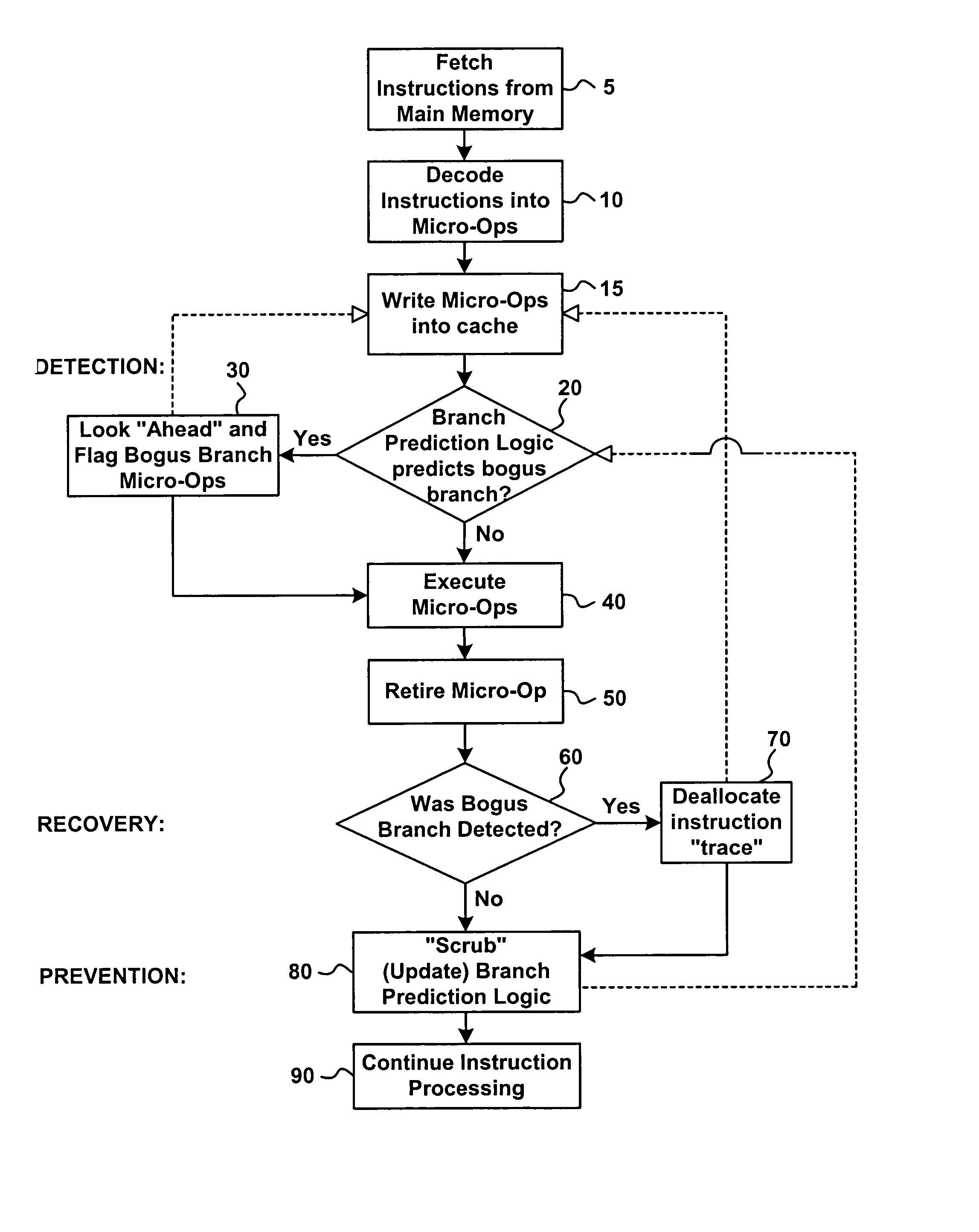

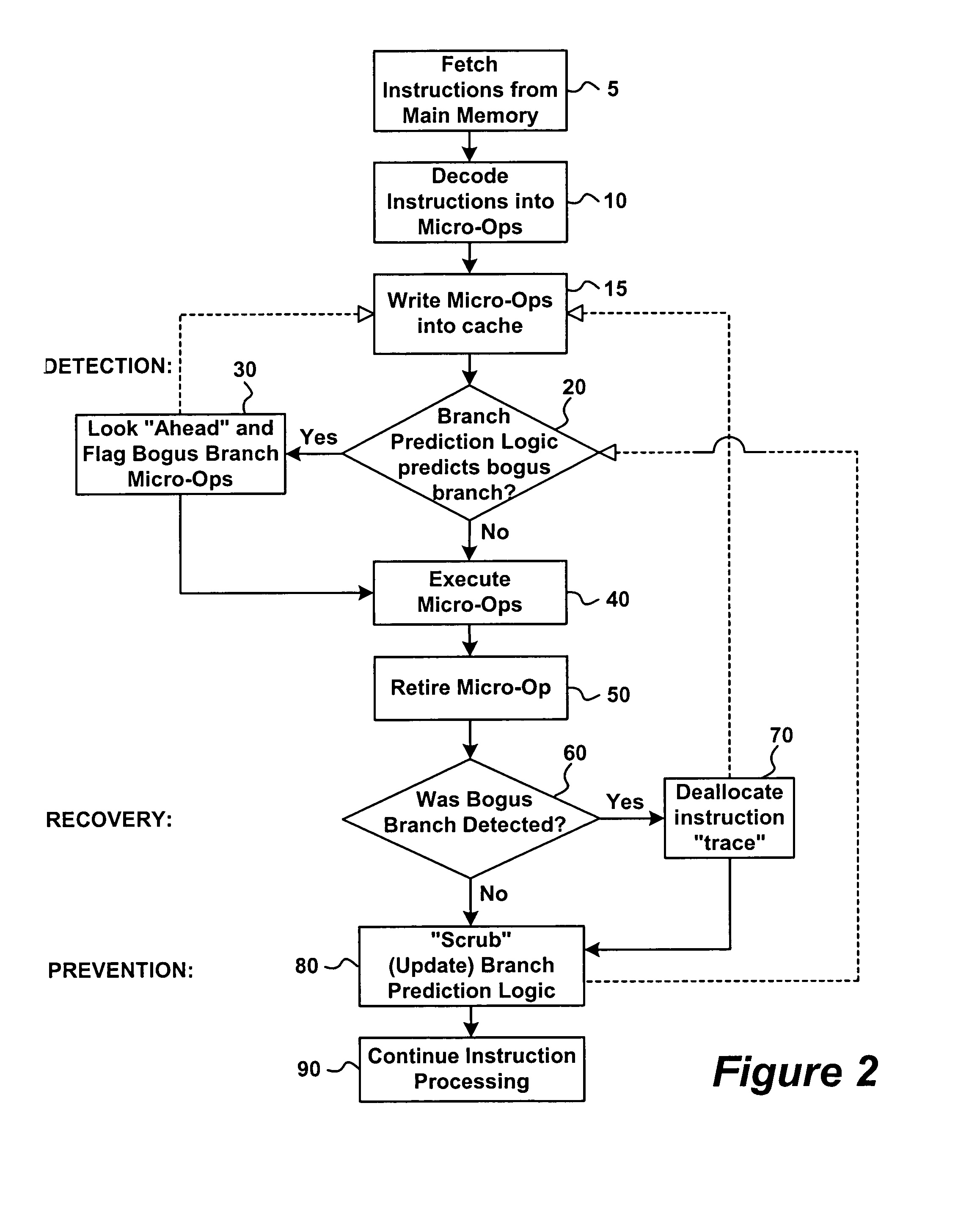

Detection, recovery and prevention of bogus branches

InactiveUS7334115B1Runtime instruction translationDigital computer detailsParallel computingMacro instruction

The present invention provides for a method and apparatus for the detection and prevention of and recovery from bogus branch predictions in a microprocessor. Micro-ops, decoded from a macro instruction, are stored in a decoded micro-op cache. Branch prediction logic determines whether a branch is bogus or not. If the branch taken was determined to be bogus, the present invention causes the micro-ops which descend from the original bogus branch micro-op instruction to be flagged and subsequently moved to the back-end of the processor for retirement. Further, the branch prediction logic (the branch prediction logic storage buffer) is updated as to what the actual direction of the branch was. In this manner then, bogus branches are detected, recovered from and further prevented.

Owner:INTEL CORP

Frameworks for generation of Java macro instructions for instantiating Java objects

InactiveUS7058934B2Efficient executionReduce in quantitySoftware engineeringProgram controlLimited resourcesLocal variable

Techniques for generation of Java macro instructions suitable for use in Java computing environments are disclosed. As such, the techniques can be implemented in a Java virtual machine to efficiently execute Java instructions. As will be appreciated, a Java macro instruction can be substituted for two or more Java Bytecode instructions. This, in turn, reduces the number of Java instructions that are executed by the interpreter. As a result, the performance of virtual machines, especially those operating with limited resources, is improved. A Java macro instruction can be generated for conventional Java instruction sequences or sequences of Java instruction that are provided in a reduced set of instruction. In any case, sequences that are frequently encountered can be replaced by a Java macro instruction. These sequences are typically encountered when Java objects are instantiated, during programming loops, and when a local variables are assigned a value.

Owner:ORACLE INT CORP

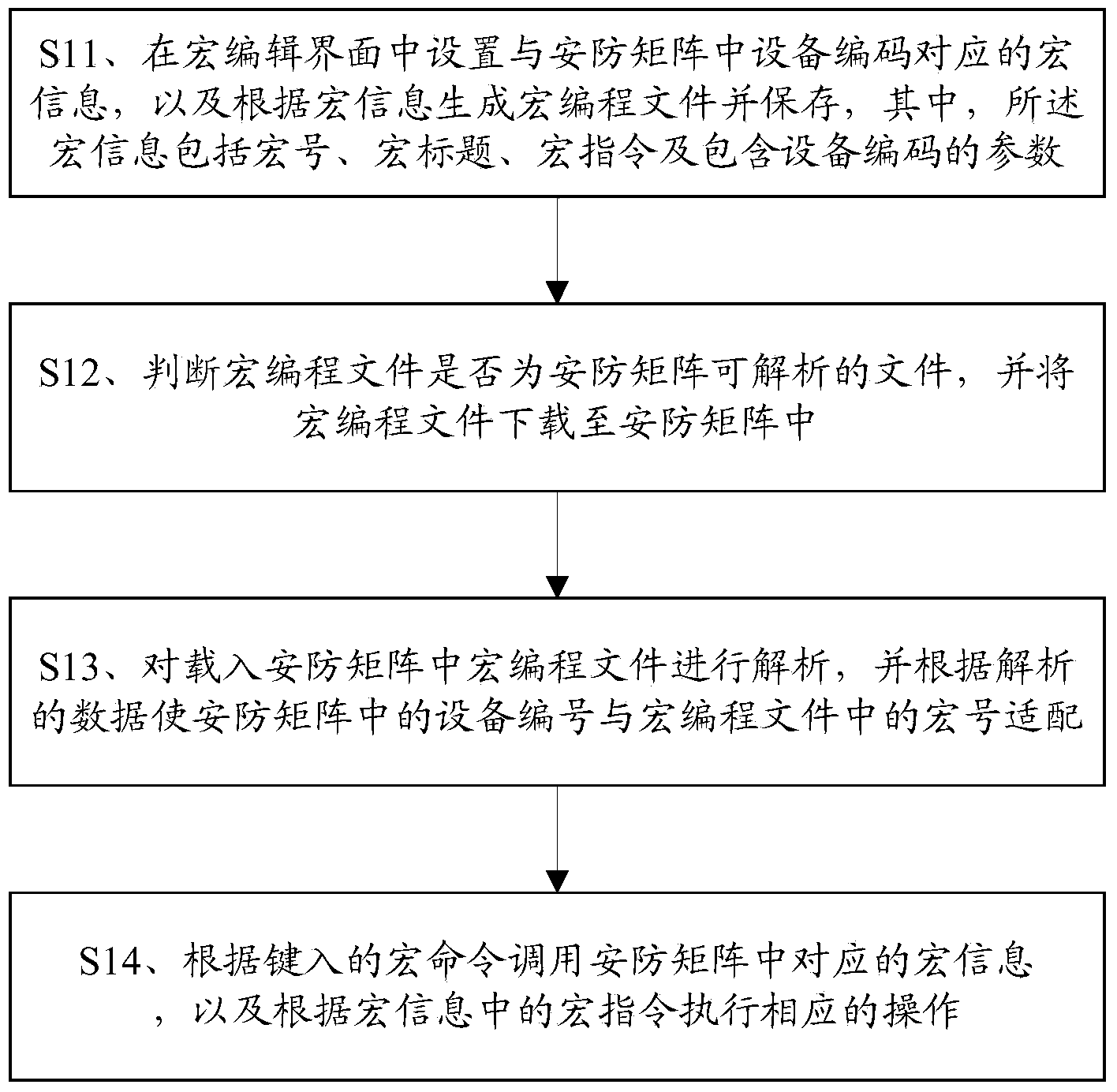

Security and protection matrix method based on macro-programming control

ActiveCN103777952AEasy to operateEasy to manageClosed circuit television systemsSpecific program execution arrangementsMatrix methodMacro instruction

The invention discloses a security and protection matrix control method based on macro-programming control. A matrix element of a security and protection matrix is provided with an equipment code. The security and protection matrix control method comprises the following steps: S11, setting macro-information corresponding to the equipment code in the security and protection matrix in a macro-editing interface, and generating and storing a macro-programming file according to the macro-information; S12, if the macro-programming file is judged to be a file that the security and protection matrix can be analyzed, downloading the micro-programming film into the security and protection matrix; S13, analyzing the macro-programming film loaded into the security and protection matrix, and adapting an equipment code in the security and protection matrix and a macro-number in the macro-programming film according to the analyzed data; S14, calling the corresponding macro-information in the security and protection matrix according to keyed macro-orders, and executing corresponding operation according to a macro-instruction in the macro-information. The security and protection matrix control method provided by the invention realizes flexible configuration with the equipment corresponding to the equipment code in the security and protection matrix, so that a user can conveniently operate and manage.

Owner:SHENZHEN INFINOVA

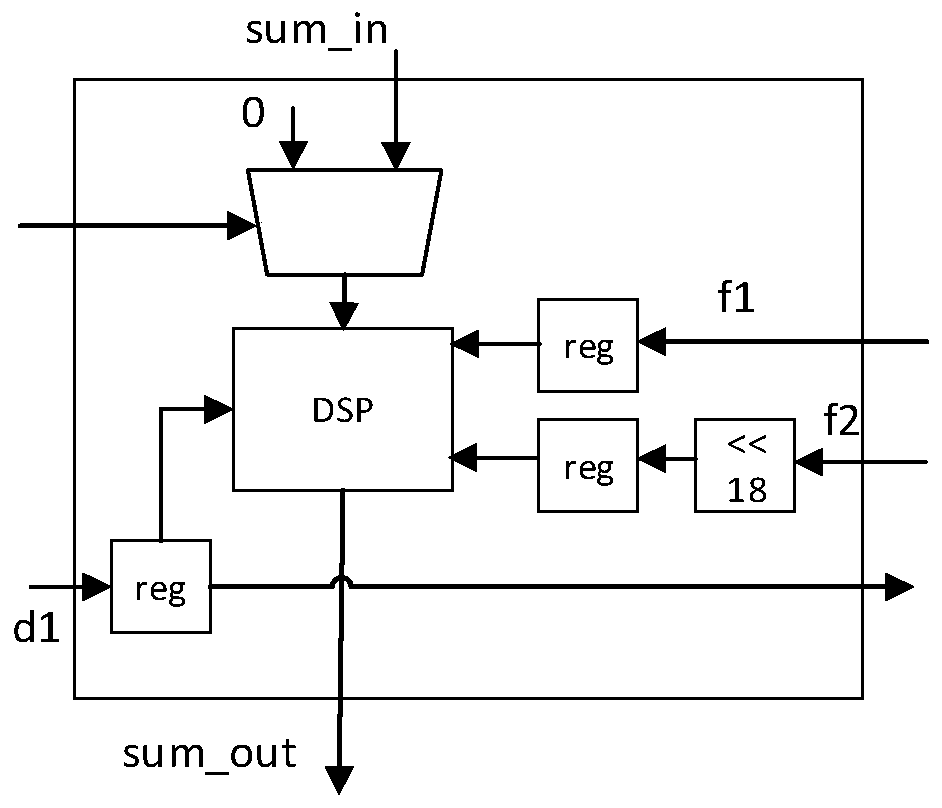

A method and apparatus for accelerating a convolution network based on a macro instruction set

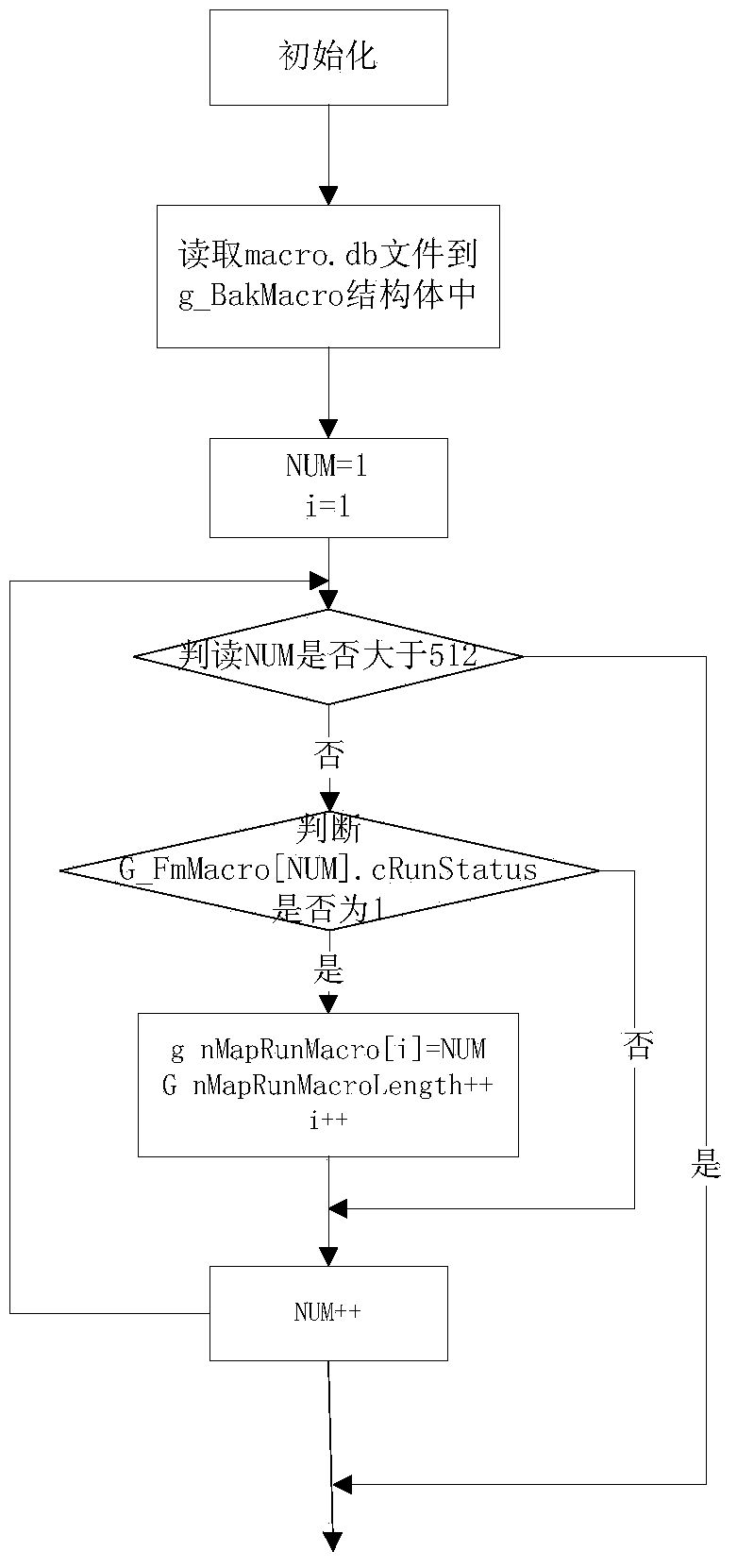

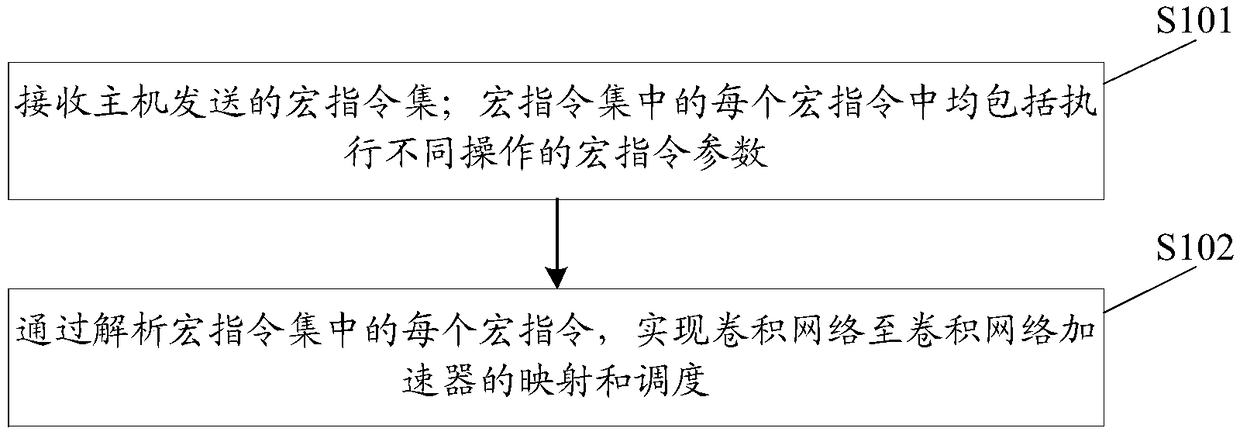

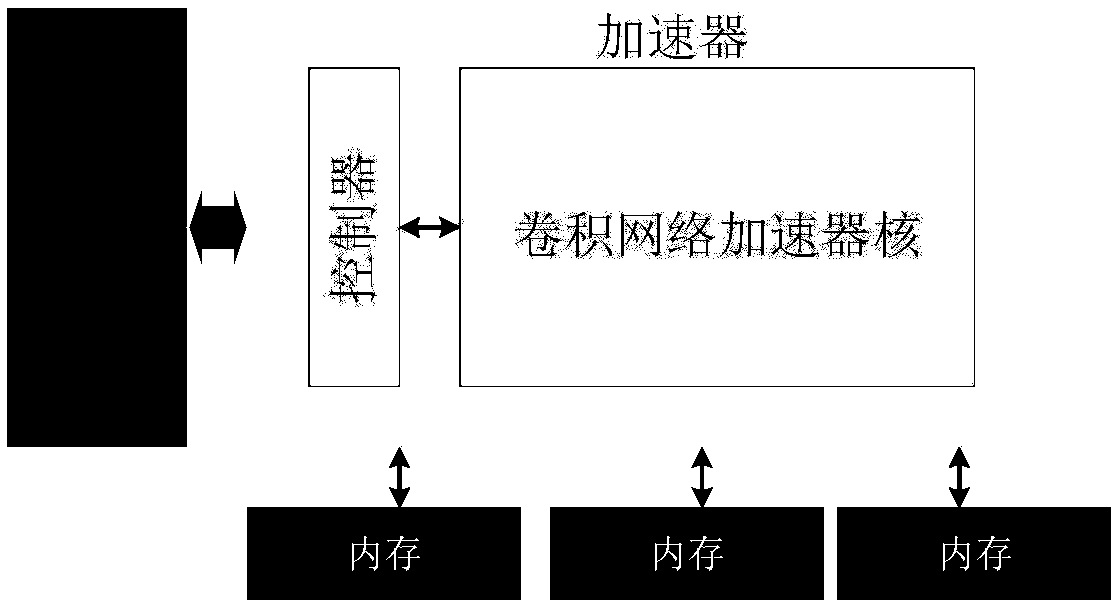

InactiveCN109086875AImplement schedulingSimplify the mapping processNeural architecturesParallel computingMacro instruction

The invention discloses a convolution network acceleration method based on a macro instruction set, which is based on a convolution network accelerator. The method comprises steps: a macro instructionset sent by a host is received; each macro instruction in the macro instruction set includes macro instruction parameters for executing different operations; the mapping and scheduling from convolution network to convolution network accelerator is realized by parsing every macro instruction in macro instruction set. It can be seen that the present invention discloses a macro instruction set of aconvolution network accelerator, the macro instruction set consists of every part of convolution network into a macro instruction, which realizes the efficient mapping and scheduling of convolution network to the hardware of convolution network accelerator with different specifications and types, simplifies the mapping process of convolution network in depth neural network, and has a wide range ofapplication scenarios. The invention also discloses a convolution network accelerating device based on a macro instruction set, which can also realize the technical effect.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

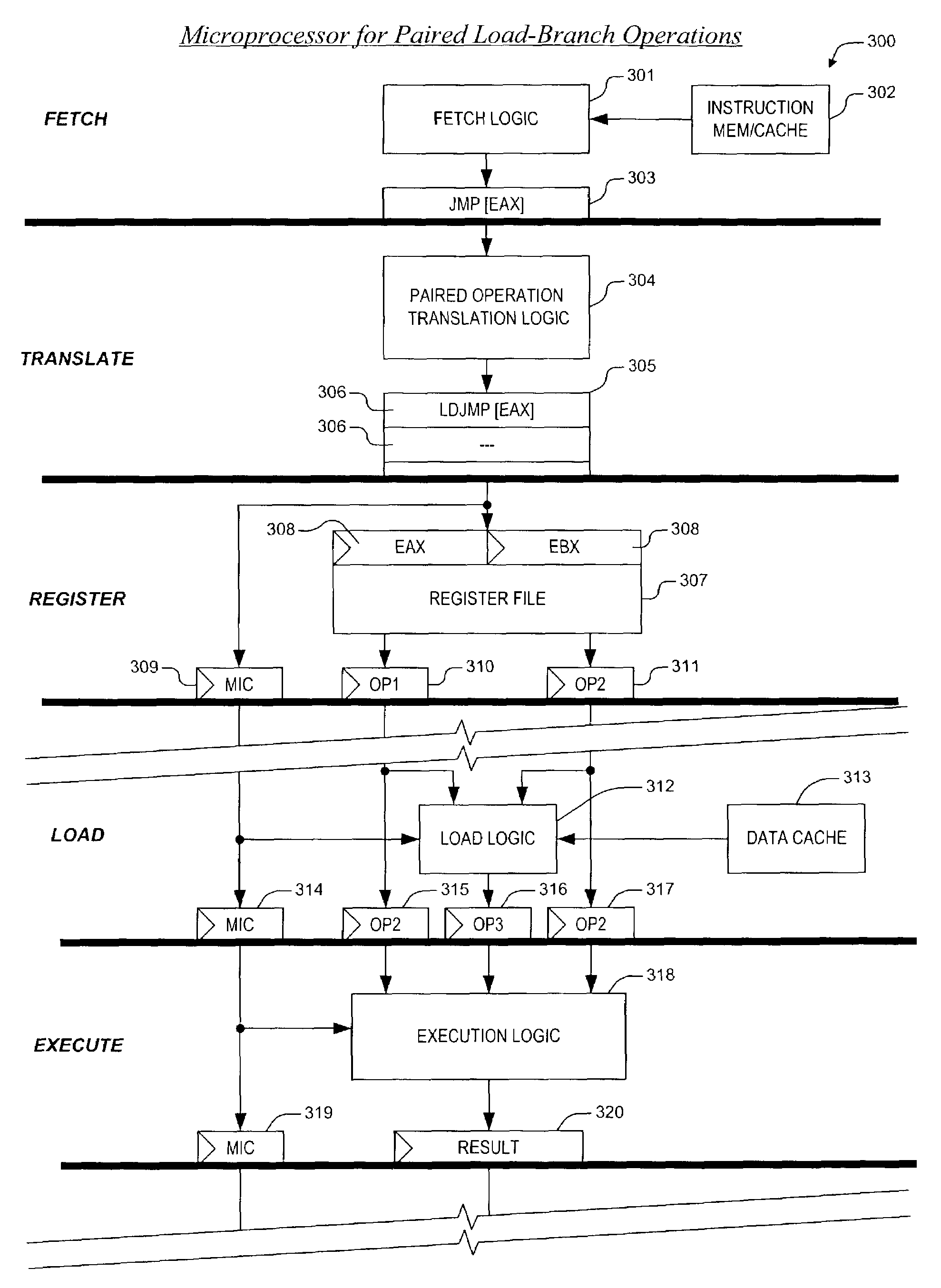

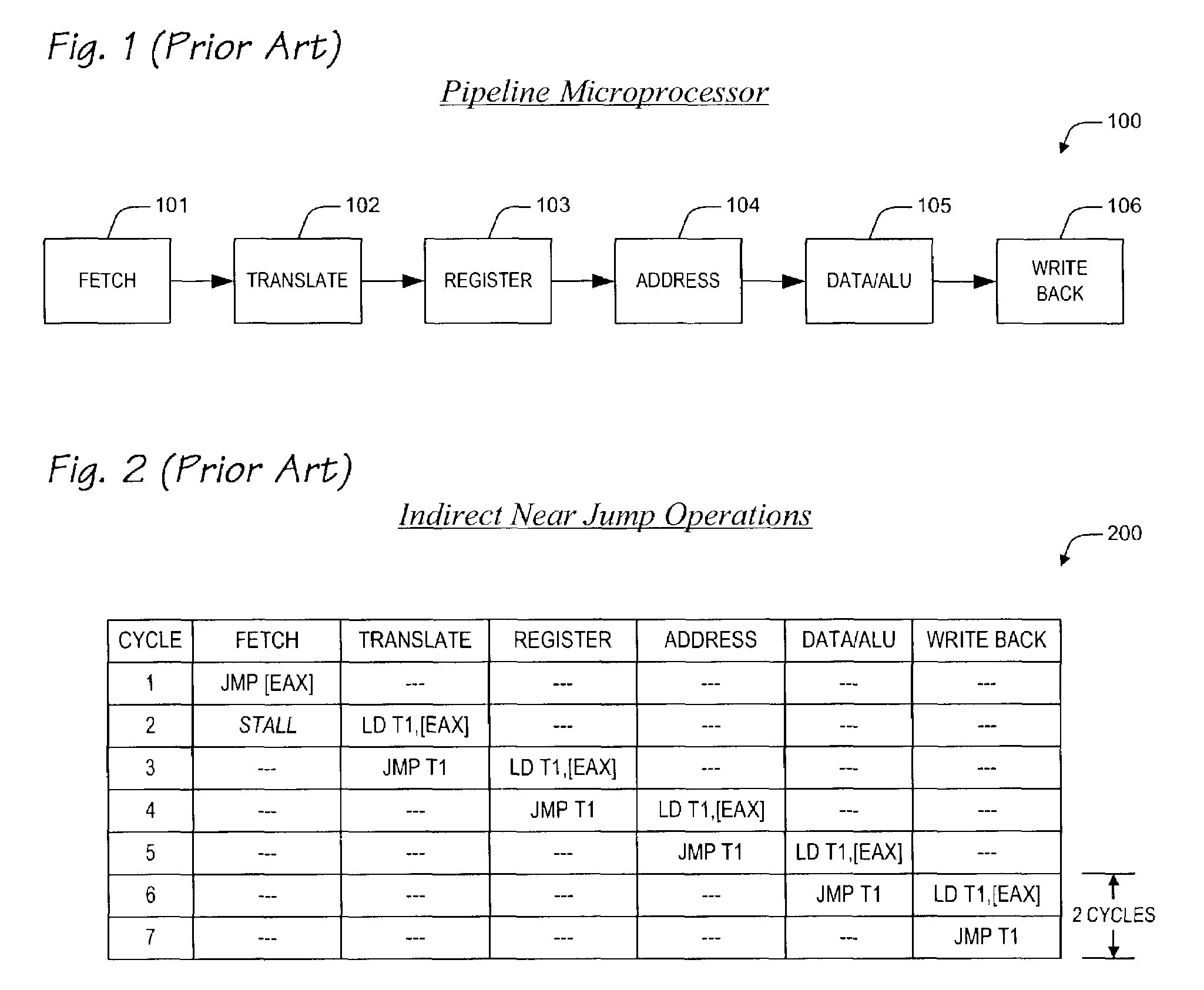

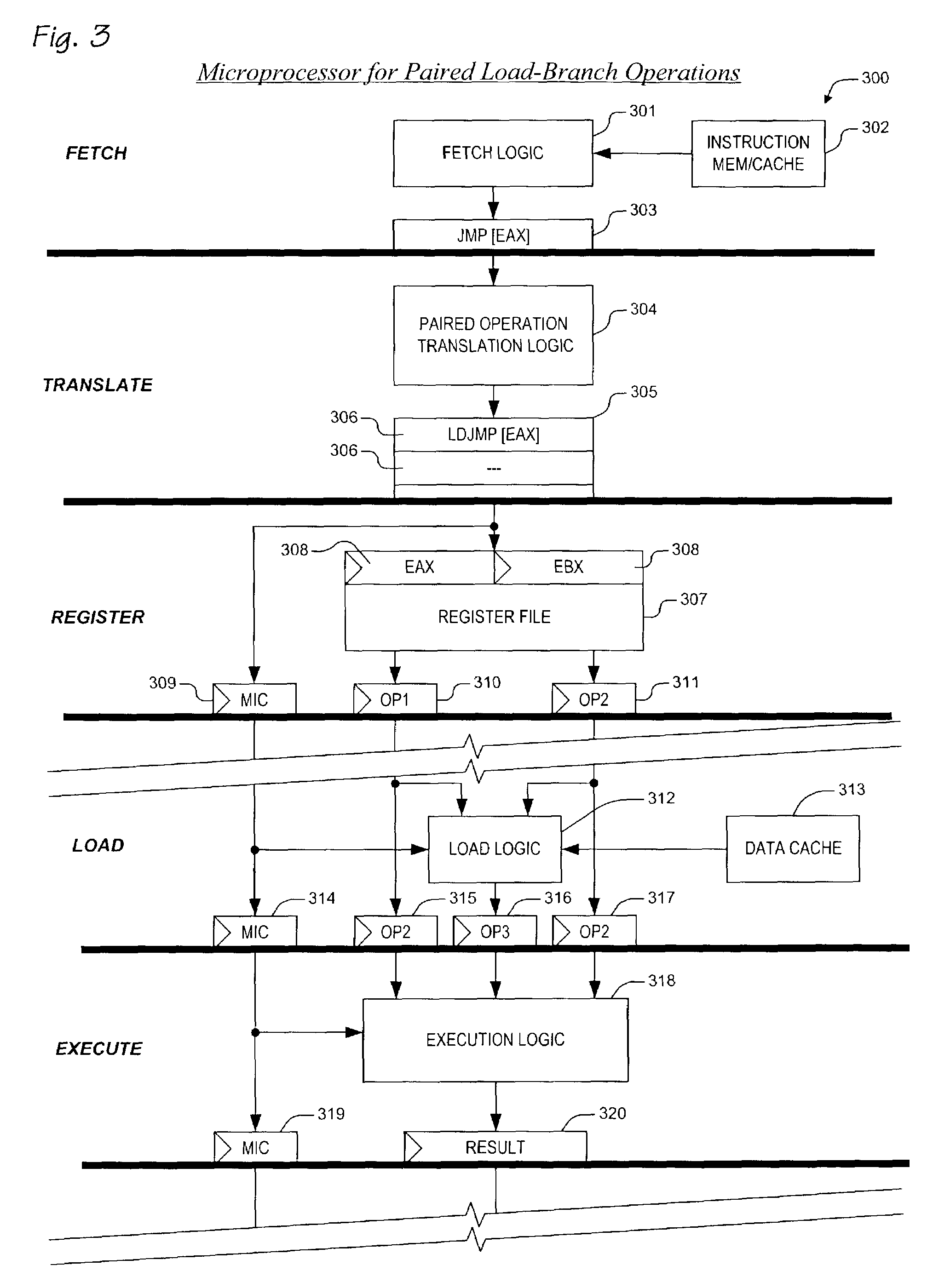

Paired load-branch operation for indirect near jumps

ActiveUS7055022B1Runtime instruction translationDigital computer detailsParallel computingMacro instruction

A microprocessor apparatus is provided for performing an indirect near jump operation that includes paired operation translation logic, load logic, and execution logic. The paired operation translation logic receives an indirect near jump macro instruction, and generates a load-jump micro instruction, where the load-jump micro instruction directs load logic to retrieve an offset and directs the execution logic to generate a target address. The load logic is coupled to the paired operation translation logic and receives the load-jump micro instruction. The load logic retrieves the offset from memory, where the offset indicates a jump destination that is relative to an instruction address corresponding to the indirect near jump macro instruction. The execution logic is coupled to the load logic. The execution logic receives the offset, and employs the instruction address and the offset to generate the target address specifying the jump destination for the near jump operation.

Owner:IP FIRST

Apparatus and method for two micro-operation flow using source override

InactiveUS7451294B2Improve performanceImprove efficiencyInstruction analysisRuntime instruction translationProgramming languageMicro-operation

A method and apparatus for a two micro-operation flow using source override. In one embodiment, the method includes the identification of a macro-instruction having one or more streaming single instruction multiple data extension type operands. Once received, the macro-instruction is decoded into a first micro-operation (uOP) and a second uOP. Once decoded, a signal is asserted to disable source operand override logic if the first micro-operation updates a logical destination register that matches a logical source register of the micro-operation. Otherwise, the mutual source override is active and executed by a register alias table (RAT) when uOP with matching logic source and destination register are detected in a same clock cycle. In doing so, macro-instructions having 128-bit operands may be processed using, for example, two uOPs (one for the lower half and one for the upper half) in a 64-bit implementation, while preserving the atomicity of the original instruction.

Owner:INTEL CORP

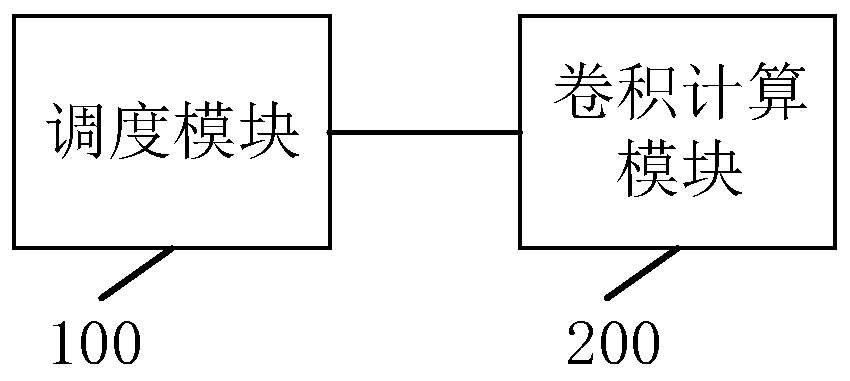

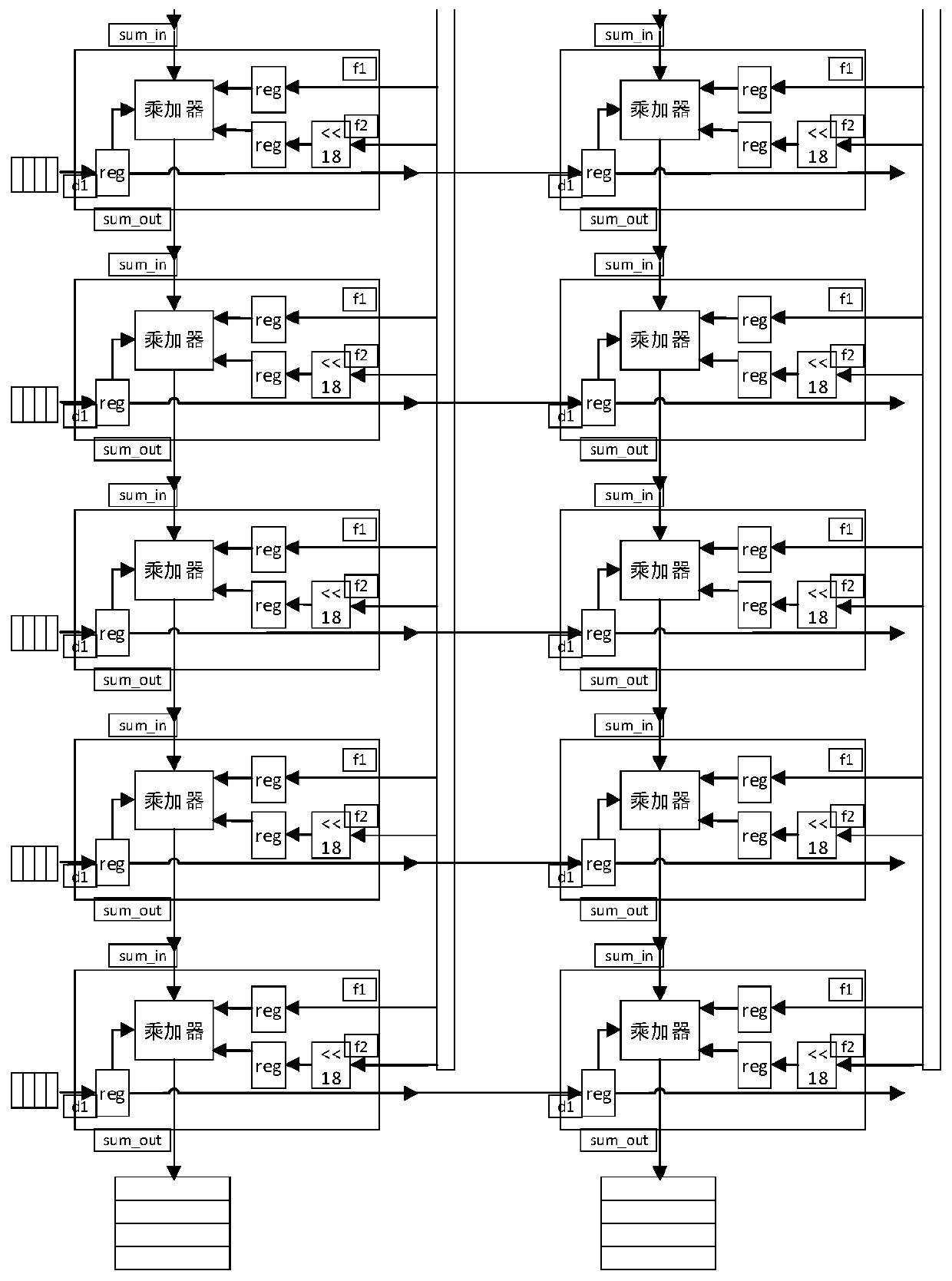

Deep learning processor and electronic equipment

InactiveCN109871951AImprove parallelismHigh speedPhysical realisationParallel computingComputer module

The invention discloses a deep learning processor, and the processor comprises a scheduling module which is used for receiving a data processing request, and analyzing a macro instruction in a targetinstruction set according to the data processing request so as to obtain an analysis result; The convolution calculation module is used for executing a two-dimensional convolution calculation operation corresponding to the analysis result in a three-dimensional convolution pulse array to obtain a data processing result; Wherein the three-dimensional convolution pulse array is obtained by arranginga plurality of operation units according to a multiplication and addition device array construction rule. According to the method, the requirement of convolution calculation for bandwidth can be reduced, the efficiency of convolution calculation is improved, and the processing flow of deep learning is optimized. The invention further discloses the electronic equipment which has the above beneficial effects.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD