Method and system for executing register type instruction in RISC (Reduced Instruction-Set Computer) processor

A technology of registers and processors, applied in the computer field, can solve problems such as insufficient registers and incomplete data dependence, and achieve the effect of simple implementation and improved performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

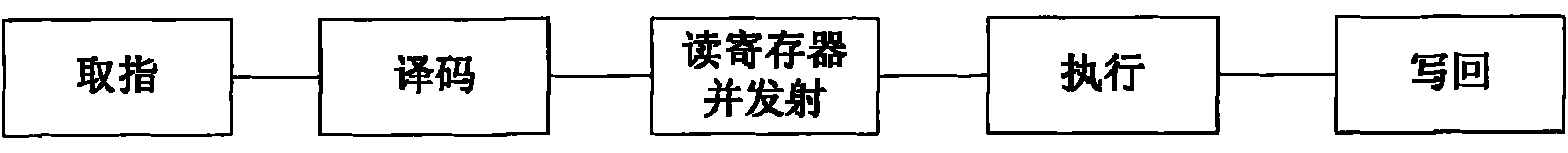

[0063] Step S210, when fetching the instruction, fetch the instruction according to the instruction address, and send it to the decoding stage.

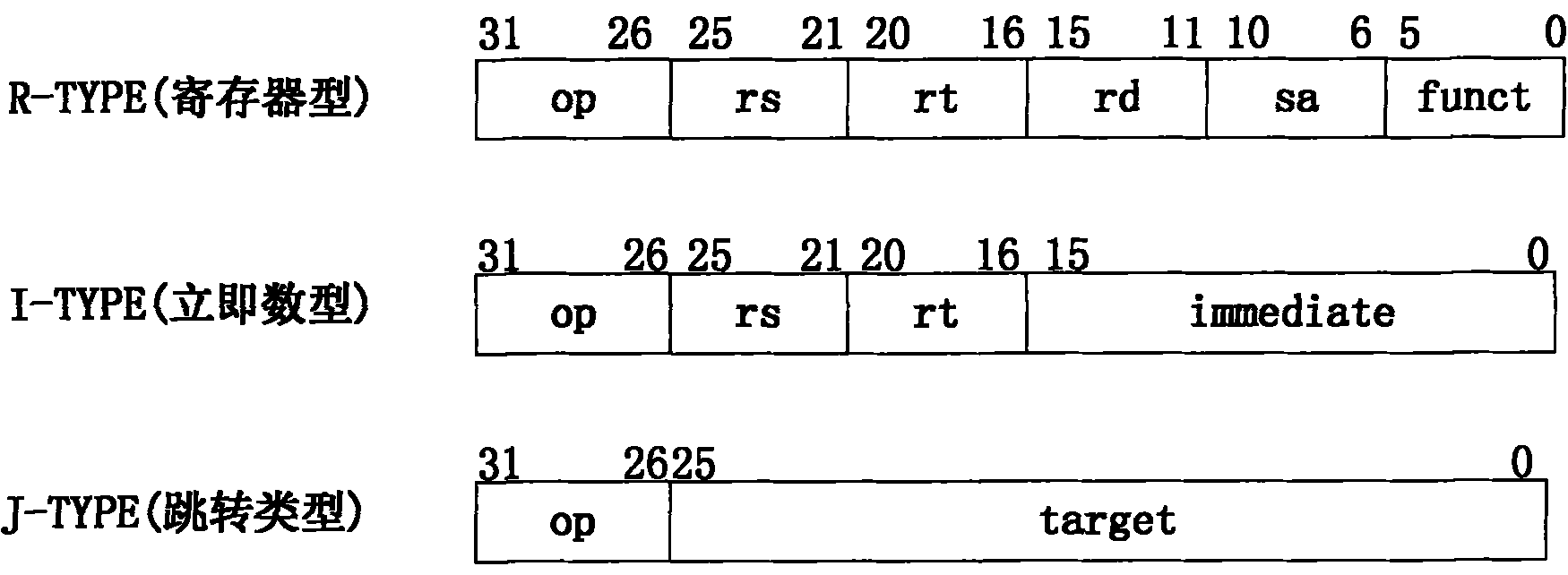

[0064] Step S220, when decoding, determine the type of the instruction according to the opcode of the current instruction, and recognize that the current instruction is a macro instruction or a register type instruction, and for the register type instruction, determine the operand type according to the type of the register type instruction, and Add flag bits indicating the operand type to the register number of the register type instruction to generate a complete register number; determine the functional part number of the instruction according to the opcode of the current instruction, and encode the current instruction to generate an internal recognizable by the functional part Opcode encoding.

[0065] The specific implementation manner of step S220 is as follows Figure 4 shown.

[0066] In step S401, the decoding unit determine...

specific Embodiment approach 2

[0078] In a specific implementation manner, the specific steps of step S200 are as follows.

[0079] Step S210', when fetching the instruction, fetch the instruction according to the instruction address, and send it to the decoding stage.

[0080] Step S220', when decoding, determine the type of the instruction according to the opcode of the current instruction, and recognize that the current instruction is a macro instruction or a register type instruction, and for the register type instruction, determine the operand type according to the type of the register type instruction, and Add a flag indicating the operand type to the register number of the register type instruction to generate a complete register number; encode the current instruction to generate an internal opcode code that can be recognized by the functional unit.

[0081] Step S230', when reading registers and transmitting, read the register file corresponding to the register number in the register file of the typ...

Embodiment

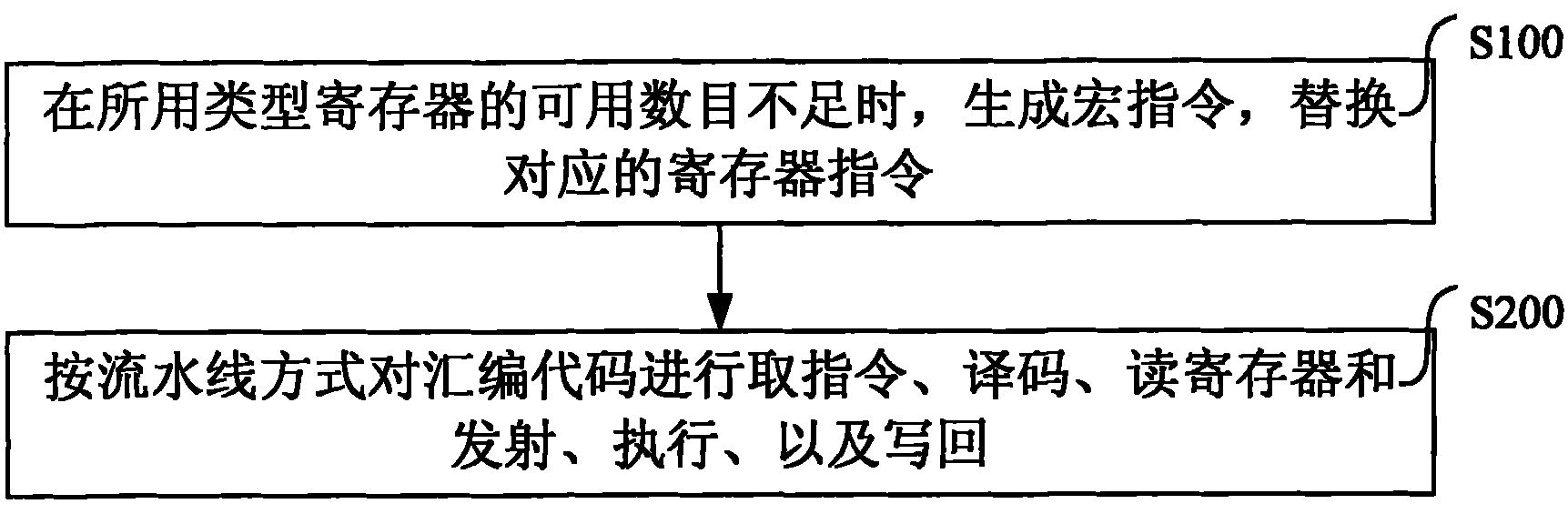

[0090] The flow process of a specific embodiment of the method for executing register type instructions in the RISC processor of the present invention is as follows Figure 5 shown.

[0091] In this embodiment, the MIPS floating-point multiply-add instruction madd.f is taken as an example.

[0092] Step S501, when finding a floating-point multiplication-add instruction madd.f in the assembly code, the available number of used floating-point registers will be insufficient, then generate the macro instruction PMAC_F corresponding to the multiplication-add instruction madd.f, so that the macro instruction PMAC_F Replaces the multiply-add instruction madd.f.

[0093] The internal opcode encoding of the macroinstruction PMAC_F is the same as the internal opcode encoding of the floating-point multiply-add instruction madd.f, and the register number of the macroinstruction PMAC_F is a complete register number, including a flag bit indicating the type of register used, which is float...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More