Double-sampling full-difference sampling-hold circuit

A sample-and-hold circuit and double-sampling technology, applied in the direction of analog-to-digital converters, etc., can solve the problems affecting the accuracy of the sample-and-hold circuit and the speed of the establishment of the op amp, and achieve the effect of increasing the establishment speed, improving the accuracy, and eliminating the switch

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

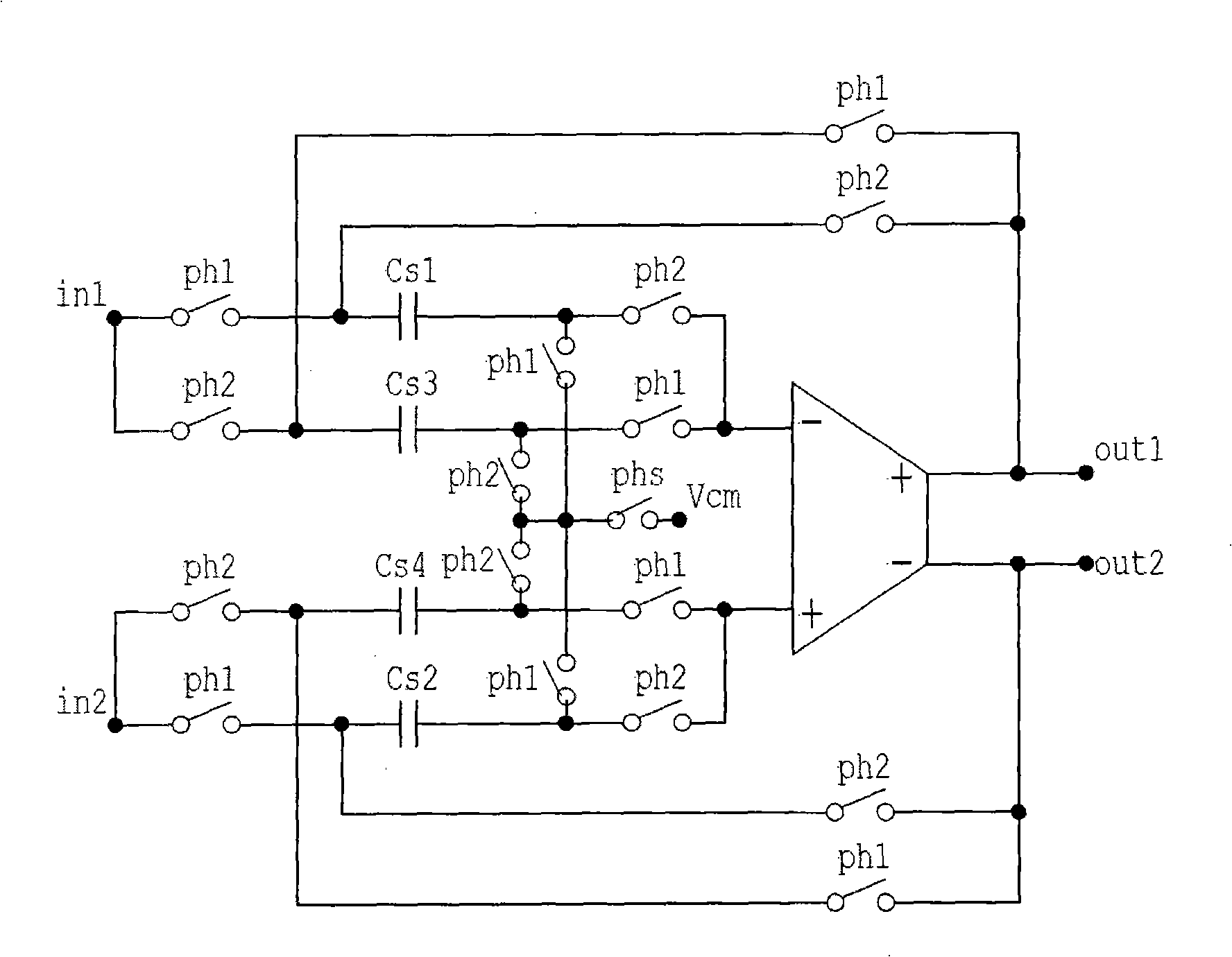

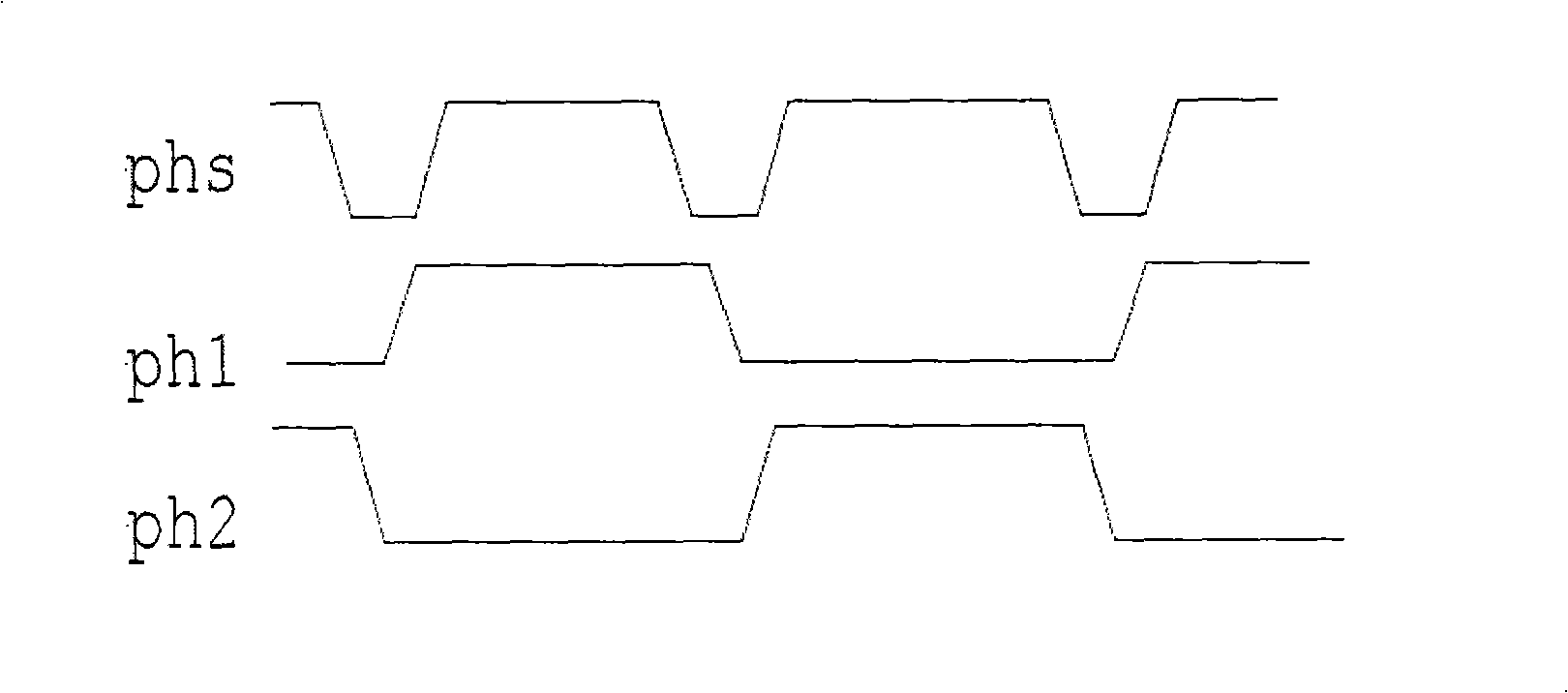

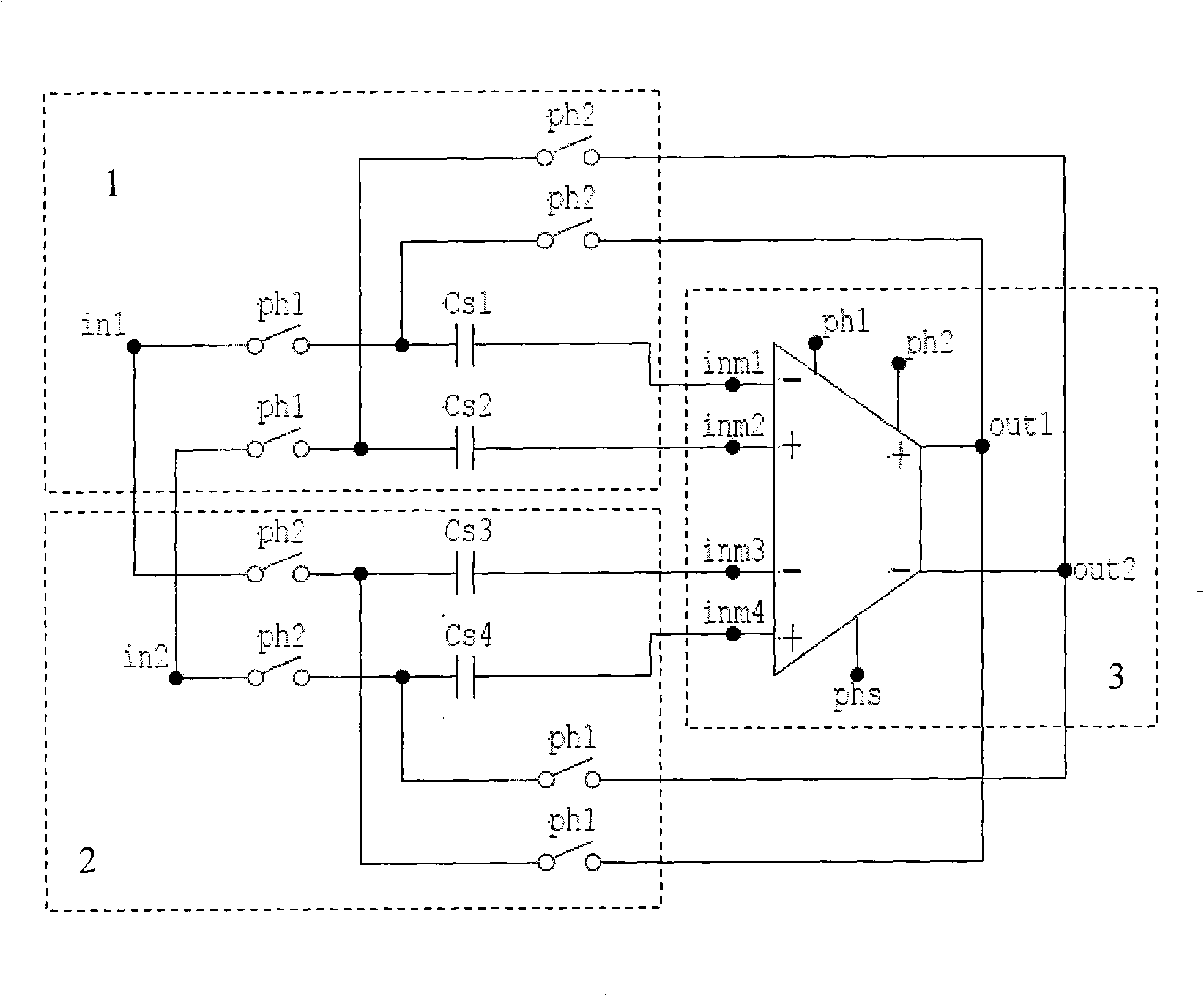

[0034] Such as image 3 as shown, image 3 A schematic structural diagram of a double-sampling fully differential sample-and-hold circuit provided by the present invention. The double-sampling fully differential sample-and-hold circuit includes a differential switched capacitor unit 1 , a differential switched capacitor unit 2 , and a double-folded branch operational amplifier 3 . The timing relationship of Ph1, ph2, and phs is as follows figure 2 shown. image 3 Among them, the differential switched capacitor unit 1 and the double folded branch op amp 3 implement the functions of sampling when the clock signals ph1 and phs are high and holding when the clock signal ph2 is high; the differential switched capacitor uni...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More