IC testing methods and apparatus

A technology for testing integrated circuits and circuits, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] The present invention provides a structure that enables testing of shift registers. In order for the instruction register to be testable, applicants have realized that one possibility is to feed the update register output to the shift register. The testing of this register (including the asynchronous reset of the updated register) can use a variety of modes, which are sequentially shifted into or out of the register structure.

[0051] The present invention provides such a feedback path specific implementation to enable the instruction register to use a simple test sequence. This enables control of the structure via state mechanical agreements.

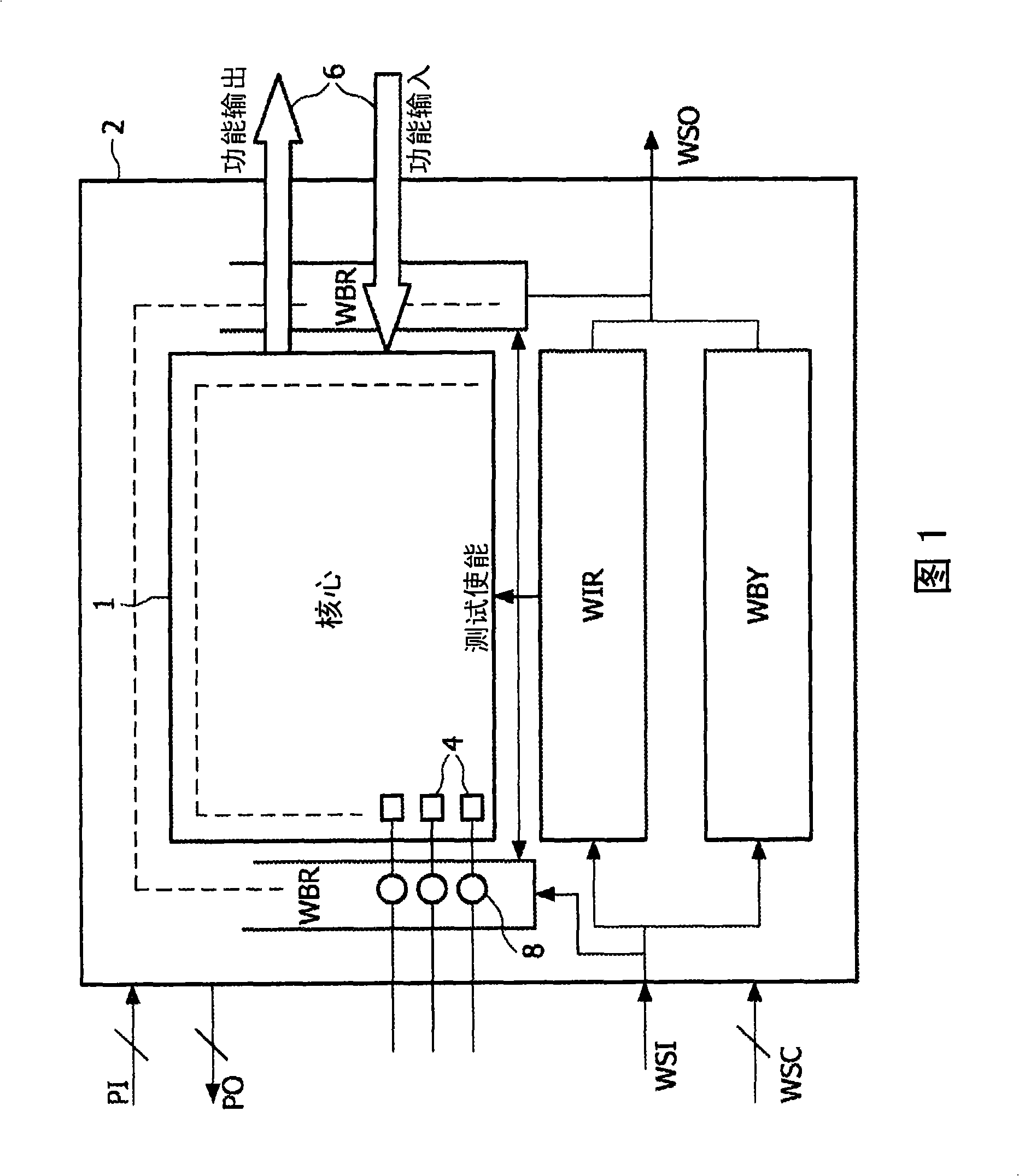

[0052] Before describing the invention in further detail, a detailed overview of wrapper structure and operation will be given.

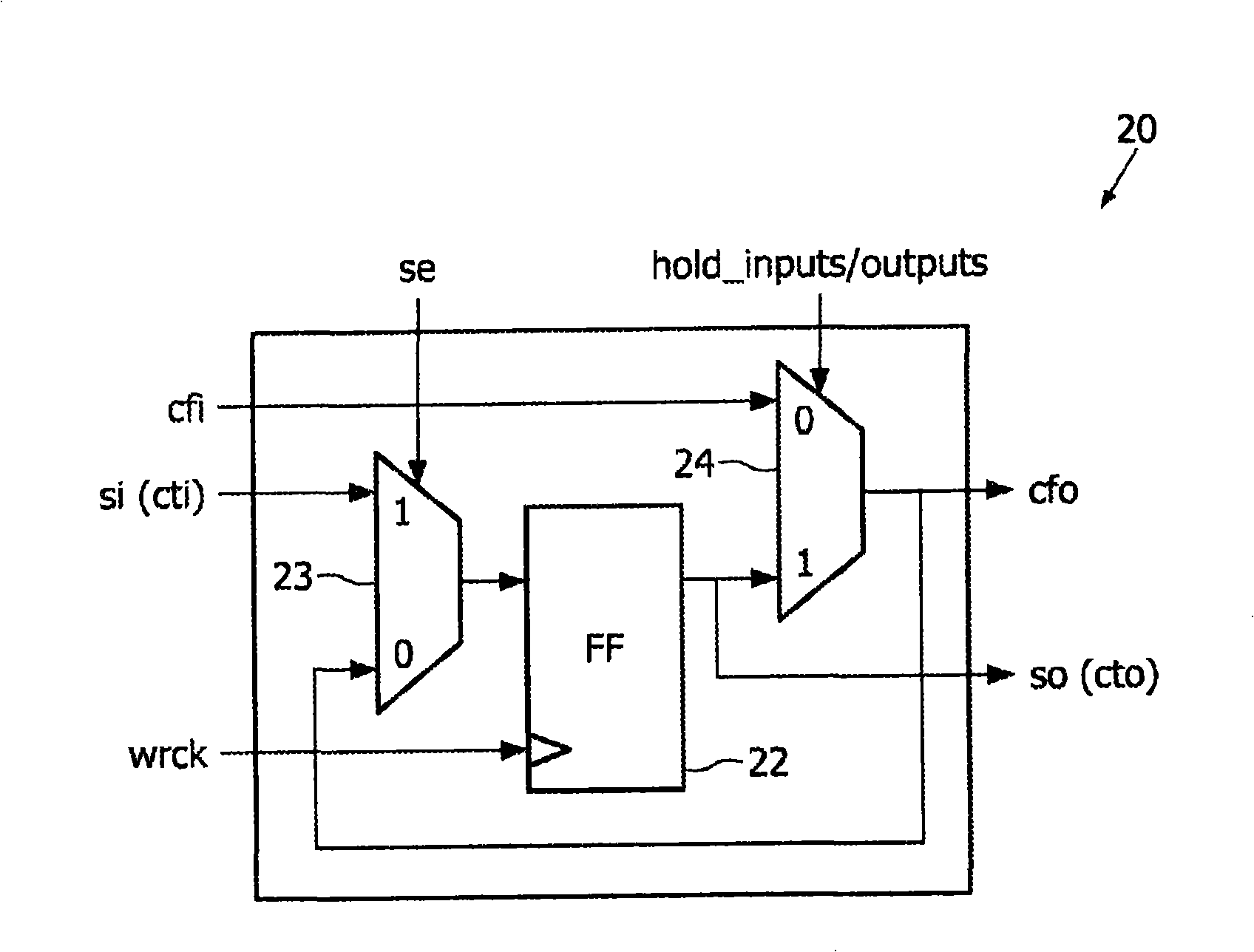

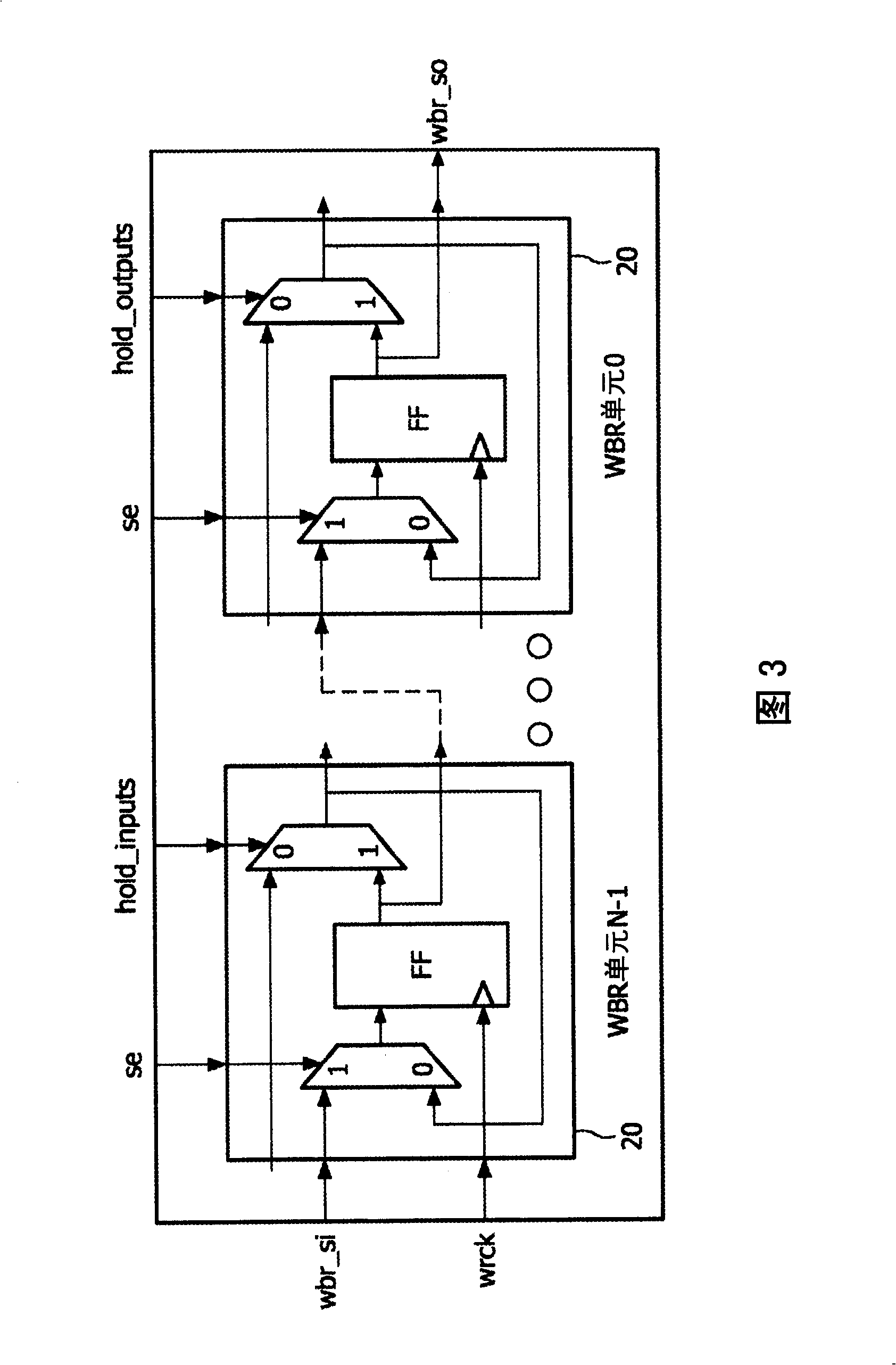

[0053] As mentioned above, wrapper boundary registers form multiple units, figure 2 An example of such a unit 20 is shown, corresponding to one of the units 8 shown in FIG. 1 .

[0054] This uni...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com