System bus deadlock prevention method, device and on-chip system

A system bus, system deadlock technology, applied in the direction of instruments, electrical digital data processing, etc., can solve problems such as limiting the processing speed of Master1, unable to access Slave1 normally, and no processing, to ensure performance, reduce blocking time, and ensure processing. effect of speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

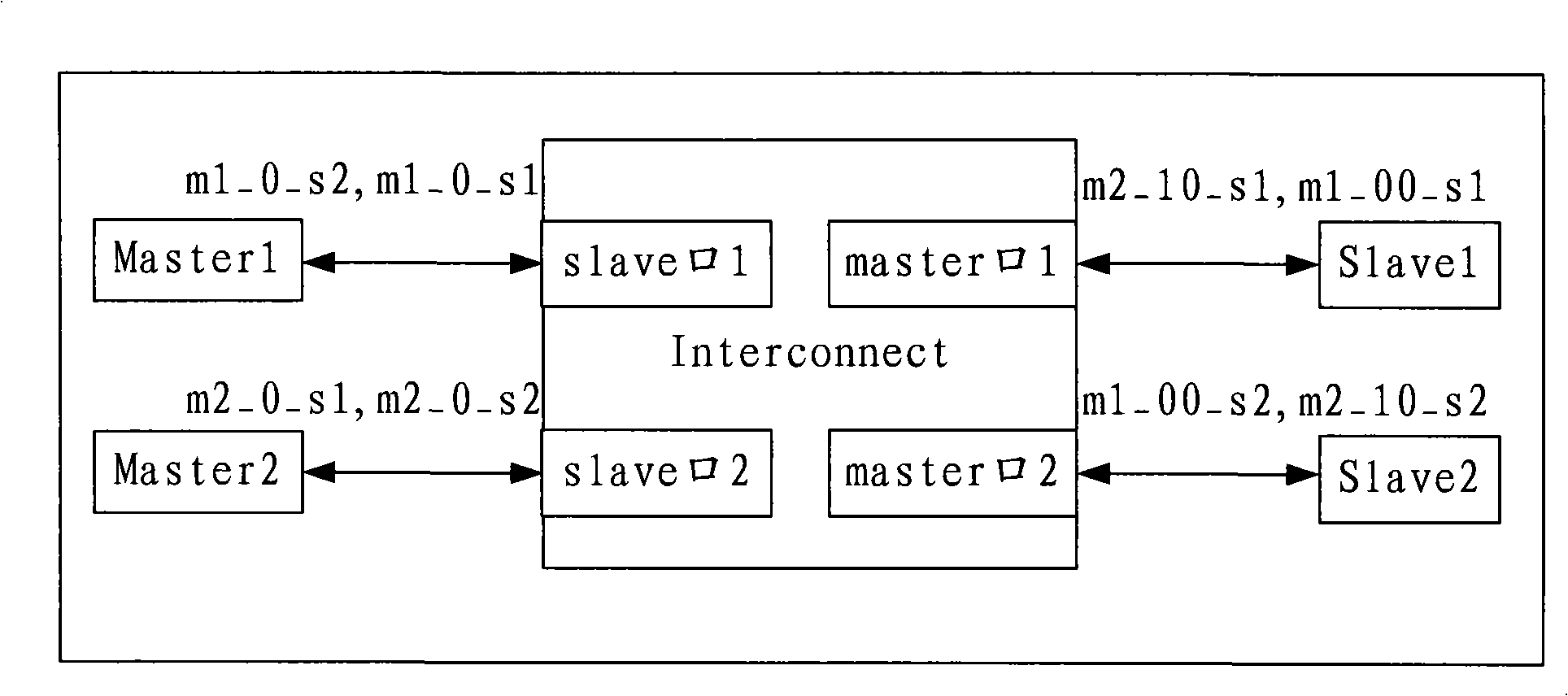

[0052] Such as Figure 5 As shown, the anti-deadlock method of the system bus in this embodiment includes the following steps:

[0053] 501. The bus interconnection module receives an operation command sent by the master device. In this embodiment, the operation command may include a serial number, an accessed slave device, an address corresponding to the operation command, and a specific operation of the operation command.

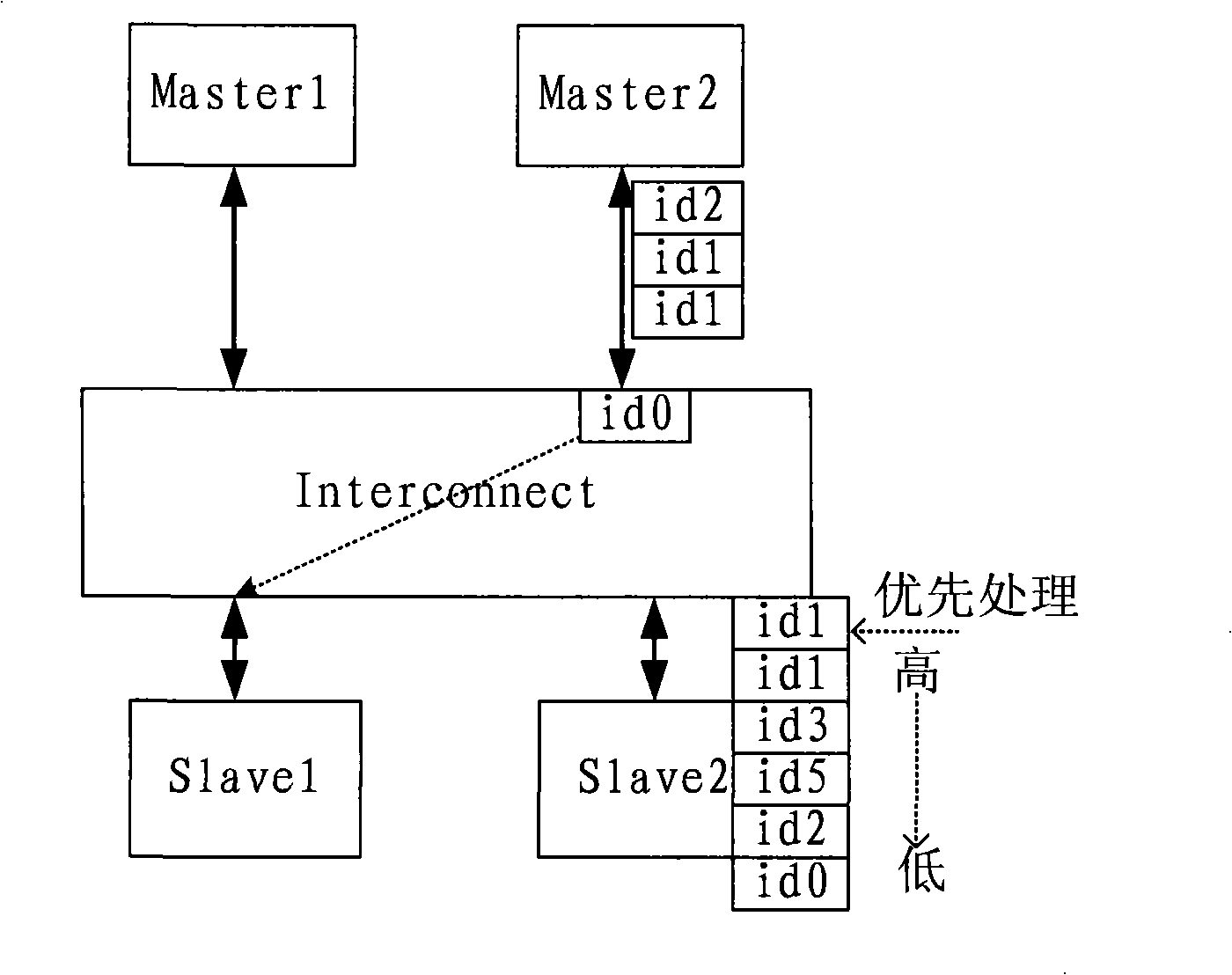

[0054] 502. The bus interconnection module judges whether the received operation command and the delivered but unfinished target operation command will cause a system deadlock. The specific technique for judging whether it will cause system deadlock in this step is: when the same master device uses the same serial number operation command to access different slave devices, or different master devices use the same serial number operation command to access different slave devices respectively When the device is used, it may cause system deadlock when the s...

Embodiment 2

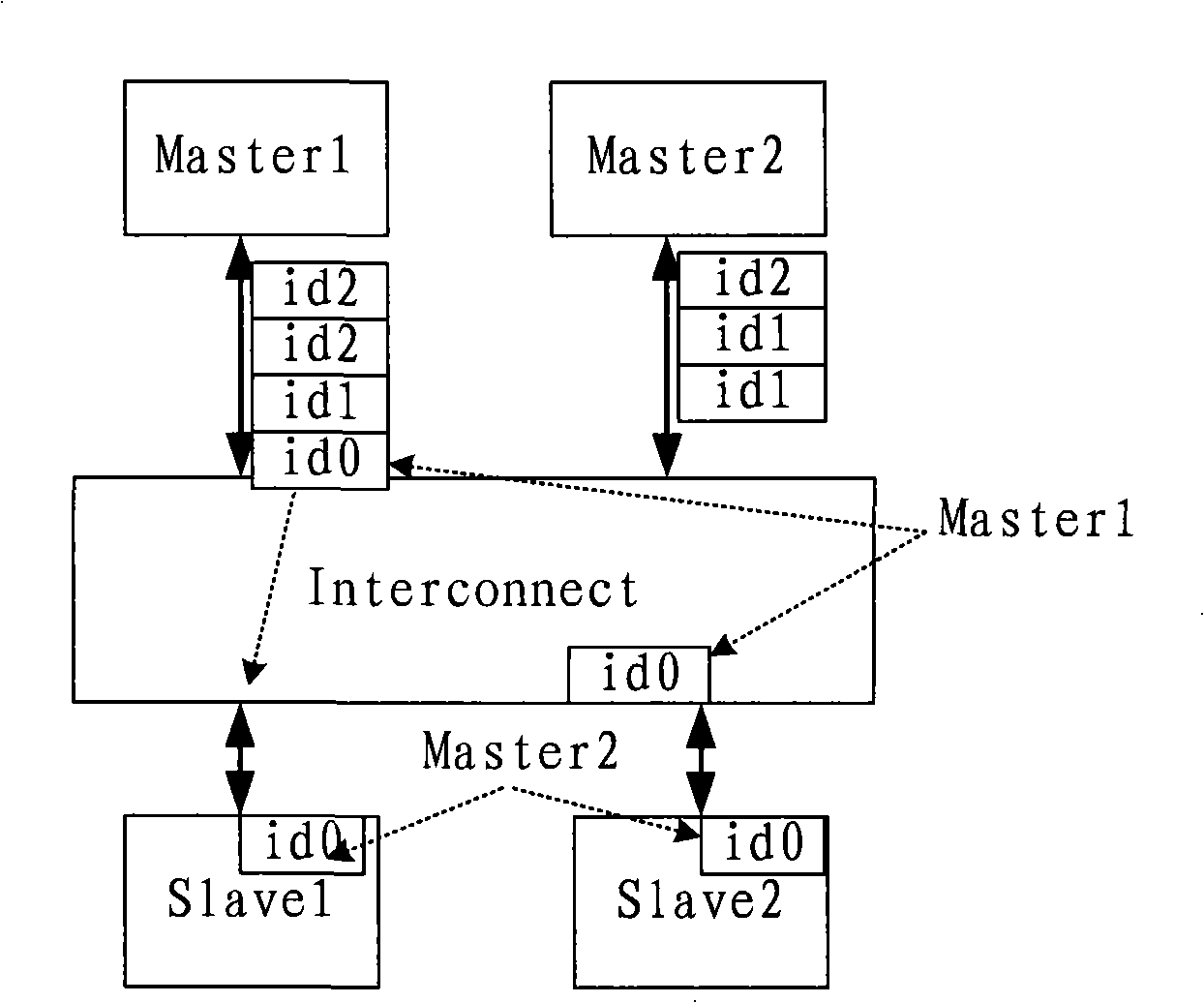

[0066] This embodiment is an anti-deadlock technology of the internal bus of the system implemented in the AXI bus, and a similar technical solution of this embodiment can also be adopted in other buses. Such as Figure 8 As shown, the anti-deadlock method of the system bus in this embodiment includes the following steps:

[0067] 801. The interconnect of the AXI bus saves each operation command sent to the slave device, and records the serial number of the saved operation command and the corresponding slave device. After the operation command is completed, it can be invalidated, or directly To delete, in this embodiment, the method of setting to invalid is adopted. The effective target operation command saved in the interconnect indicates that the operation command has been sent but not completed.

[0068] 802, the interconnect of the AXI bus receives the operation command sent by Master1 (master device 1), assuming that the sequence number of the operation command is 0, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More