Multiple gate field effect transistor structure and method for fabricating same

A field-effect transistor, multi-gate technology, used in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

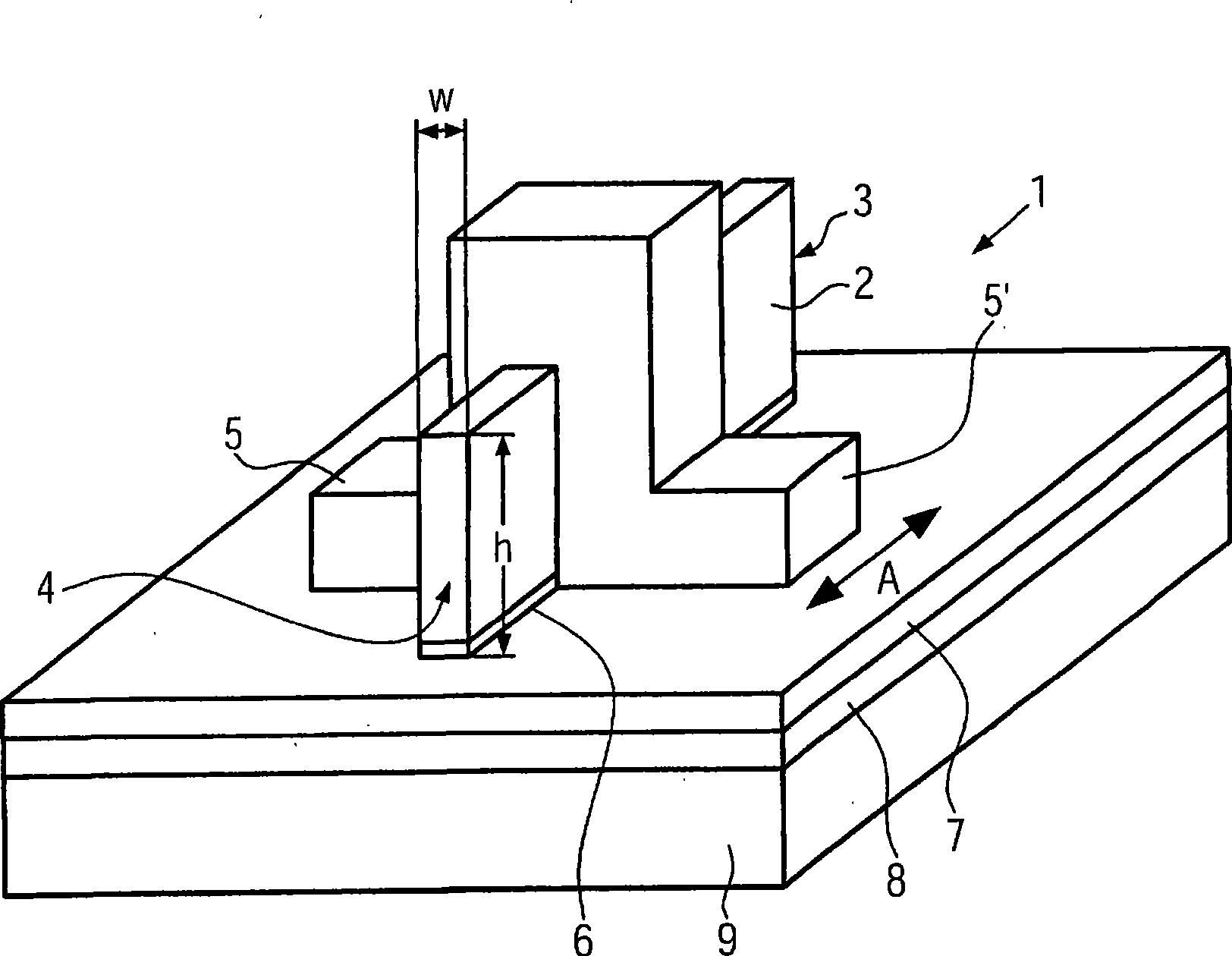

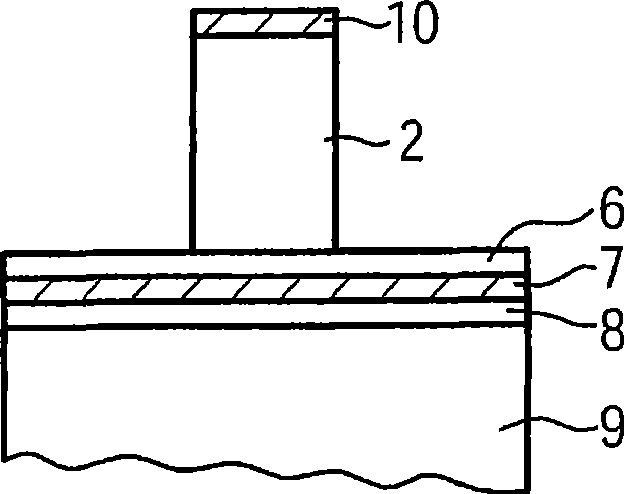

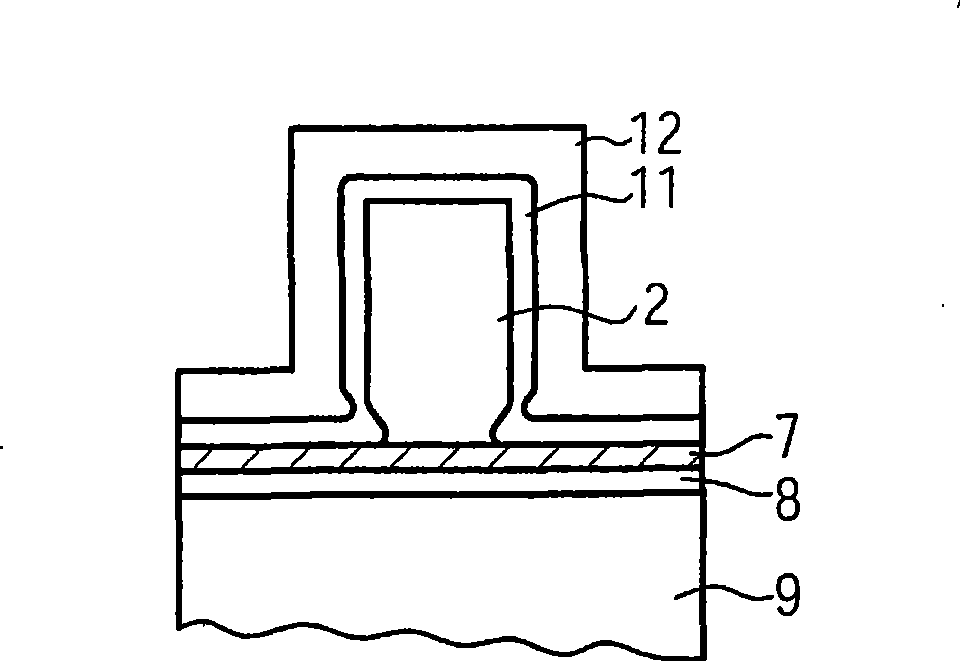

[0024] figure 1Taking FinFET structure 1 as an example schematically and in principle shows the main part of the MuGFET structure. The FinFET 1 comprises a fin structure 2 formed from an active semiconductor top layer of an SOI type substrate. In the example shown, the semiconductor top layer (and thus the fin 2 ) consists of silicon, wherein in other not shown embodiments of the invention, the fin 2 can be made of, for example, strained silicon, SiGe, SiC, Ge and / or A (III)-B(V) compounds such as other semiconductor materials.

[0025] As an improvement, strained silicon can be used instead of the top silicon layer of the SOI type substrate. Using a strained silicon layer greatly improves electron mobility in the (100) orientation of silicon, thereby providing higher transistor currents.

[0026] exist figure 1 In , the height h of the fin 2 is about 50 nm, but in other not shown embodiments of the present invention may be between 30 nm and 100 nm. The width w of the fin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More