Charge balancing method in current input adc

A technology of charge balance and current, applied in amplifiers with semiconductor devices/discharge tubes, electrical components, physical parameter compensation/prevention, etc., can solve problems such as input current offset errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

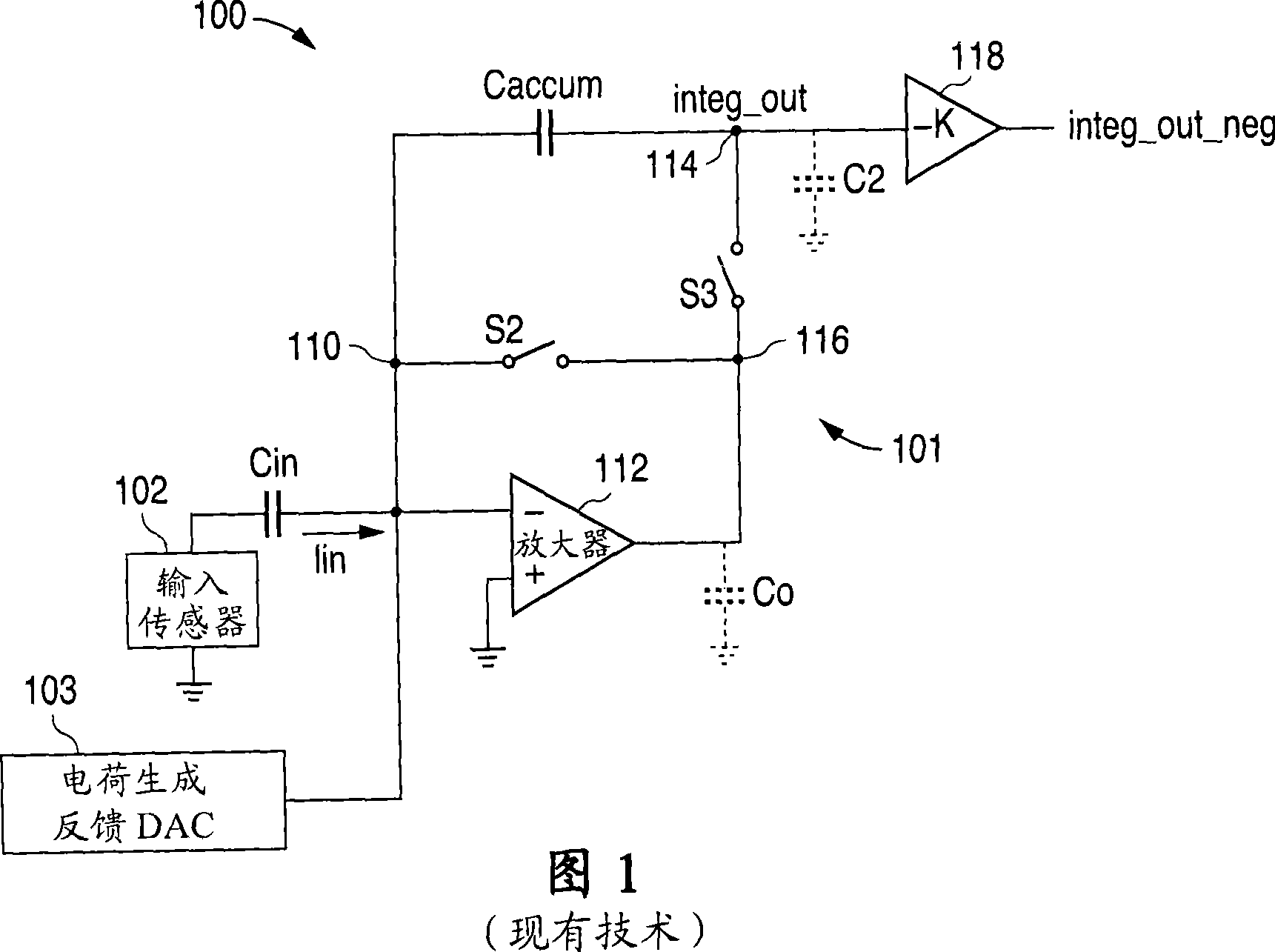

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

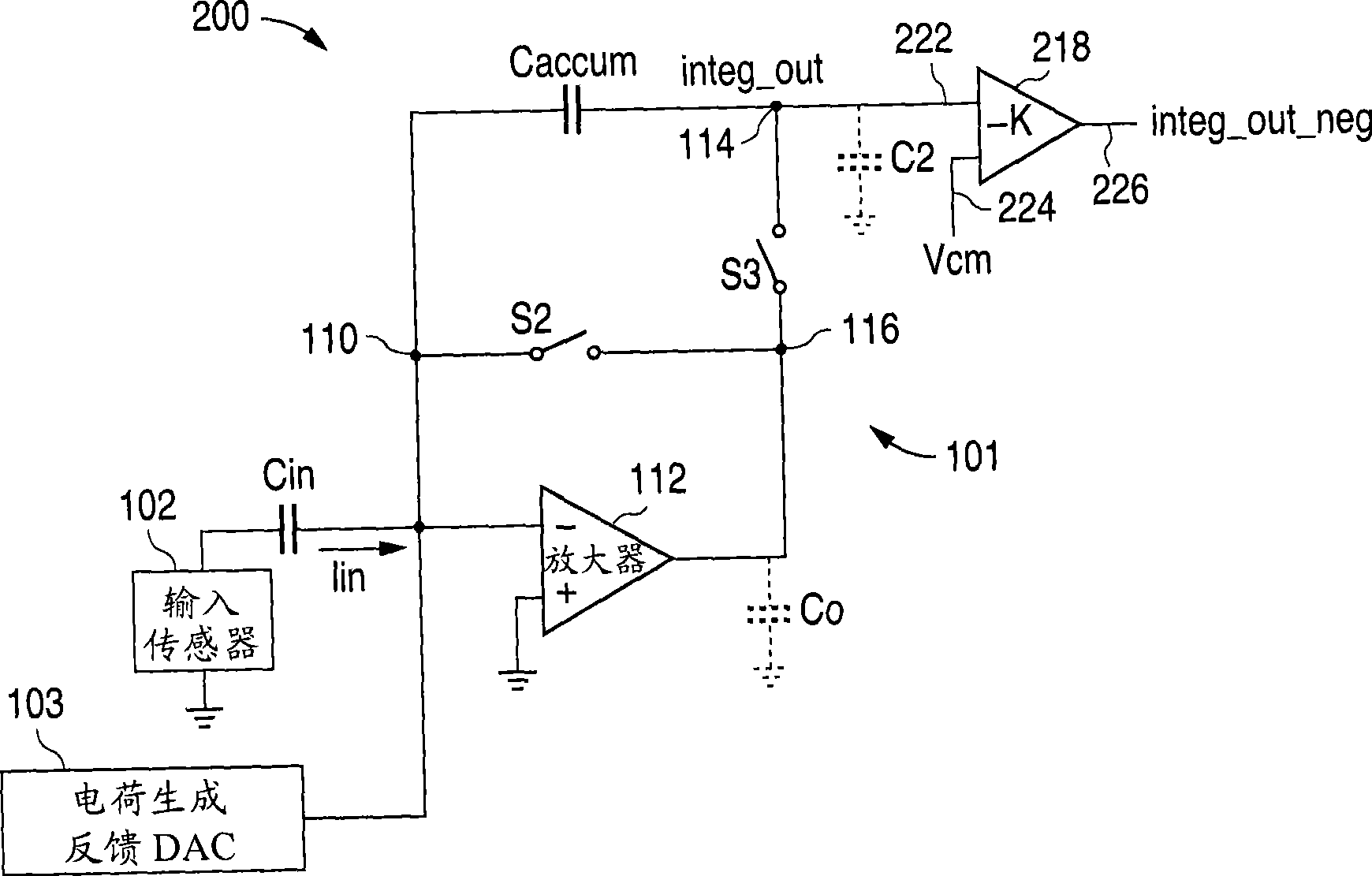

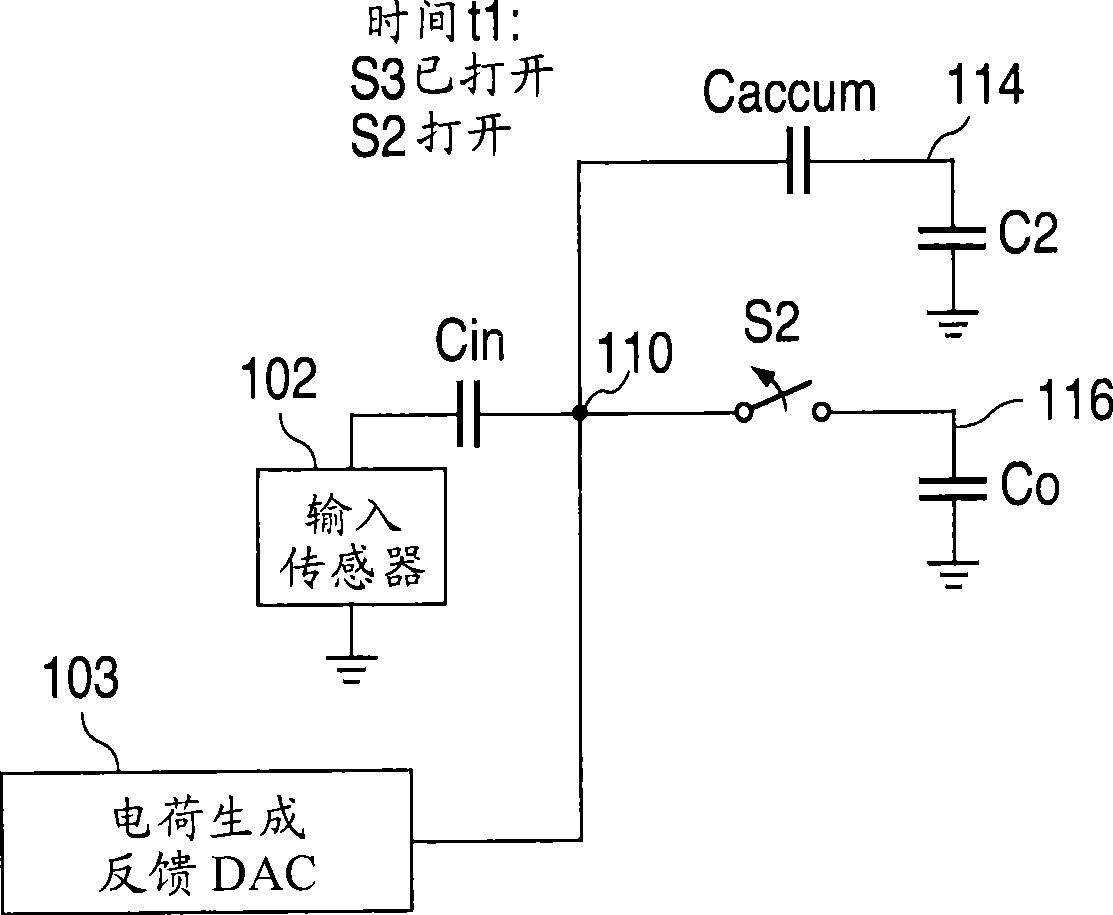

[0020] In accordance with the principles of the present invention, a buffer circuit with signal independent low input capacitance uses a bootstrapping technique at the input device such that the channel region of the input device has an absolute input voltage to the gate of the input device Not sensitive. In addition, a bootstrap technique is used to create a local feedback path to greatly reduce the input capacitance at the input of the device. An advantage of the snubber circuit is that the magnitude and variation of the input capacitance of the snubber circuit is reduced by orders of magnitude relative to conventional devices.

[0021] In particular, the low input capacitance buffer circuit of the present invention has particular application in analog-to-digital converters (ADCs), especially current-input ADCs that receive low-level input currents to be digitized. The buffer circuit of the present invention can be coupled with an integrator to form a charge balancing regul...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More