Information processing apparatus having memory clock setting function and memory clock setting method

A technology for information processing devices and memory controllers, applied in memory systems, electrical digital data processing, digital data processing components, etc., can solve problems such as increased memory power consumption and inability to fully display the transmission rate, so as to reduce power consumption Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

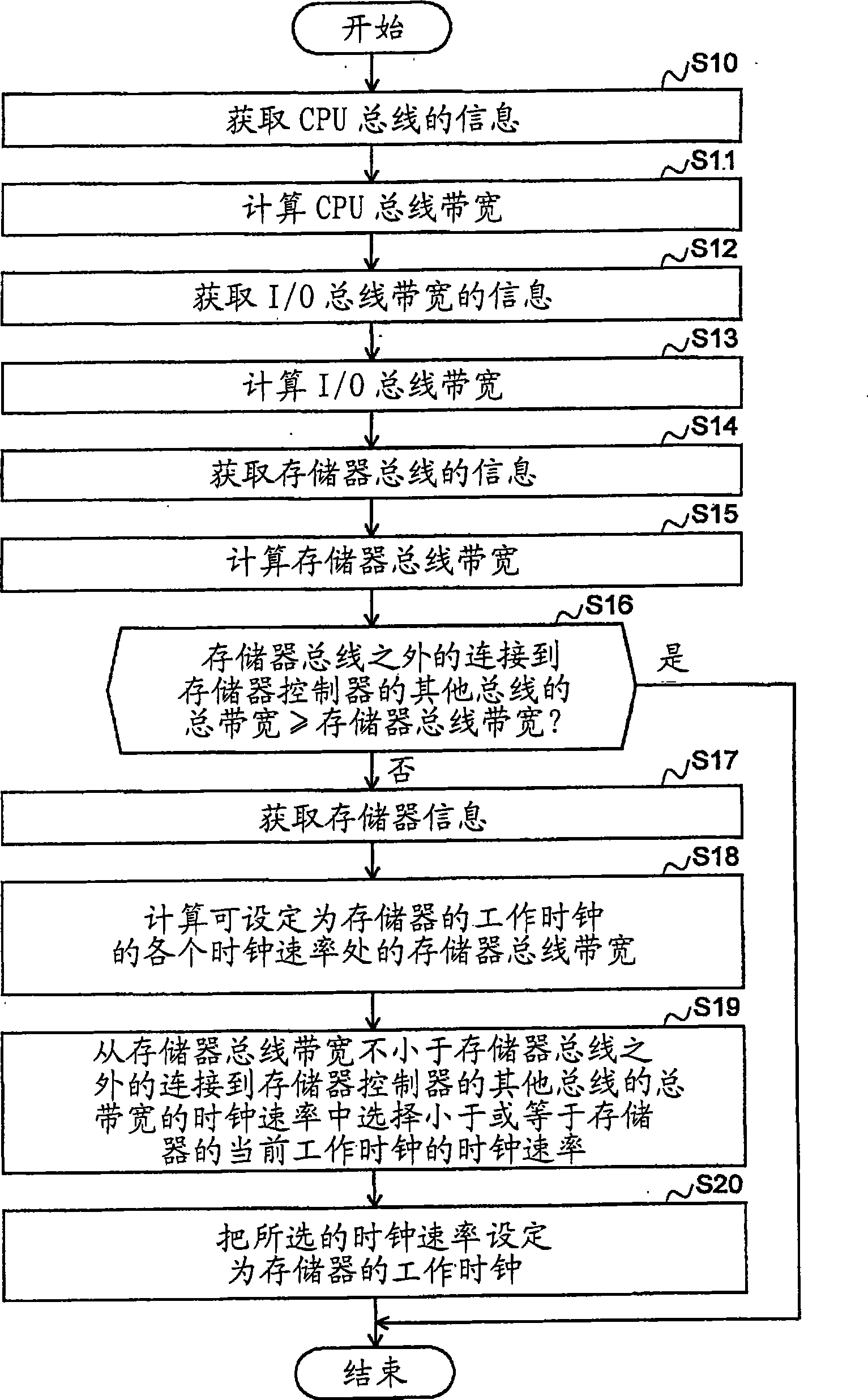

[0027] Embodiments of the present invention will be described below with reference to the drawings.

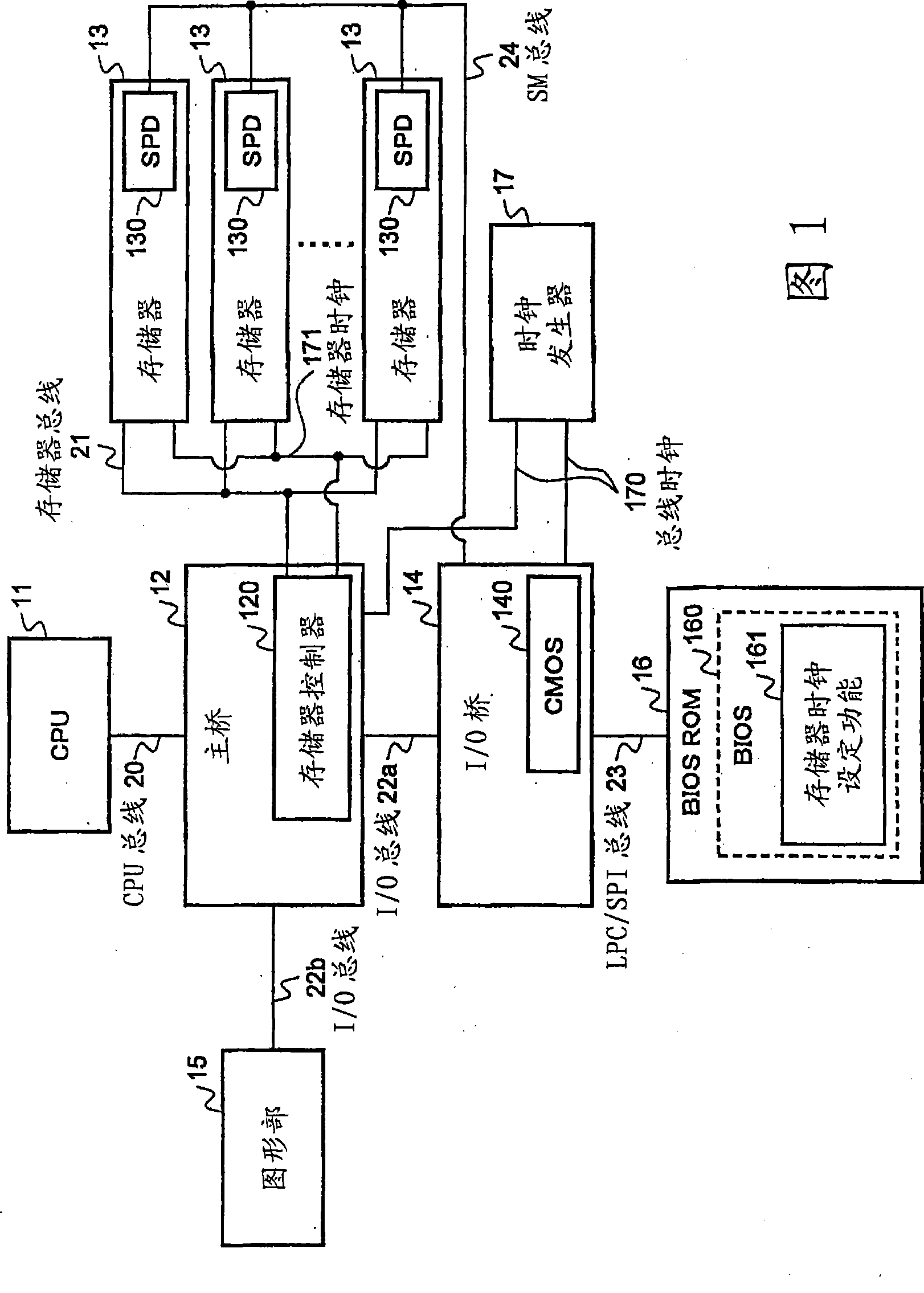

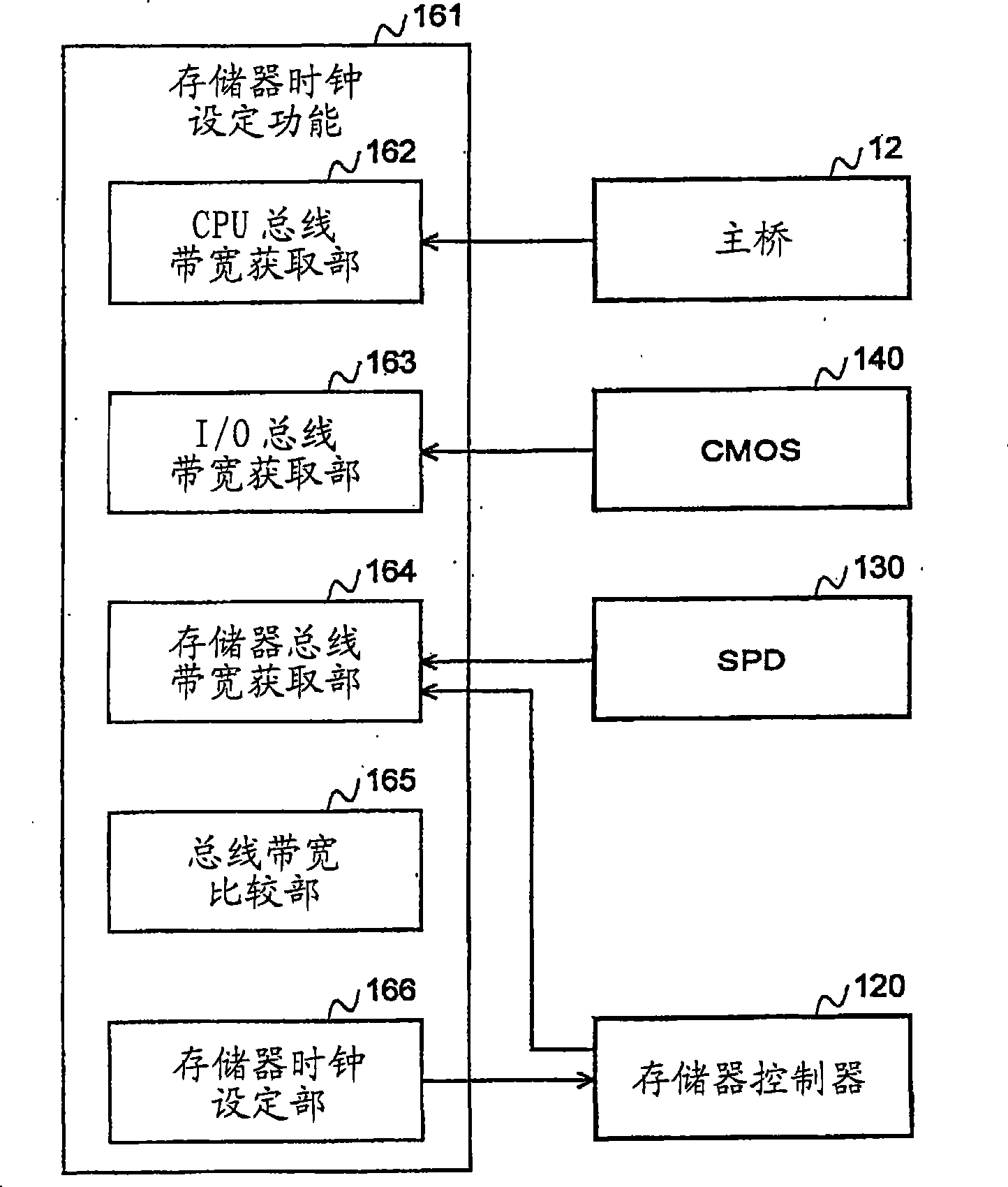

[0028] FIG. 1 is a diagram showing a configuration example of an information processing device according to an embodiment of the present invention. The information processing device includes a CPU 11 , a main bridge 12 , a memory 13 , an I / O bridge 14 , a graphics unit 15 , a BIOS ROM 16 and a clock generator 17 .

[0029] The CPU 11 is a processor that controls a system or device.

[0030] The host bridge 12 is a chip that connects the CPU 11, memory 13, and I / O, and may include a memory controller 120 according to a chipset (platform). In the example of the information processing apparatus shown in FIG. 1 , the host bridge 12 includes a memory controller 120 . In the main bridge 12, the setting of the CPU 11 is performed. The memory controller 120 controls the memory 13 to set the working clock or working timing of the memory 13 .

[0031] The memory 13 is a main storage...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More