Configurable frequency synthesizer circuit based on time-delay lock loop

A technology of frequency synthesis circuit and delay-locked loop, applied in the direction of electrical components, automatic power control, etc., can solve the problems that the user is not easy to change the frequency synthesis coefficient flexibly, and the frequency synthesis circuit of the delay-locked loop cannot, so as to improve the jitter performance , Excellent anti-jitter performance, simple principle to achieve the effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

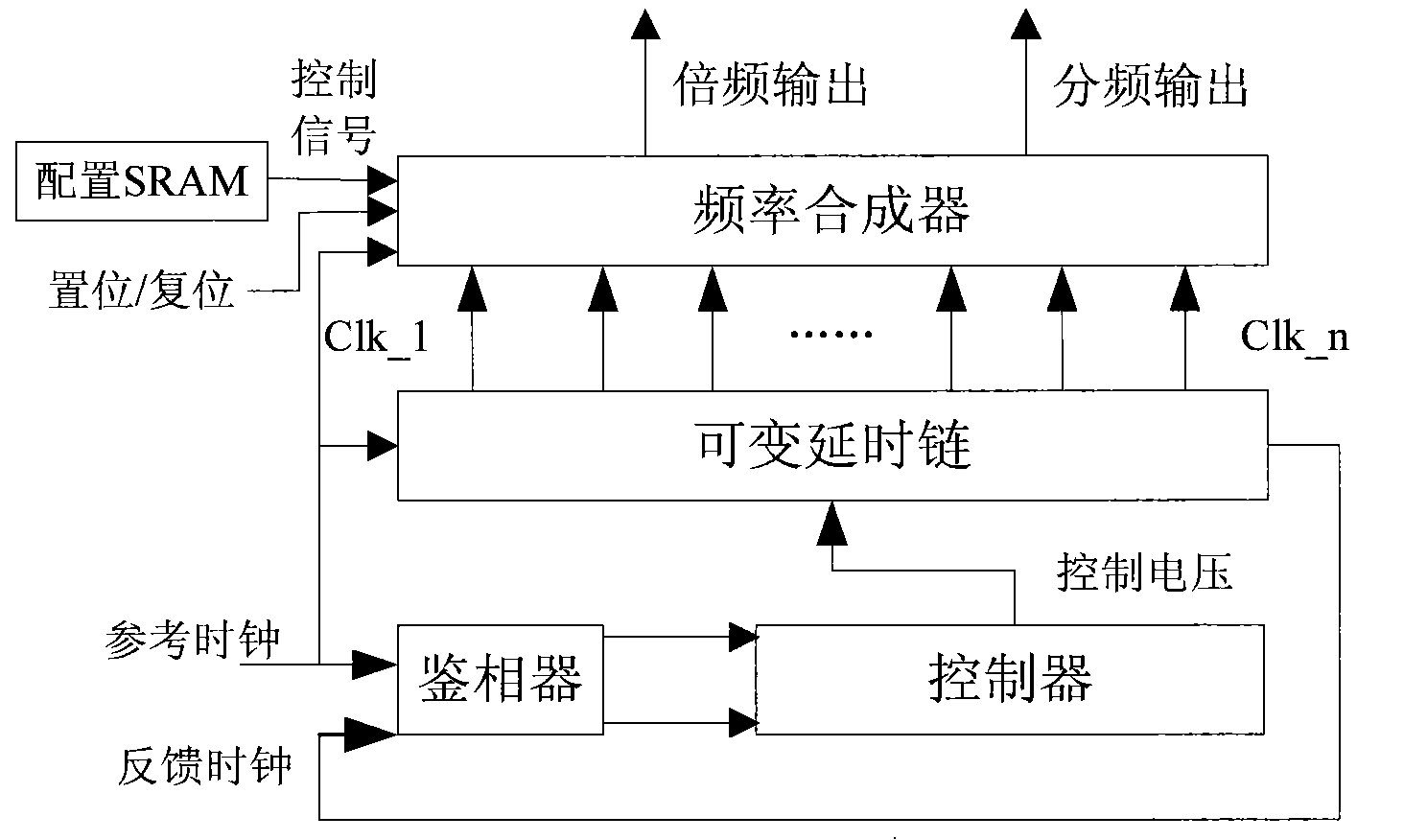

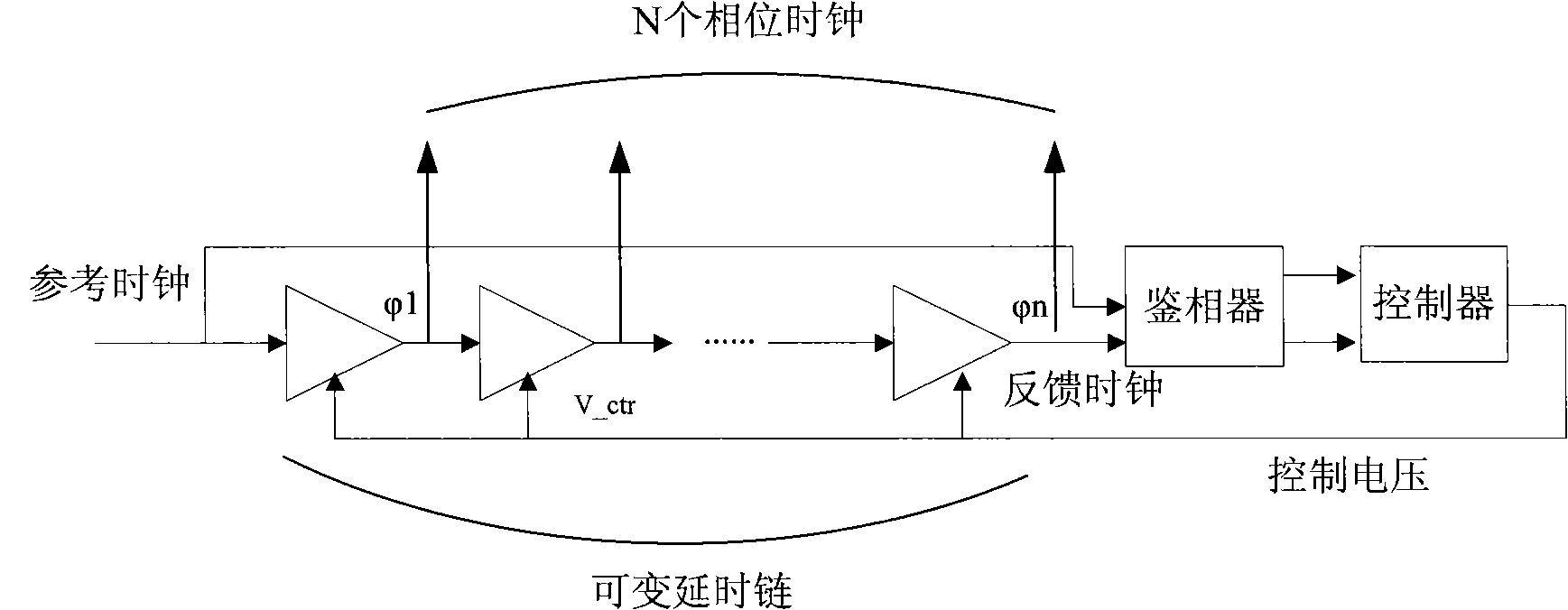

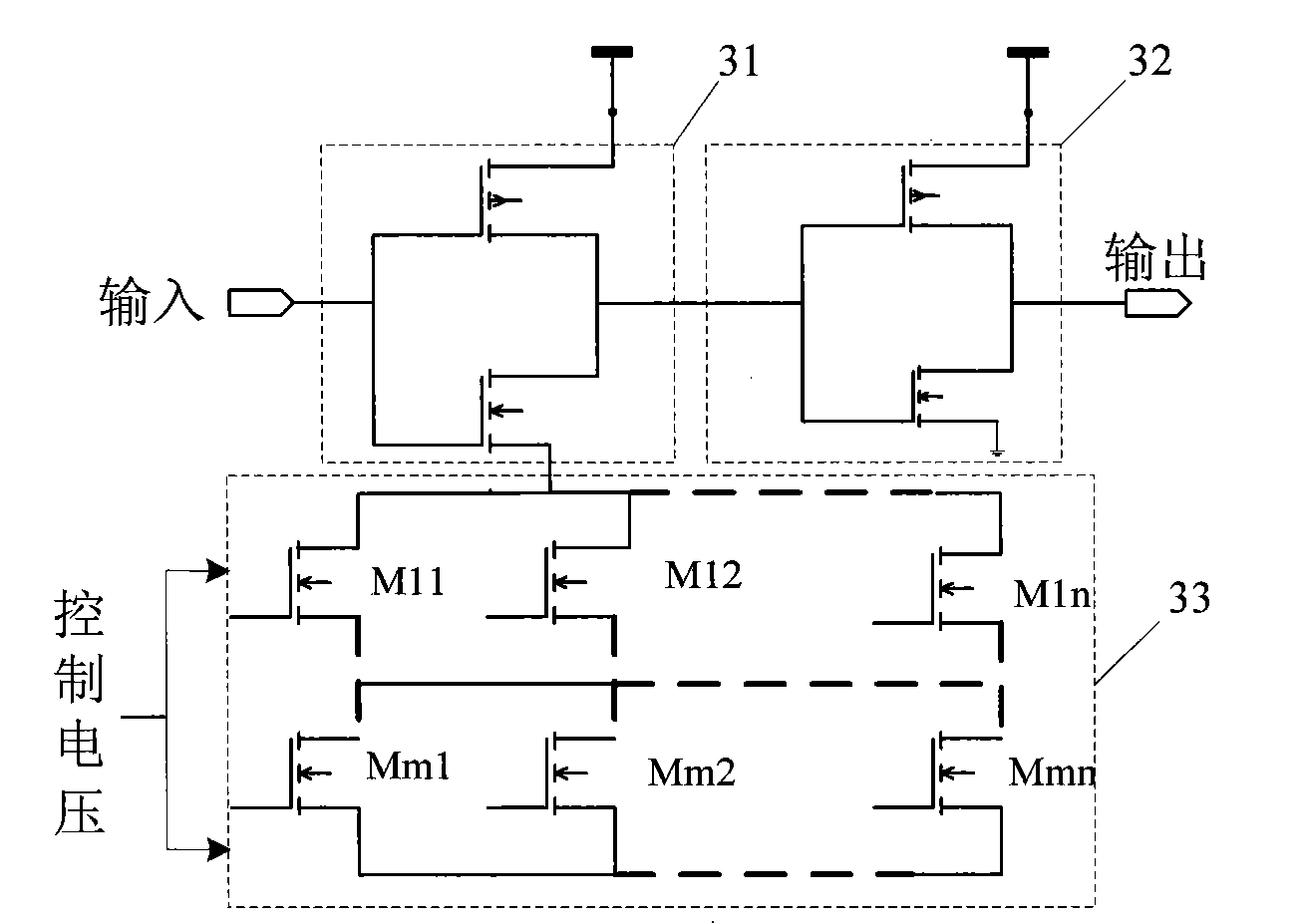

[0027] like figure 1 As shown, the configurable delay-locked loop frequency synthesis circuit of the present invention includes a delay-locked loop composed of a phase detector, a controller and a variable delay chain, a frequency synthesizer composed of a frequency multiplication synthesizer and a frequency division synthesizer , configure SRAM. The phase detector receives the reference clock and the feedback clock, and outputs the comparison signal and the lock signal after phase discrimination and comparison. After the comparison signal and the lock signal are processed by the controller, they output the control voltage to control the variable delay chain to generate N phase clocks and output them to the frequency synthesis device. The frequency synthesizer processes N phase clocks, under the control of the configuration SRAM, by selecting the appropriate phase clock to control the set / reset time of the RS flip-flop in the frequency multiplication synthesizer and frequency...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More