Multi-rate compatible digital intermediate frequency implementing apparatus and method

A technology of digital intermediate frequency and implementation method, applied in the direction of synchronization/start-stop system, etc., can solve the problems of heavy workload, unstable switching, unfavorable post-maintenance, etc., and achieve the effect of convenient simulation, simple design and wide application range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

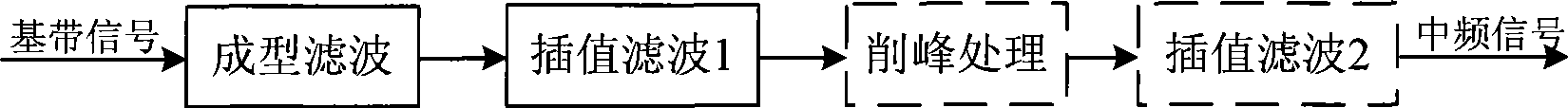

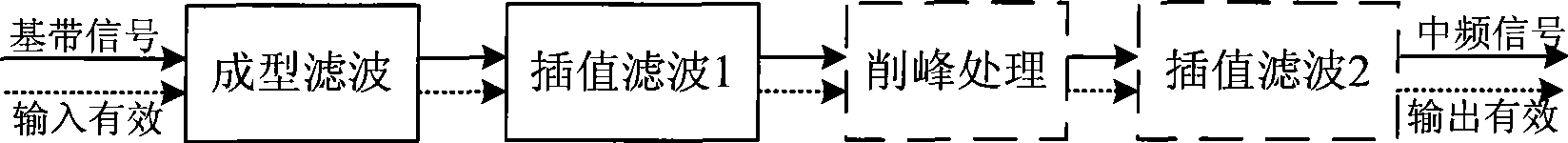

Method used

Image

Examples

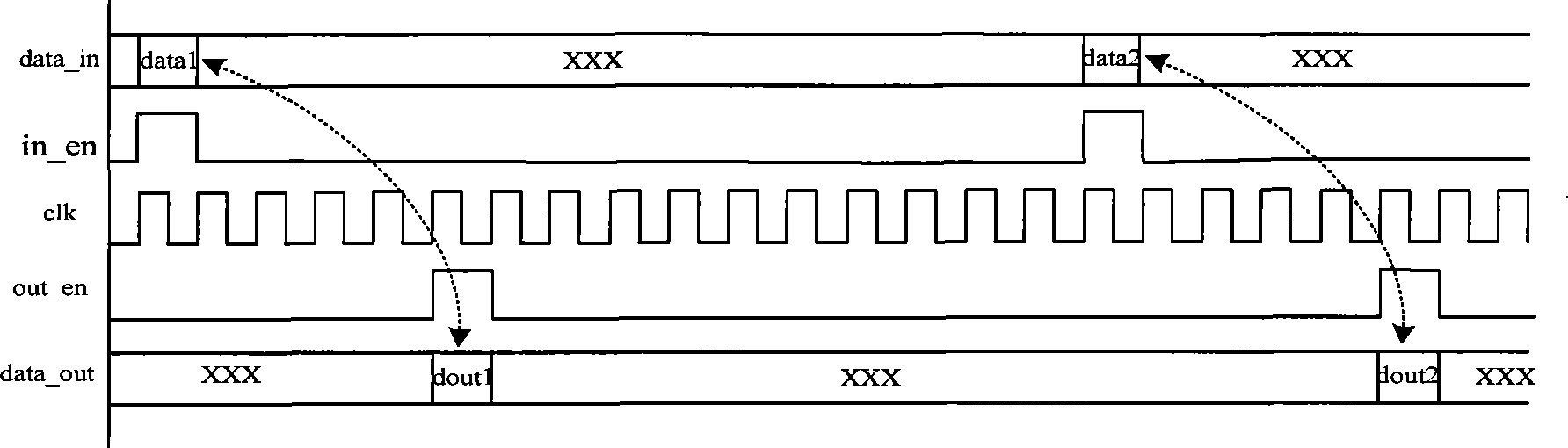

Embodiment 1

[0028]After the design of Embodiment 1 is completed, it is naturally downward compatible with the design with a baseband bandwidth of 5M. The specific processing process of Embodiment 2 requires exactly the same processing time as Embodiment 1. The difference is only the data rate of Embodiment 2. It is twice as slow as the first embodiment, so the second embodiment is longer than the first embodiment, and the invalid data (xxxx in the figure indicates invalid data) between every two valid data outputs is longer. Similar to Embodiment 1, further, if the signal rate of the last stage of the intermediate frequency is a unified rate, then a rate matching module is added at the last stage to perform interpolation filtering with different multiples of different rates to ensure that no matter what baseband rate, the final The rate of IF output is the same. If the final output rates of the intermediate frequencies do not need to be consistent, the processing of the rate matching modu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More