Active array substrate, liquid crystal display panel and method for manufacturing active array substrate

An active array and substrate technology, applied in semiconductor/solid-state device manufacturing, optics, instruments, etc., can solve problems affecting display quality and inconsistency, achieve the effect of improving display quality and avoiding uneven load effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

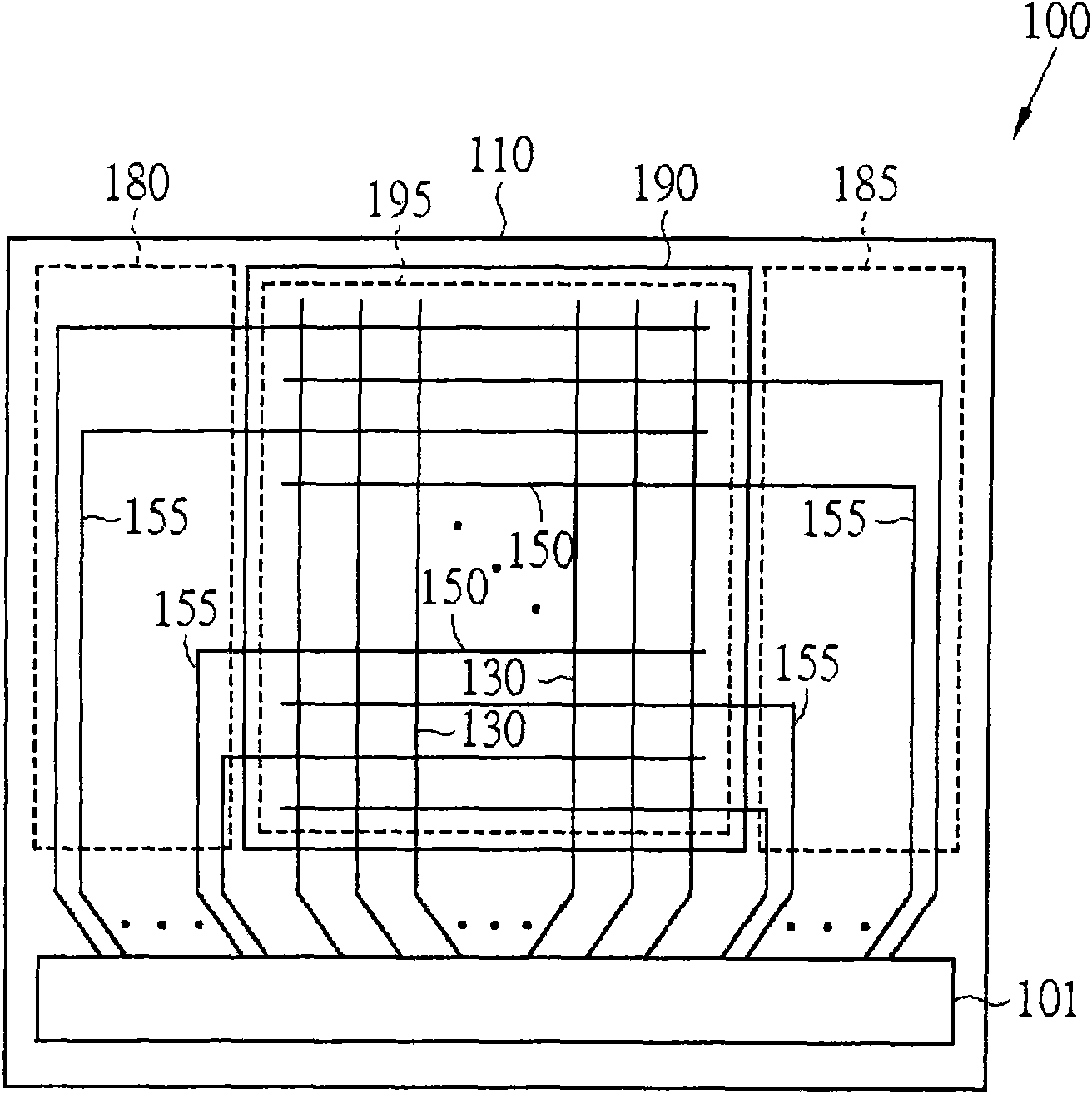

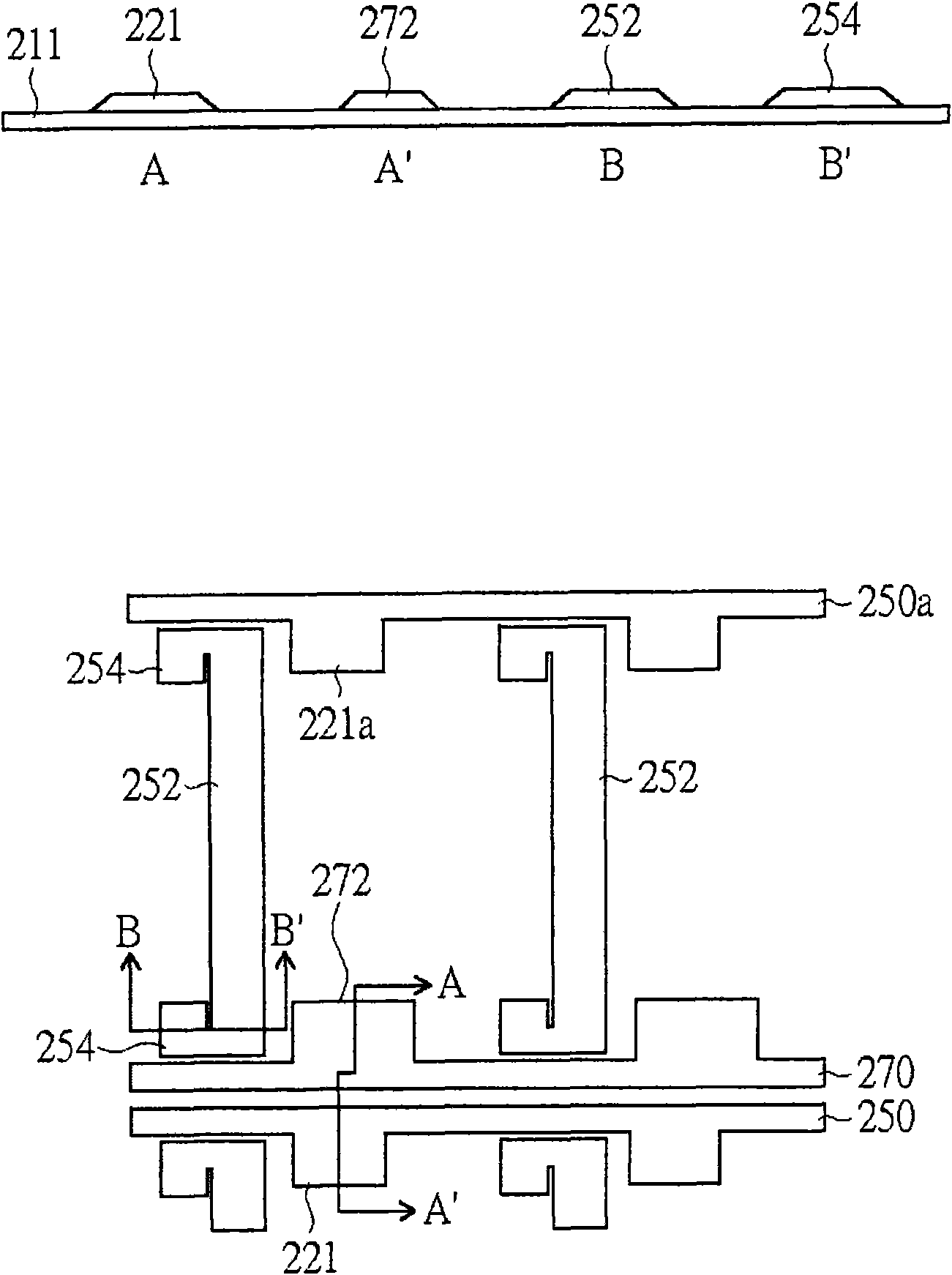

[0060] Figure 2A to Figure 2G It is a flow chart of the manufacturing method of the active array substrate according to the first embodiment of the present invention.

[0061] Please refer to Figure 2AFirstly, a substrate 211 is provided, a first conductive layer (not shown) is formed on the substrate 211, and then the first conductive layer is patterned to form scanning lines 250, 250a, gates 221, 221a, common lines 270, and capacitor lower electrodes 272 , the first part 252 and the transfer part 254 . The way of patterning the first conductive layer can be known methods such as exposure, development and etching, for example. The wire transfer part 254 is connected to the first part 252. For a pixel unit, both ends of the first part 252 can be respectively connected to a wire transfer part 254, that is, the first part 252 and the two wire transfer parts 254 can be roughly Constitute a reverse C-shaped or I-shaped, but not limited to this. The capacitor bottom electrode...

no. 2 example

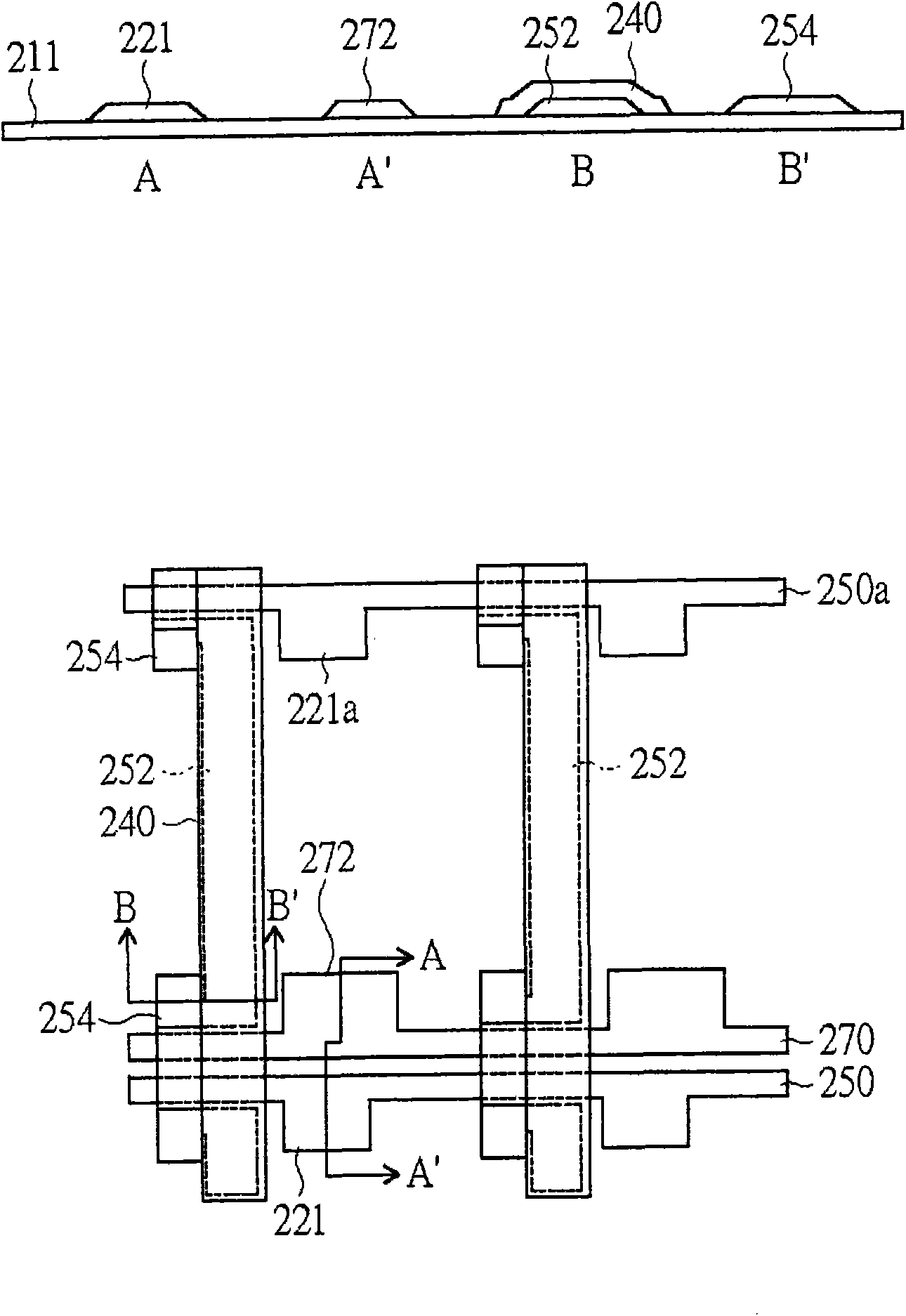

[0071] image 3 It is the active array substrate of the second embodiment of the present invention.

[0072] Please refer to image 3 , the only difference from the first embodiment is that only a part of the auxiliary semiconductor layer 282 and the data line 290 overlaps with the first portion 252 , so as to reduce the load effect slightly. The remaining components and manufacturing methods are the same or similar to those of the first embodiment, and will not be repeated here.

no. 3 example

[0074] Figure 4 It is the active array substrate of the third embodiment of the present invention.

[0075] Please refer to Figure 4 , the only difference from the first embodiment is that the auxiliary semiconductor layer 282 and the data line 290 are completely offset from the first portion 252 and do not overlap, so as to reduce the load effect. The remaining components and manufacturing methods are the same or similar to those of the first embodiment, and will not be repeated here.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More