Integrated method of raise source leakage structure complementary metal-oxide-semiconductor transistor (CMOS) and Bipolar device

A technology that improves source and drain and integrates methods. It is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, and electrical components. It can solve problems such as shallowing, epitaxial single crystal height restrictions, and slow impurity diffusion. It can expand the process window, Improve the effect of short channel effect and relax the design size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment

[0047] The inventive method specifically comprises the steps:

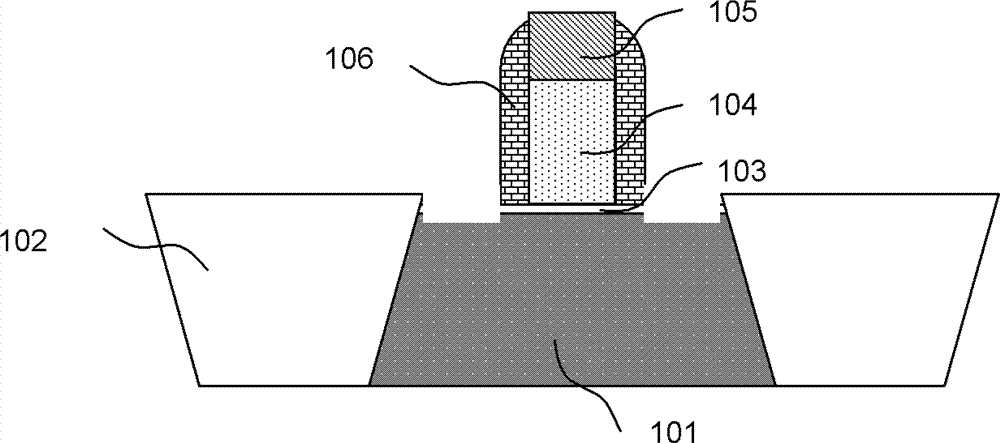

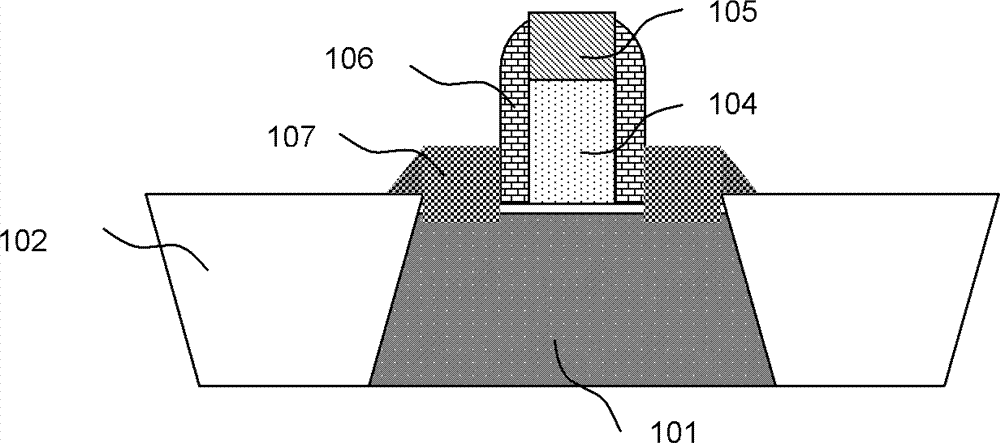

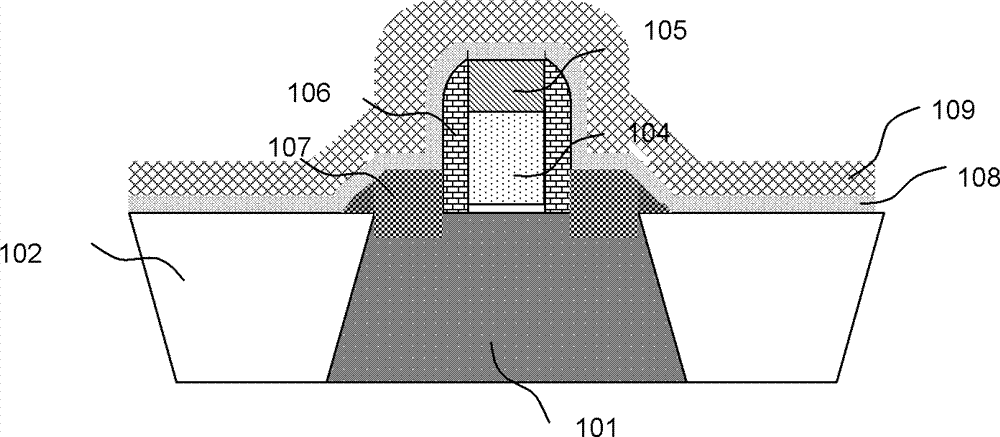

[0048] 1. If figure 1 As shown, the definition of the CMOS gate pattern and the formation of sidewalls are completed according to the traditional process flow. The CMOS regional structure includes an active region 101, a shallow trench isolation region 102, and a gate structure, wherein the gate structure is 20 from bottom to top. A gate oxide layer 103 of -70 angstroms, a gate polysilicon 104 of about 2000 angstroms, a top dielectric film 105 of about 1000 angstroms, and a gate spacer 106. On the basis of the traditional shallow trench isolation (STI) structure, a traditional gate structure is formed. After the LDD is implanted, the gate spacer 106 is formed. When the gate spacer 106 is formed, anisotropic etching is used to make silicon The active area 101 of the substrate has a loss of about 20-100 Angstroms. Because the silicon substrate is damaged during the etching process, polysilicon will grow in the so...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More