Failure testing system for embedded logic cores in system on chip

A technology of logic core and system-on-chip, applied in the field of integrated circuit fault test system

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

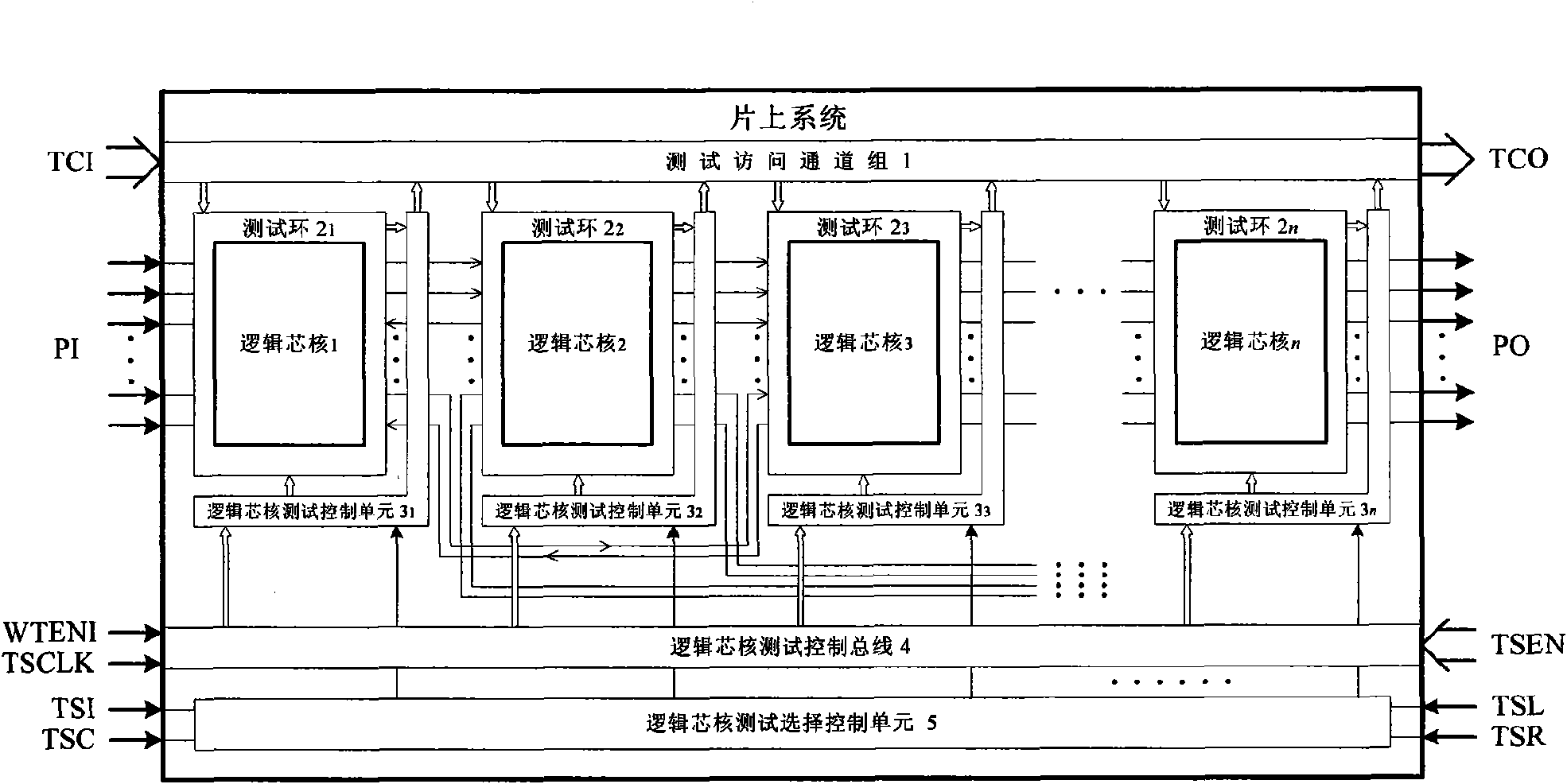

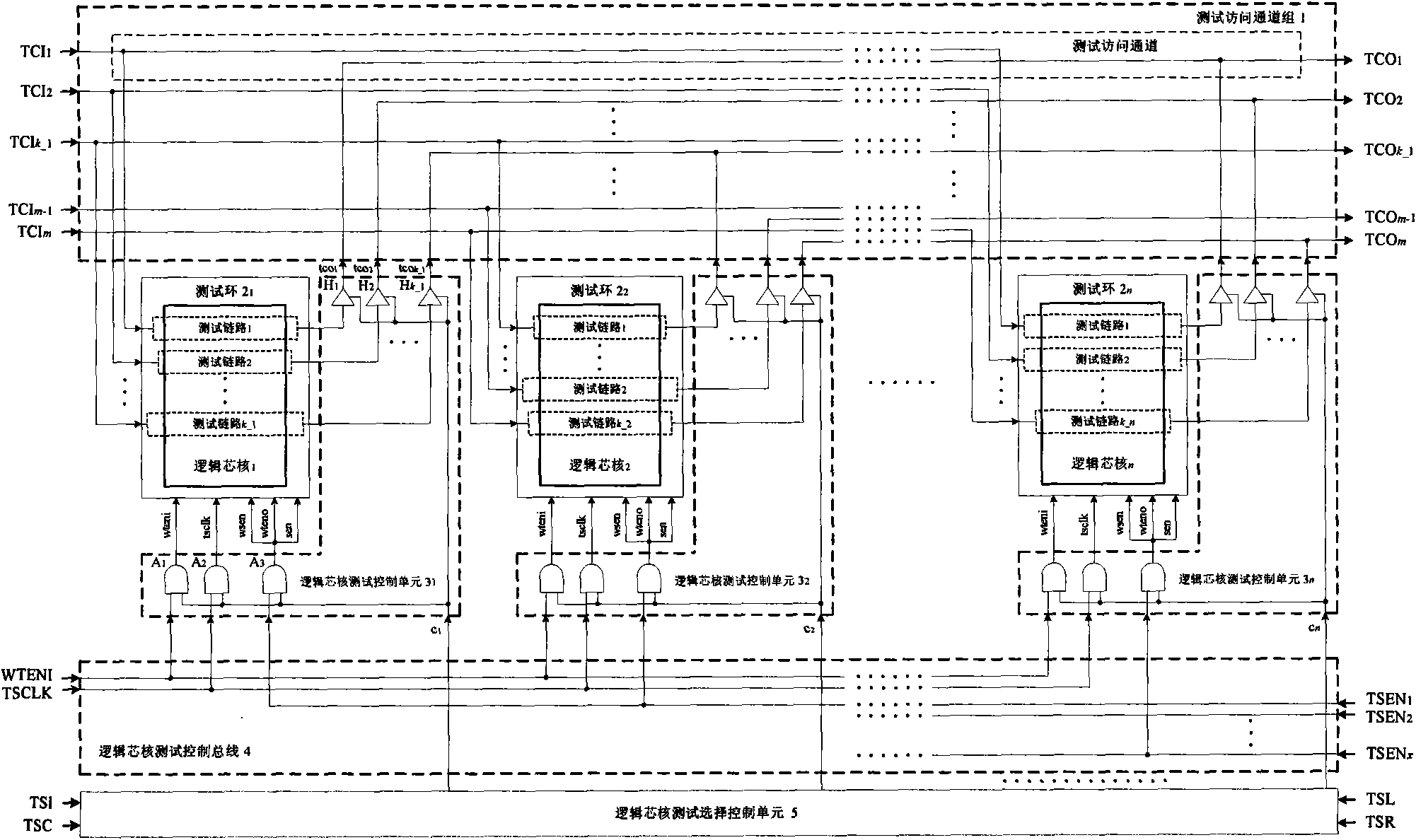

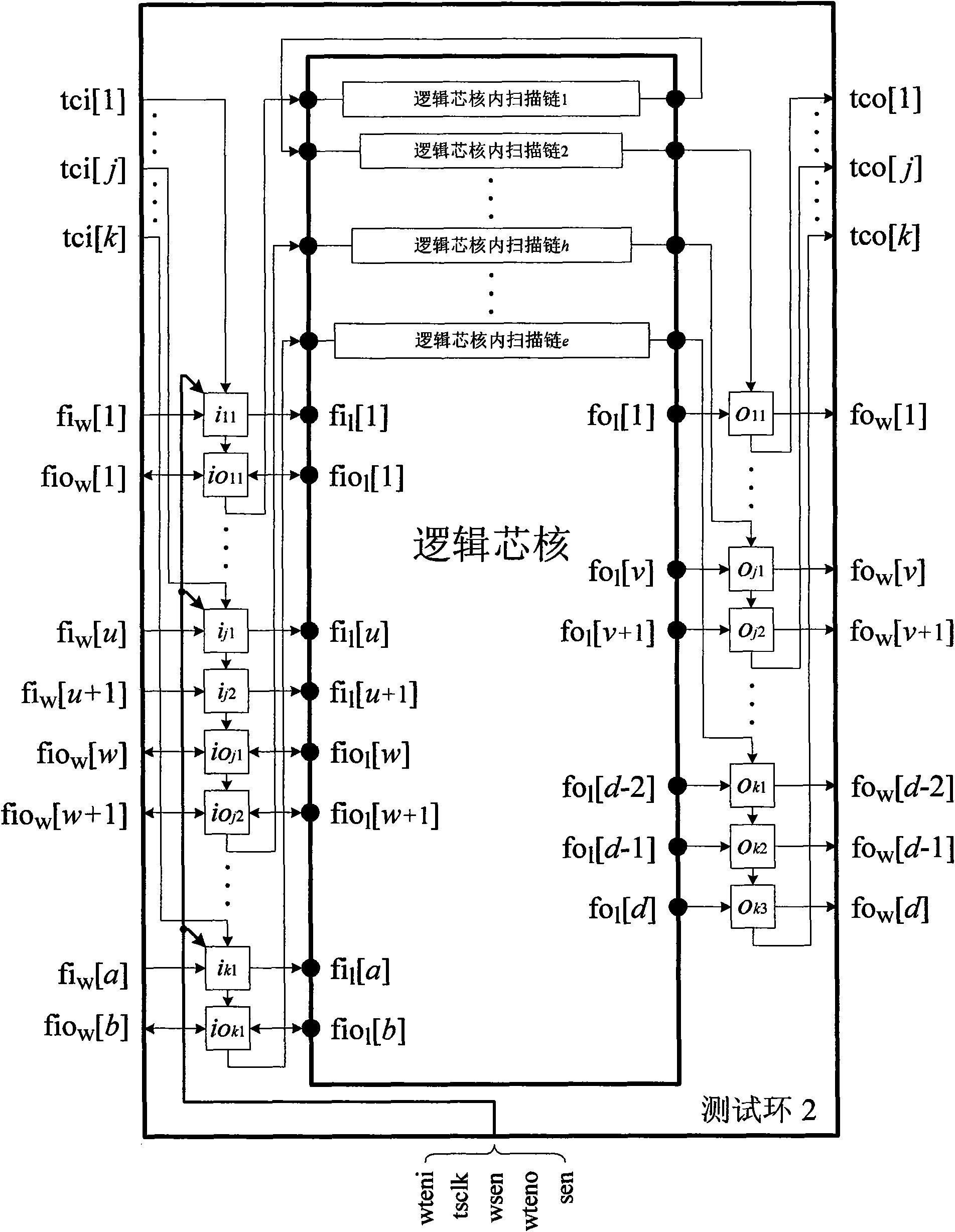

[0034] A preferred embodiment of the present invention is: see figure 1 , the fault test system of the embedded logic core in the SoC is a circuit added to improve the fault test of the embedded logic core. Its circuit consists of a test access channel group 1, n test rings 2, n logic core test control units 3, a logic core test control bus 4 and a logic core test selection control unit 5, where n is the system on chip The number of logical cores in .

[0035] This circuit structure is: see figure 1 , the test access channel group 1 has a set of external test access channel signal input pins TCI and a set of external access test channel signal output pins TCO, and the on-chip output test ring 2 connected to each logic core; each test ring 2 There is a group of external system-on-chip function signal input pins PI or system-on-chip function signal output pins PO, and the internal logic core and output connections are connected to the logic core test control unit 3 and other t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More