Flash chip detecting method based on boundary scan

A technology of chip detection and boundary scan, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems of lack of systematic testing and limitations of chip testing versatility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

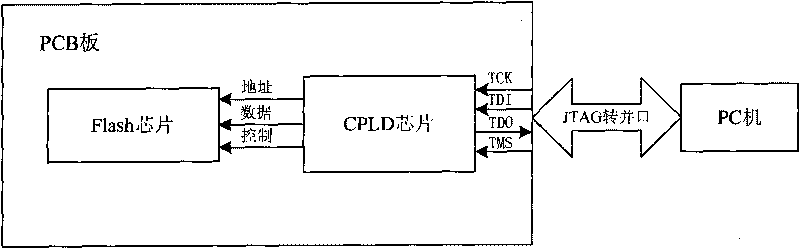

[0023] The working principle of the present invention is as follows:

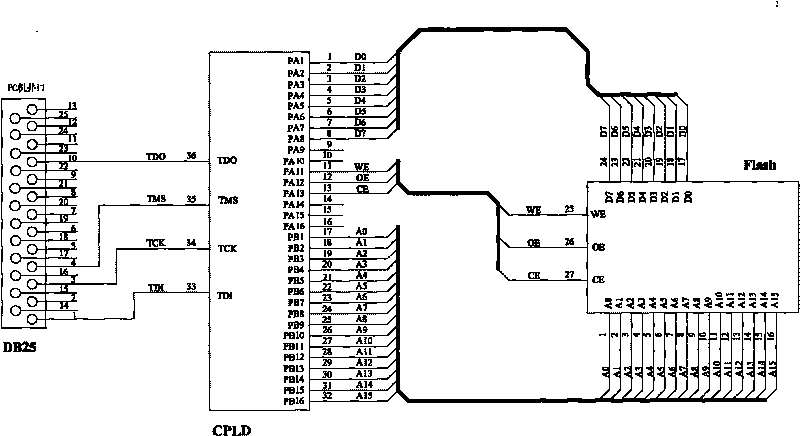

[0024] Connect the JTAG test ports TDI, TMS, TCK, and TDO of the CPLD chip to the parallel port of the upper PC, and write the control instructions and target codes to the JTAG port from the parallel port of the PC to the BSR (Boundary Scan Register) of JTAG through the program , BSR is composed of BSC (Boundary Scan Cell) connected in series. When designing the PCB, connect the data scan chain, address scan chain, and control scan chain of the CPLD to the data lines, address lines, and control lines of the Flash chip under test. There are corresponding signals sent to its BSC on the pins of the BSC, and the signals can be sent to the Flash under test through the corresponding pins of the BSC.

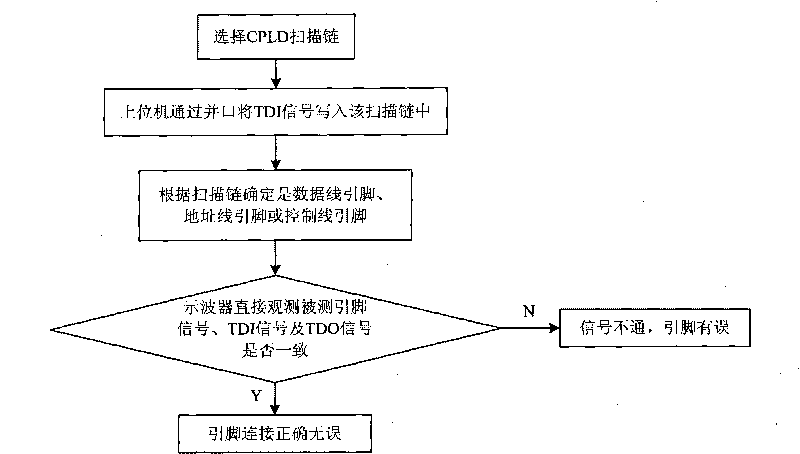

[0025] Among the present invention, CPLD chip adopts the CPLD device LFXP2_5E_XXQ208 of Lattic Company, combines figure 1 with image 3 Shown, method flow process of the present invention is as follows:

[0026]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More