Multi-channel flash memory chip array structure and write-in and read-out methods thereof

A flash memory chip, multi-channel technology, applied in the direction of information storage, static memory, digital memory information, etc., can solve the problem of slow read and write speed of flash memory data, achieve fast read and write speed, high reliability, and ensure the effect of reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

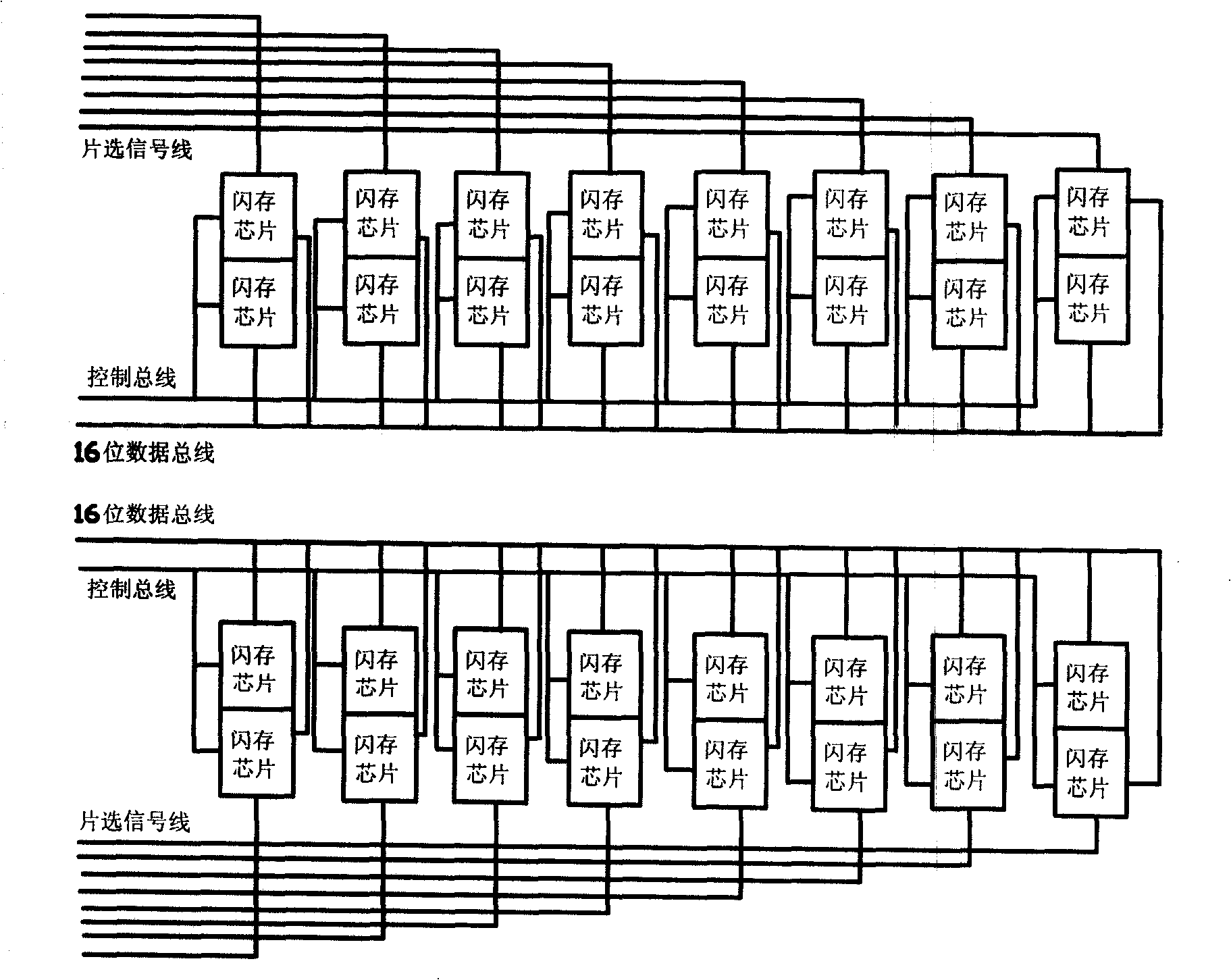

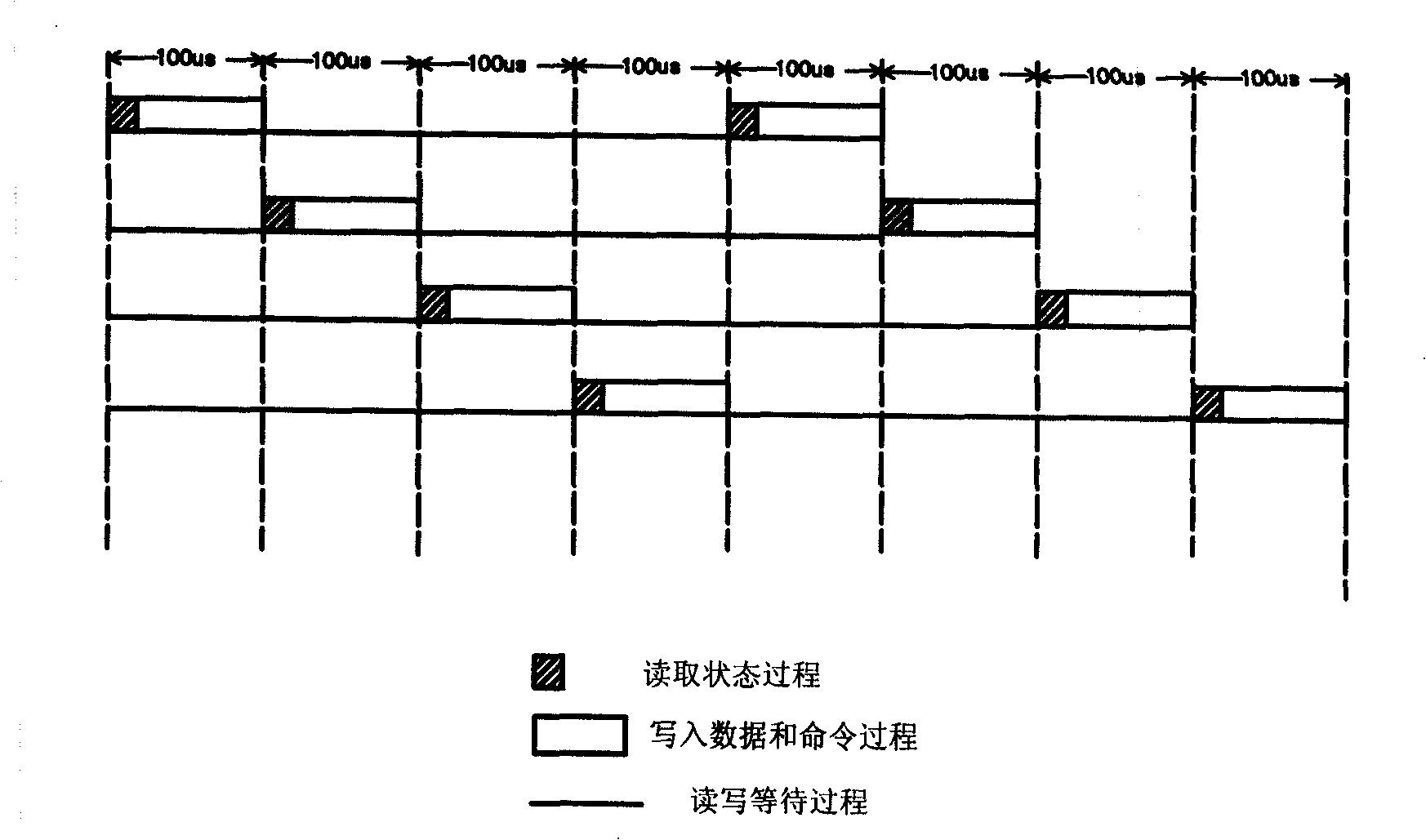

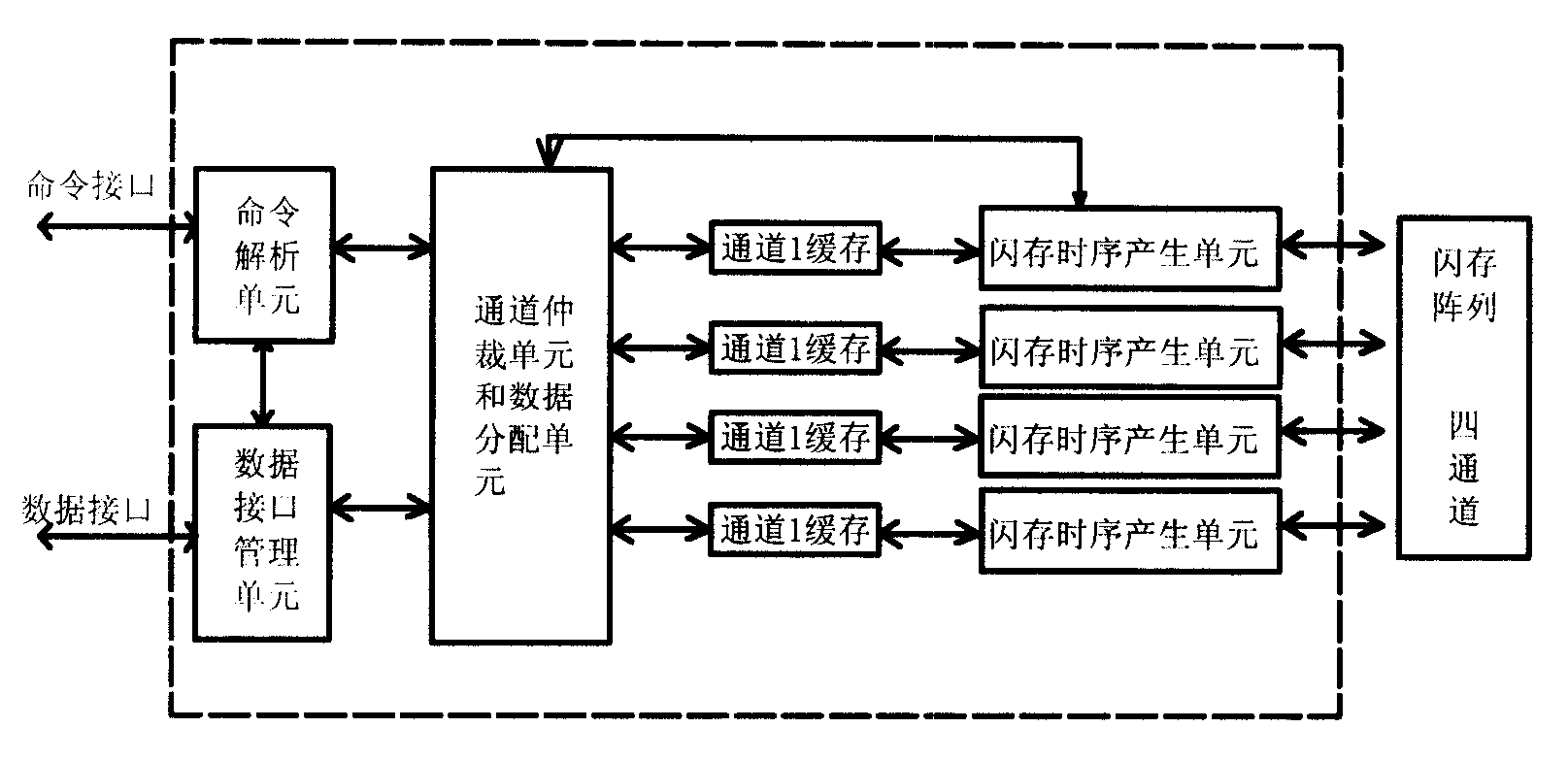

[0037] A multi-channel flash memory chip array structure of the present invention includes a flash memory chip, and multiple channels formed by a data bus, a control bus and a chip selection signal line connected to the flash memory chip, and each flash memory chip corresponds to a chip selection signal line , The chip select signal line of each chip is independent, and all flash memory chips in each channel share a data bus and a control bus independent of other channels. When the flash memory chips in each channel form a flash memory chipset cascade, the chipset is composed of 2 or 4 chips into a 16-bit or 32-bit wide data bus. The purpose of building the chipset is to increase the bit width and increase the unit The writing speed of data within the time, the chips in the chipset share the control bus and the chip select bus, and the data bus is not shared.

[0038] The present invention adopts multi-channel, ie, multi-dimensional array method to manage flash memory chips. For ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More