Clock synchronous circuit

A clock synchronization and circuit technology, applied in the field of data transmission, can solve the problems of short delay unit delay time, large balanced delay, and data cannot be accurately collected, and achieve the effect of making up for the lack of balance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

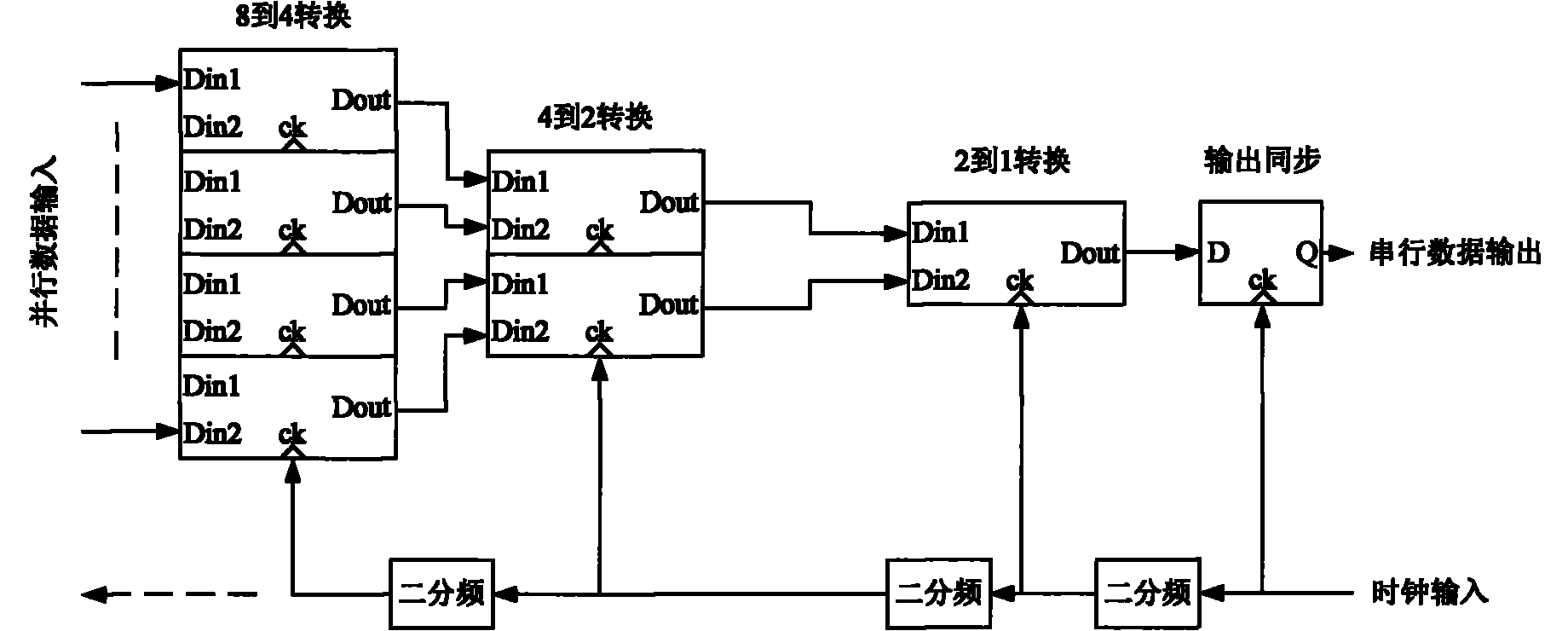

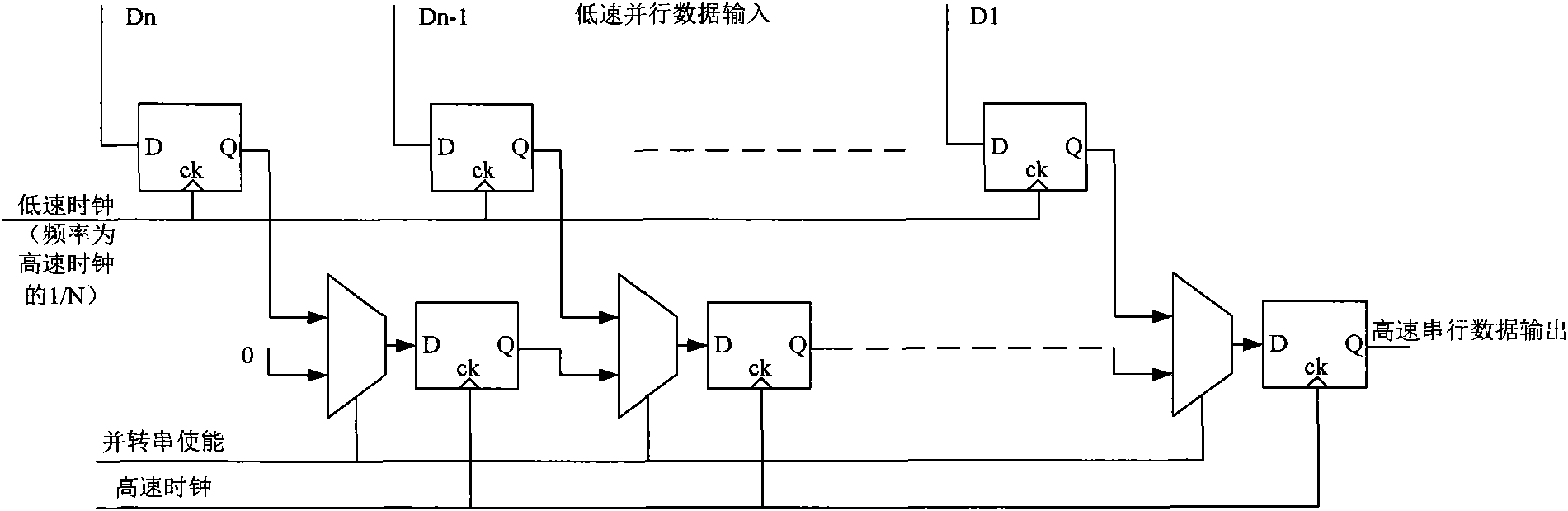

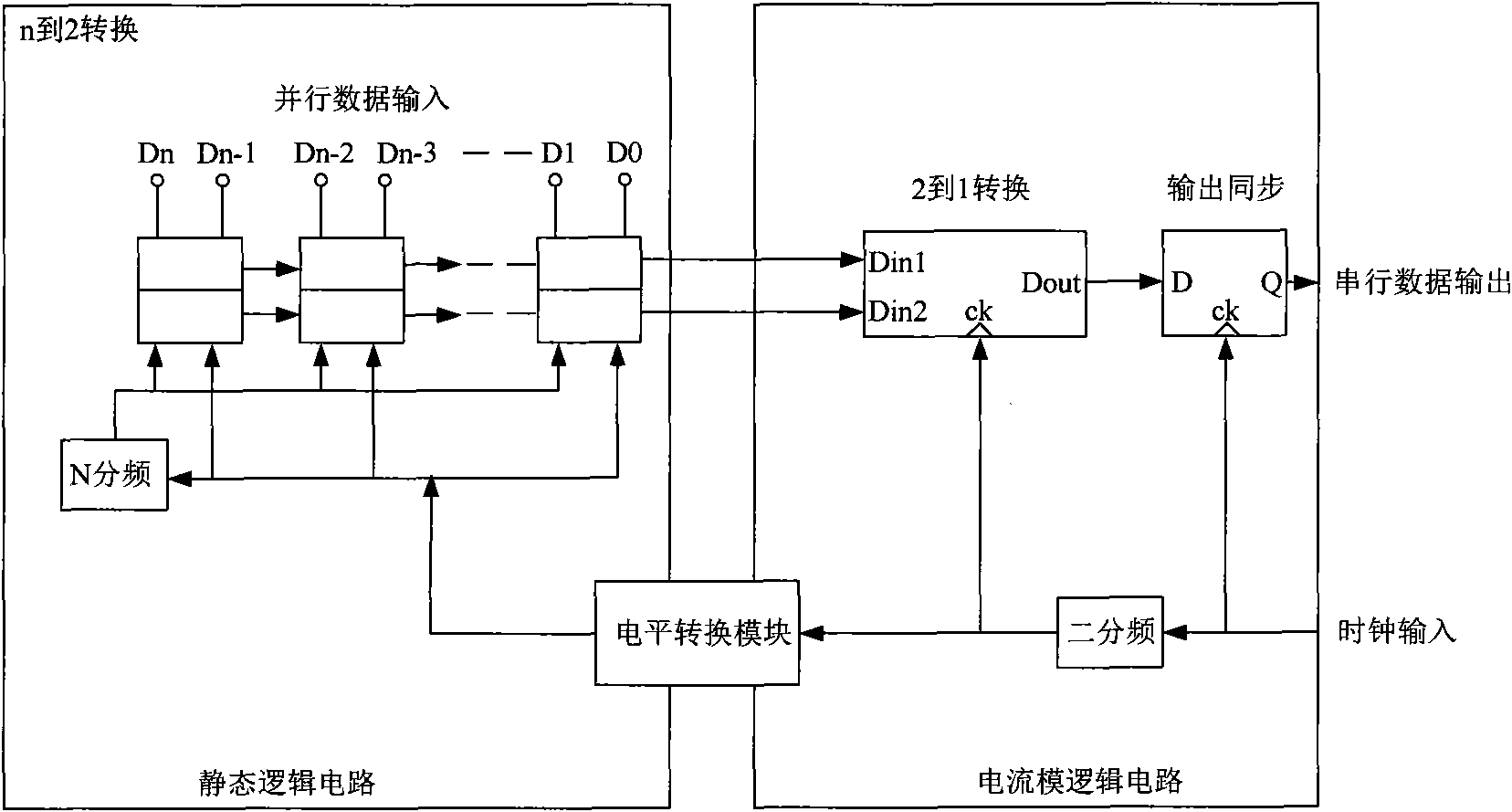

[0029] Figure 4 It is a schematic structural diagram of a parallel-to-serial conversion circuit with a delay chain loop, which can explain the application of the present invention. The delay chain loop of the present invention can achieve synchronization before and after the clock signal level conversion, and the reliability is enhanced and more economical than the prior art. power consumption. Figure 4 The parallel-serial conversion circuit shown includes static logic circuit (parallel-serial conversion circuit with shift register structure), current mode logic circuit (parallel-serial conversion circuit with tree structure) and delay chain loop. The delay chain circuit includes a delay chain module, two level conversion modules, a sampling module, and a delay chain control module. The clock signal used by the current mode logic circuit is a CML level clock signal. The clock signal is converted into a CMOS Logical level clock after being level-converted and then adopted by...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More