SOI (Silicon on Insulator) variable buried oxide layer thickness device and preparation method thereof

A buried oxide layer and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve problems such as the inability to make full use of the drift region, and achieve the effect of uniform surface electric field and improved breakdown performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

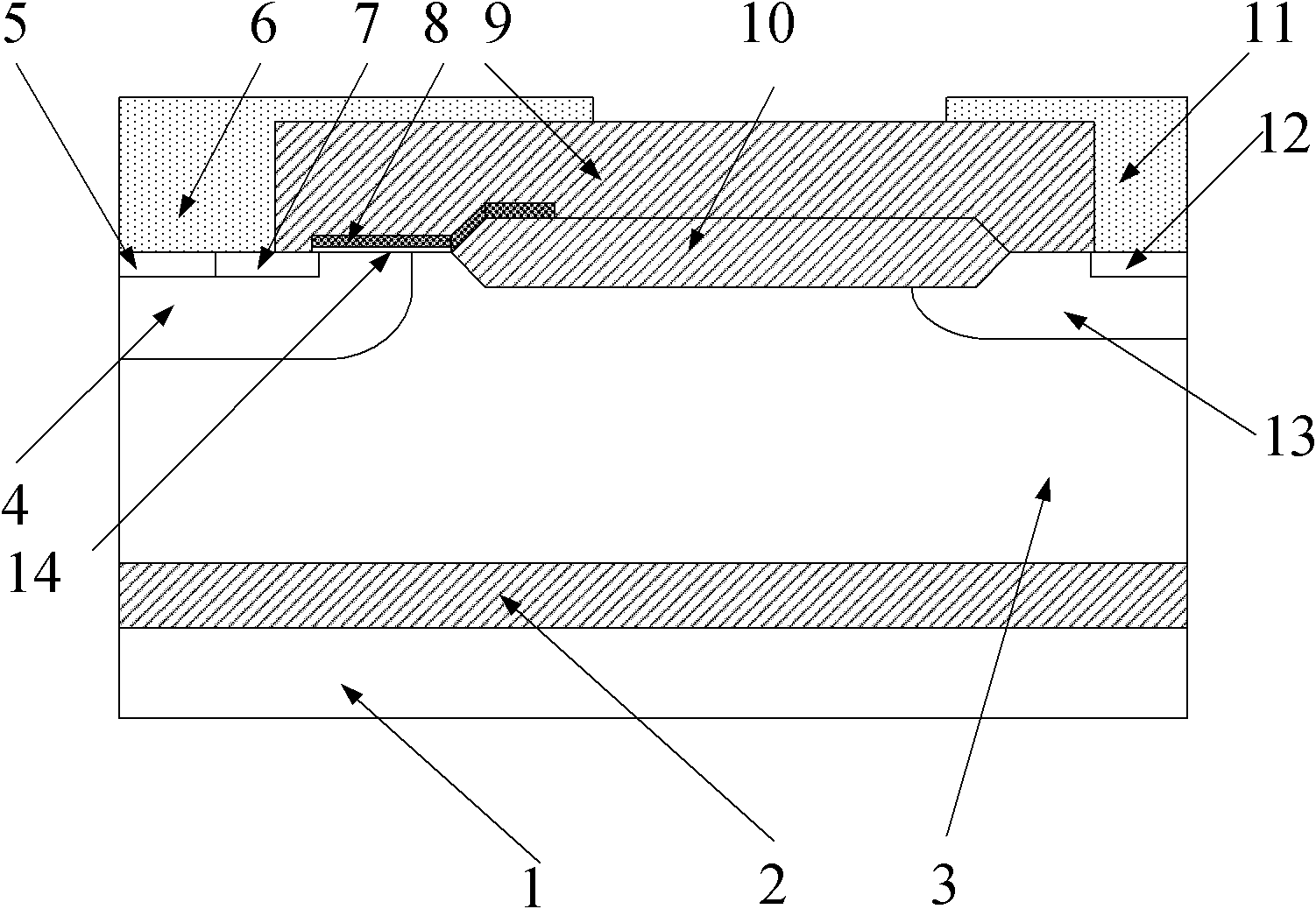

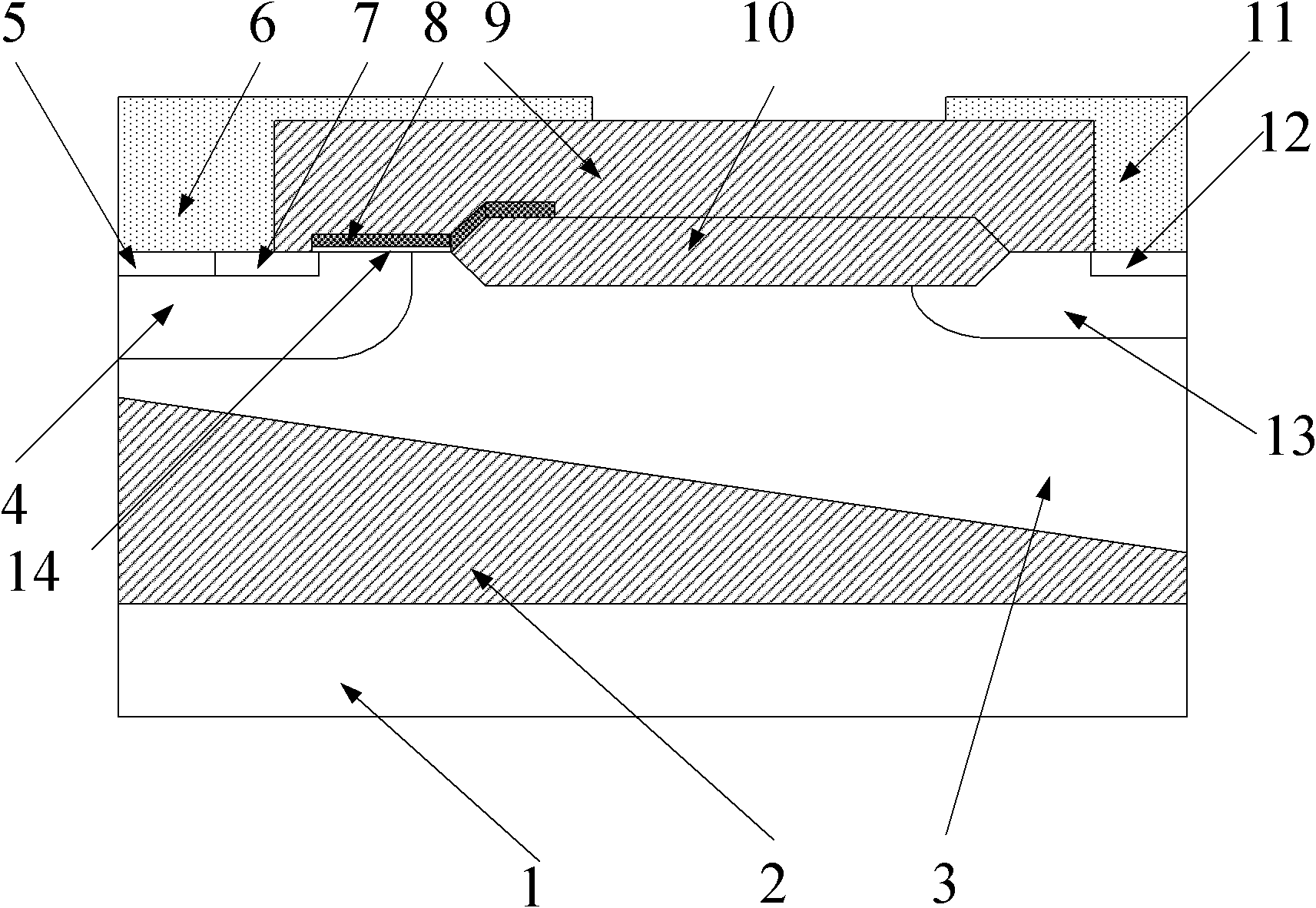

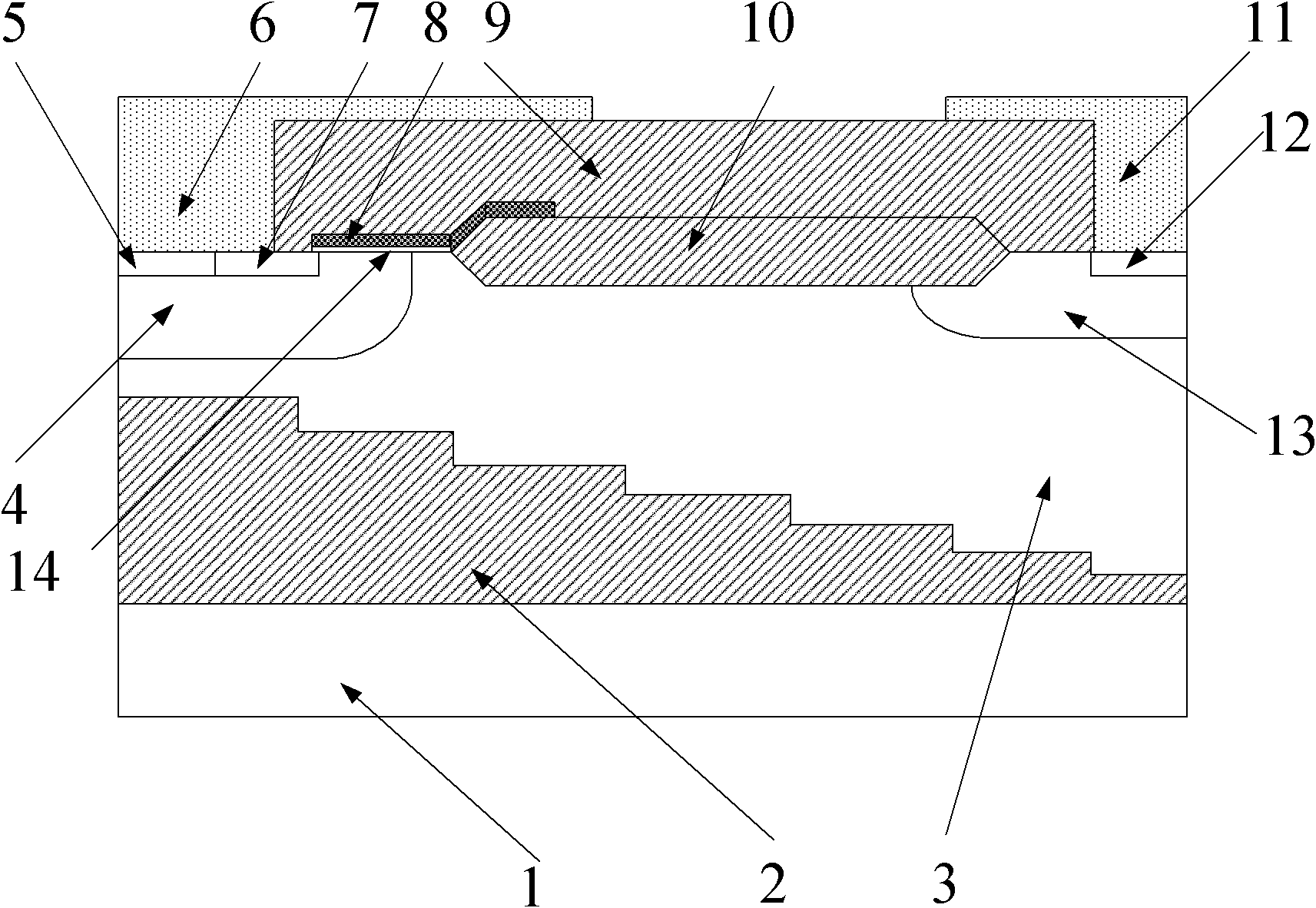

[0031] In the SOI variable buried oxide layer thickness device in this example, the thickness variation of the buried oxide layer can be continuous or stepped. The cross-sectional view of the SOILDMOS device when the buried oxide layer is continuously changing is as follows figure 2 , the cross-sectional view of the SOILDMOS device when the buried oxide layer changes in steps is as follows image 3 , the breakdown characteristic curves of conventional SOILDMOS devices and the SOILDMOS devices of this embodiment are as follows Figure 4 , the surface field distribution characteristic curves of the conventional SOILDMOS device and the SOILDMOS device of this embodiment are as follows Figure 5 , the conventional SOI LDMOS device and the SOILDMOS device of this embodiment have breakdown voltage and drift region concentration variation curves as shown in Image 6 .

[0032] The thickness of the buried oxide layer of the SOI variable buried oxide layer thickness device gradually...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More