Semiconductor device, and method for manufacturing the same

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve problems such as difficulty in forming high-performance transistors and reduced carrier mobility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0381] figure 1 is an equivalent circuit using the CMOS inverter of the present invention. Hereinafter, the circuit operation of the CMOS inverter will be described. The input signal Vin1 is applied to the gates of both Qn11 belonging to NMOS and Qp11 and Qp12 belonging to PMOS. When Vin1 is "1", Qn11 belonging to NMOS will be in ON state, Qp11 and Qp12 belonging to PMOS will be in OFF state, and Vout1 will be in "0". On the contrary, when Vin1 is "0", Qn11 belonging to NMOS will be OFF, Qp11 and Qp12 belonging to PMOS will be ON, and Vout1 will be "1". As described above, the CMOS inverter operates so that the signal of Vout1 which is the output value becomes an inverse value with respect to the signal of Vin1 which is the input value.

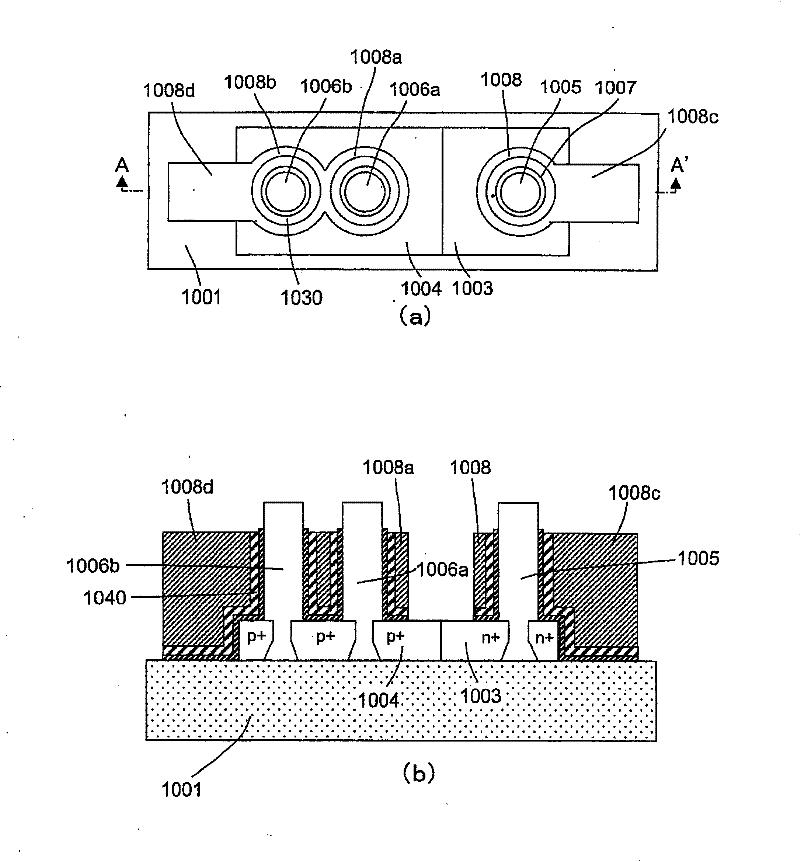

[0382] figure 2 is a plan view of a CMOS inverter using the present invention. image 3 (a) and (b) are figure 2 Sectional view of tangent line A-A' and B-B' in . Below, refer to figure 2 and image 3 To illustrate the present in...

Embodiment 2

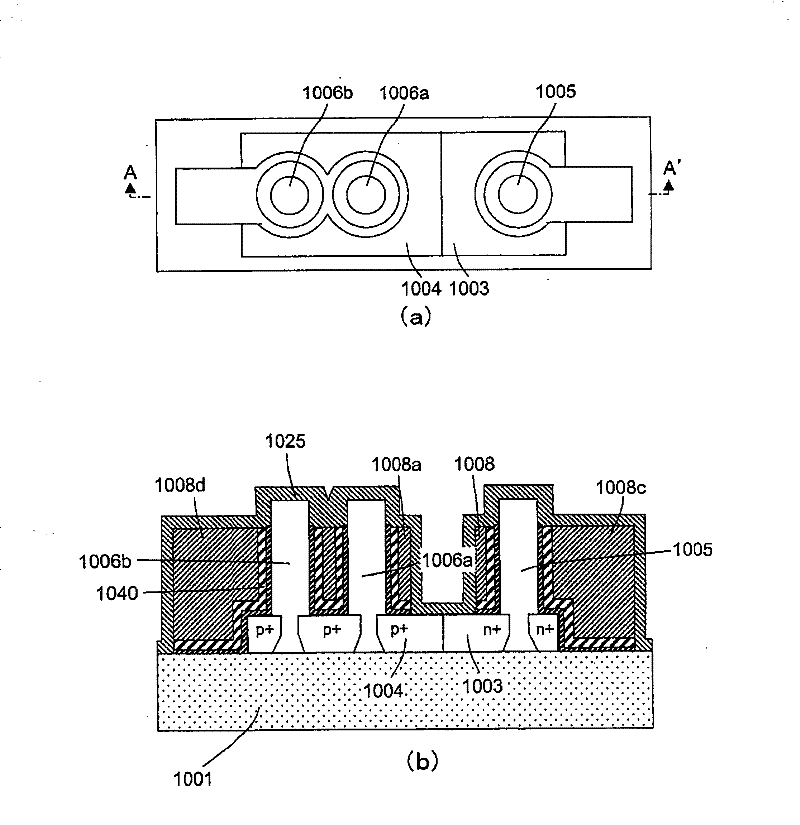

[0430] The present embodiment is an embodiment in which a CMOS inverter is configured by SGT having a structure in which a silicide layer is formed on the drain diffusion layer formed on the entire surface of the planar silicon layer and the source diffusion layer on the columnar silicon layer. By forming the silicide layer on the entire surface of the drain diffusion layer formed on the planar silicon layer, the parasitic resistance of the drain diffusion layer can be reduced. In addition, by forming a silicide layer on the source diffusion layer on the columnar silicon layer, the parasitic resistance of the source diffusion layer can be reduced. The silicide layer formed on the drain diffusion layer and the source diffusion layer can be formed only on the drain diffusion layer and the source diffusion layer in the same step in a self-aligned manner.

[0431] Figure 32 is an equivalent circuit using the CMOS inverter of the present invention. Hereinafter, the circuit opera...

Embodiment 3

[0452] The present example is an example of an SGT having a structure in which a contact portion formed on an upper portion of a columnar silicon layer is shared by a plurality of columnar silicon layers.

[0453] Figure 43 is an equivalent circuit using the CMOS inverter of the present invention. Since the circuit operation of the CMOS inverter is the same as that of Embodiment 2, it is omitted here.

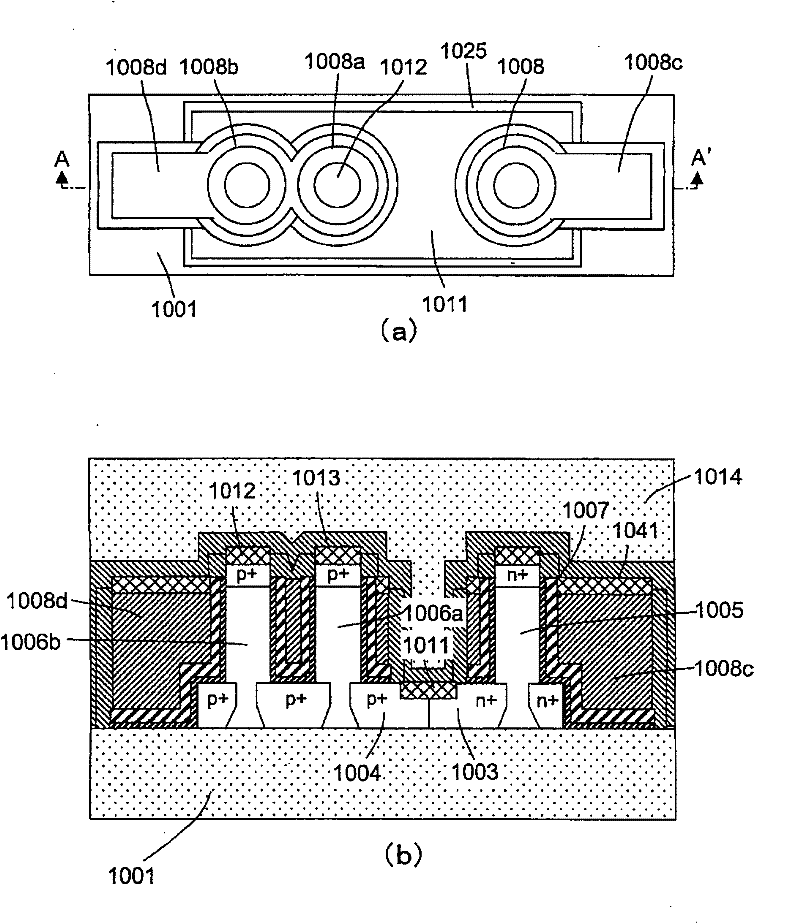

[0454] Figure 44 is a plan view of a CMOS inverter using the present invention. Figure 45 (a) and (b) are Figure 44 Sectional view of tangent line A-A' and B-B' in .

[0455] The difference between this embodiment and Embodiment 2 is that in this example, the source diffusion layer on the upper part of the two adjacent columnar silicon layers (306a, 306b) of Qp41, Qp42 belonging to PMOS is formed by sharing The rectangular contact portion 316c is connected. Specifically, when the interval between adjacent columnar silicon layers is smaller than the minimum contact por...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More