Method for exposing semiconductor substrate and invalidation analysis method

A semiconductor and substrate technology, which is applied in the field of failure analysis of semiconductor devices, can solve problems such as damage to semiconductor substrates, and achieve the effect of ensuring accuracy and improving accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

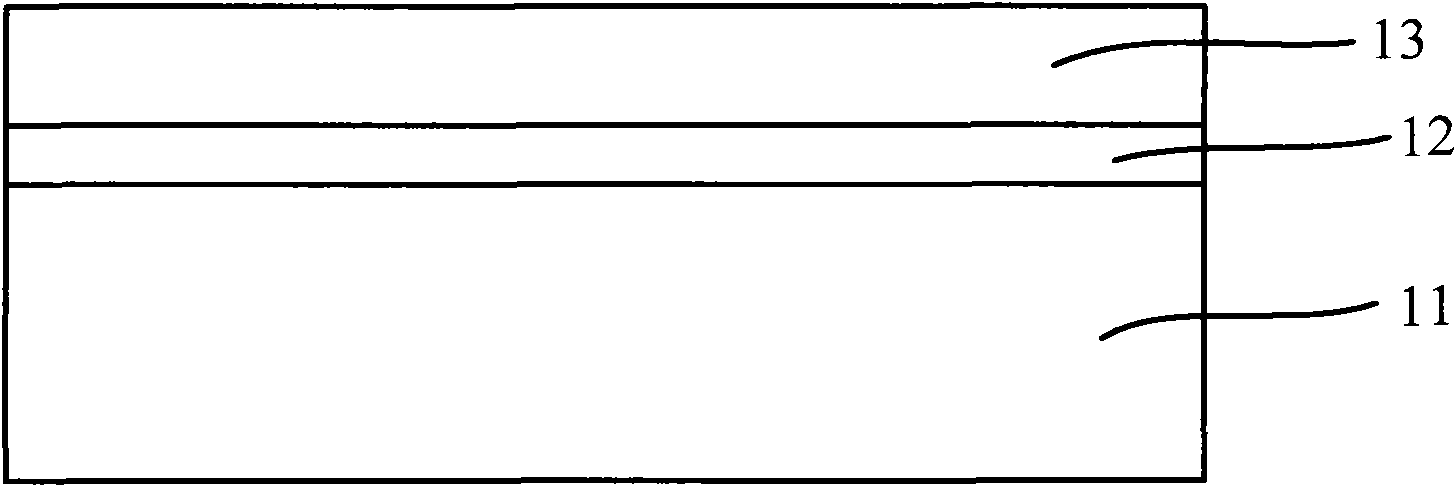

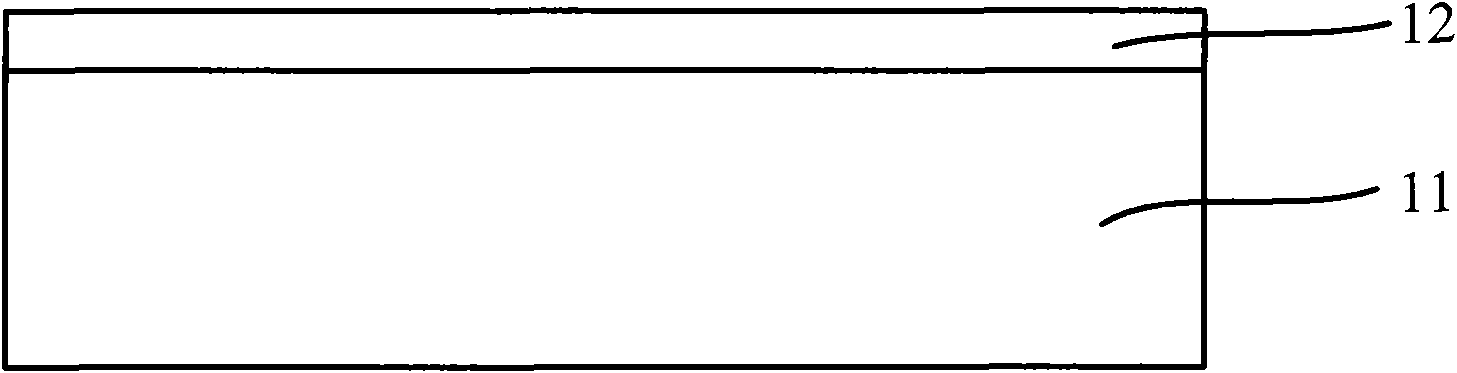

[0018] According to the analysis of the inventors, it is found that if the silicon substrate is defective, a concentrated current (or high current) will be formed in the region corresponding to the defect position between the polysilicon layer and the silicon substrate after the failure test, and the silicon dioxide layer will be broken down. When polysilicon etchant is used to remove the polysilicon layer, the polysilicon etchant will erode the silicon substrate through the concentrated current area, resulting in pits on the silicon substrate (such as Figure 4 Defect 21a) shown. In this case, if the defect analysis of the exposed silicon substrate is carried out, it is impossible to judge whether it is a defect of the substrate itself, a defect caused to the substrate during the process, or a defect caused by the substrate when the polysilicon layer is stripped. defects caused by the bottom. Therefore, peeling off the polysilicon layer and the silicon dioxide layer on the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More