Patents

Literature

53 results about "Buffered oxide etch" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Buffered oxide etch (BOE), also known as buffered HF or BHF, is a wet etchant used in microfabrication. Its primary use is in etching thin films of silicon dioxide (SiO₂) or silicon nitride (Si₃N₄). It is a mixture of a buffering agent, such as ammonium fluoride (NH₄F), and hydrofluoric acid (HF). Concentrated HF (typically 49% HF in water) etches silicon dioxide too quickly for good process control and also peels photoresist used in lithographic patterning. Buffered oxide etch is commonly used for more controllable etching.

Method of selectively depositing a thin film material at a semiconductor interface

InactiveUS20070108404A1Detergent mixture composition preparationSemiconductor/solid-state device manufacturingDevice formMetal silicide

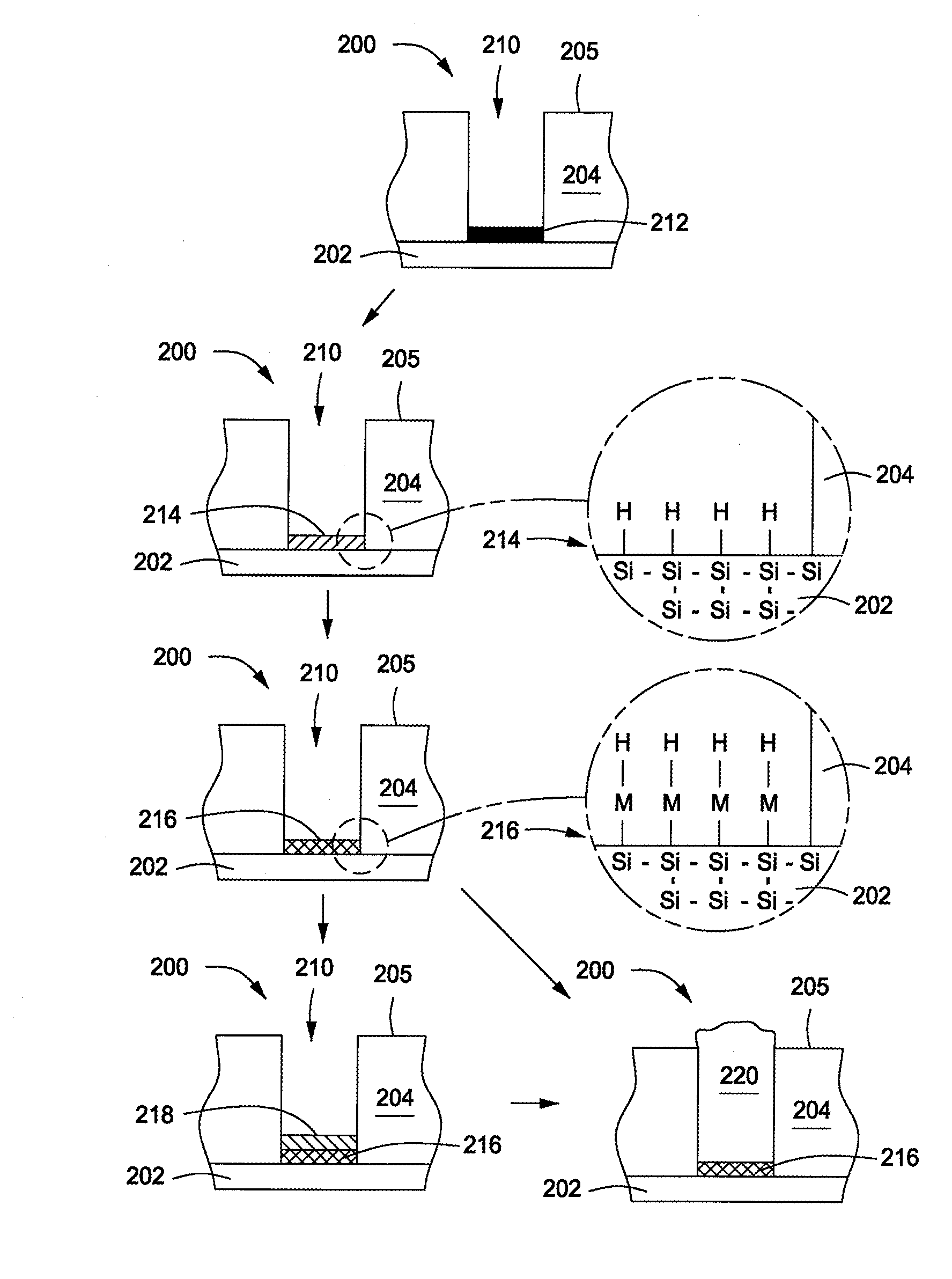

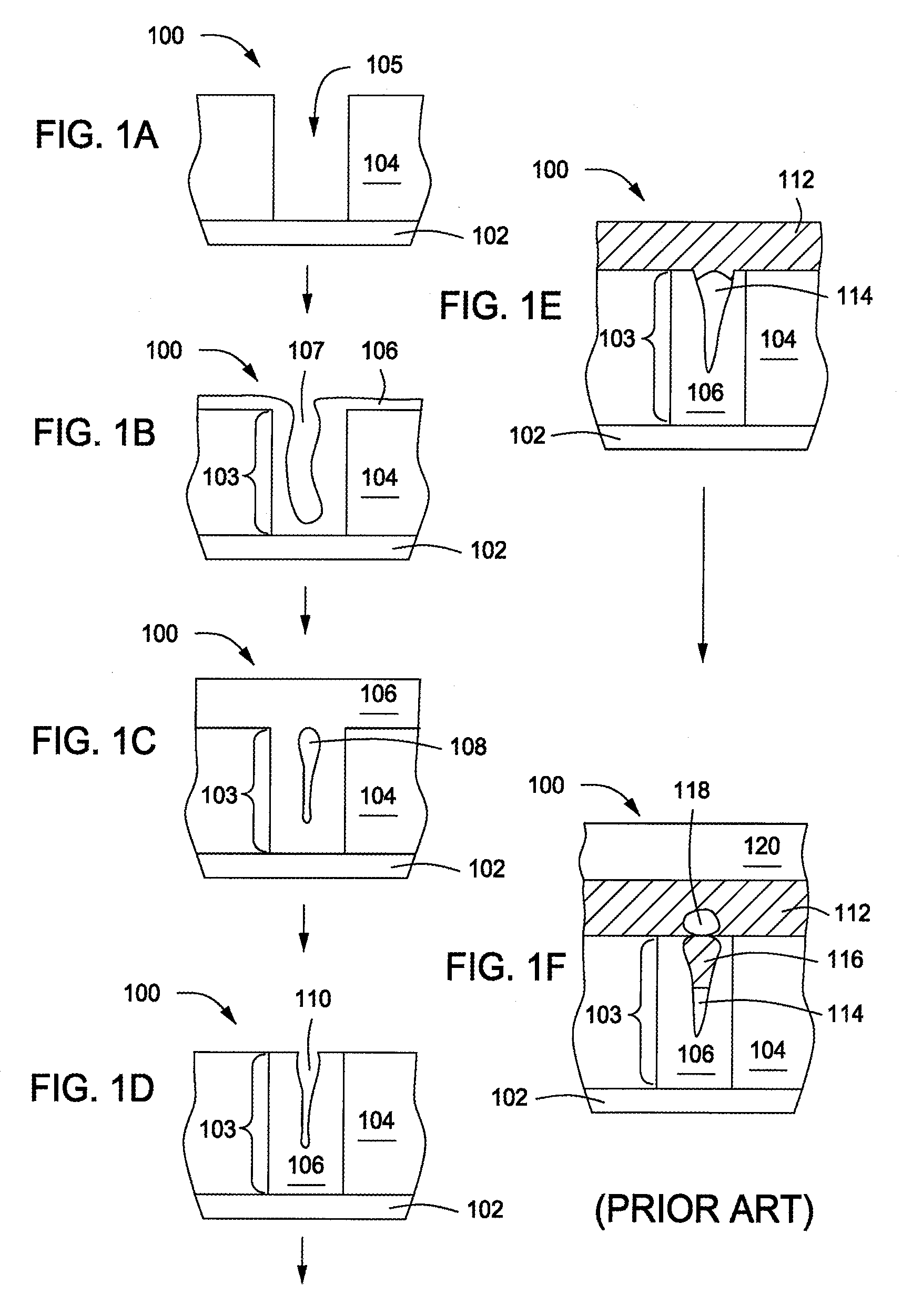

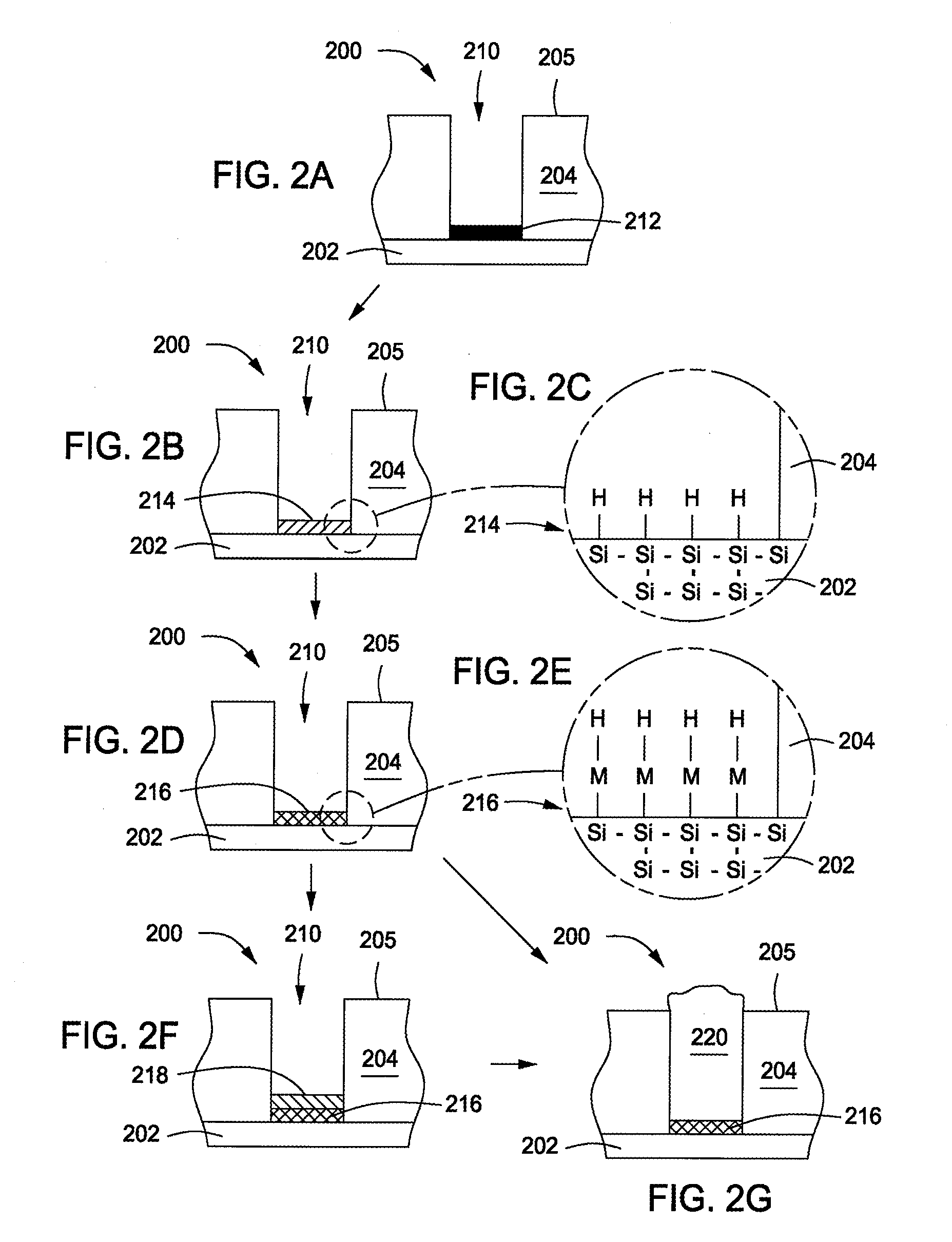

Embodiments of the invention provide processes to form a high quality contact level connection to devices formed on a substrate. In one embodiment, a method for depositing a material on a substrate is provided which includes exposing the substrate to a buffered oxide etch solution to form a silicon hydride layer during a pretreatment process, depositing a metal silicide layer on the substrate, and depositing a first metal layer (e.g., tungsten) on the metal silicide layer. The buffered oxide etch solution may contain hydrogen fluoride and an alkanolamine compound, such as ethanolamine diethanolamine, or triethanolamine. The metal silicide layer may contain cobalt, nickel, or tungsten and may be deposited by an electroless deposition process. In one example, the substrate is exposed to an electroless deposition solution containing a solvent and a complexed metal compound.

Owner:APPLIED MATERIALS INC

Conditioner and conditioning disk for a CMP pad, and method of fabricating, reworking, and cleaning conditioning disk

InactiveUS20020127962A1Effective conditioningProlong lifeGrinding drivesBelt grinding machinesSize differenceCleaning methods

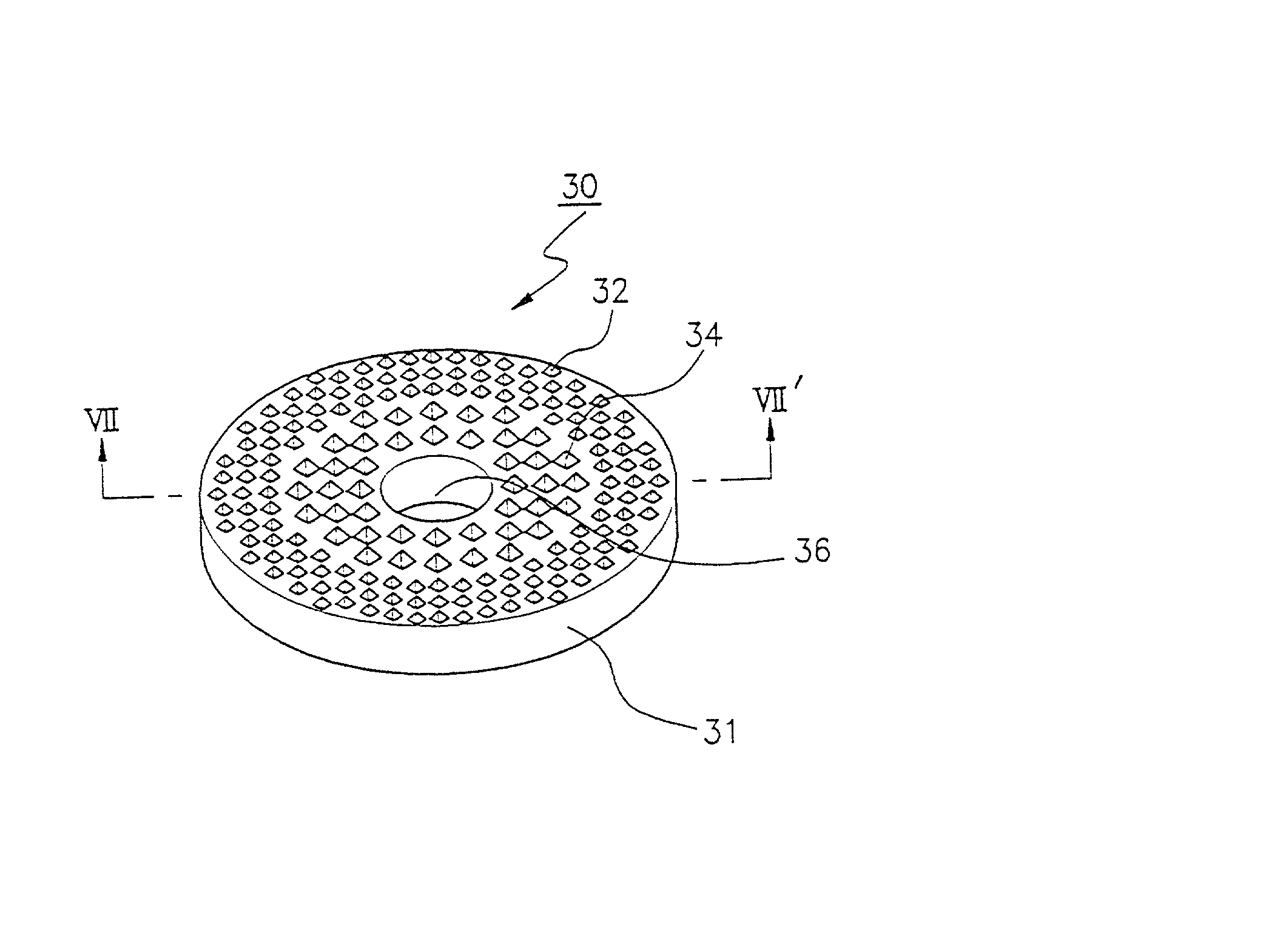

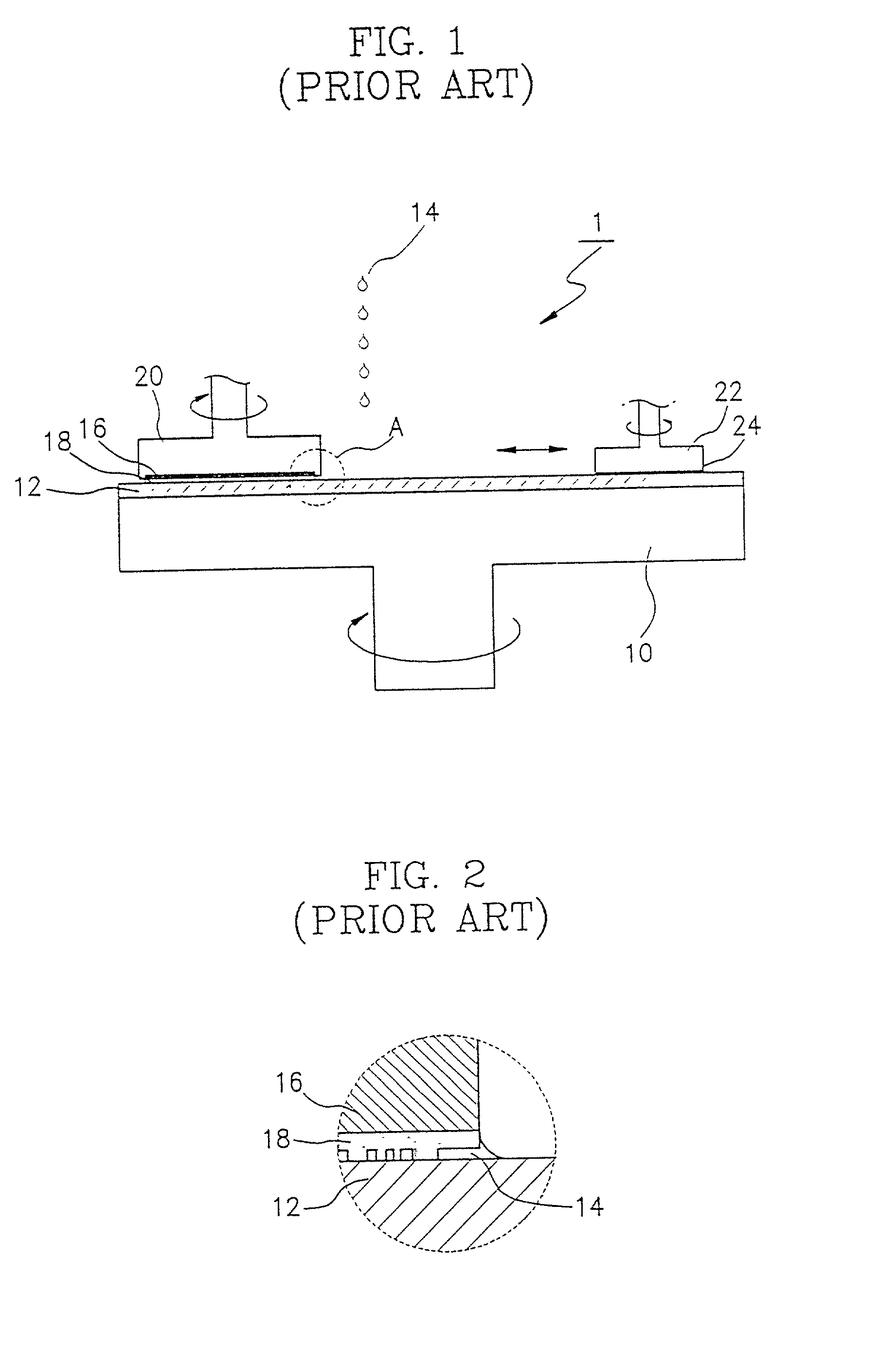

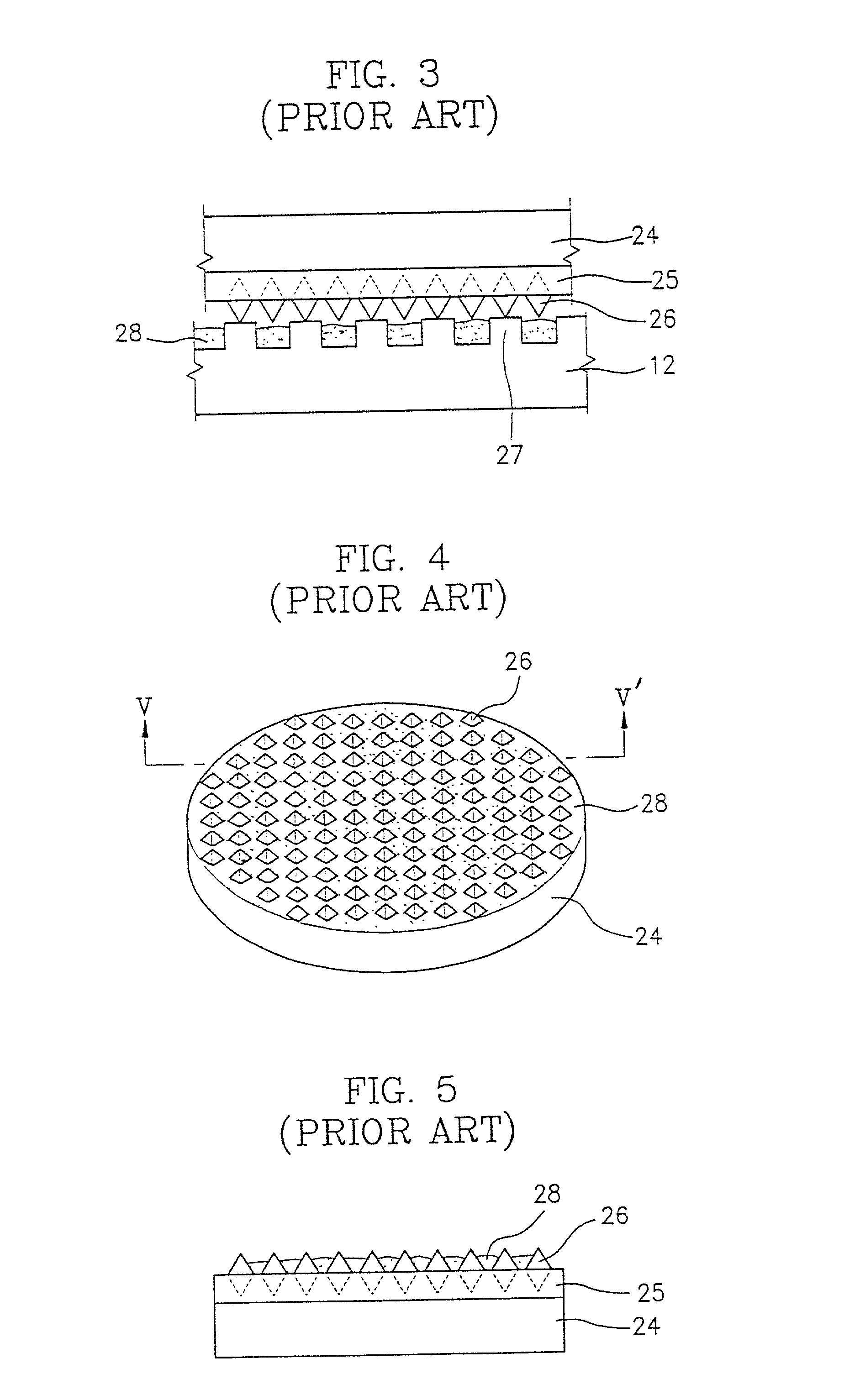

A conditioning disk and a conditioner for a chemical mechanical polishing (CMP) pad, and a method of fabricating, reworking, and cleaning the conditioning disk, are utilized to improve conditioning efficiency, and to reduce production expenses. The conditioning disk for a CMP pad is divided into regions defined by a size difference of abrasive grains formed on the body surface in each region of the conditioning disk. The method of fabricating the conditioning disk is performed by forming adhesive films for attaching the abrasive grains onto the body surface multiple times. In addition, a used conditioning disk may be reworked by detaching the abrasive grains from the body, and attaching new abrasive grains. A used conditioning disk can also be cleaned of by-products of the conditioning process by a cleaning method using a HF solution or BOE (buffered oxide etch) solution.

Owner:SAMSUNG ELECTRONICS CO LTD

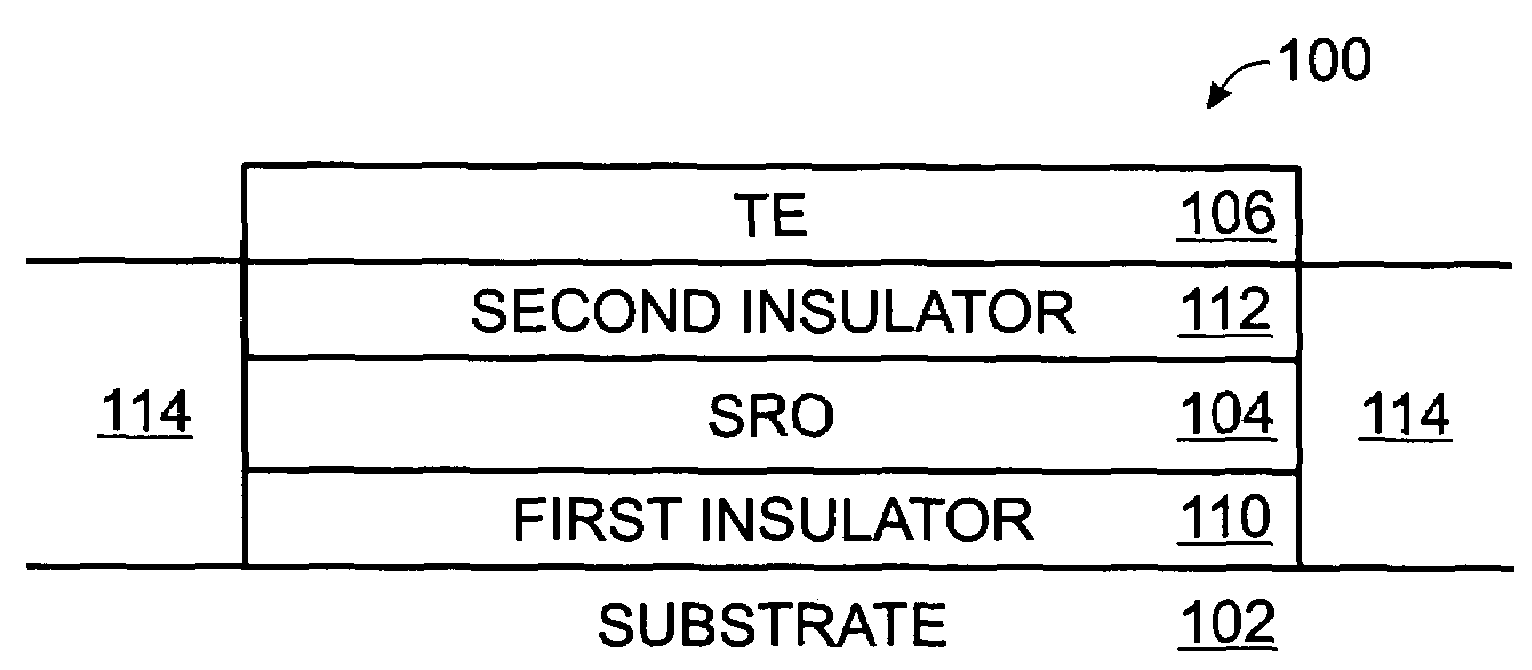

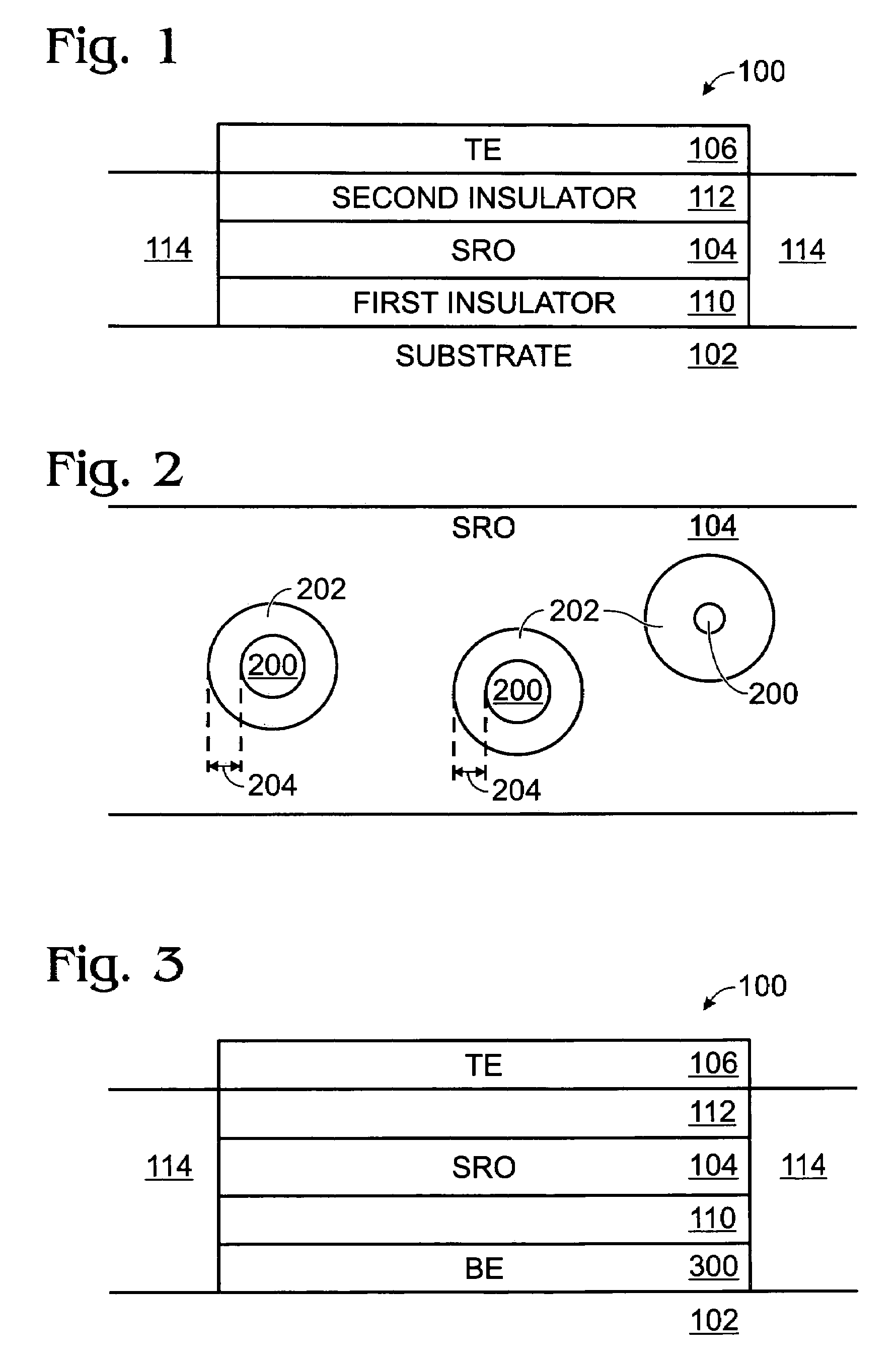

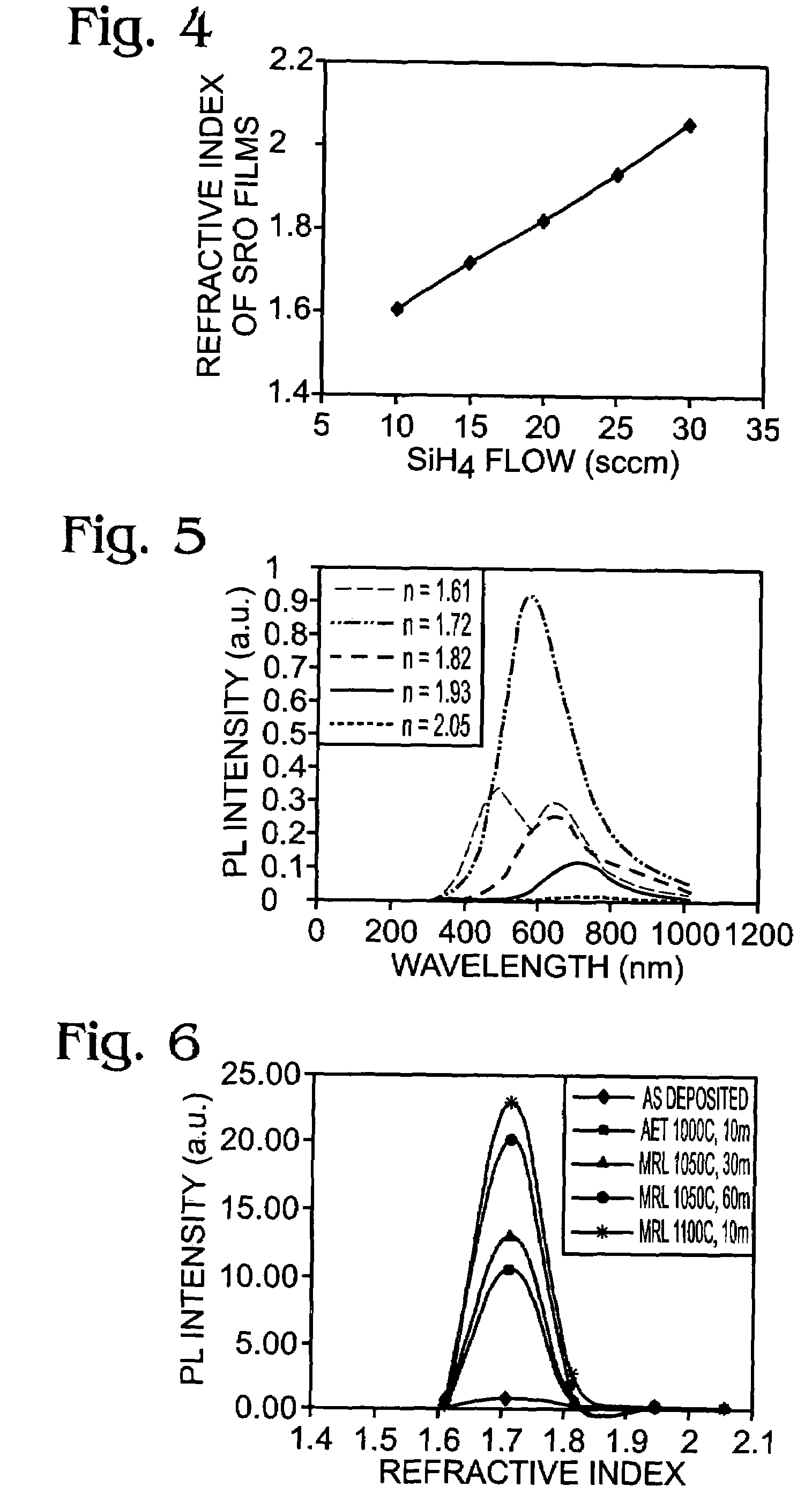

High-luminescence silicon electroluminescence device

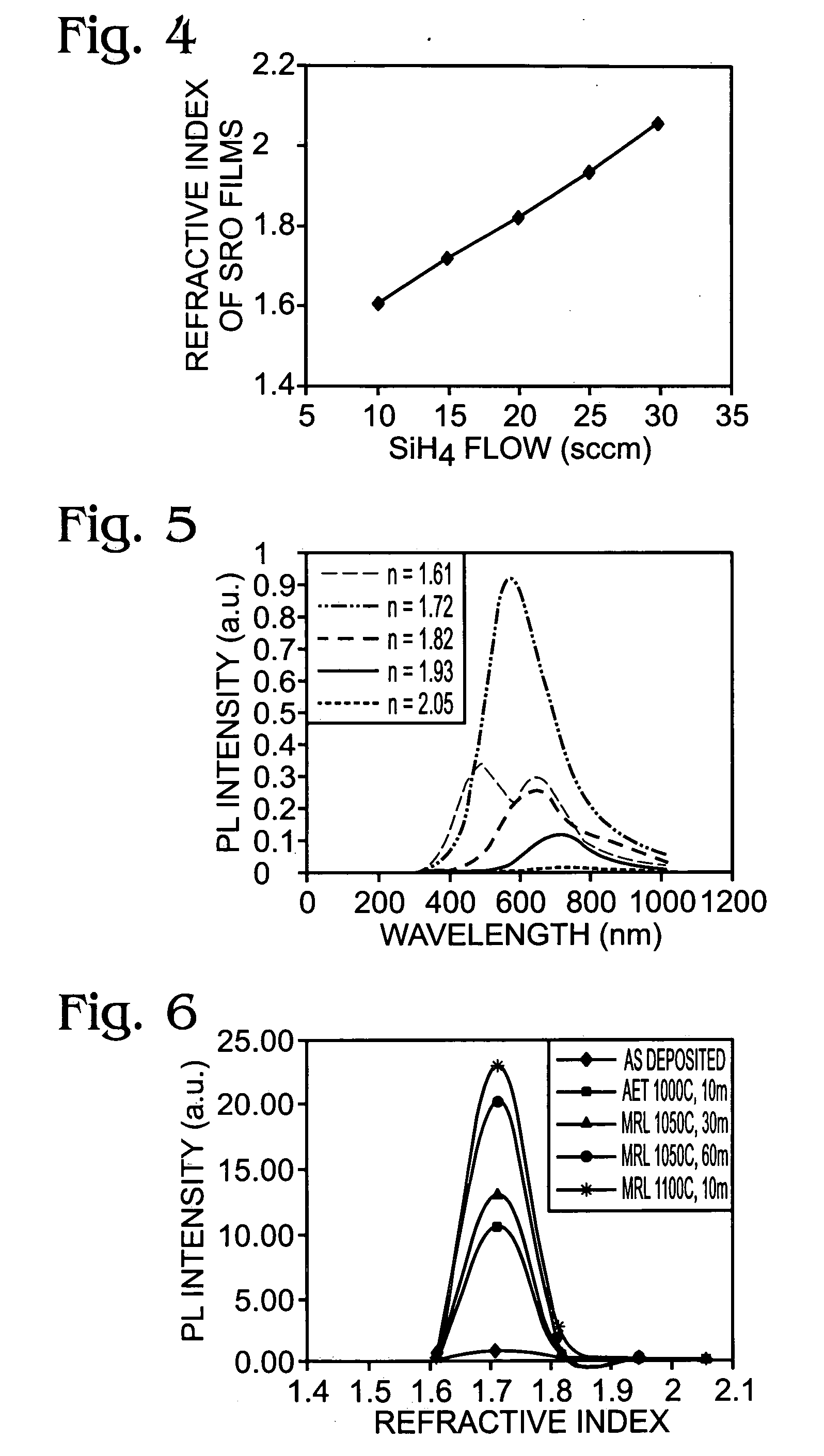

InactiveUS20060189014A1Enhance homogeneous oxidation of nano-SiFacilitated DiffusionFinal product manufactureSemiconductor/solid-state device detailsPorosityRefractive index

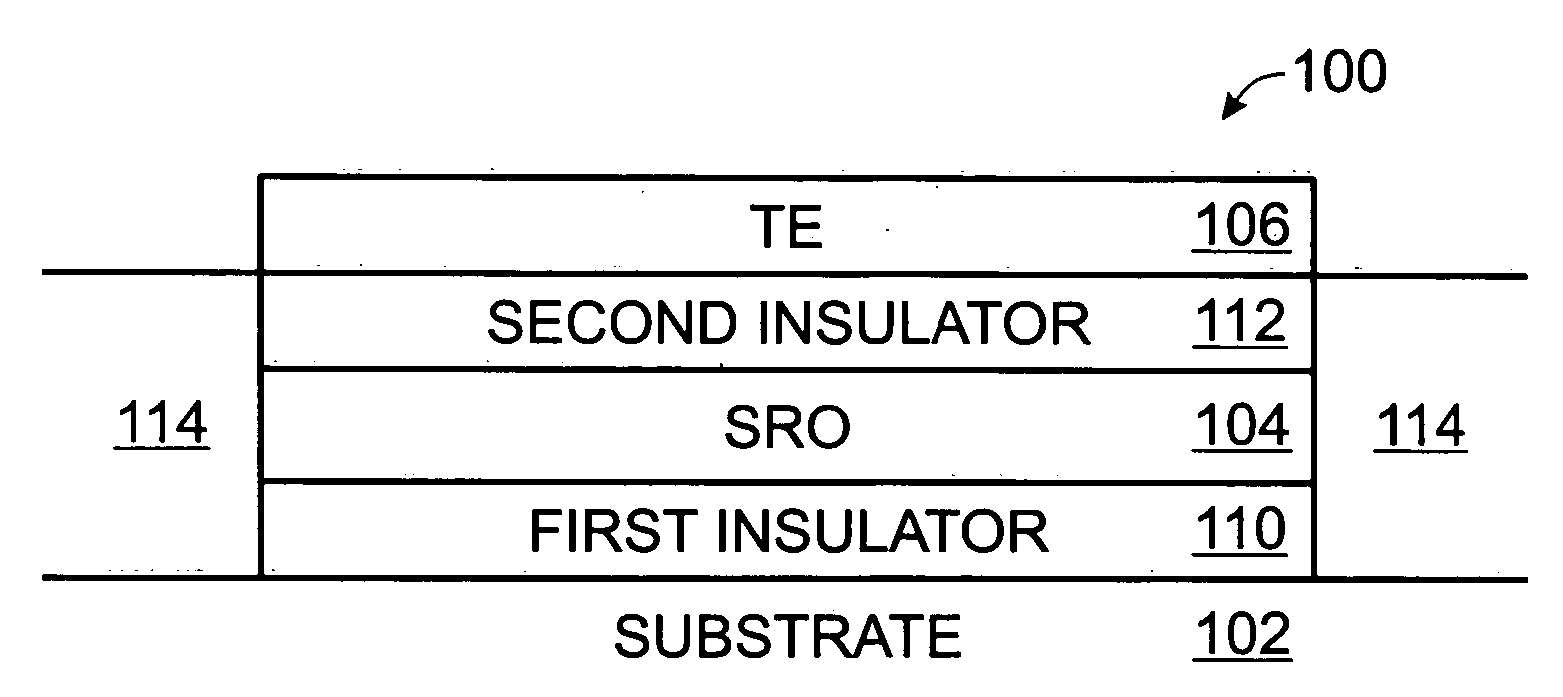

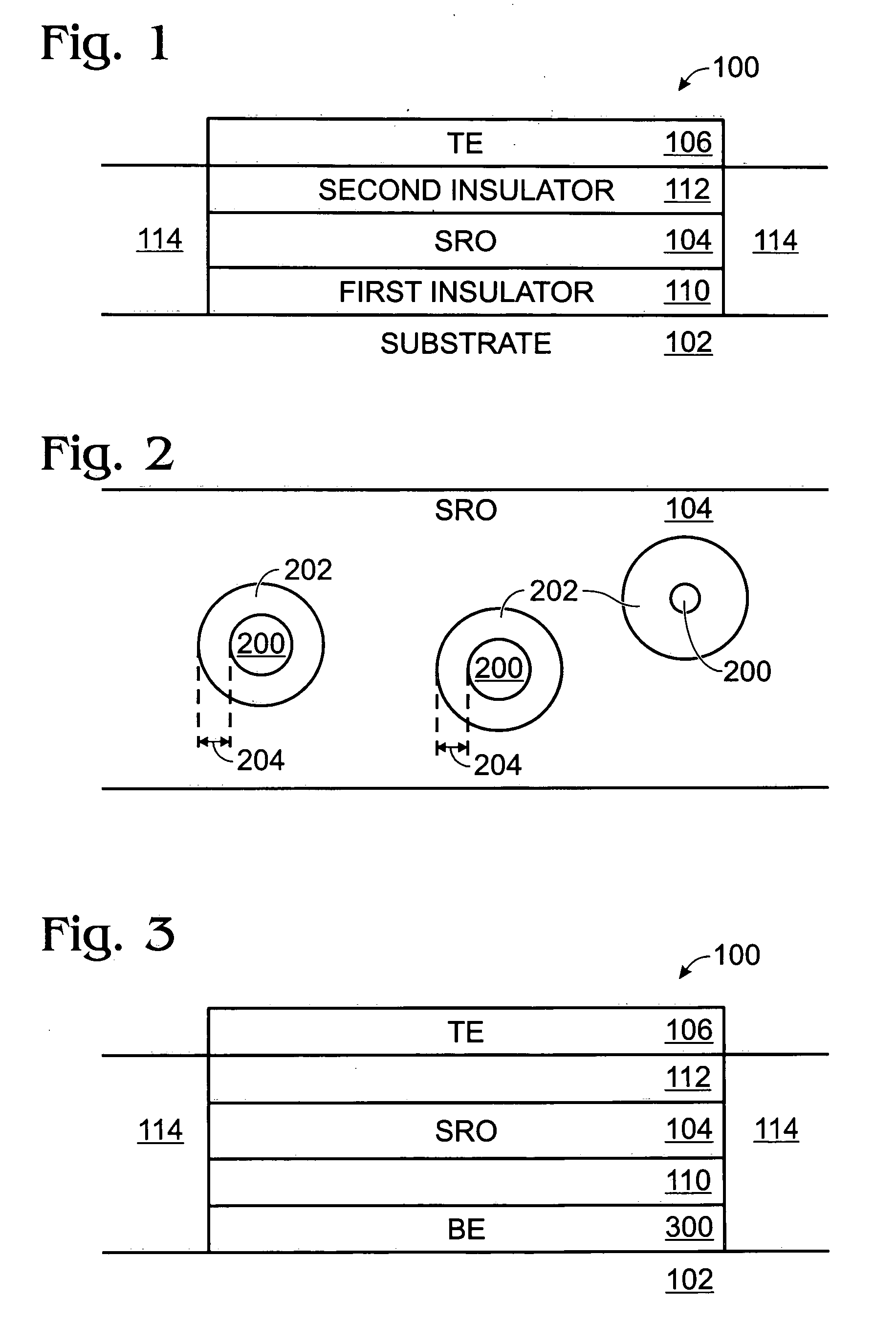

A method for forming a high-luminescence Si electroluminescence (EL) phosphor is provided, with an EL device made from the Si phosphor. The method comprises: depositing a silicon-rich oxide (SRO) film, with Si nanocrystals, having a refractive index in the range of 1.5 to 2.1, and a porosity in the range of 5 to 20%; and, post-annealing the SRO film in an oxygen atmosphere. DC-sputtering or PECVD processes can be used to deposit the SRO film. In one aspect the method further comprises: HF buffered oxide etching (BOE) the SRO film; and, re-oxidizing the SRO film, to form a SiO2 layer around the Si nanocrystals in the SRO film. In one aspect, the SRO film is re-oxidized by annealing in an oxygen atmosphere. In this manner, a layer of SiO2 is formed around the Si nanocrystals having a thickness in the range of 1 to 5 nanometers (nm).

Owner:SHARP KK

Method for exposing semiconductor substrate and invalidation analysis method

ActiveCN101996880ASolve the problem of damaging the silicon substrateGuaranteed accuracySemiconductor/solid-state device manufacturingOptically investigating flaws/contaminationHydrofluoric acidChemical solution

The invention provides a method for exposing a semiconductor substrate and an invalidation analysis method. The method comprises the following steps: providing a semiconductor sample; removing an oxidation layer between the semiconductor substrate and a semiconductor polycrystal layer with chemical solution; and removing the semiconductor polycrystal layer through ultrasonic oscillation and exposing the semiconductor substrate, wherein the semiconductor sample comprises the semiconductor substrate, the oxidation layer and the semiconductor polycrystal layer from bottom to top in sequence; and the chemical solution is buffer oxide etching solution or hydrofluoric acid. The method for exposing the semiconductor substrate and the invalidation analysis method solve the problem that the semiconductor substrate can be damaged by de-layering the semiconductor polycrystal layer and the oxidation layer above the semiconductor substrate by layers in the prior art.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method of forming high-luminescence silicon electroluminescence device

InactiveUS7259055B2Enhance homogeneous oxidation of nano-SiFacilitated DiffusionFinal product manufactureSemiconductor/solid-state device detailsPorosityRefractive index

A method for forming a high-luminescence Si electroluminescence (EL) phosphor is provided, with an EL device made from the Si phosphor. The method comprises: depositing a silicon-rich oxide (SRO) film, with Si nanocrystals, having a refractive index in the range of 1.5 to 2.1, and a porosity in the range of 5 to 20%; and, post-annealing the SRO film in an oxygen atmosphere. DC-sputtering or PECVD processes can be used to deposit the SRO film. In one aspect the method further comprises: HF buffered oxide etching (BOE) the SRO film; and, re-oxidizing the SRO film, to form a SiO2 layer around the Si nanocrystals in the SRO film. In one aspect, the SRO film is re-oxidized by annealing in an oxygen atmosphere. In this manner, a layer of SiO2 is formed around the Si nanocrystals having a thickness in the range of 1 to 5 nanometers (nm).

Owner:SHARP KK

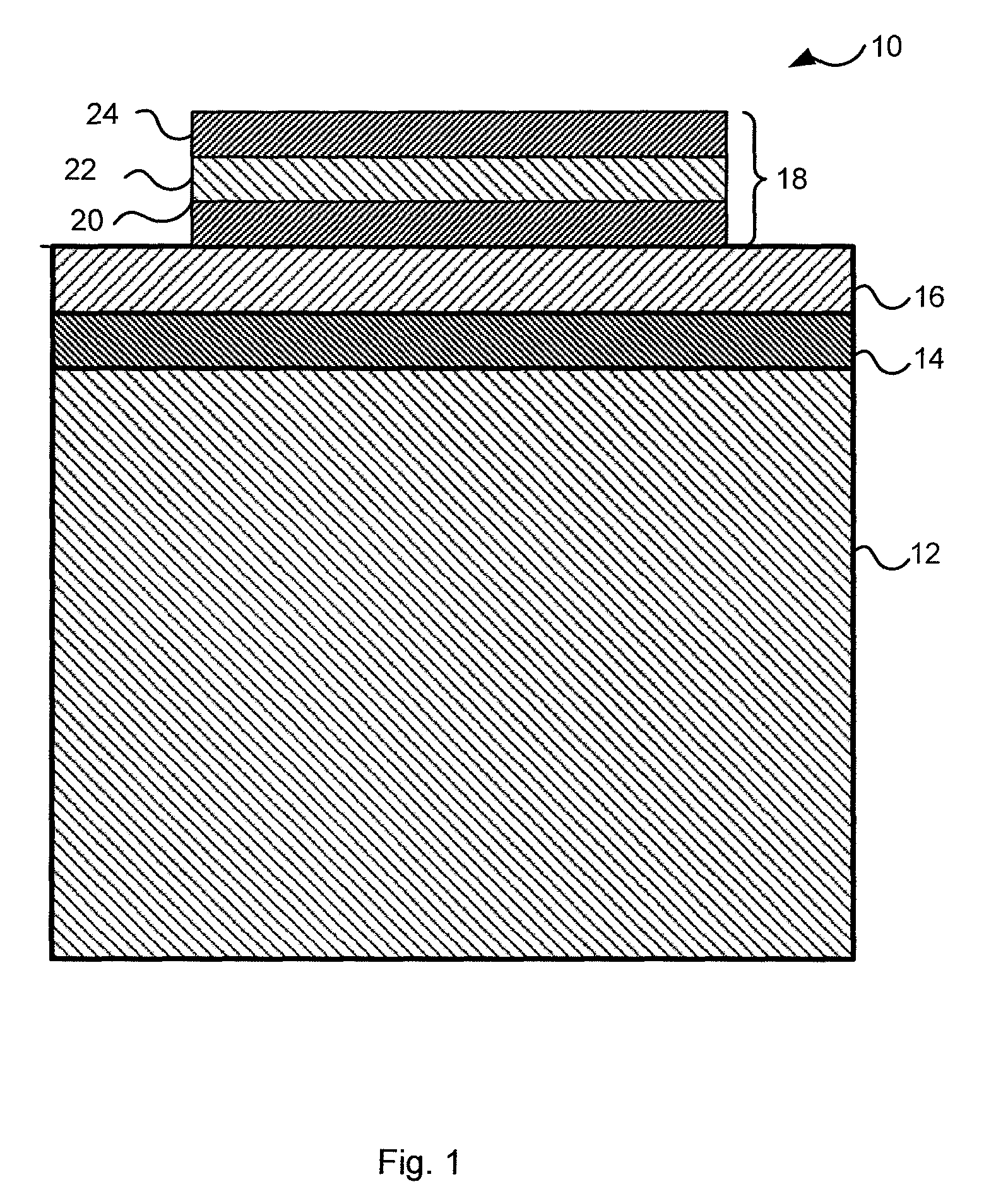

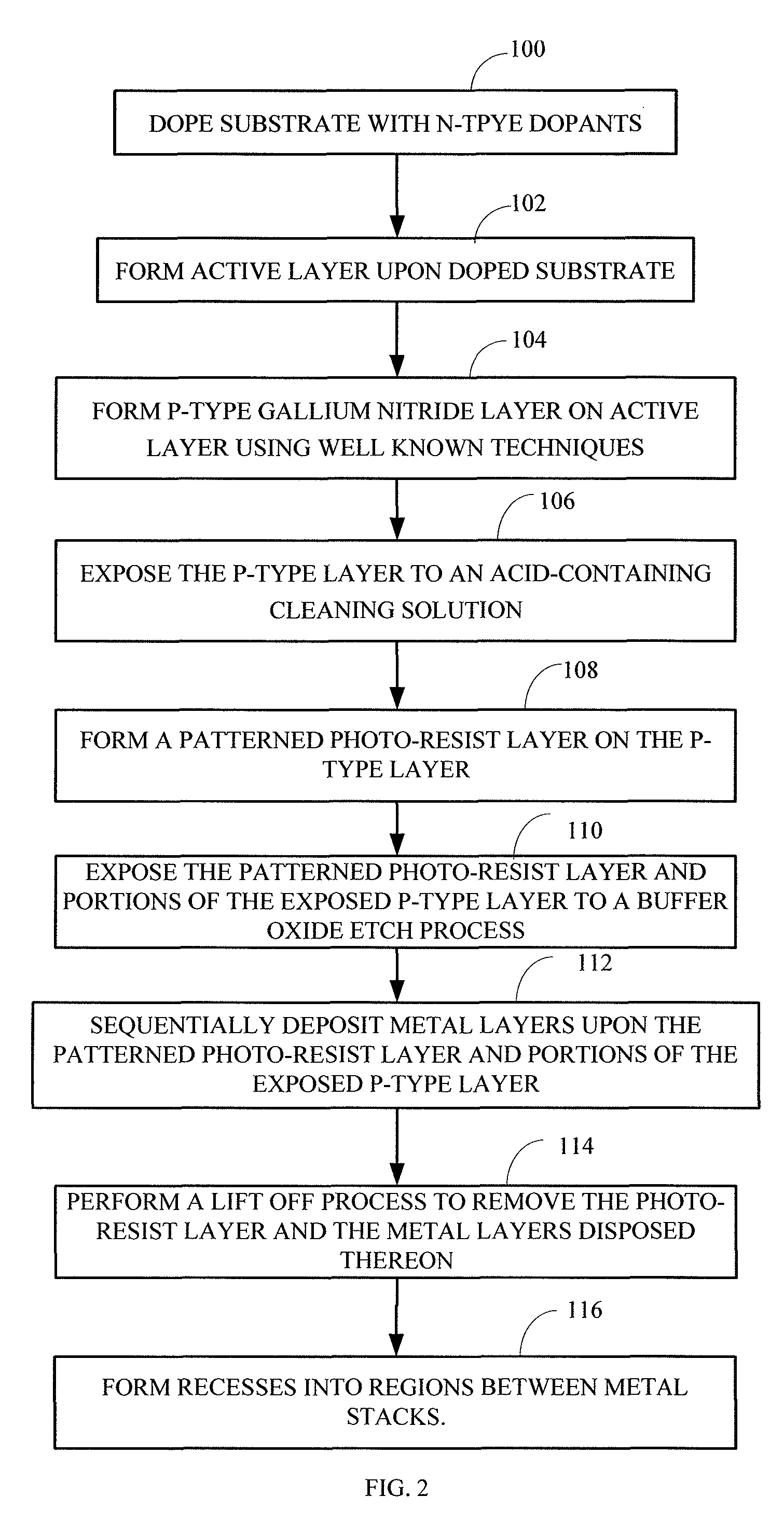

Techniques of forming Ohmic contacts on GaN light emitting diodes

ActiveUS8148180B2Semiconductor/solid-state device manufacturingSemiconductor devicesPlatinumQuantum well

A method of forming ohmic contacts on a light emitting diode that features a surface treatment of a substrate includes exposing a surface of a p-type gallium nitride layer to an acid-containing solution and a buffered oxide etch process. A quantum well is formed in a gallium nitride substrate and a layer of p-type gallium nitride is deposited over the quantum well. The surface of the p-type gallium nitride is exposed to an acid-containing solution and then a buffered oxide etch process is performed to provide an etched surface. A metal stack including a layer of silver disposed between layers of platinum is then deposited.

Owner:KORRUS INC

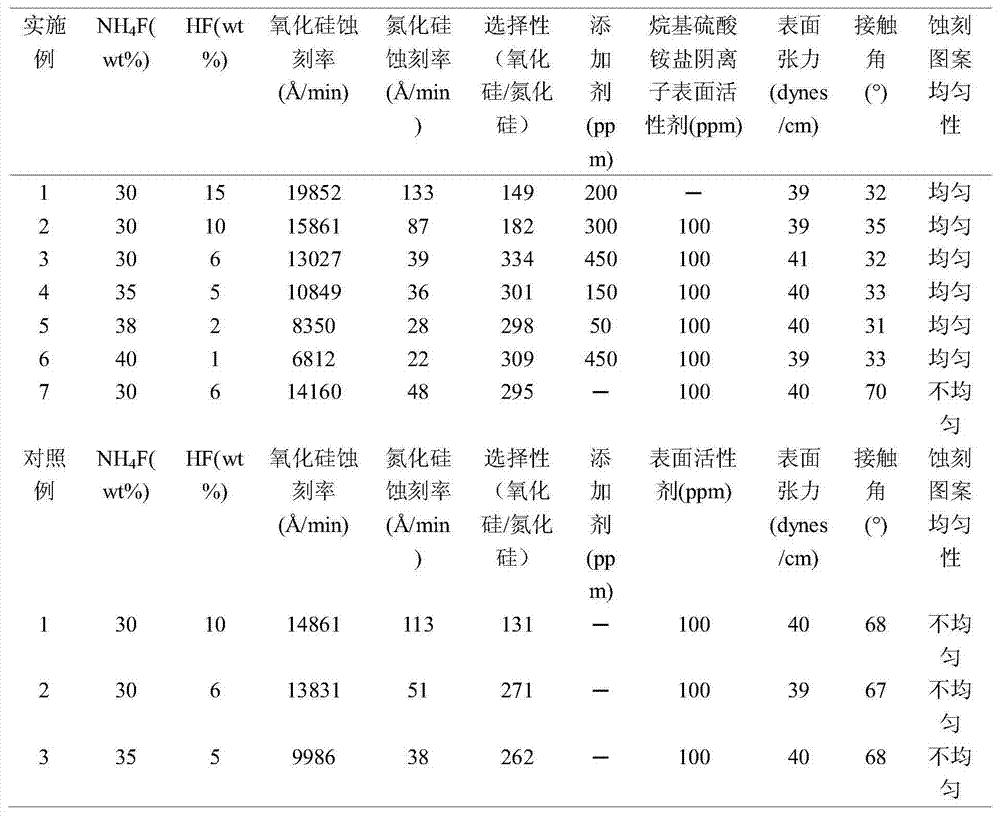

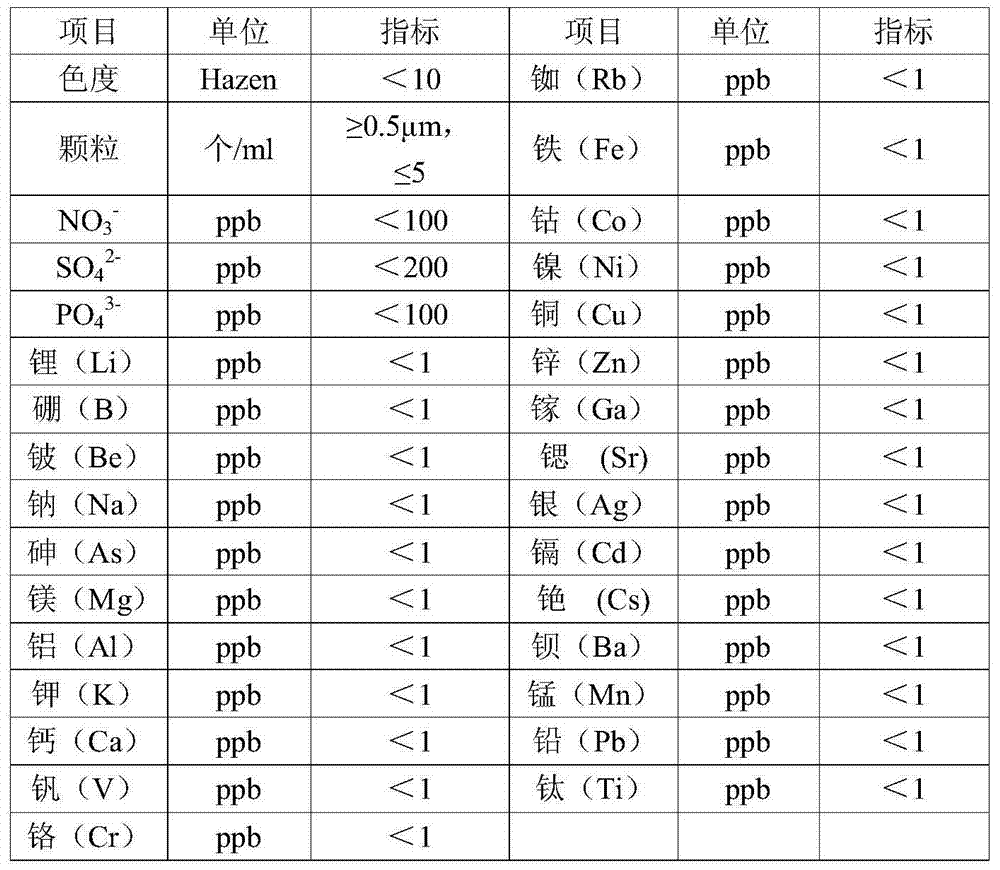

Method for preparing BOE (Buffer Oxide Etch) etching liquid

InactiveCN103756680ALow impurity contentImprove etch selectivitySurface treatment compositionsSilicon dioxideImpurity

The invention discloses a method for preparing a BOE (Buffer Oxide Etch) etching liquid. The method comprises the following steps: (1) sequentially adding 49wt% hydrofluoric acid (HF), 3-wt% ammonia water and super-pure water into a reactor, and stirring to react for 6-12 hours at the room temperature, so as to obtain a mixture of hydrofluoric acid (HF) and ammonium fluoride (NH4F); and (2) sequentially adding additives and alkyl ammonium sulfate anionic surfactants into the obtained mixture, stirring and mixing for 6-18 hours at the room temperature so as to obtain the transparent BOE etching liquid after uniform mixing. The BOE etching liquid prepared by using the method is high in etching selectivity, and the contact angle of the BOE etching liquid to a silicon wafer is remarkably reduced. In addition, the preparation method is simple to operate, and the etching liquid is low in impurity content.

Owner:ZHEJIANG KAISN FLUOROCHEM

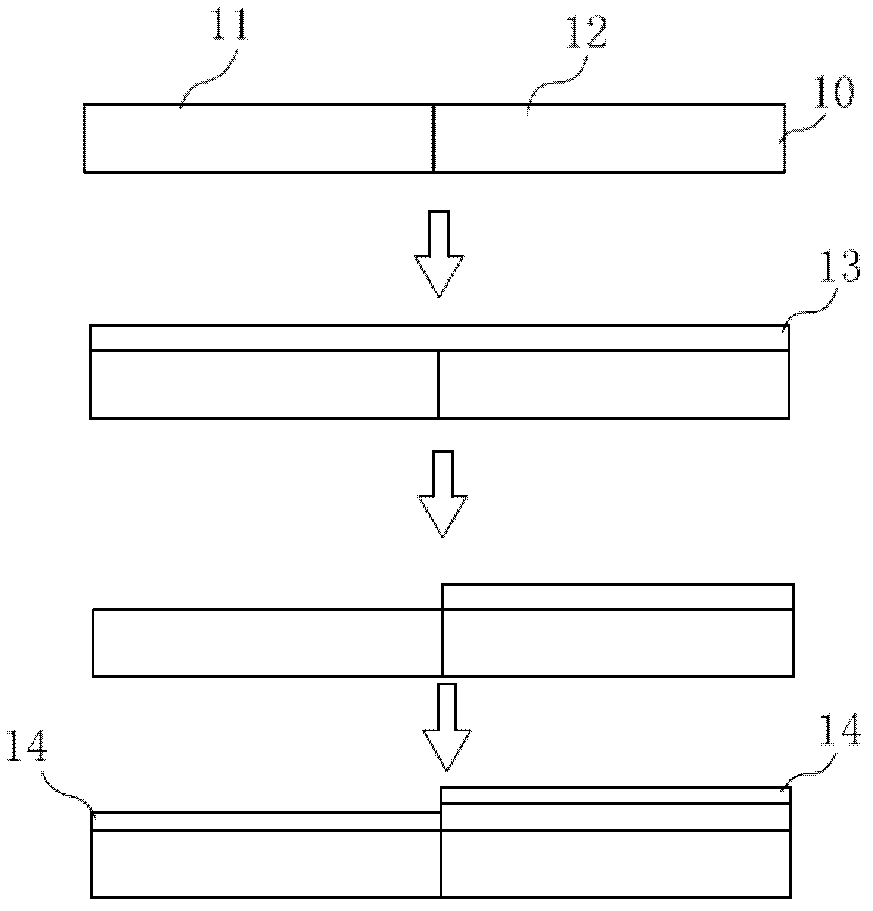

Method of fabricating array substrate

ActiveUS20110124162A1Improve propertiesLow production costSolid-state devicesSemiconductor/solid-state device manufacturingAmorphous siliconOptoelectronics

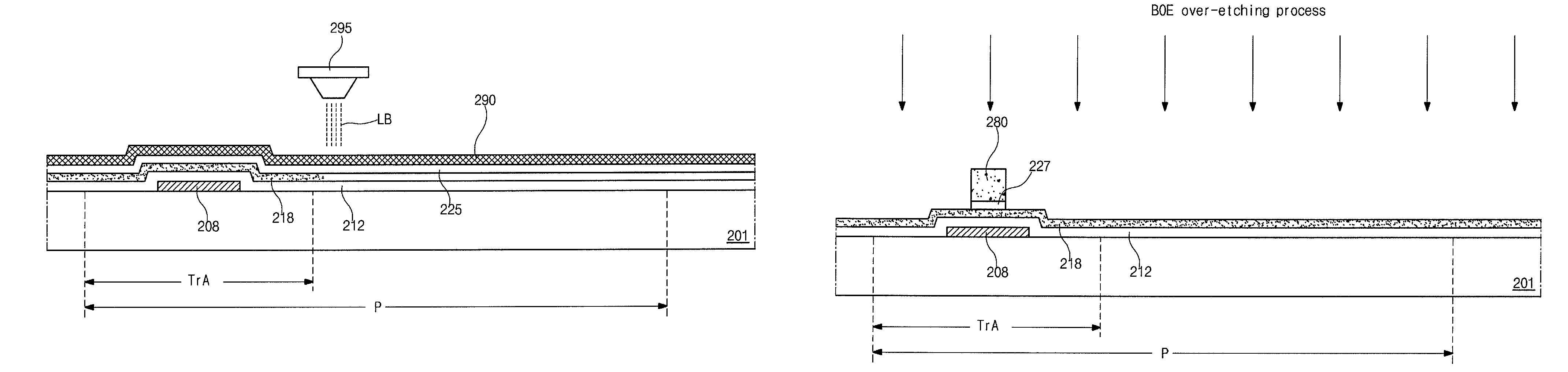

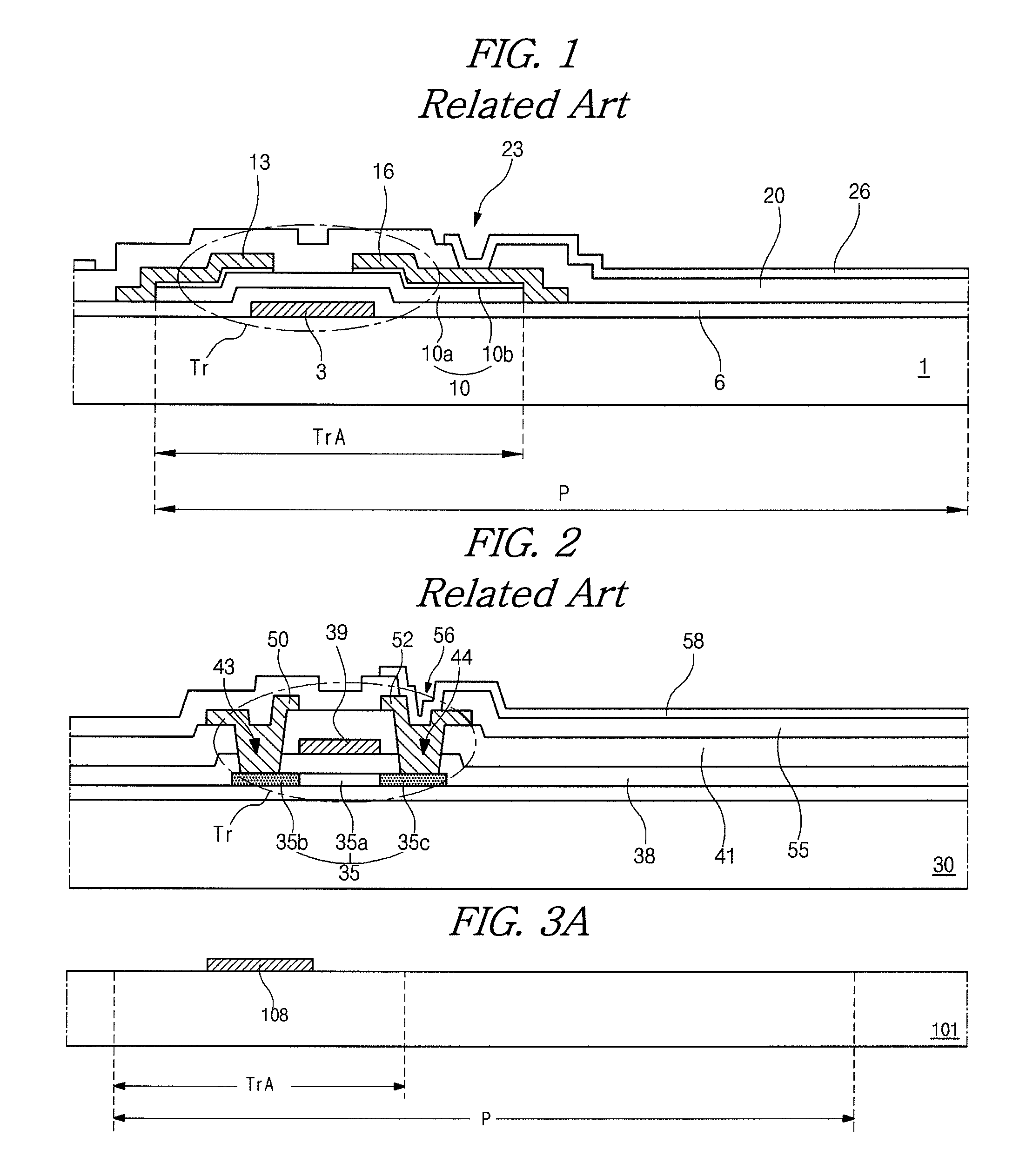

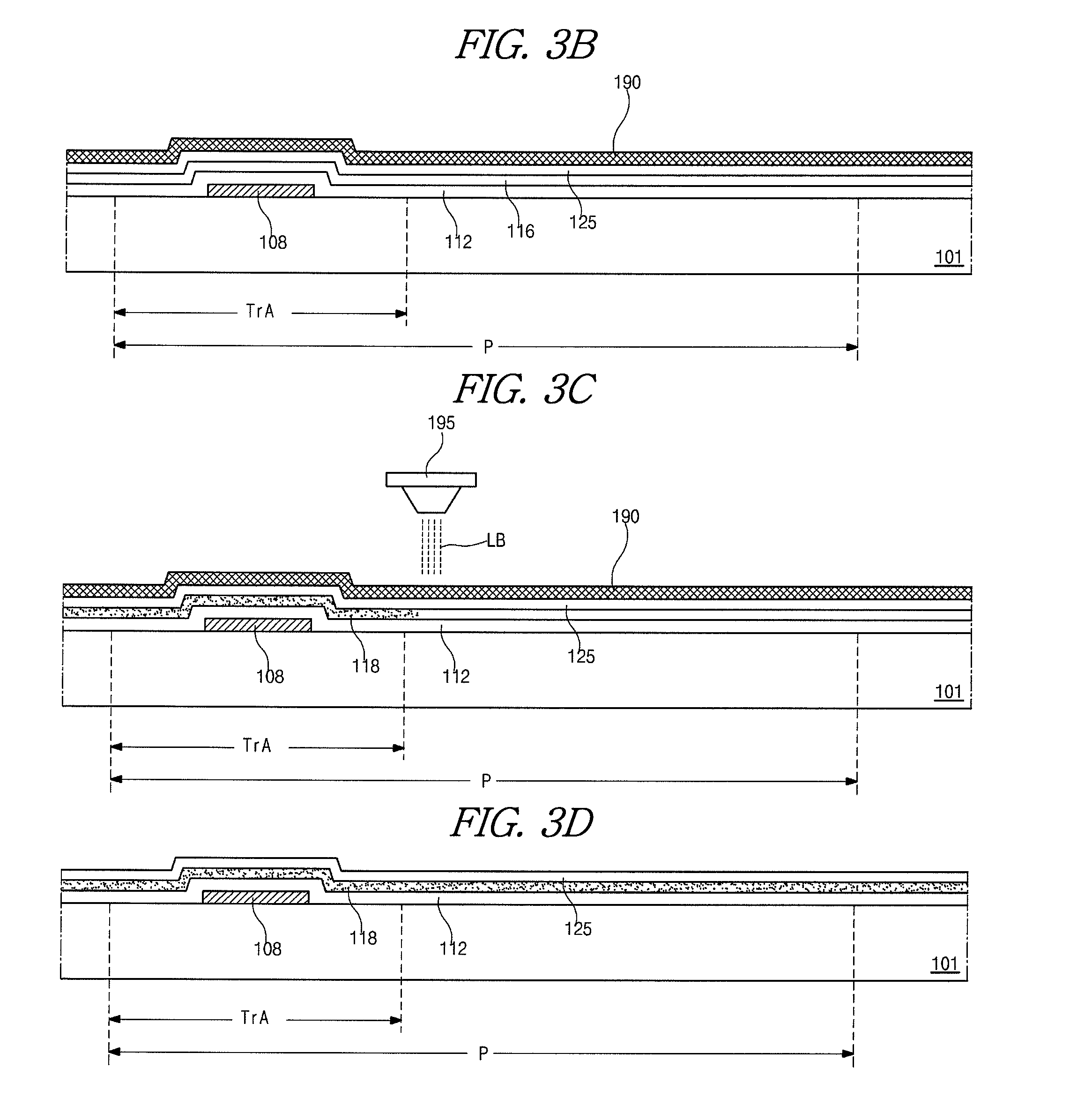

A method of fabricating an array substrate includes forming a gate line and a gate electrode; forming a gate insulating layer, an intrinsic amorphous silicon layer, an inorganic material insulating layer and a heat transfer layer on the gate line and the gate electrode; irradiating a laser beam onto the heat transfer layer to crystallize the intrinsic amorphous silicon layer into a polycrystalline silicon layer; removing the heat transfer layer; patterning the inorganic insulating material layer using a buffered oxide etchant to form an etch-stopper corresponding to the gate electrode forming an impurity-doped amorphous silicon layer and a metal layer on the etch-stopper and the polycrystalline silicon layer; patterning the metal layer to form a data line, a source electrode and a drain electrode and forming a pixel electrode on the passivation layer.

Owner:LG DISPLAY CO LTD

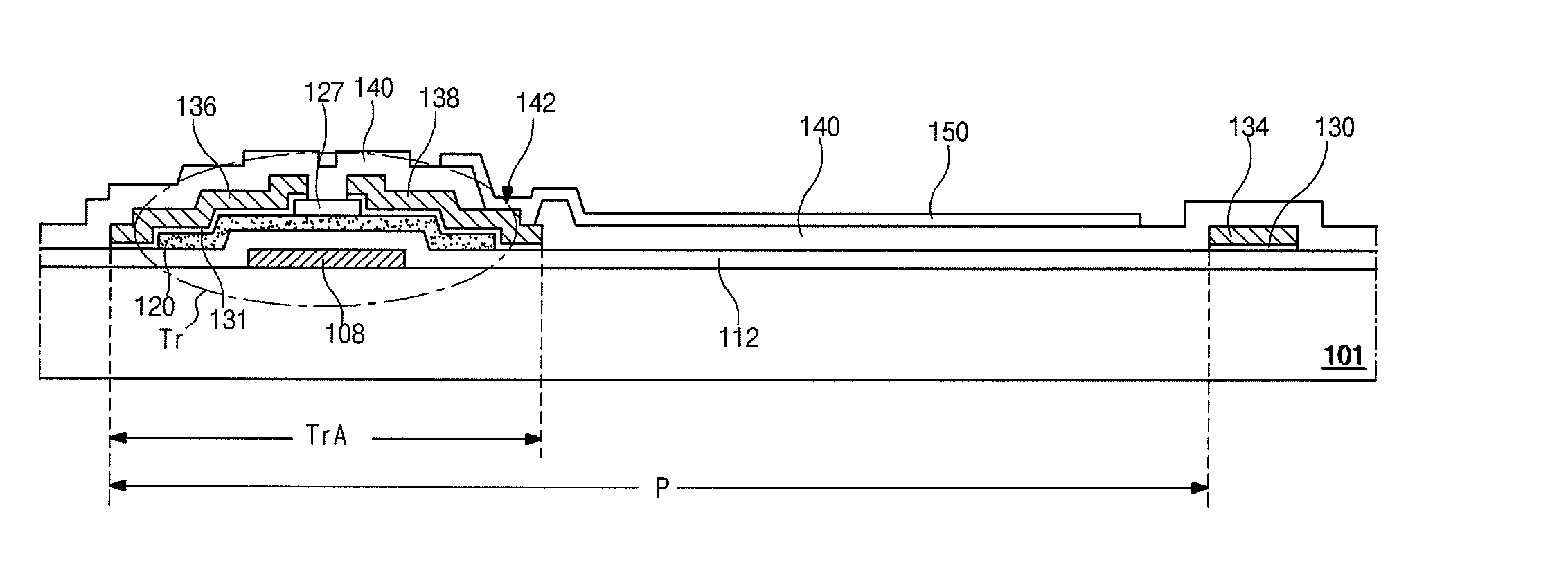

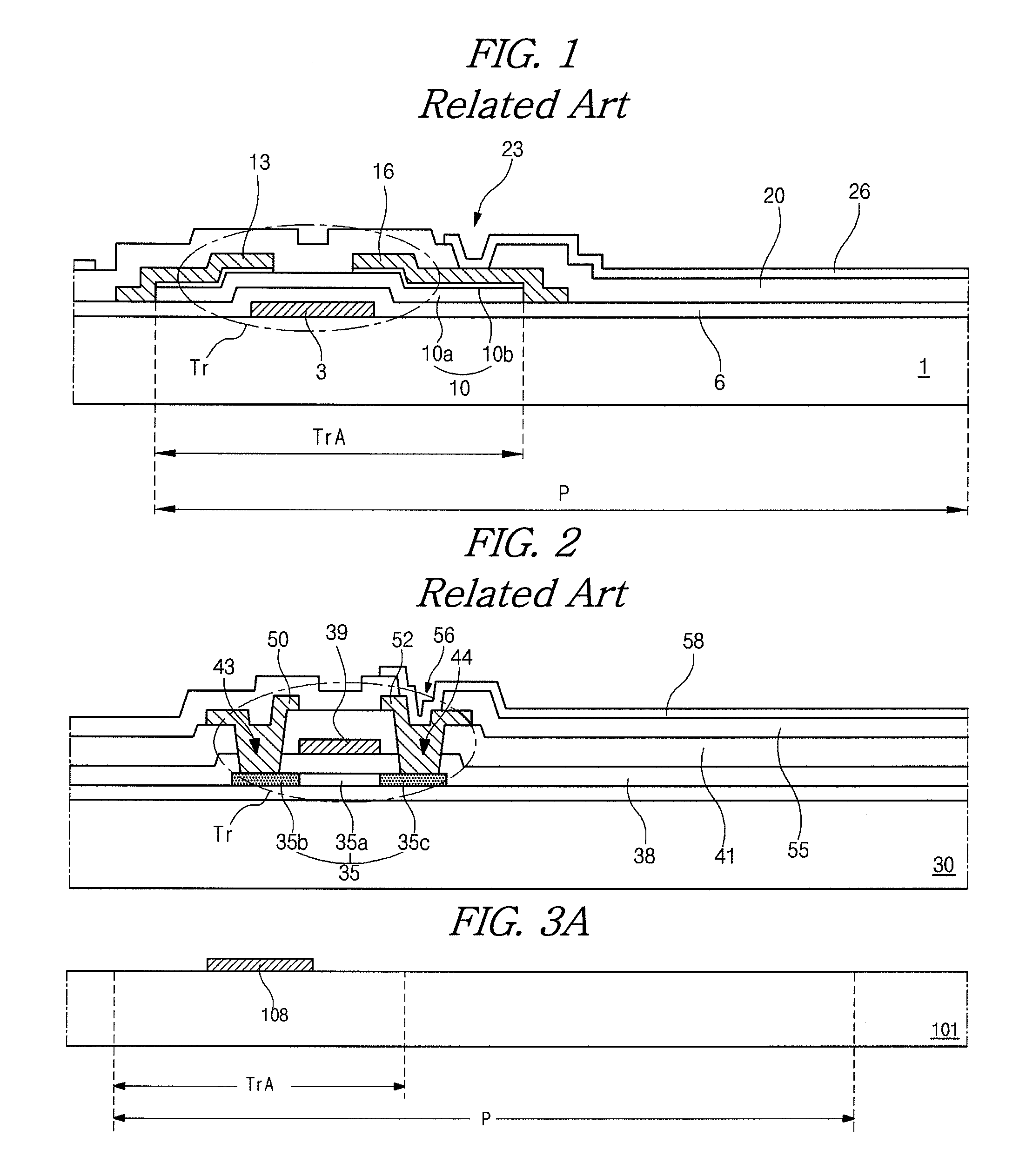

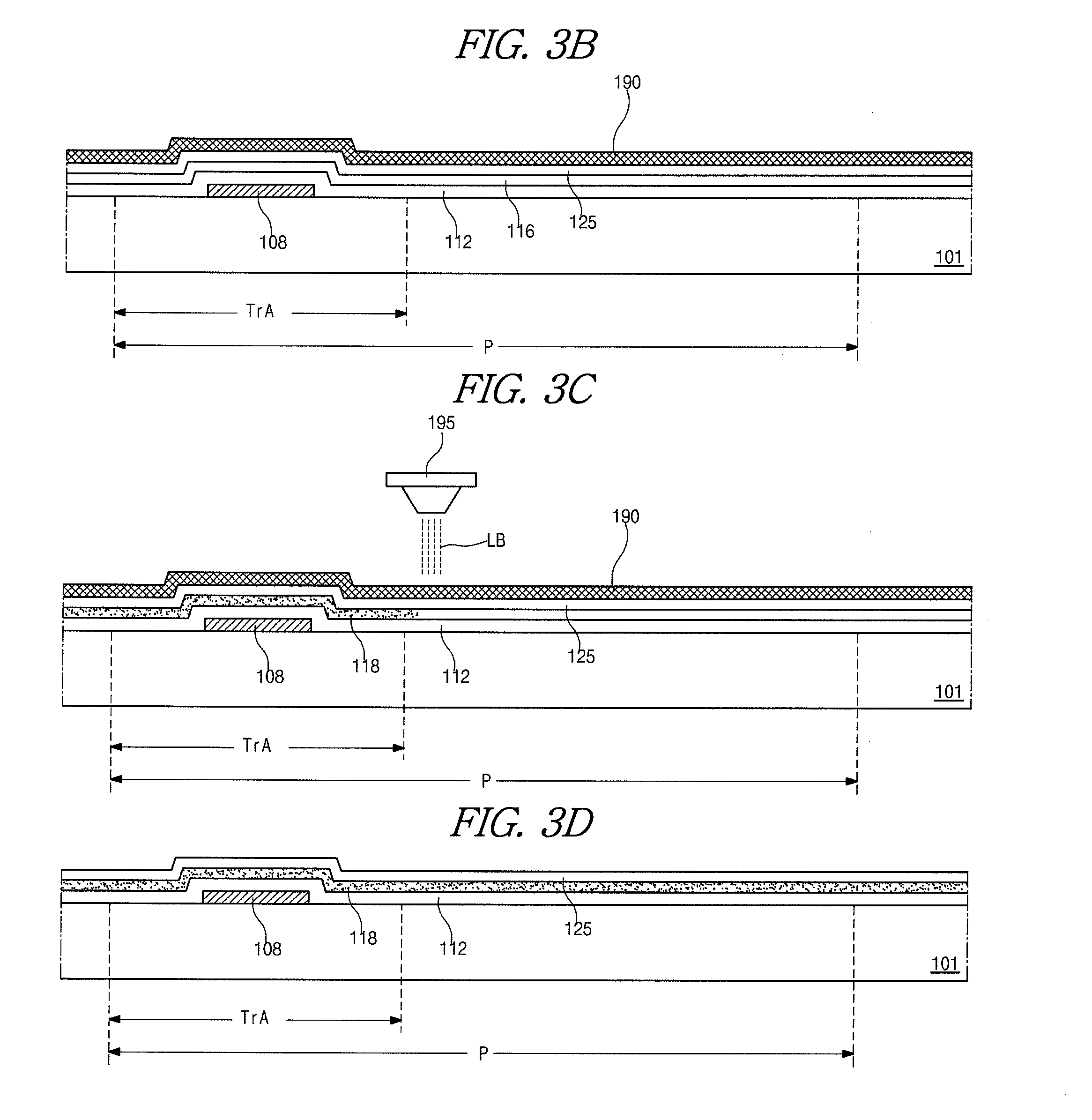

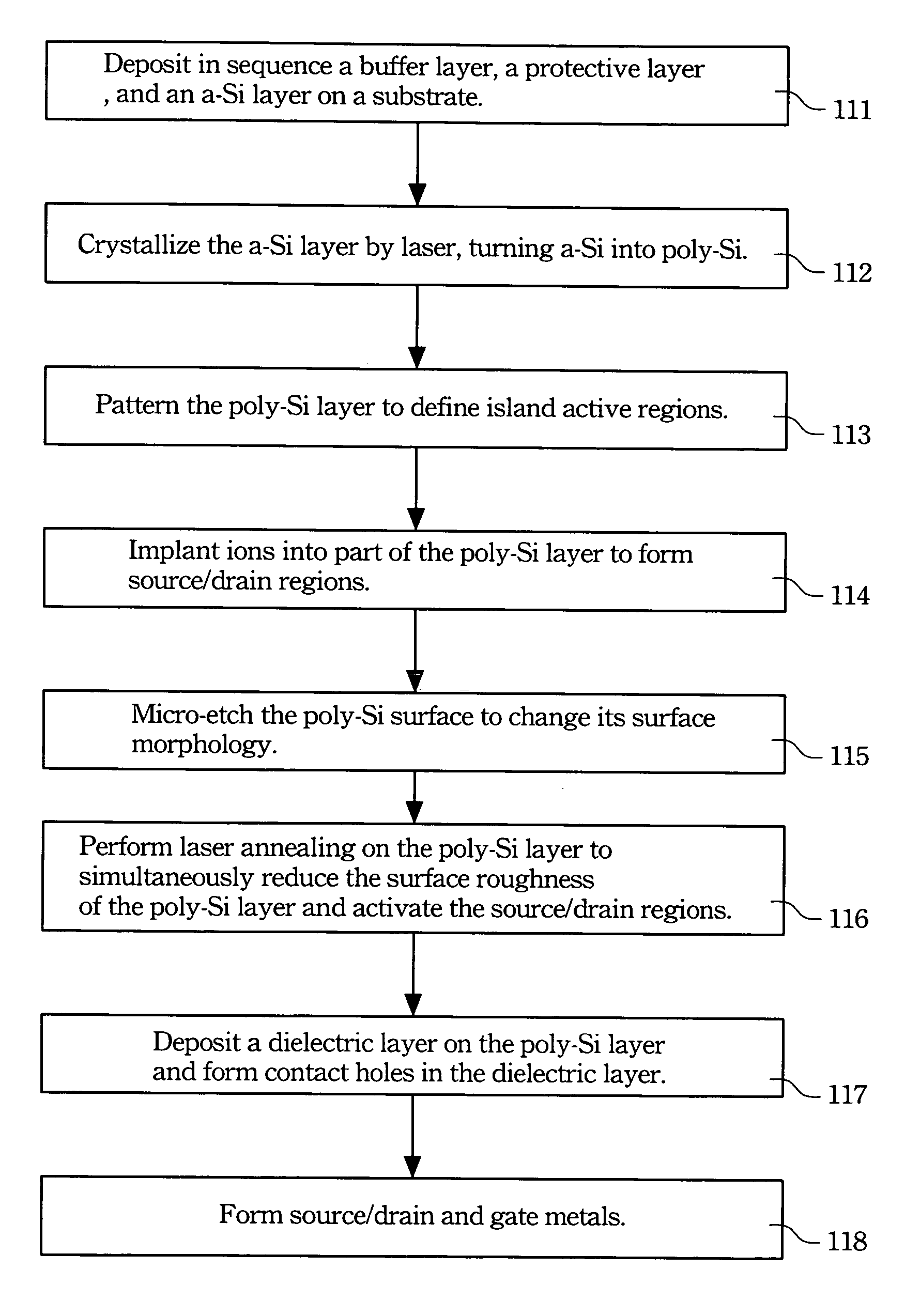

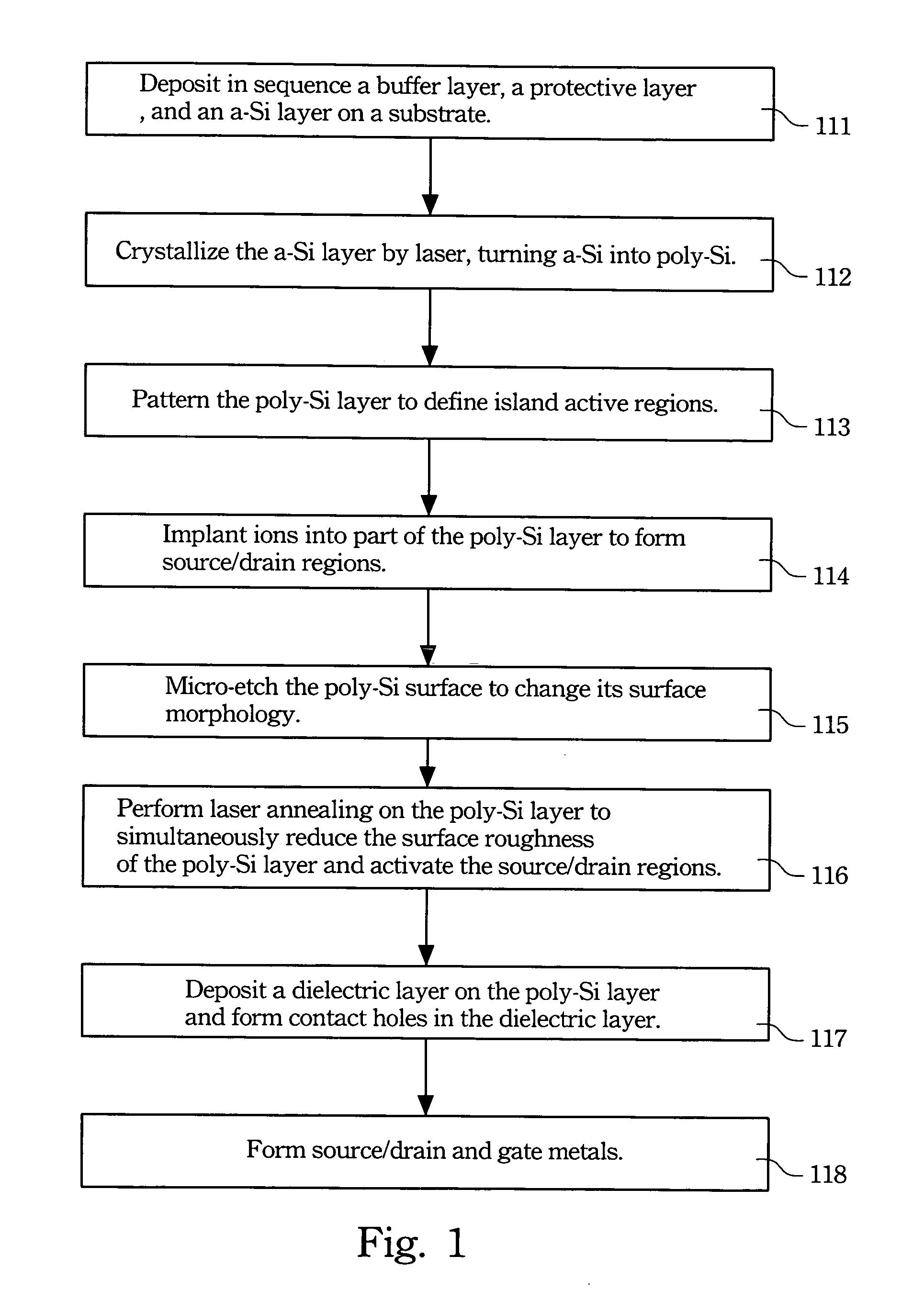

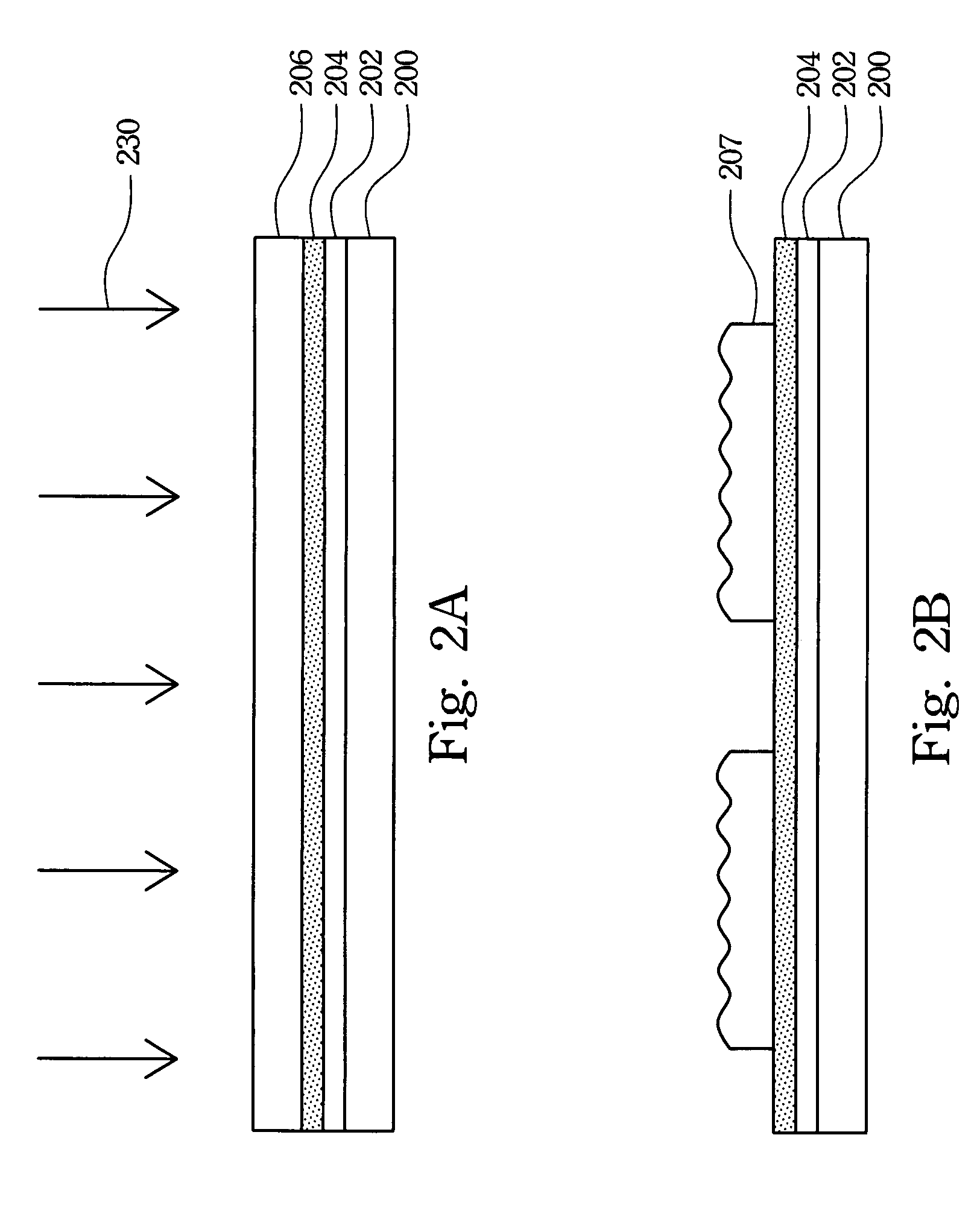

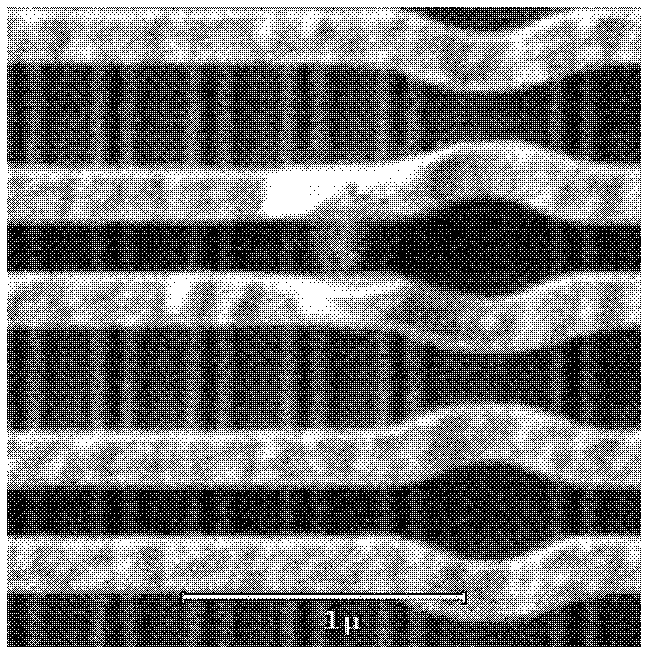

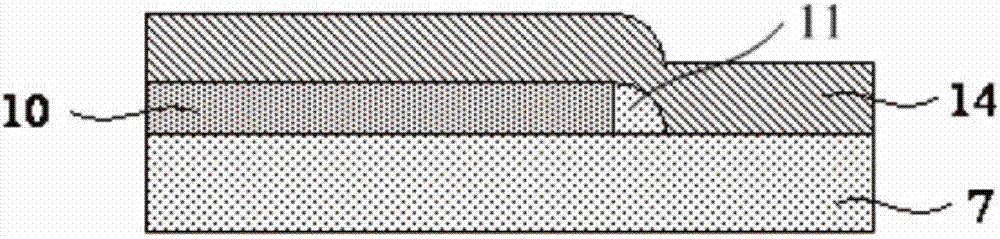

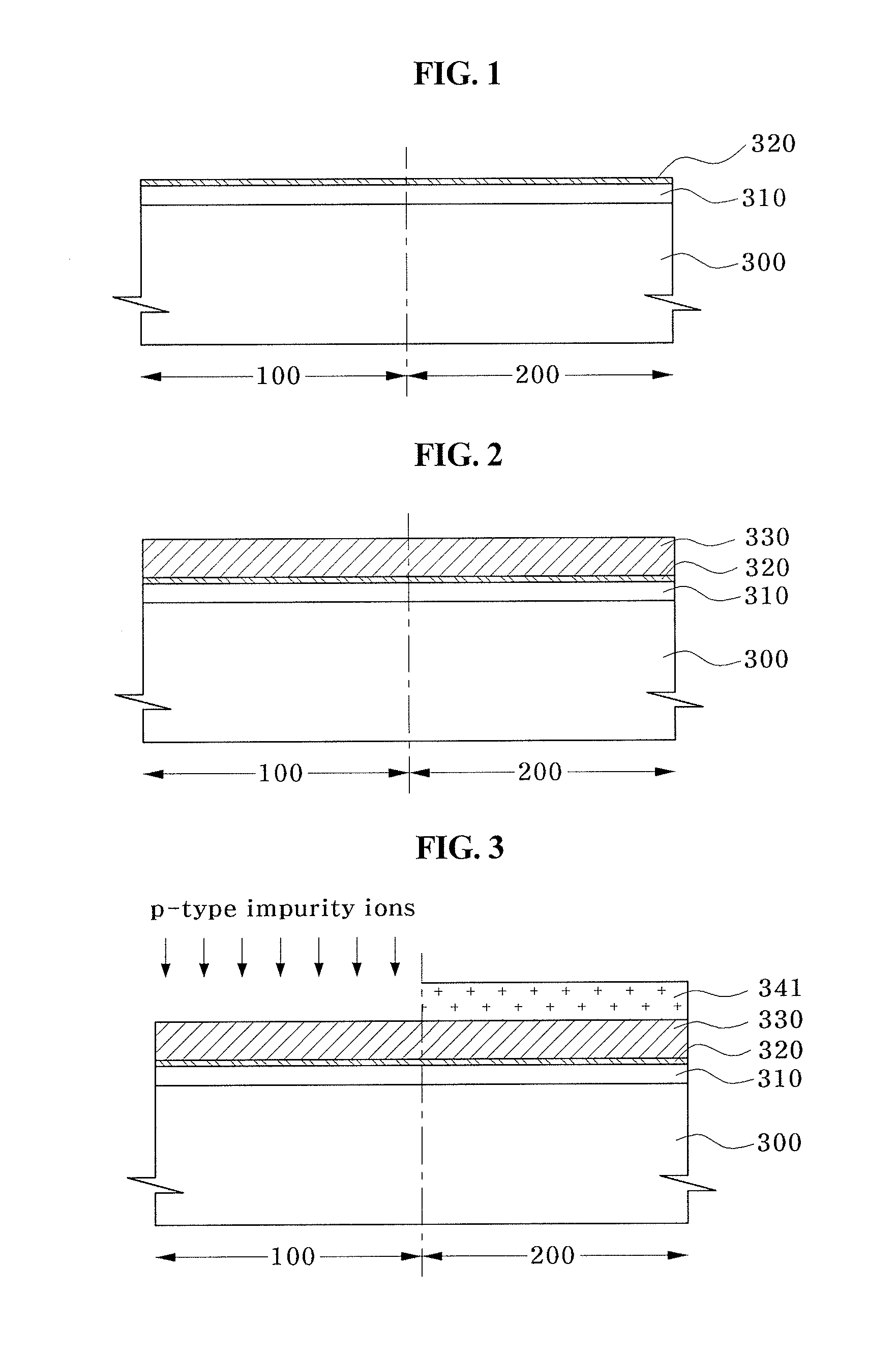

Method of fabricating planarized poly-silicon thin film transistors

InactiveUS20060051905A1Improve etch selectivityProtection from damageSolid-state devicesSemiconductor/solid-state device manufacturingSilicon thin filmIon implantation

A buffer layer, a protective layer and a poly-silicon layer are formed on a substrate in turn, and the poly-silicon layer is then patterned to form island active regions. Next, n-type ions are implanted into portions of the poly-silicon layer to form source / drain regions. Then, a dilute buffer oxide etchant is utilized to micro-etch the poly-silicon layer to change the surface morphology of the poly-silicon. Finally, a laser annealing process is performed to partially melt the poly-silicon for forming a smooth surface and activating the source / drain region of the poly-silicon simultaneously.

Owner:IND TECH RES INST

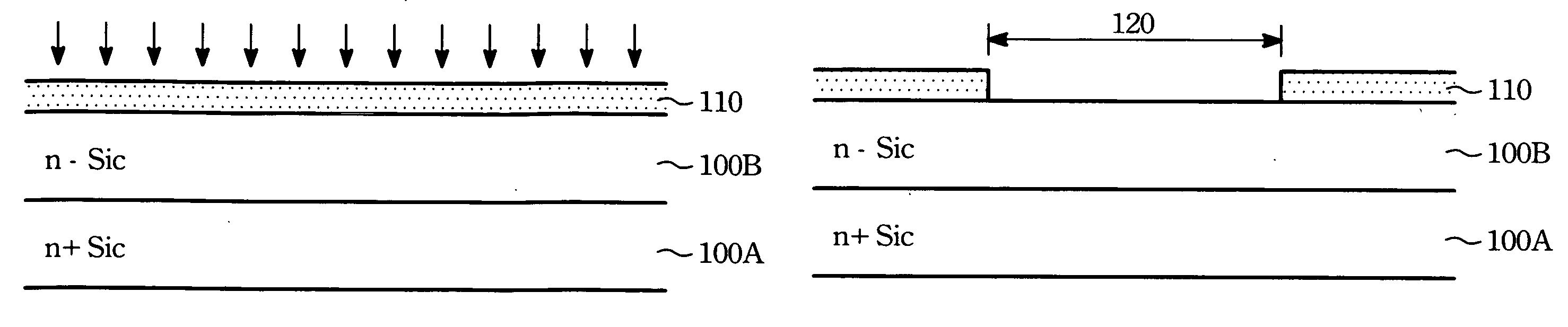

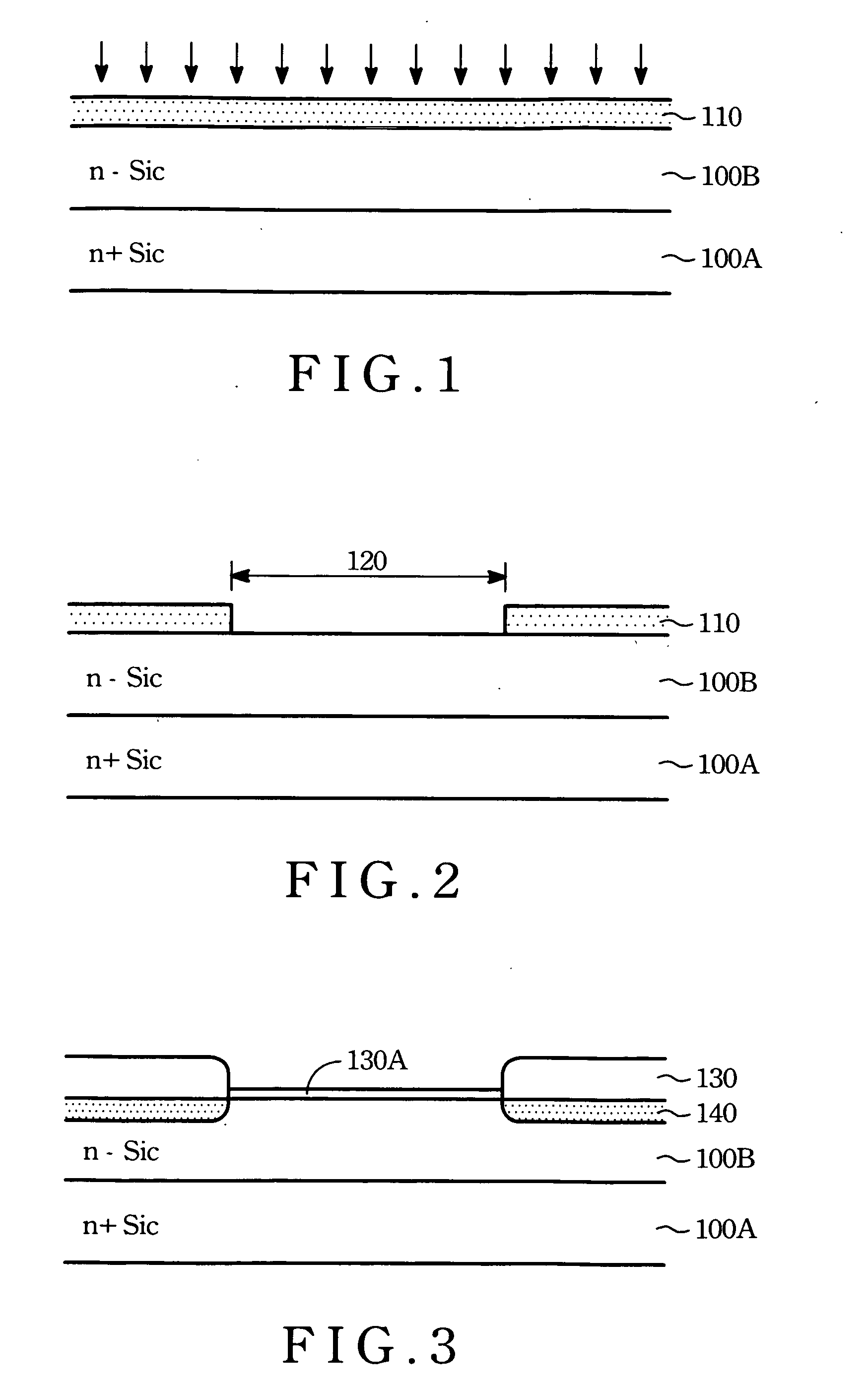

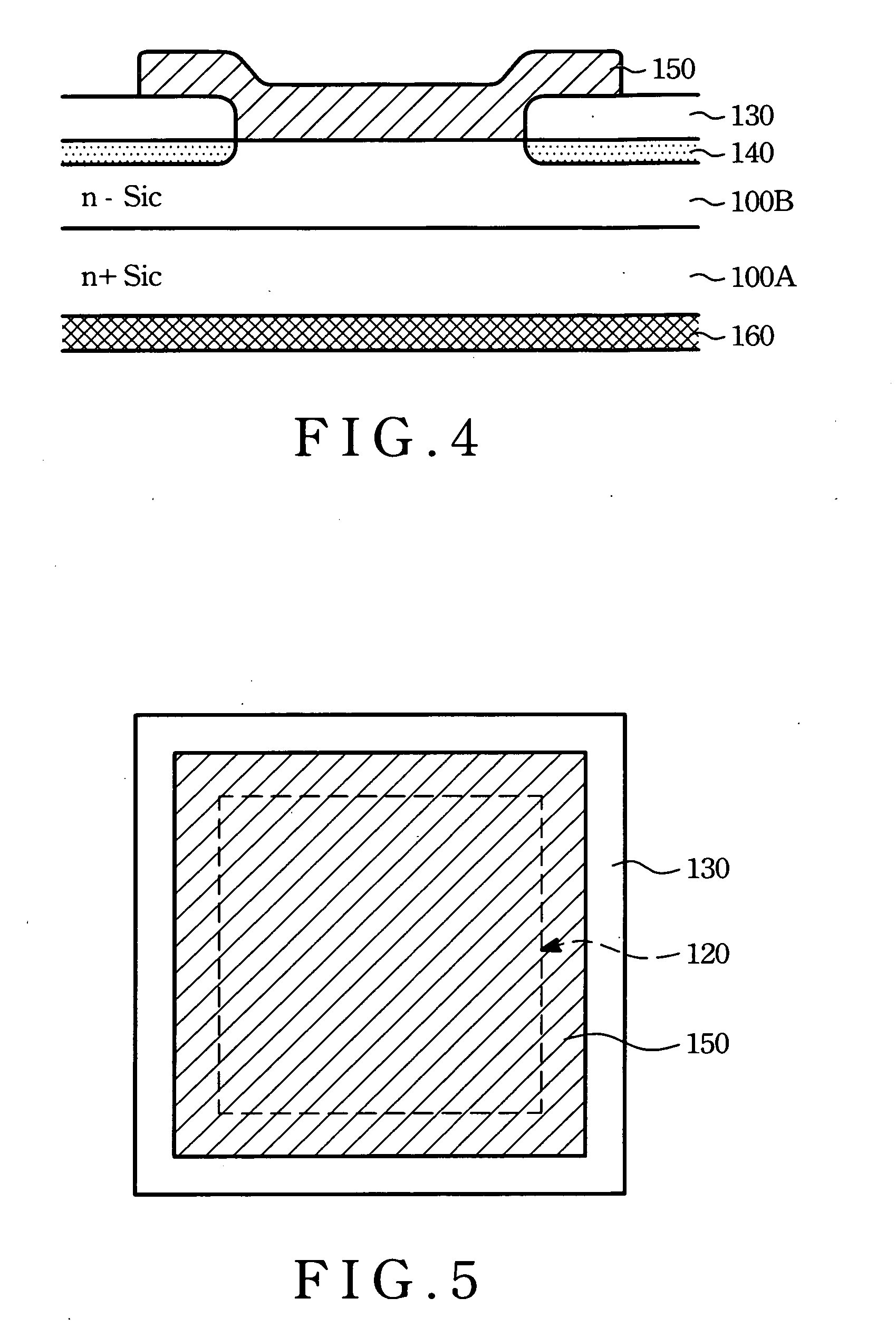

Silicon carbide Schottky diode and method of making the same

ActiveUS20070293001A1Semiconductor/solid-state device manufacturingSemiconductor devicesThin oxideLayer removal

A method of forming silicon carbide Schottky diode is disclosed. The processes required two photo-masks only. The processes are as follows: firstly, an n+-silicon carbide substrate having an n− silicon carbide drift layer is provided. Then a silicon layer is formed on the drift layer. An ion implant is carried out to dope the silicon layer. Afterward the doped silicon layer is patterned to define an active region. A thermal oxidation is then followed to form a thick oxide layer by oxidizing the silicon layer and form guard rings by using the doped silicon layer as a diffused source. The thin oxide layer on the drift layer is then removed by dilute HF dip or by BOE (buffer oxide etching) solution dip. Thereafter, a top metal layer is deposited and patterned to define as anode. After a backside layer removal, a metal layer served as cathode is formed.

Owner:CHIP INTEGRATION TECH

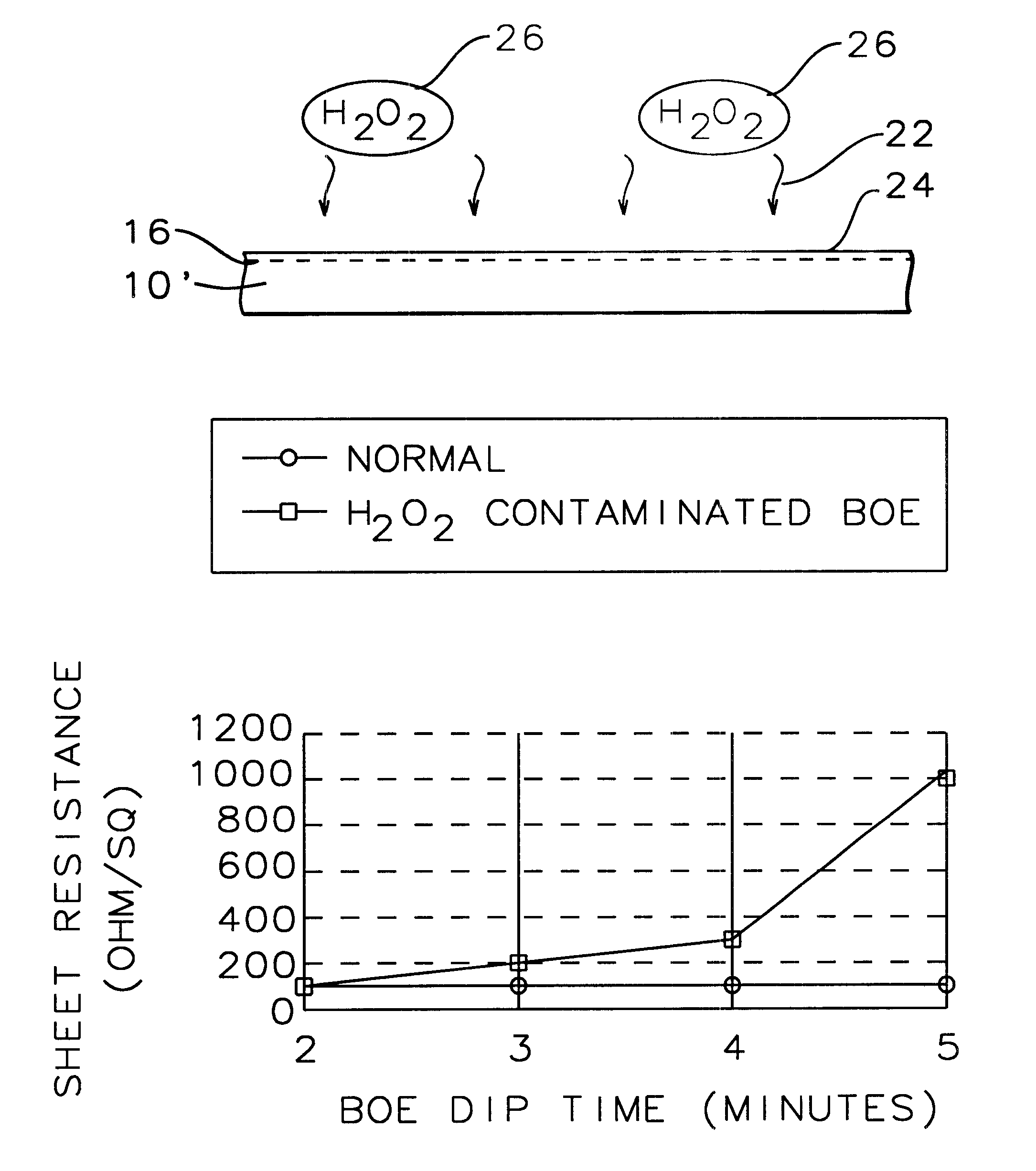

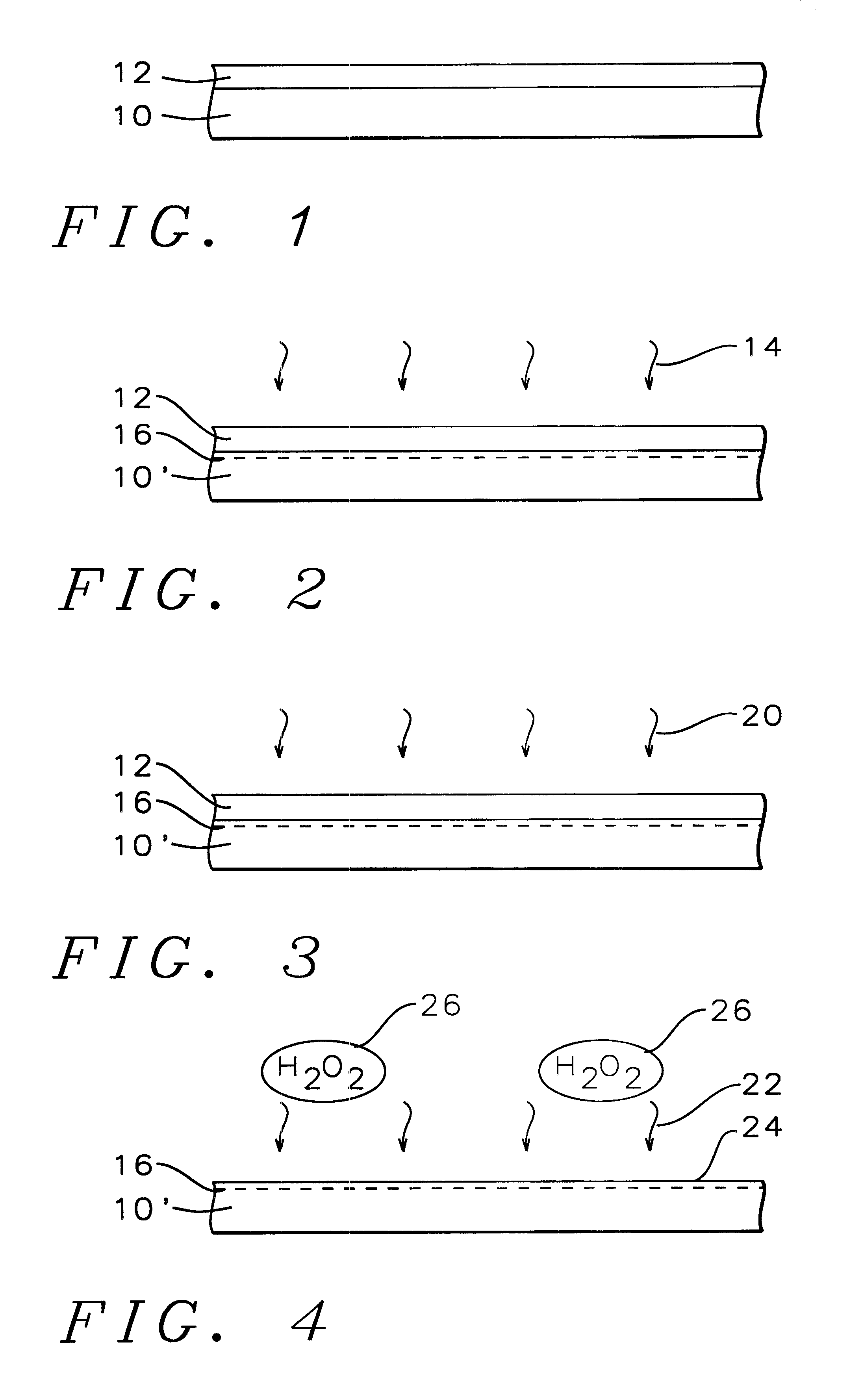

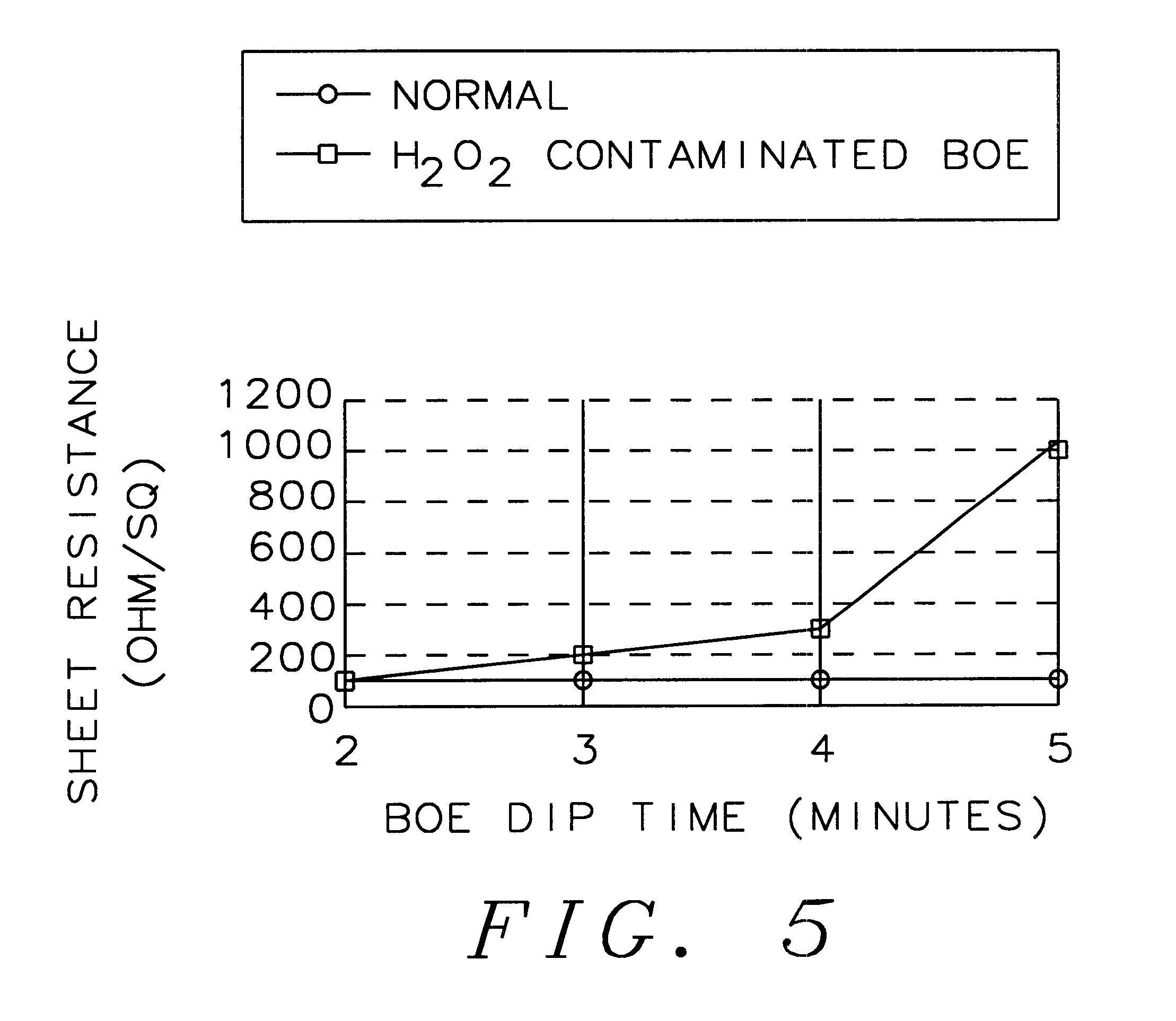

Silicon monitor for detection of H2O2 in acid bath

InactiveUS6358761B1Readily commercially implementedSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingAcid etchingSilicon oxide

A method and means for detection of oxidizing contamination in acid etching baths employed to etch silicon oxide layers from silicon substrates employed in silicon integrated circuit microelectronics fabrications. There is provided a silicon substrate having within a doped region formed employing ion implantation. The silicon substrate is immersed within a buffered oxide etch (BOE) acid bath, wherein the presence of an oxidizing contaminant correlates with an increase in the resistance of the doped region upon the removal of any silicon oxide layer on the silicon surface.

Owner:TAIWAN SEMICON MFG CO LTD

Gate-oxide etching method and multi-grid-electrode manufacturing method

ActiveCN103165437AAvoid damageQuality improvementSemiconductor/solid-state device manufacturingSemiconductor devicesParticulatesEtching

The invention provides a gate-oxide etching method and a multi-grid-electrode manufacturing method. The gate-oxide etching method includes controlling over-etching time of buffered oxide etch (BOE), enabling over-etching time of the BOE to be smaller than 30% of main etching time, and matching with concentration ratio of APM. According to the method, damage on surface of a lining can be reduced on the condition that the gate-oxide is completely etched. Meanwhile, the gate-oxide etching method is applied to the multi-grid-electrode manufacturing method, and defects of particulate matters can be reduced, so that quality of multi-grid-electrode components is greatly improved.

Owner:CSMC TECH FAB2 CO LTD

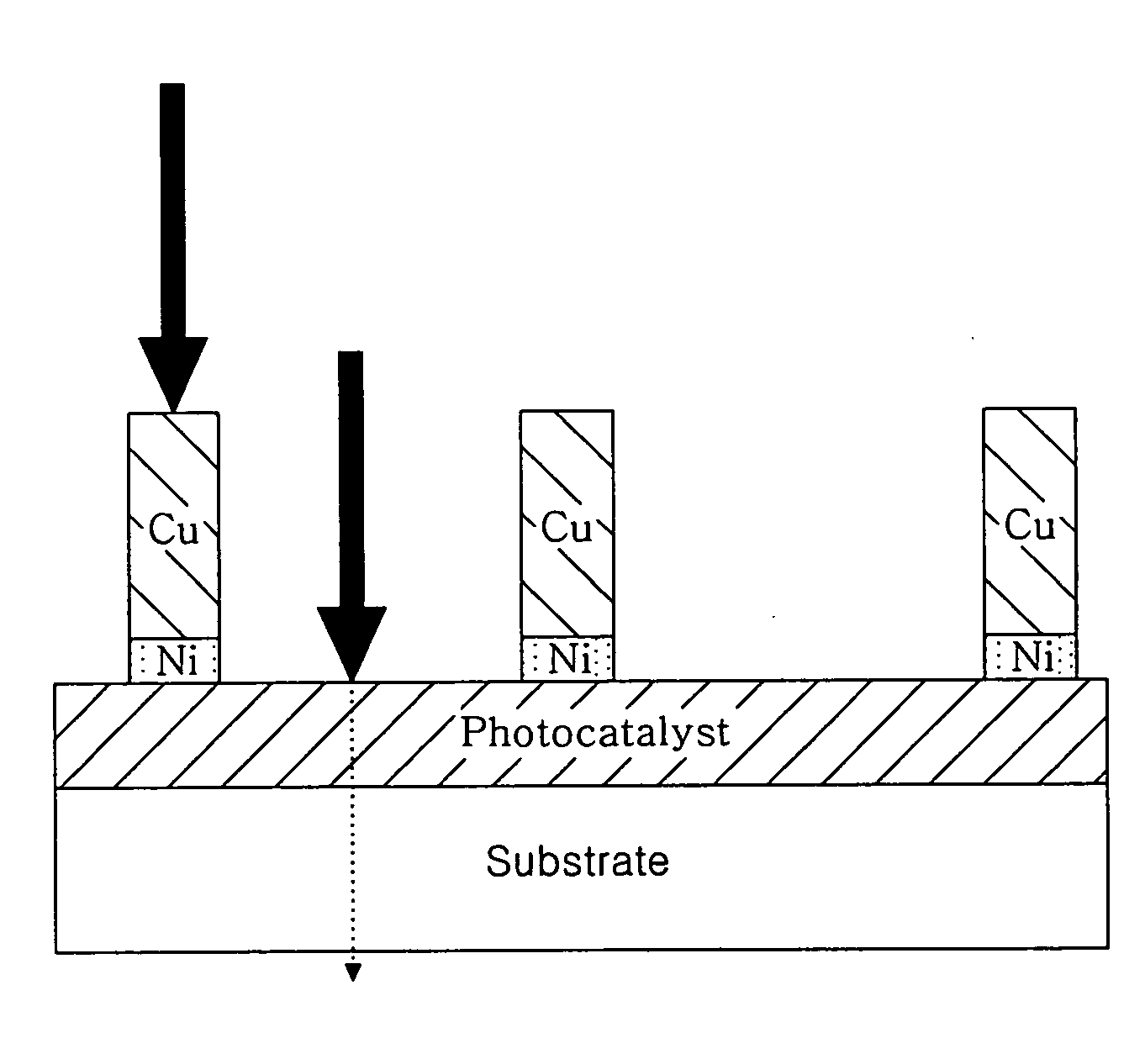

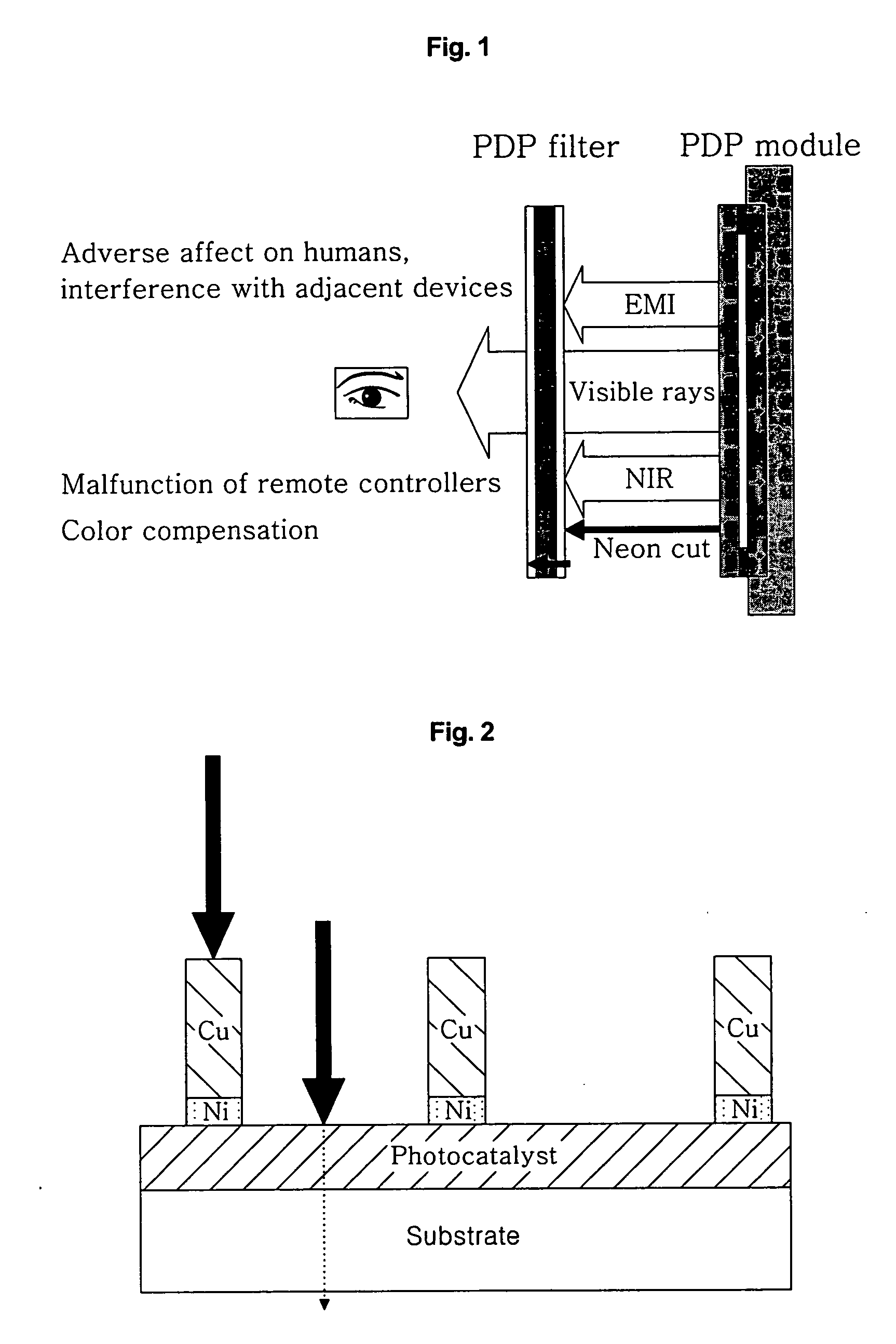

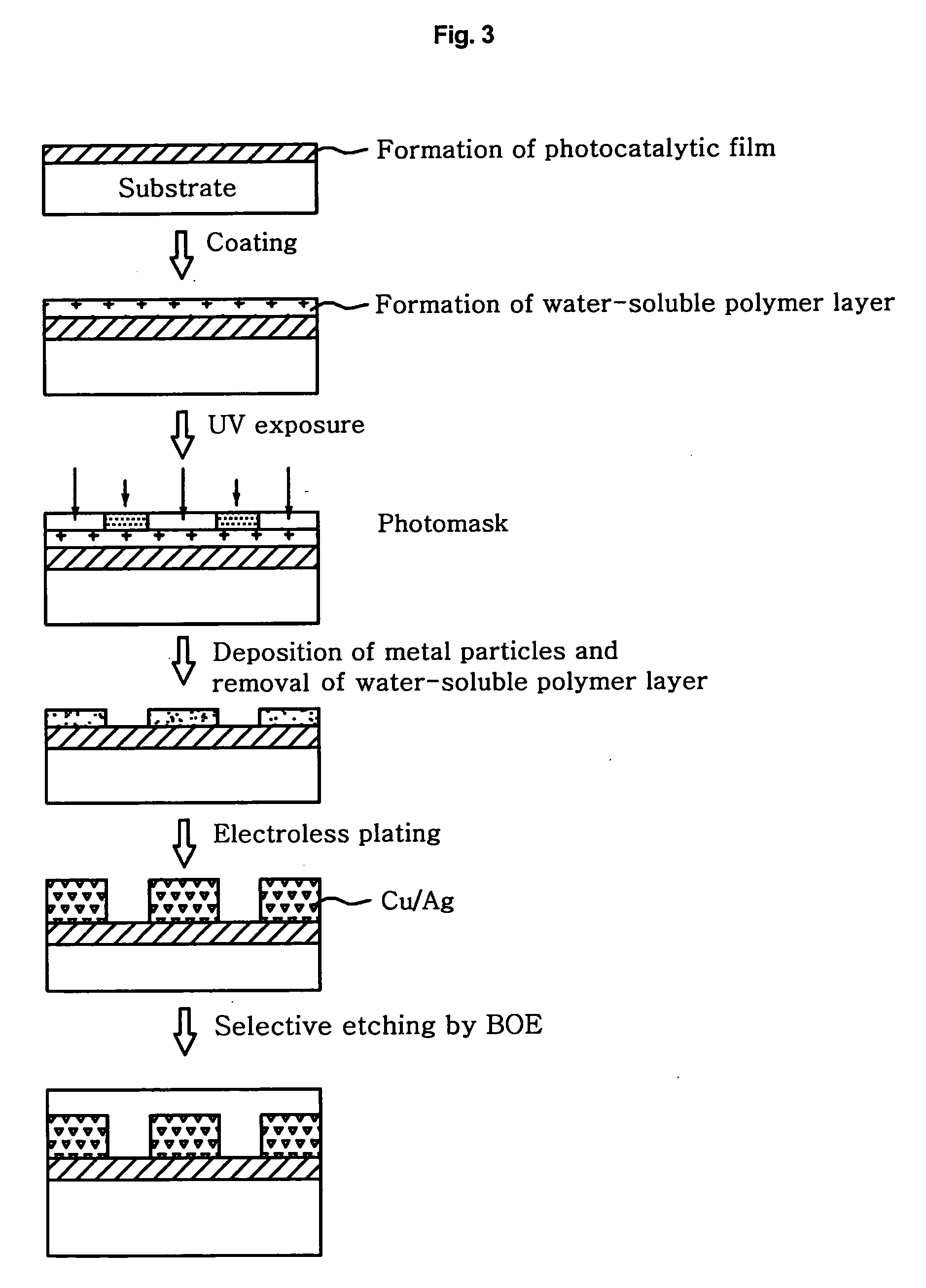

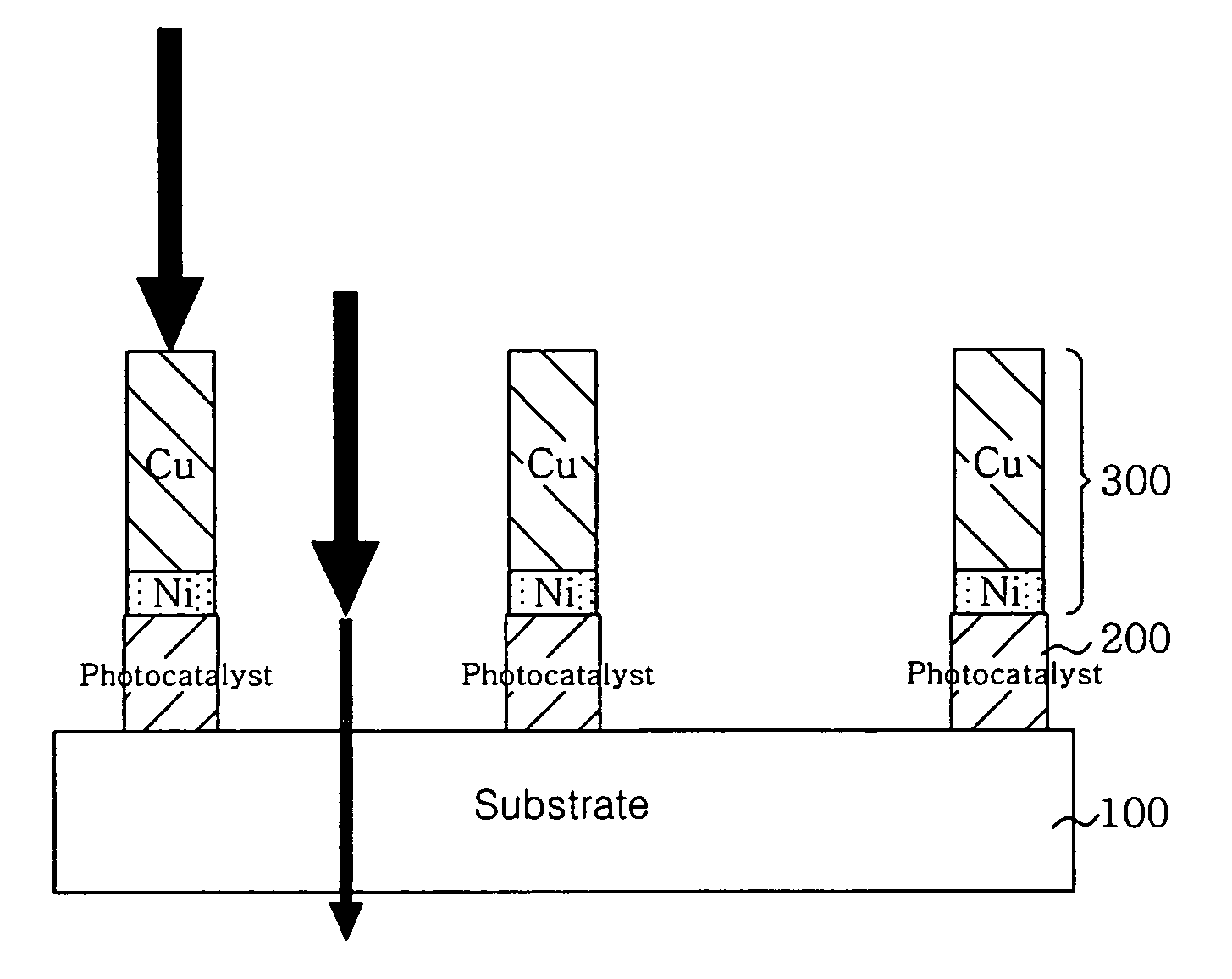

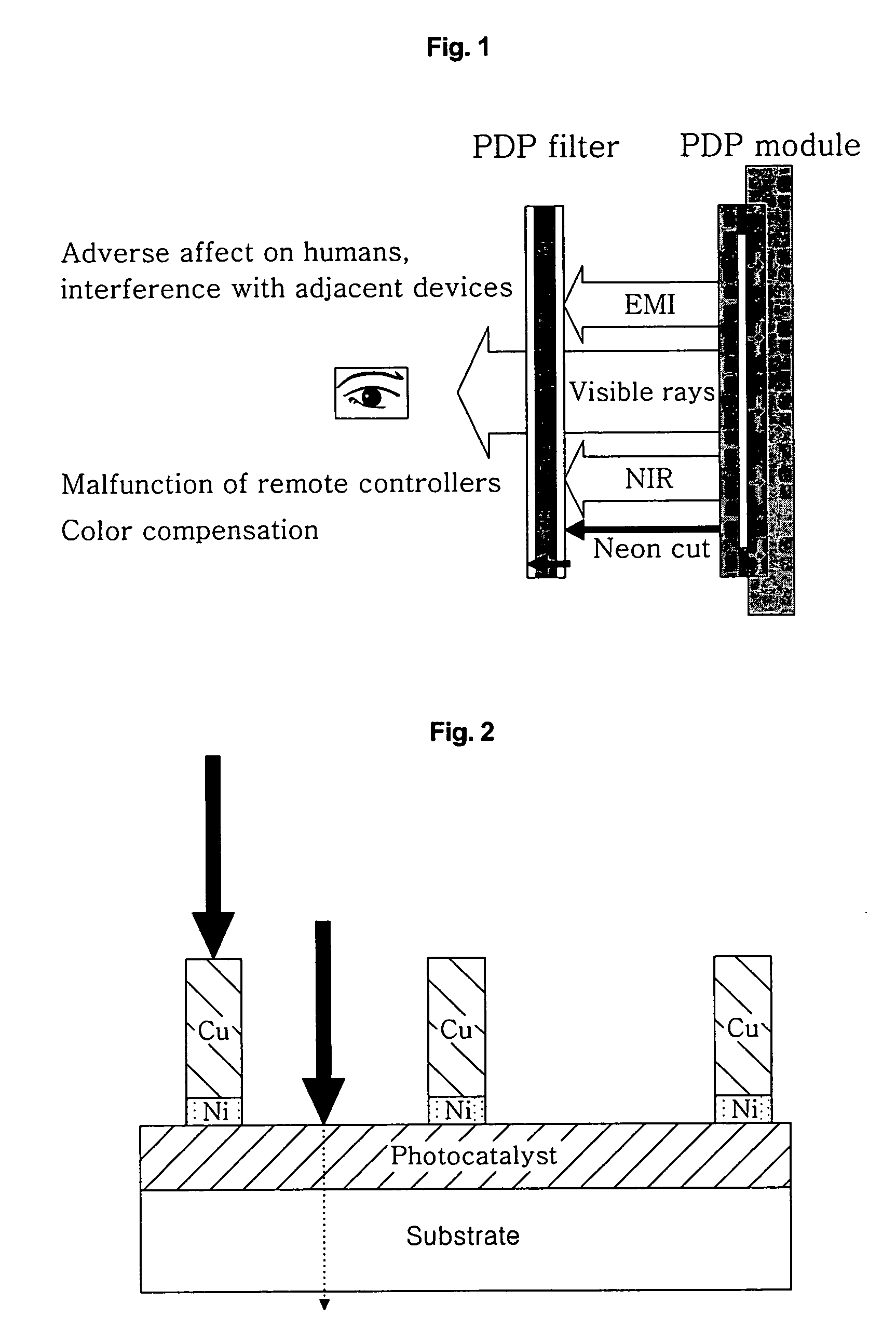

Method for manufacturing high-transmittance optical filter for image display devices

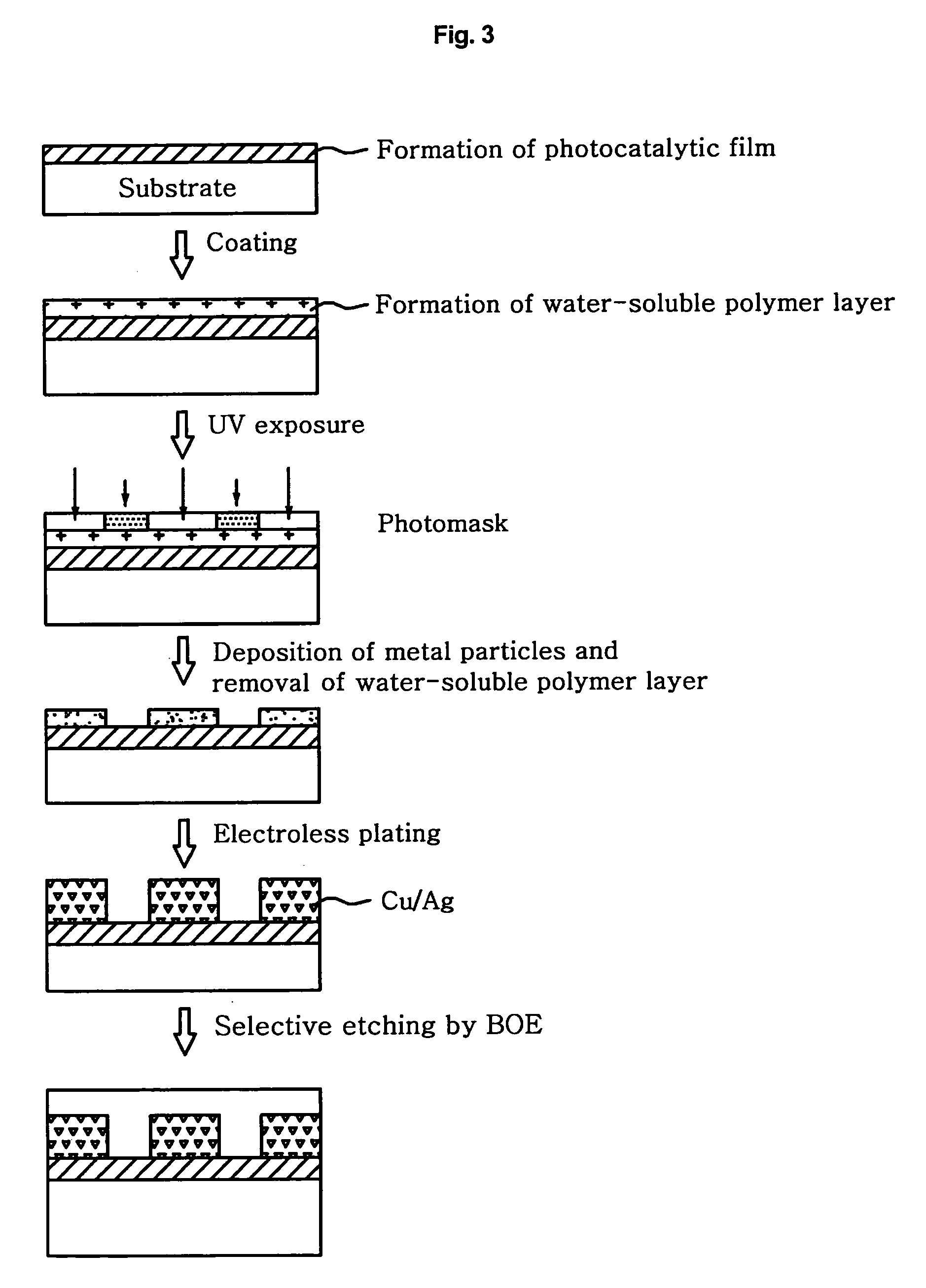

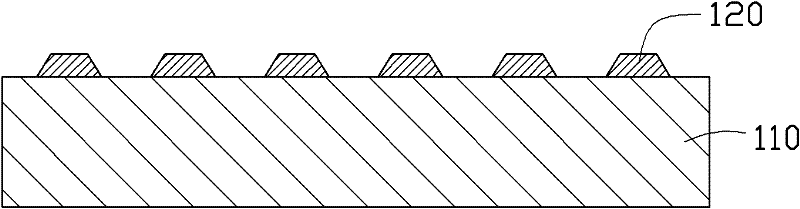

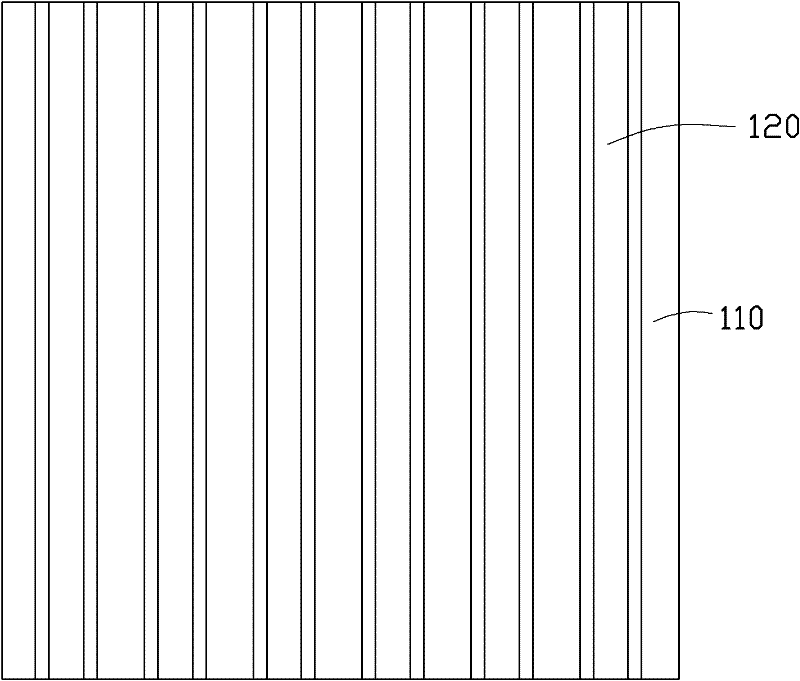

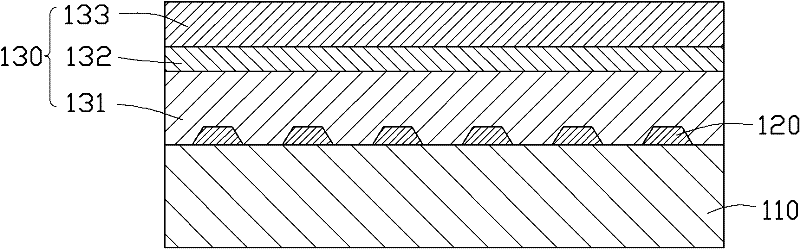

InactiveUS20060127818A1High light transmittanceGood effectMagnetic/electric field screeningPretreated surfacesImage resolutionDisplay device

A method for manufacturing a high-transmittance optical filter for image display devices, which may include the steps of coating a photocatalytic compound on a transparent substrate to form a photocatalytic film, selectively exposing the photocatalytic film to light and growing a metal crystal thereon by plating to form a metal pattern, and selectively etching and removing the photocatalytic compound remaining on the transparent substrate using a buffered oxide etchant (BOE). According to the method, a high-transmittance, high-resolution and low-resistivity optical filter can be manufactured in a simple manner at low costs.

Owner:SAMSUNG CORNING PRECISION MATERIALS CO LTD

Method for manufacturing high-transmittance optical filter for image display devices

InactiveUS7205098B2Good effectHigh light transmittanceMagnetic/electric field screeningOptical filtersImage resolutionDisplay device

A method for manufacturing a high-transmittance optical filter for image display devices, which may include the steps of coating a photocatalytic compound on a transparent substrate to form a photocatalytic film, selectively exposing the photocatalytic film to light and growing a metal crystal thereon by plating to form a metal pattern, and selectively etching and removing the photocatalytic compound remaining on the transparent substrate using a buffered oxide etchant (BOE). According to the method, a high-transmittance, high-resolution and low-resistivity optical filter can be manufactured in a simple manner at low costs.

Owner:SAMSUNG CORNING PRECISION MATERIALS CO LTD

Method for manufacturing light emitting diode (LED) grains

The invention relates to a method for manufacturing light emitting diode (LED) grains. A silicon dioxide pattern layer is formed at the bottoms of the LED grains and is removed by buffered oxide etch to form penetrating holes after the growth of a semiconductor light emitting structure is finished; and through the penetrating holes, the probability that light rays which are emitted by the semiconductor light emitting structure and face a sapphire substrate are emitted upwards through total reflection can be improved, so that the light emitting efficiency of the LED grains is improved.

Owner:ZHANJING TECH SHENZHEN +1

Method of fabricating array substrate

ActiveUS8158469B2Improve propertiesImprove production yieldSolid-state devicesSemiconductor/solid-state device manufacturingAmorphous siliconOptoelectronics

A method of fabricating an array substrate includes forming a gate line and a gate electrode; forming a gate insulating layer, an intrinsic amorphous silicon layer, an inorganic material insulating layer and a heat transfer layer on the gate line and the gate electrode; irradiating a laser beam onto the heat transfer layer to crystallize the intrinsic amorphous silicon layer into a polycrystalline silicon layer; removing the heat transfer layer; patterning the inorganic insulating material layer using a buffered oxide etchant to form an etch-stopper corresponding to the gate electrode forming an impurity-doped amorphous silicon layer and a metal layer on the etch-stopper and the polycrystalline silicon layer; patterning the metal layer to form a data line, a source electrode and a drain electrode and forming a pixel electrode on the passivation layer.

Owner:LG DISPLAY CO LTD

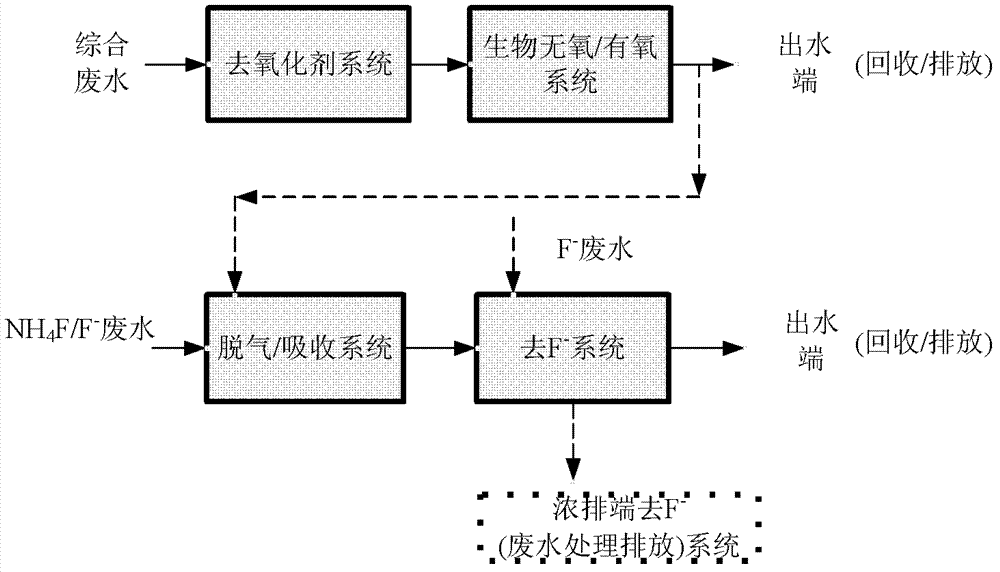

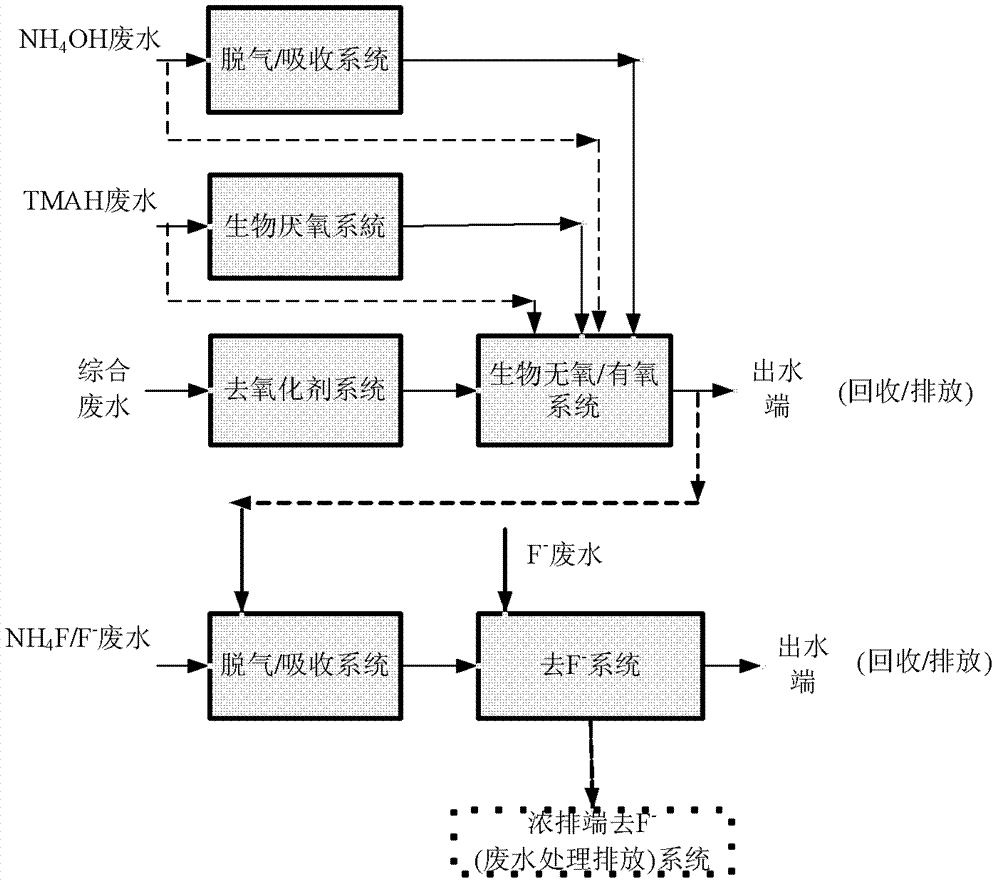

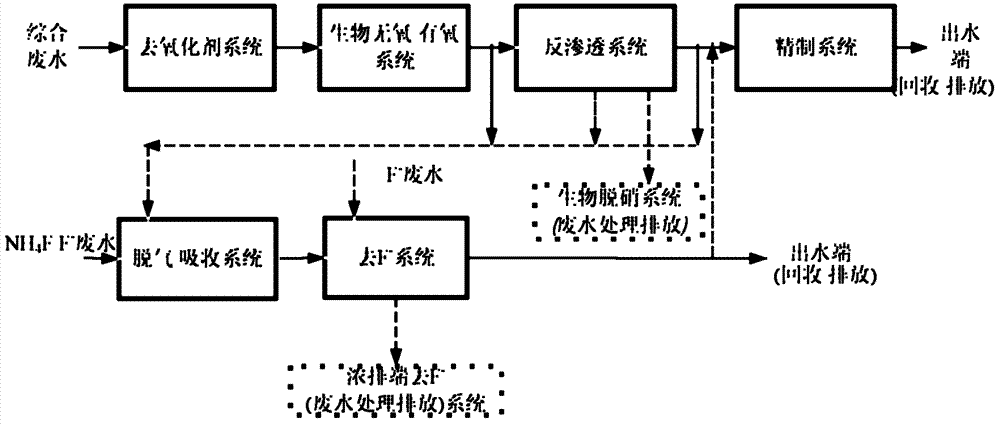

Method for treating semiconductor technology wastewater

The invention provides a method for treating synthetic wastewater collected by several strands of semiconductor technology wastewater, wherein the synthetic wastewater does not contain the NH4F / HF buffered oxide etch solution wastewater (NH4F / F wastewater for short), but basically contains an oxidizing agent, organic and inorganic substances, and ammonia nitrogen impurities. Firstly, the synthetic wastewater is treated by an antioxidant; subsequently treated in the anaerobic microbial decomposition way, the impurities are partly decomposed; and then the wastewater is treated in the aerobic microbial decomposition way, the residual organic substances and the ammonia nitrogen impurities are furthermore decomposed, thus the recyclable or dischargeable wastewater is obtained. The method also comprises the steps of individually treating an NH4OH rinsing wastewater, a TMAH yellow light technology wastewater or the NH4F / F wastewater, and also comprises the treatment method of collecting the individually treated wastewaters into the synthetic wastewater.

Owner:金光祖

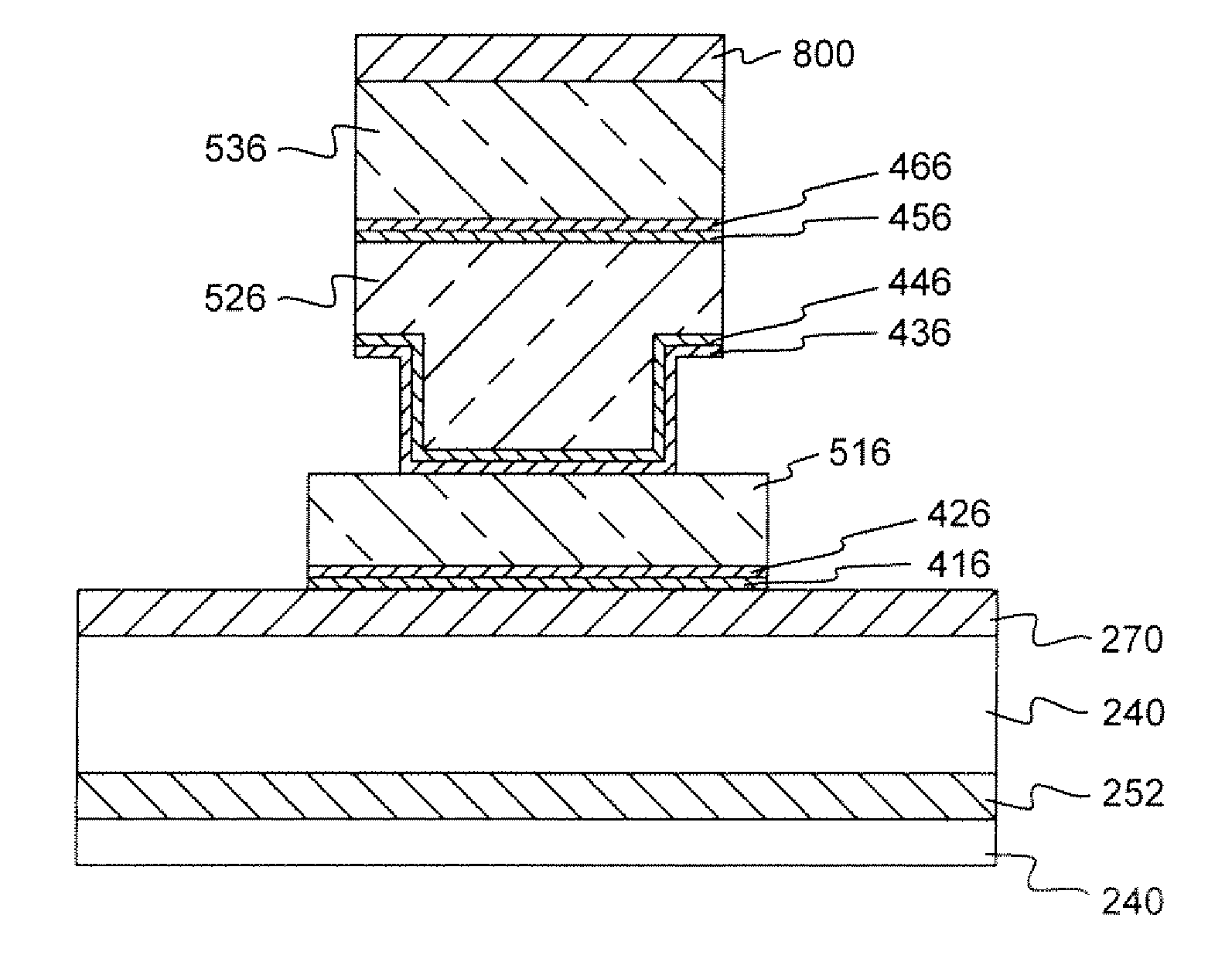

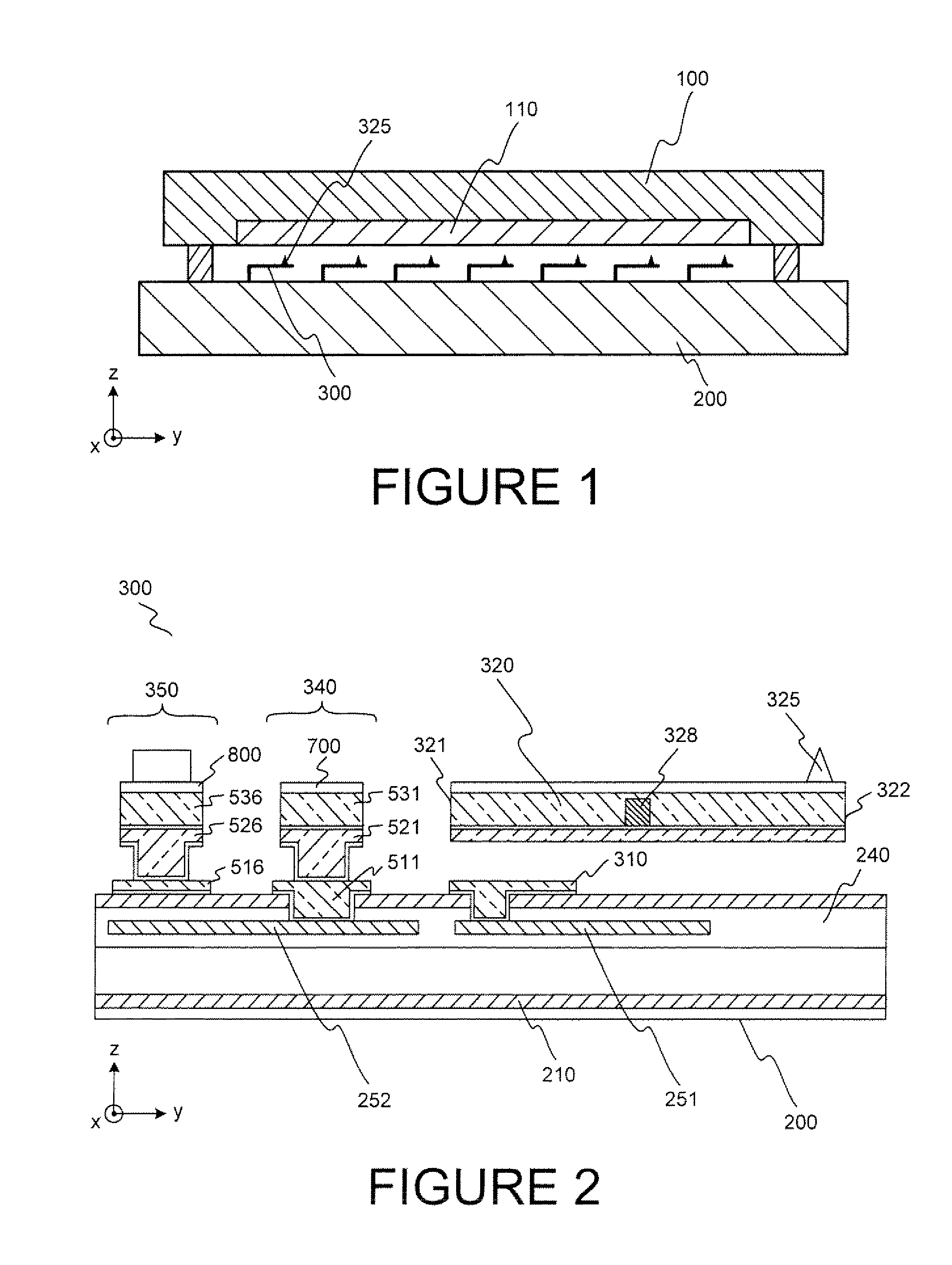

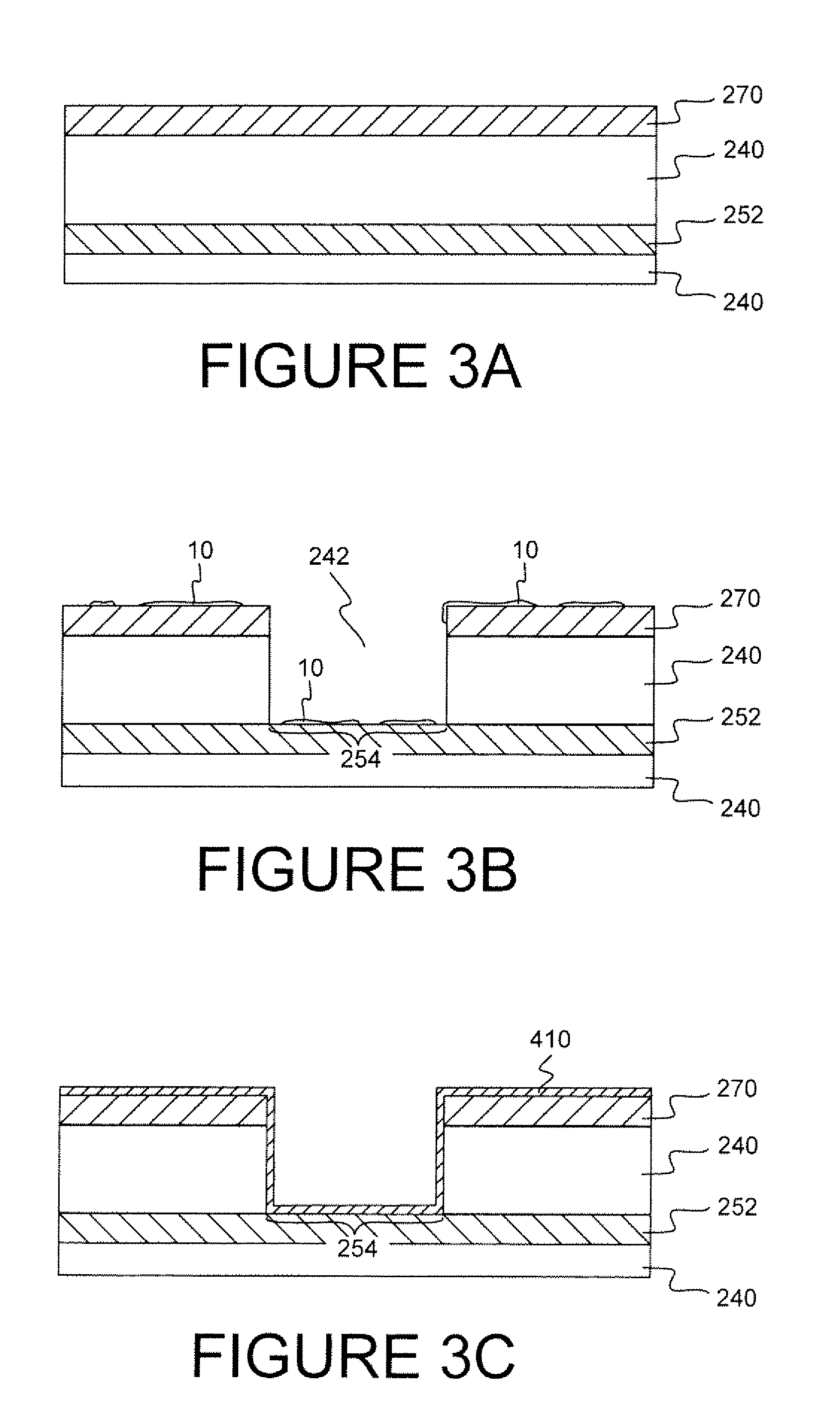

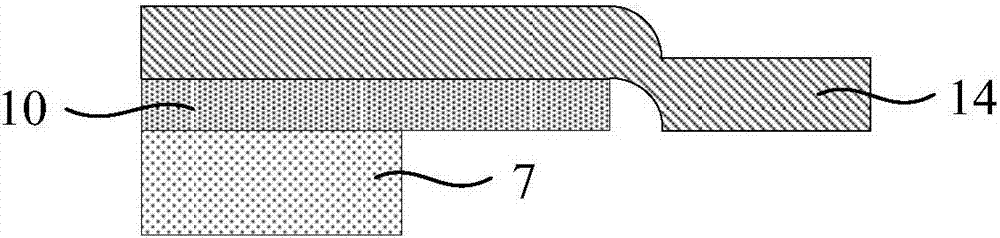

Method and device of preventing delamination of semiconductor layers

InactiveUS20100276788A1Semiconductor/solid-state device detailsSolid-state devicesDielectricProtection layer

Embodiments of the present invention describe a method and device of preventing delamination of semiconductor layers in a semiconductor device. The semiconductor device comprises a substrate with an interlayer dielectric (ILD). A protection layer is deposited on the ILD. Next, a getter layer is formed on the protection layer to remove any native oxides on the protection layer. A capping layer is then deposited on the getter layer to prevent oxidation of the getter layer. Next, a semiconductor layer is formed on the capping layer. An oxide layer is then deposited on the semiconductor layer. Subsequently, a buffered oxide etch solution is used to remove the oxide layer. By removing the native oxides on the protection layer, the getter layer prevents the reaction between the buffered oxide etch solution and the native oxides which may cause delamination of the semiconductor layer and protection layer.

Owner:INTEL CORP

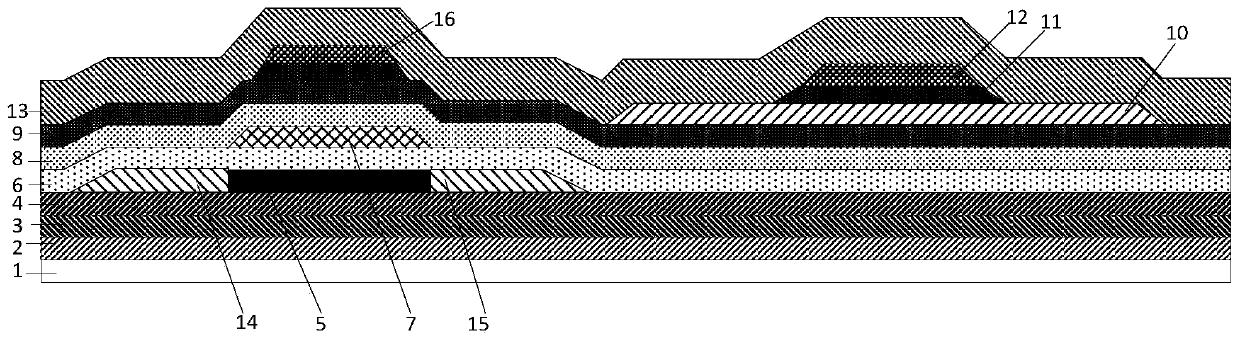

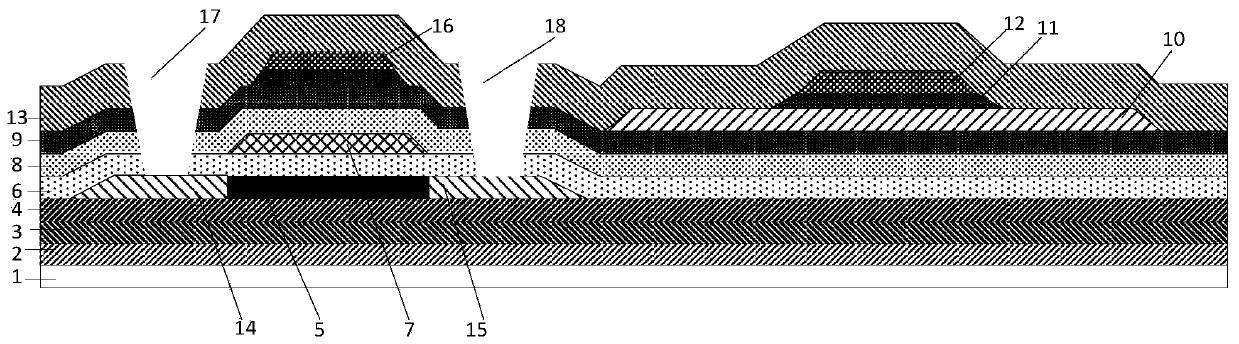

Array substrate and preparation method thereof, and display panel

PendingCN110634793AReduced manufacturing processReliable electrical connectionSolid-state devicesSemiconductor/solid-state device manufacturingBuffered oxide etchPhysics

The invention discloses an array substrate and a preparation method thereof, and a display panel and is used for avoiding breakage of an oxide active layer and improving the product yield. The preparation method of the array substrate comprises steps of forming a first active layer and a first gate layer on the substrate, forming a second active layer and a second gate layer, forming a first through hole and a second through hole for exposing the first active layer, performing the buffer oxide etching process on the first active layer, forming a first source-drain electrode layer comprising afirst source electrode layer which is in contact with the first active layer through the first through hole and a first drain electrode layer which is in contact with the first active layer through the second through hole, forming a third through hole and a fourth through hole for exposing the second active layer, and forming a second source-drain electrode layer comprising a second source electrode layer in contact with the second active layer through a third through hole and a second drain electrode layer in contact with the second active layer through a fourth through hole, and electricallyconnected the second source electrode layer or the second drain electrode layer with the first source-drain electrode layer.

Owner:BOE TECH GRP CO LTD +1

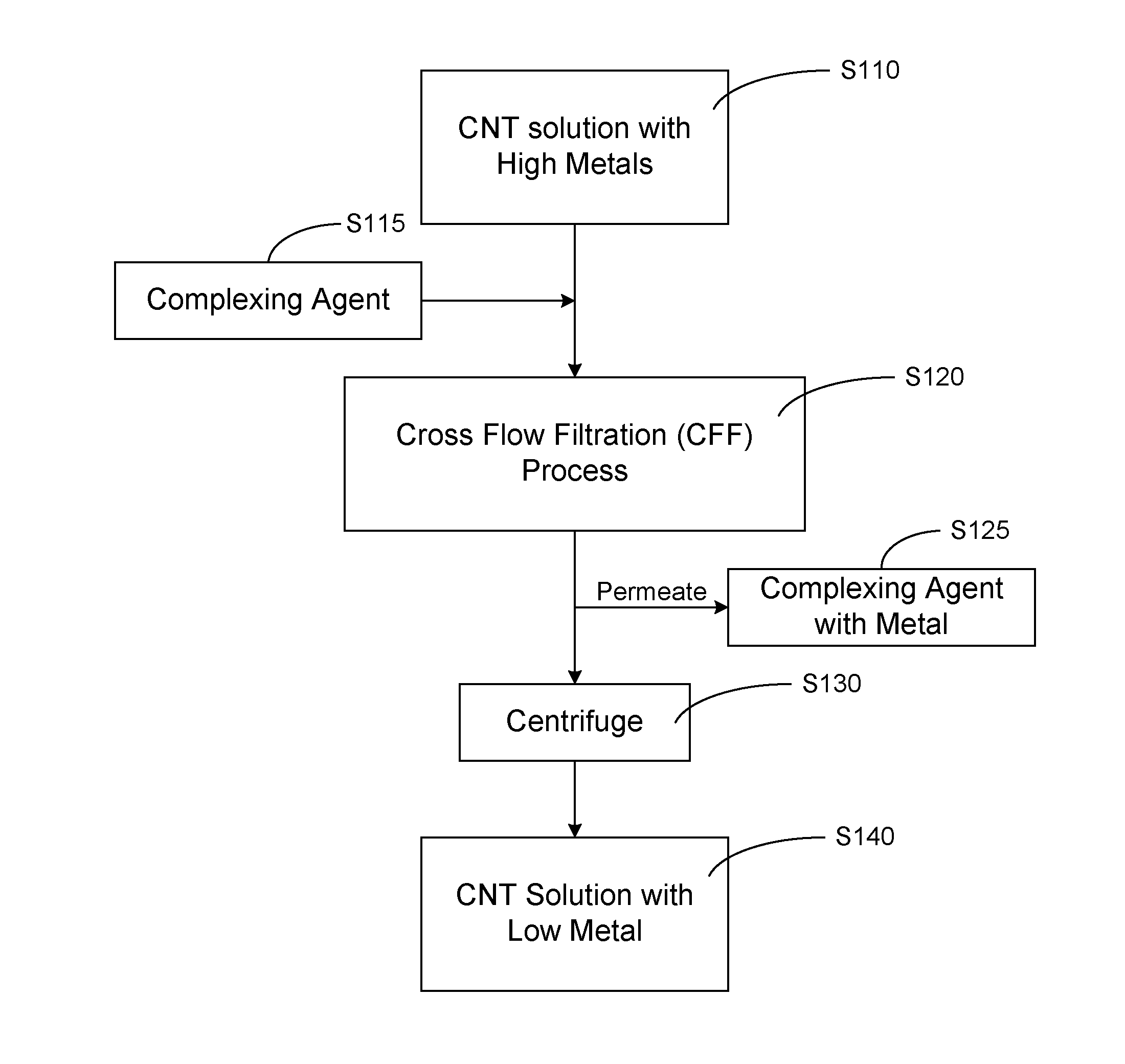

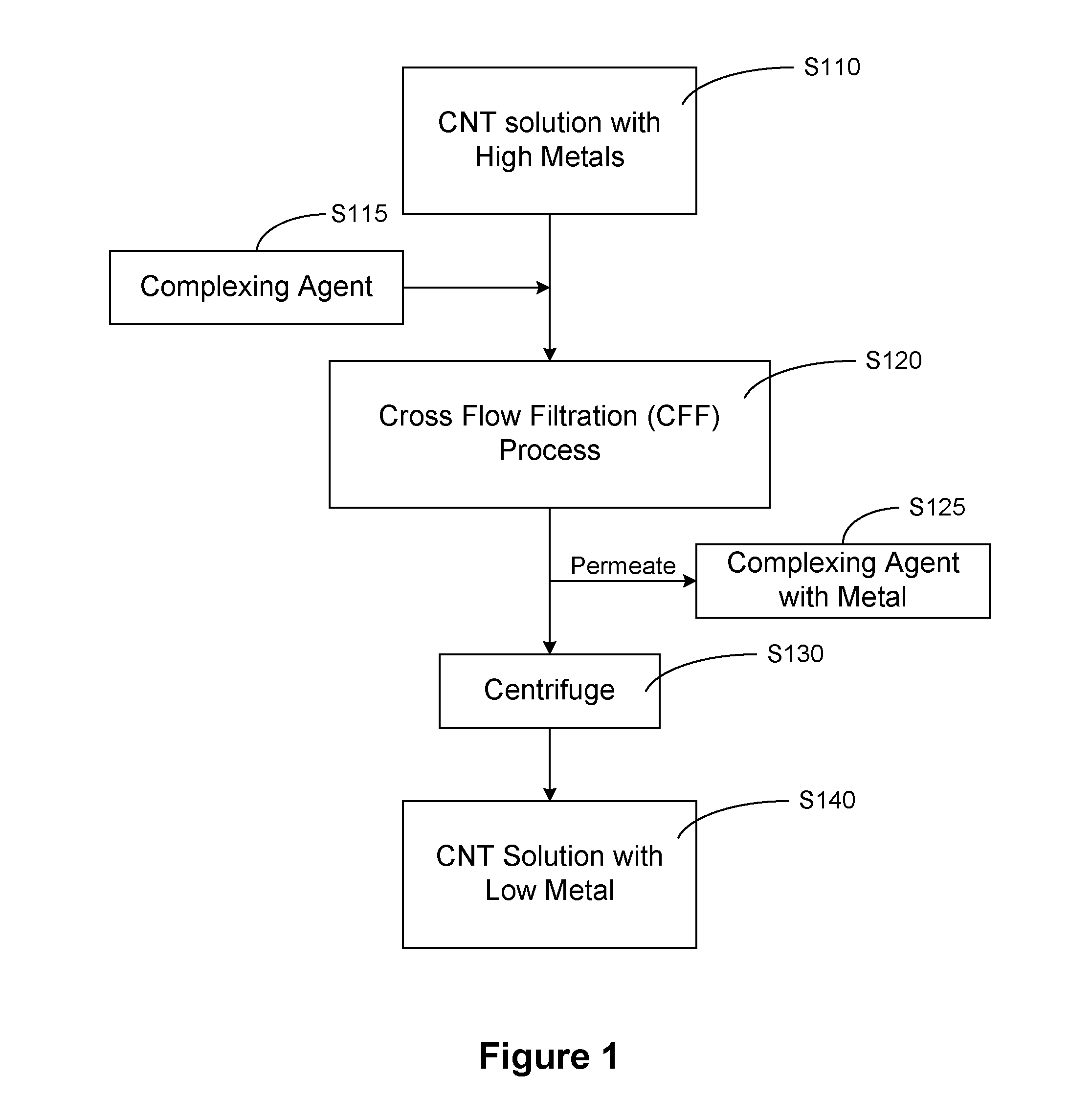

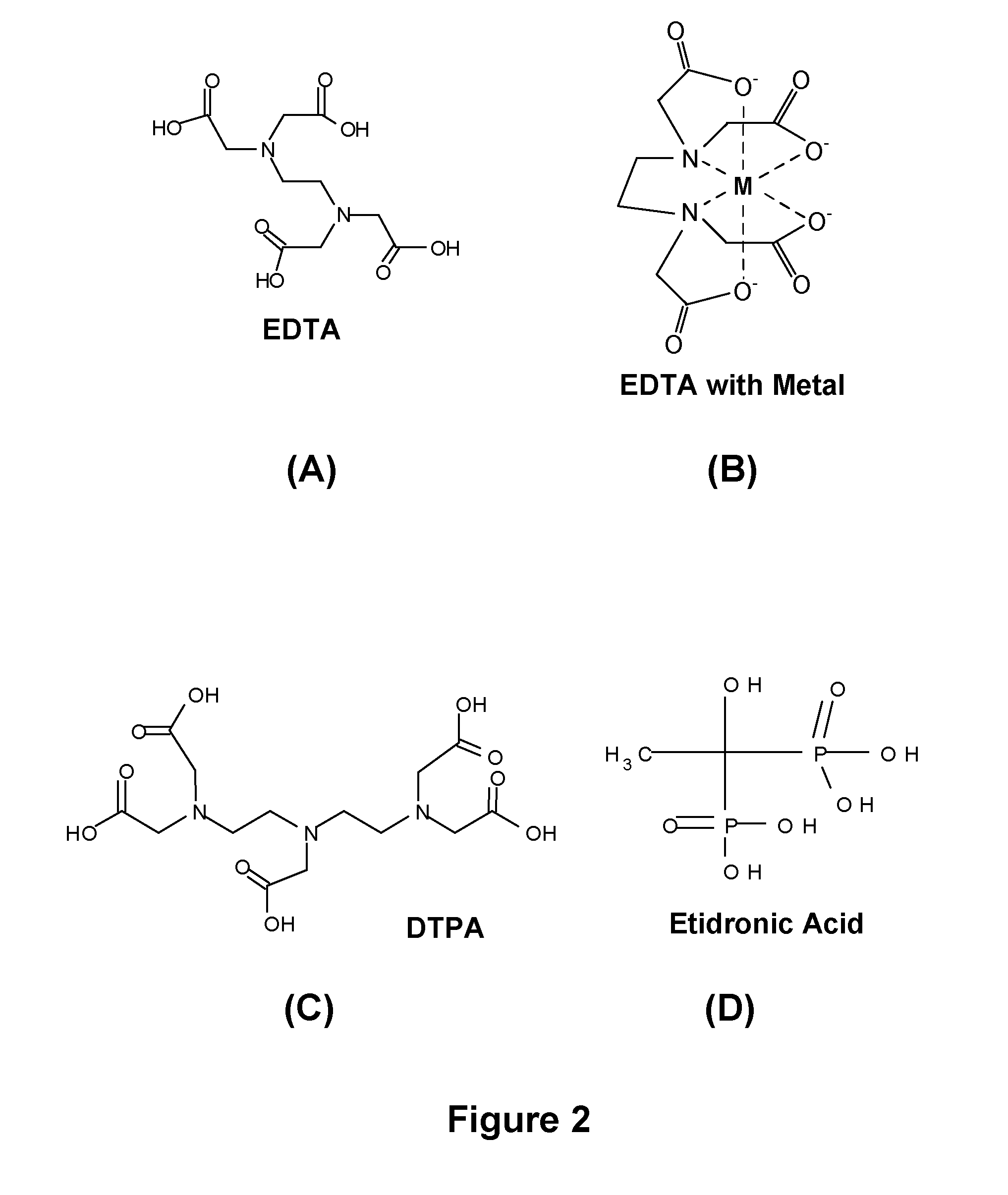

Nanotube solutions with high concentration and low contamination and methods for purifiying nanotube solutions

ActiveUS20130243954A1Reduce pollutionSuitable for useConductive materialSolid-state devicesHigh concentrationLiquid medium

Solutions of carbon nanotubes and methods for purifying the solutions are provided. The methods include mixing, for example, at least one complexing agents, at least one ionic species, and / or at least one buffer oxide etch (BOE) with a liquid medium containing carbon nanotubes and different types of contaminants, such as metal impurities, amorphous carbon, and / or silica particles, and performing a filtration process to the liquid medium so as to remove or reduce the contaminants in the liquid medium. As a result, carbon nanotube solutions of low contaminants are produced. In some embodiments, the solutions of this disclosure include a high concentration of carbon nanotubes and are substantially free from metal, amorphous carbon, and / or silica impurities.

Owner:ZEON CORP

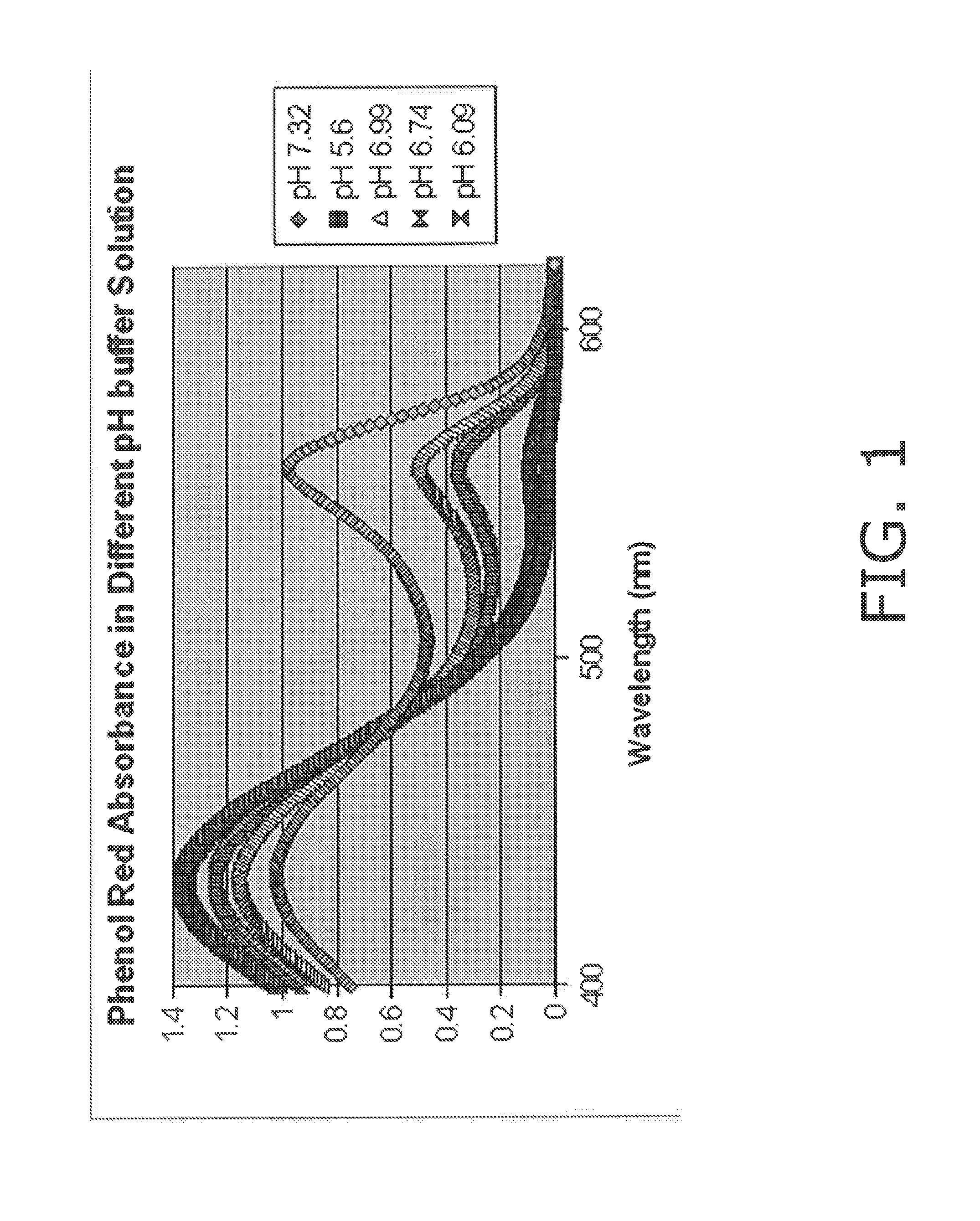

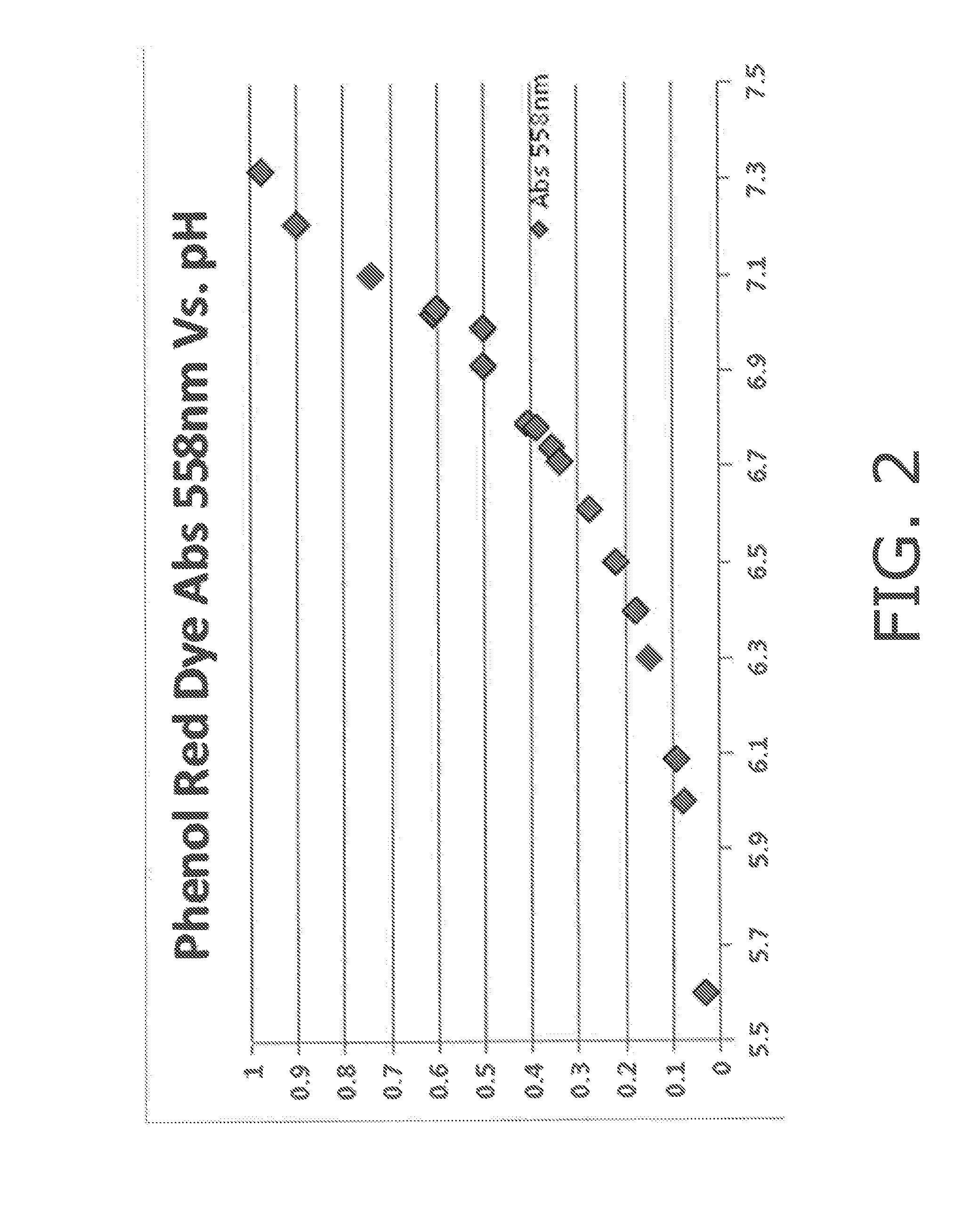

Control over hydrogen fluoride levels in oxide etchant

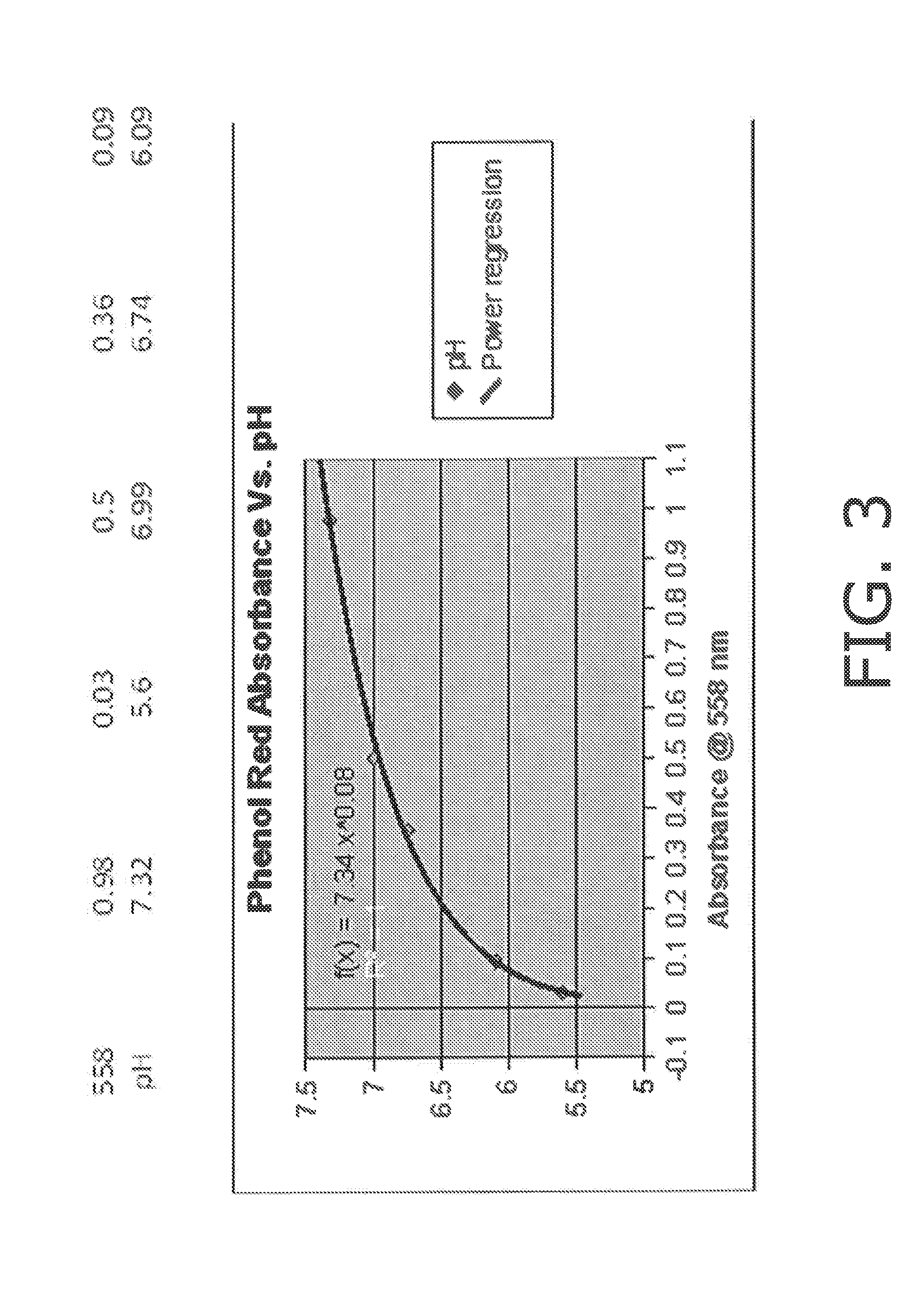

ActiveUS20130183773A1Material analysis by observing effect on chemical indicatorSemiconductor/solid-state device testing/measurementHydrofluoric acidHydrogen fluoride

The invention is directed towards methods and compositions for identifying the amount of hydrofluoric acid in a buffered oxide etching composition. In buffered oxide etching compositions it is very difficult to measure the amount of hydrofluoric acid because it has varying equilibriums and it is toxic so it hard to handle and sample. When used to manufacture microchips however, incorrect amounts of hydrofluoric acid will ruin those chips. The invention utilizes a unique method of spectrographically measuring the hydrofluoric acid when in contact with added chromogenic agents to obtain exact measurements that are accurate, immediate, and safe.

Owner:NALCO CO

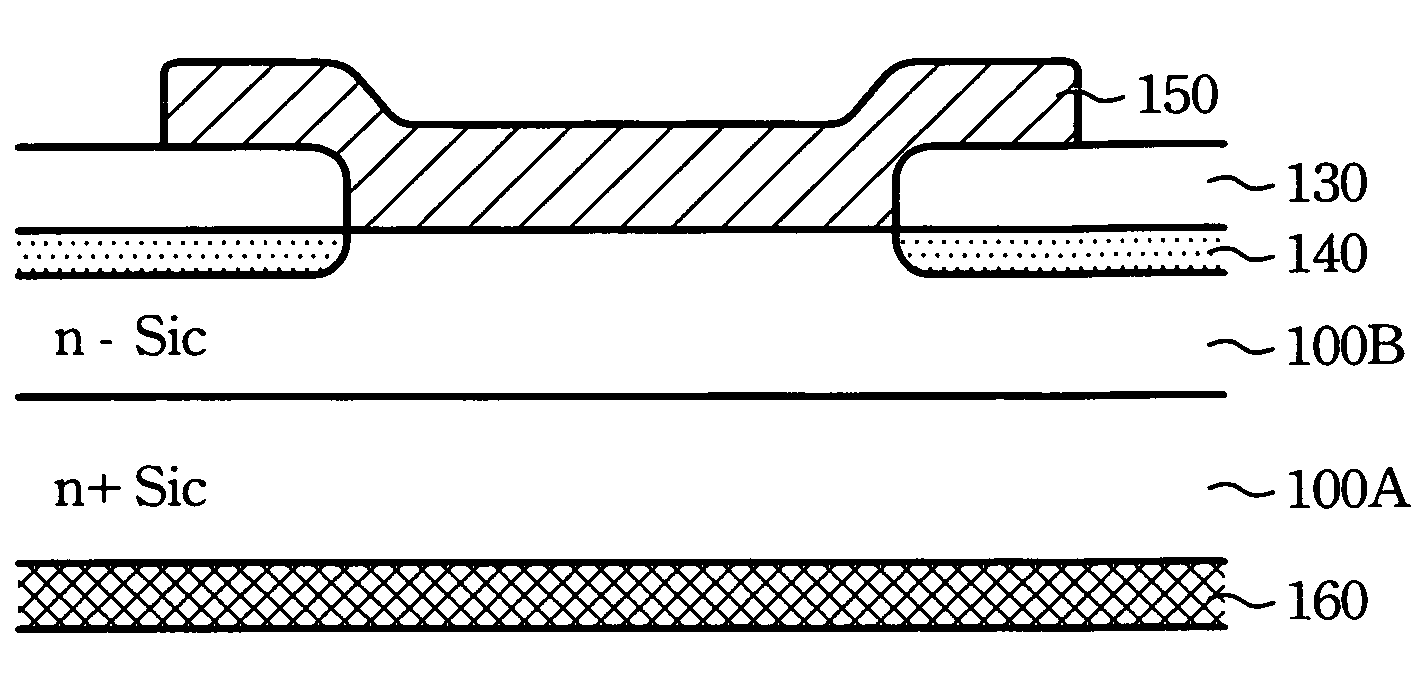

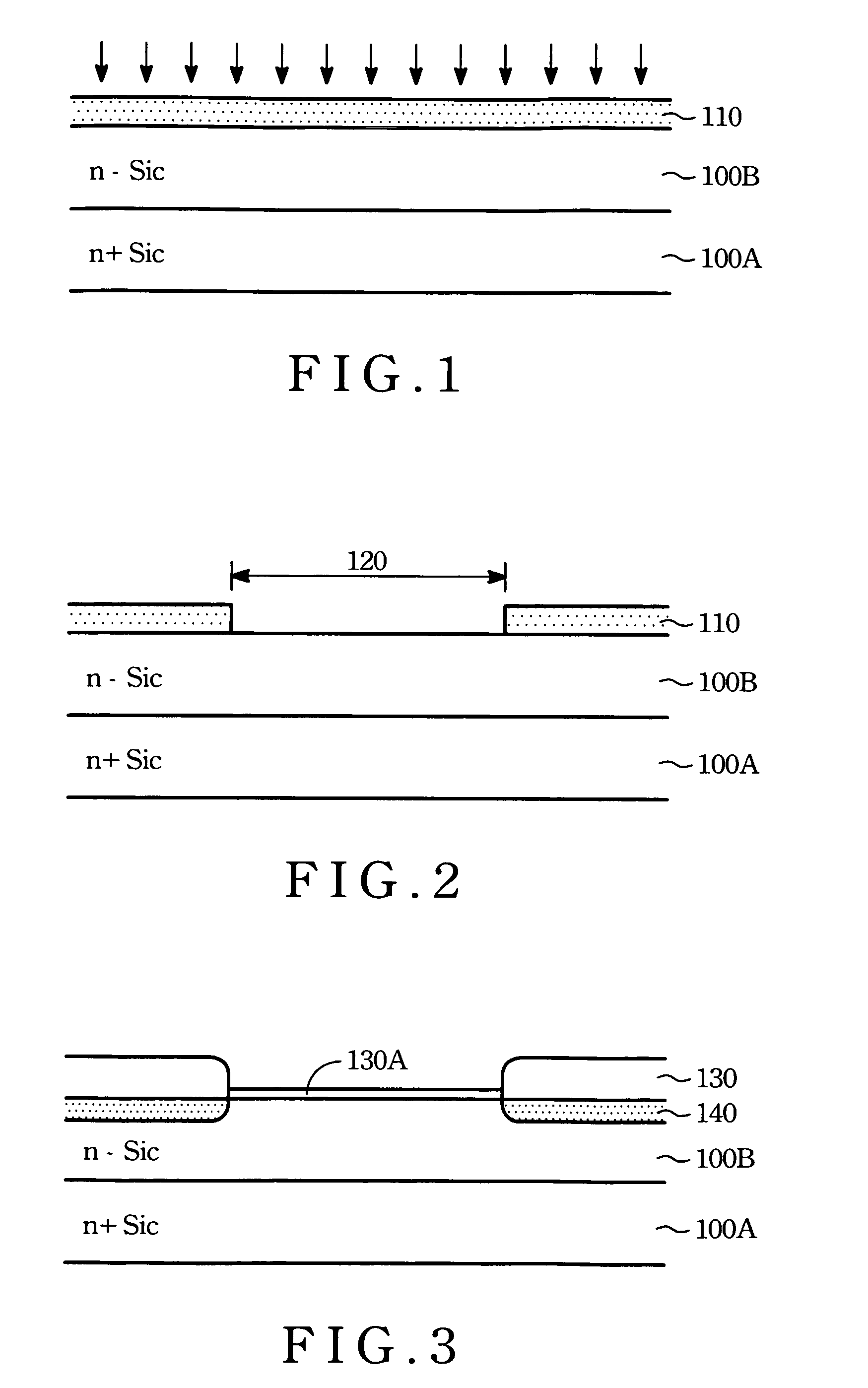

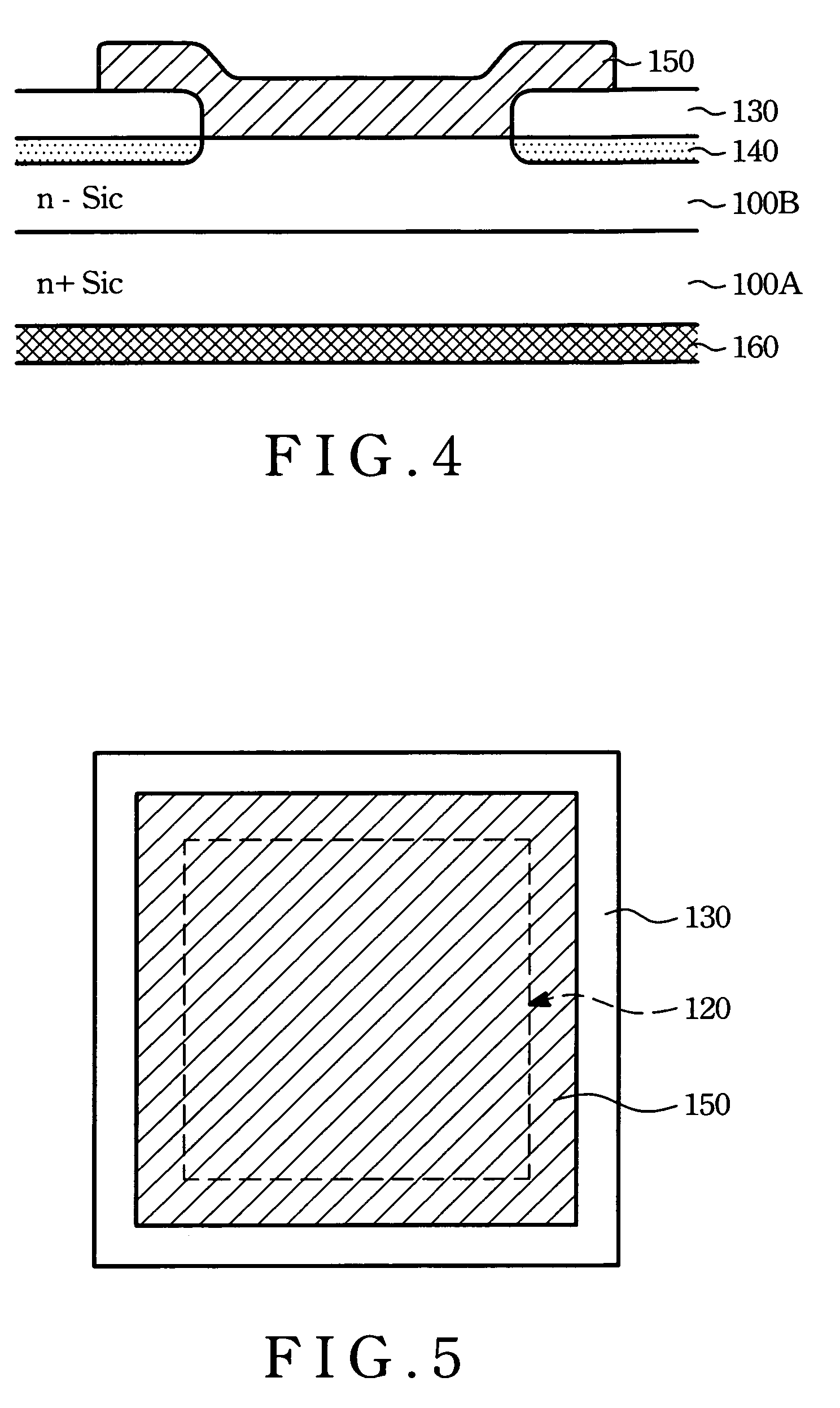

Silicon carbide Schottky diode and method of making the same

ActiveUS7368371B2Semiconductor/solid-state device manufacturingSemiconductor devicesThin oxideLayer removal

A method of forming silicon carbide Schottky diode is disclosed. The processes required two photo-masks only. The processes are as follows: firstly, an n+-silicon carbide substrate having an n− silicon carbide drift layer is provided. Then a silicon layer is formed on the drift layer. An ion implant is carried out to dope the silicon layer. Afterward the doped silicon layer is patterned to define an active region. A thermal oxidation is then followed to form a thick oxide layer by oxidizing the silicon layer and form guard rings by using the doped silicon layer as a diffused source. The thin oxide layer on the drift layer is then removed by dilute HF dip or by BOE (buffer oxide etching) solution dip. Thereafter, a top metal layer is deposited and patterned to define as anode. After a backside layer removal, a metal layer served as cathode is formed.

Owner:CHIP INTEGRATION TECH

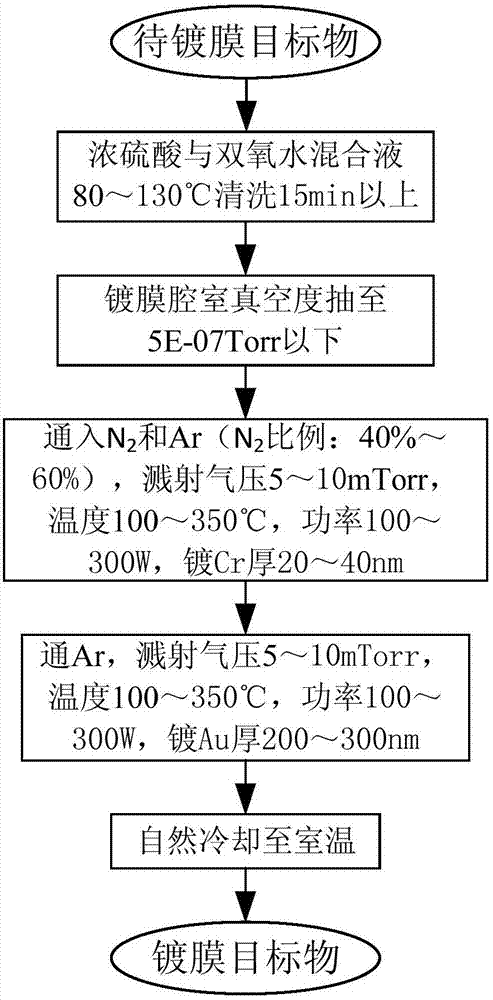

Preparation method of BOE (Buffered Oxide Etch)-resistant metal mask

ActiveCN107299318AEfficient removalImprove adhesionVacuum evaporation coatingSputtering coatingQuartzMaterials science

The invention relates to a preparation method of a BOE (Buffered Oxide Etch)-resistant metal mask, in particular to a preparation method of plating a BOE resistant metal mask layer on a quartz crystal. The method specifically comprises a washing step and a coating step. The method has the following obvious effects: (1) a BOE resisting process is performed with a single Cr / Au mask layer; (2) problems such as surface undercutting, swelling and even falling off after the etching of an existing Cr / Au mask layer are solved; (3) a transfer etching pattern of the single Cr / Au mask layer is high in accuracy, and the accuracy can be controlled to be within 1 microns; and (4) the preparation processes are simple and easily controlled, the preparation cost is low, and mass production can be carried out.

Owner:BEIJING INST OF AEROSPACE CONTROL DEVICES

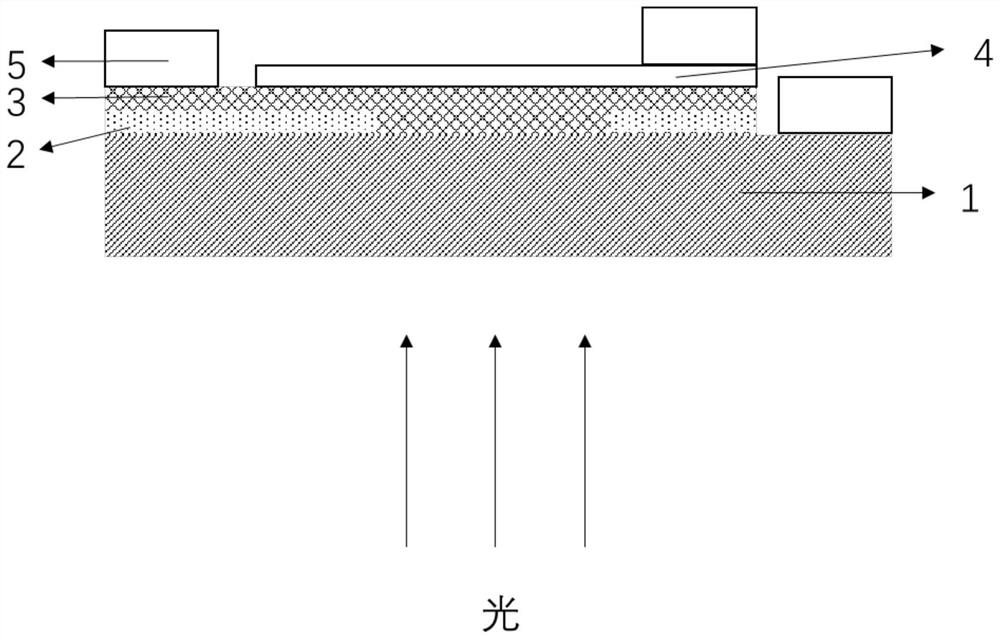

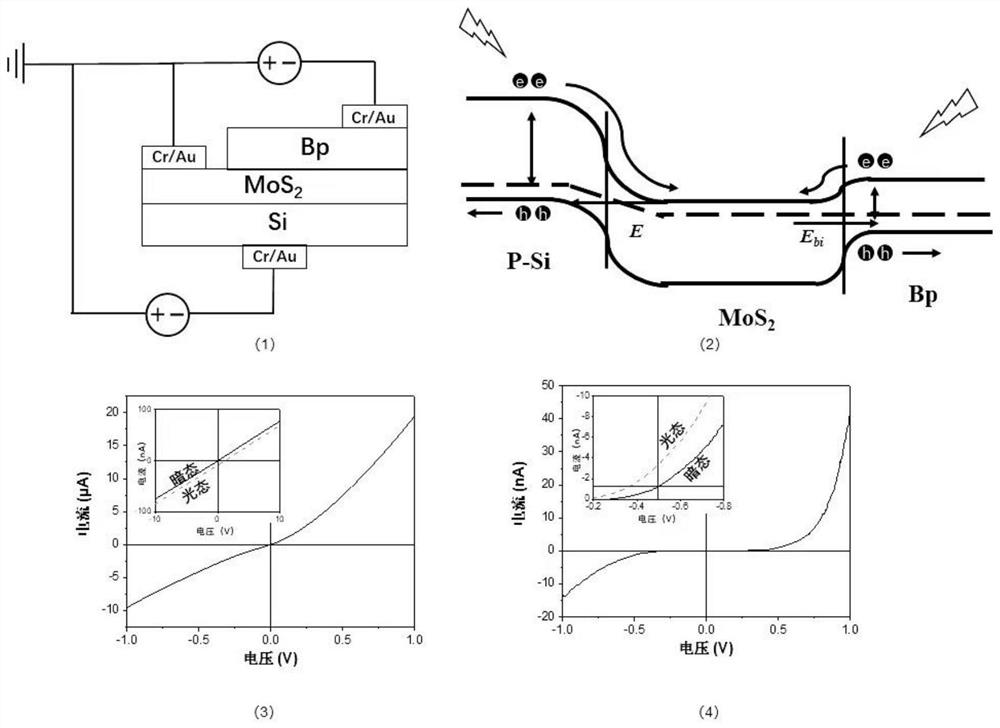

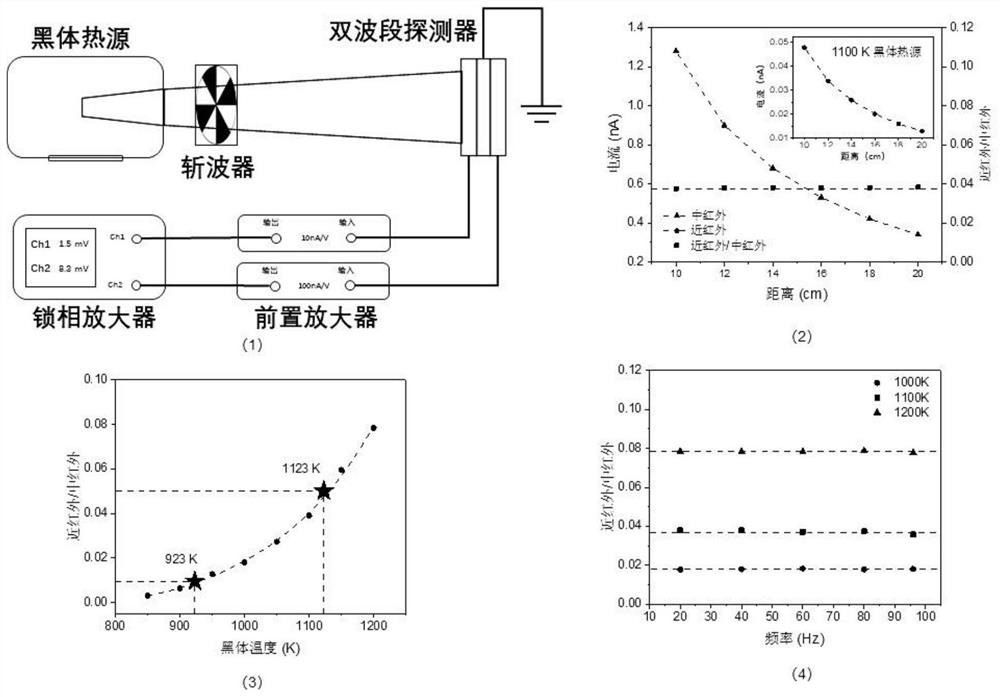

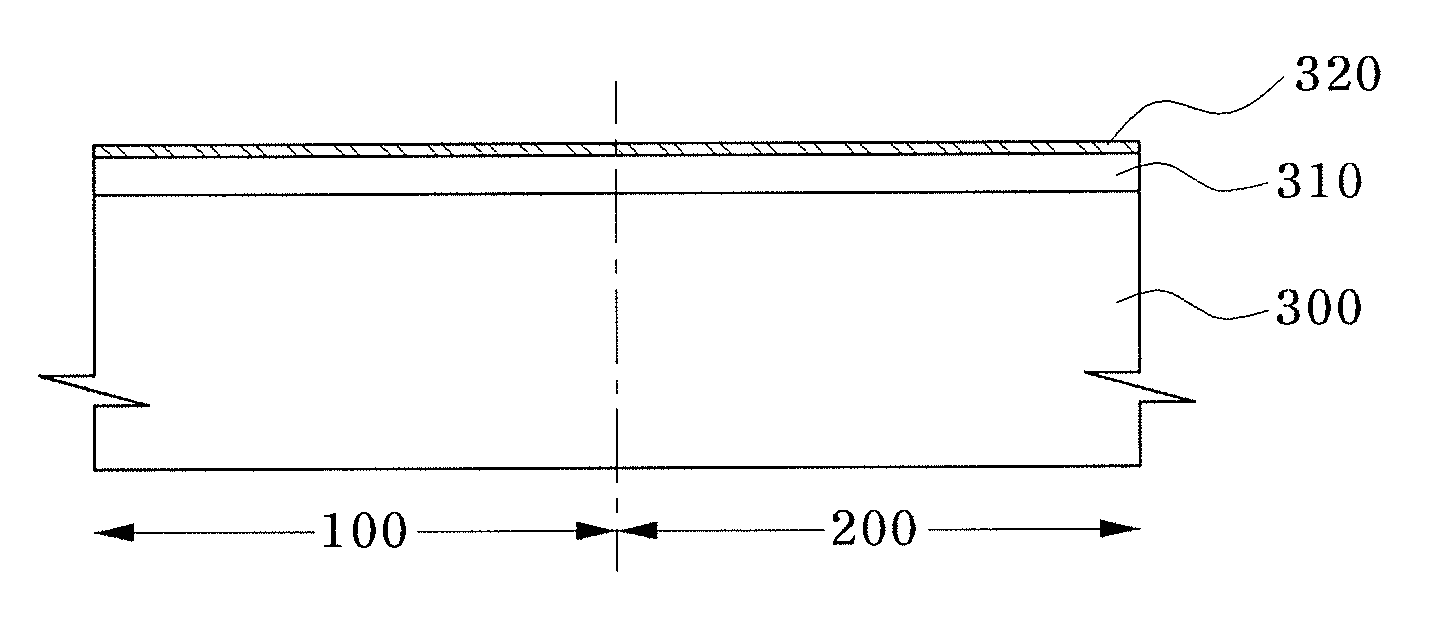

Mixed-dimension Van der Waals heterojunction room temperature two-color infrared detector and preparation method thereof

PendingCN113823702AReduce Optical CrosstalkAccurate temperature identificationFinal product manufacturePyrometry using electric radation detectorsHeterojunctionFilm material

The invention discloses a mixed-dimension Van der Waals heterojunction room temperature two-color infrared detector and a preparation method thereof. The preparation method of the device comprises the following steps of: etching double-sided polished Si / SiO2 by utilizing buffer oxide etching liquid prepared from hydrofluoric acid and ammonium fluoride in a certain proportion to form a Si window; and forming a PNP (NPN) heterostructure by non-destructively transferring a two-dimensional Van der Waals material heterojunction to the Si window by using a polypropylene carbonate film. Dual-band infrared signal detection is realized by using a photoelectric triode energy band structure, and meanwhile, crosstalk is reduced by using a Si material with high absorbance as a near-infrared photosensitive material and a long-wave-pass filter, so that the dual-band infrared response of the device is improved. The mixed-dimension Van der Waals heterojunction room temperature two-color infrared detector has the advantages that a three-dimensional thin film material and the two-dimensional Van der Waals material are combined, near-infrared / mid-infrared room temperature detection is achieved, the manufacturing cost is low, the process is simple, preparation is easy, the detection rate is high, and the working temperature is high.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

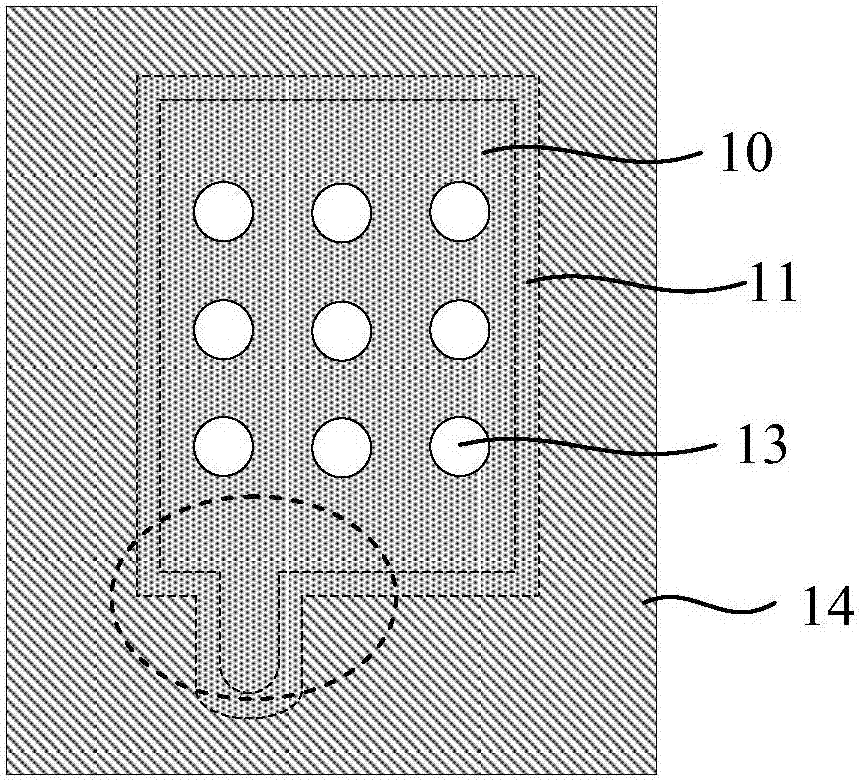

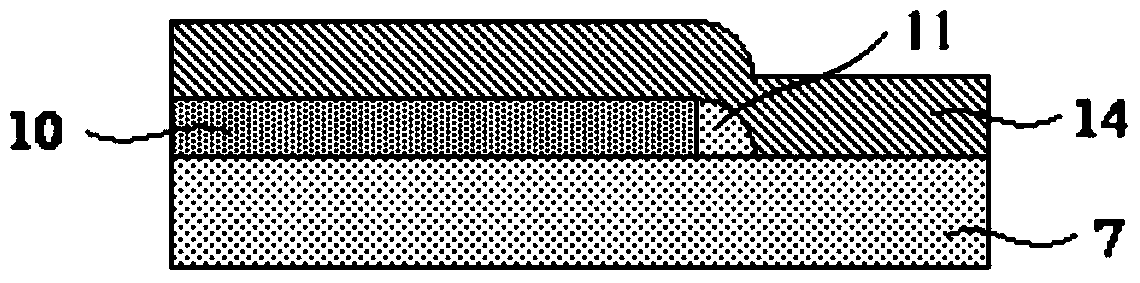

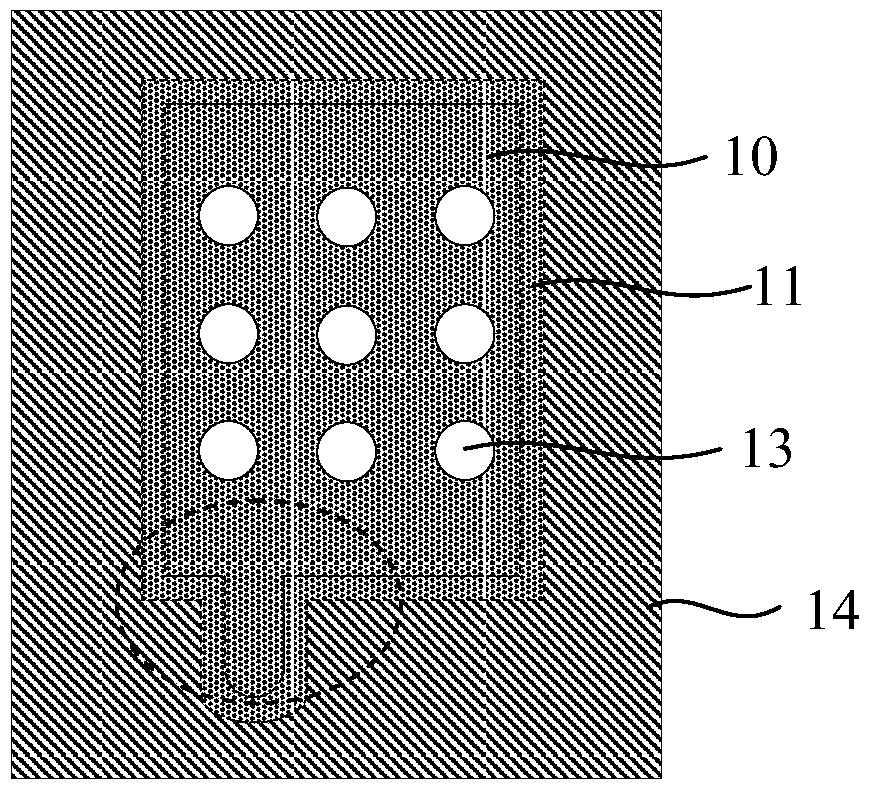

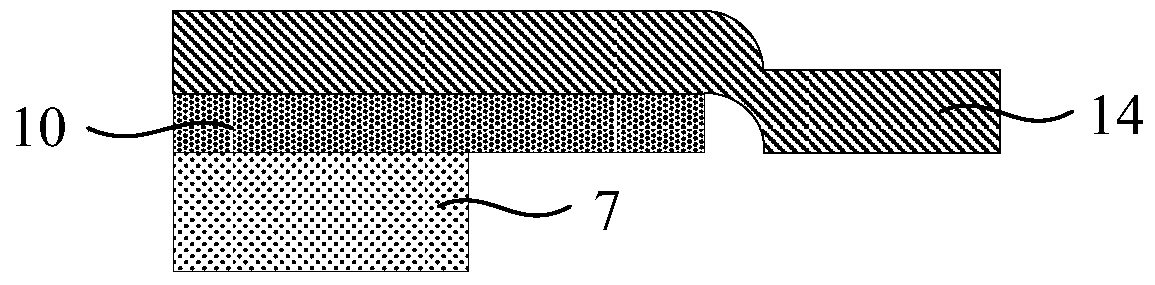

MEMS microphone and production method thereof

ActiveCN107548000APrevent side draw problemImprove APT performanceElectrostatic transducer microphonesCapacitanceMems microphone

The invention provides an MEMS microphone and a production method thereof. The microphone comprises a substrate with a first surface and a second surface opposite to the first surface; a capacitor structure positioned on the first surface of the substrate, wherein the capacitor structure comprises a cavity, fixed electrodes positioned in the cavity, a vibrating diaphragm opposite to the fixed electrodes, sound holes distributed at intervals in the fixed electrodes, and amplitude limiting structures positioned in the sound holes, wherein polycrystalline silicon spacing layers are arranged around the fixed electrode; and a back cavity positioned in the substrate, wherein the top of the back cavity is exposed from the second surface of the substrate, and the capacitor structure is exposed from the bottom of the back cavity. According to the MEMS microphone and the production method thereof provided by the invention, the problem that in the prior art, when oxide spacing layers are used forimproving APT performance, after a final buffer oxide etching technology, a side excavating phenomenon occurs in an area adjacent to the connection end of the fixed electrode due to siphonic effect brought by the oxide spacing layers is solved.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

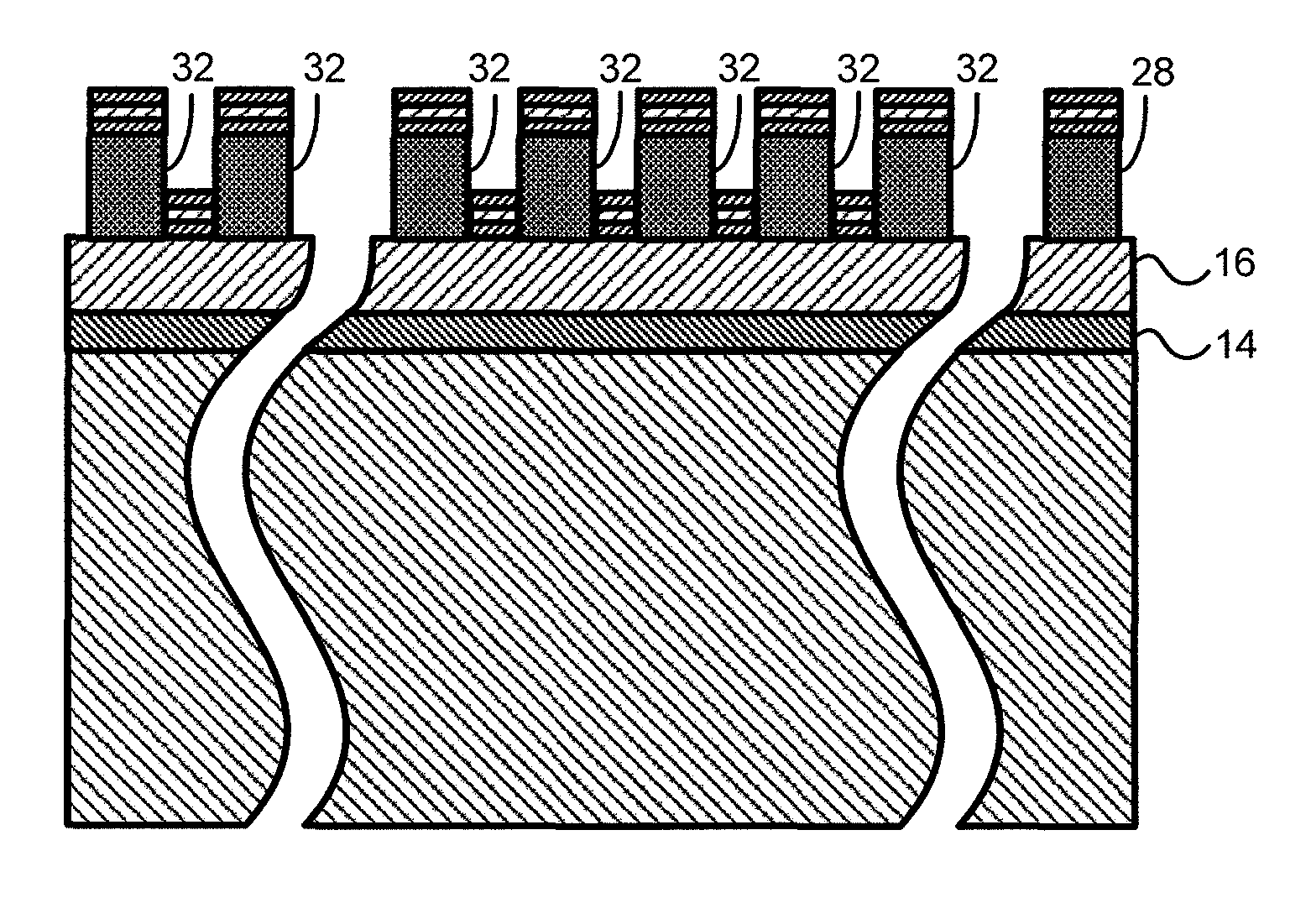

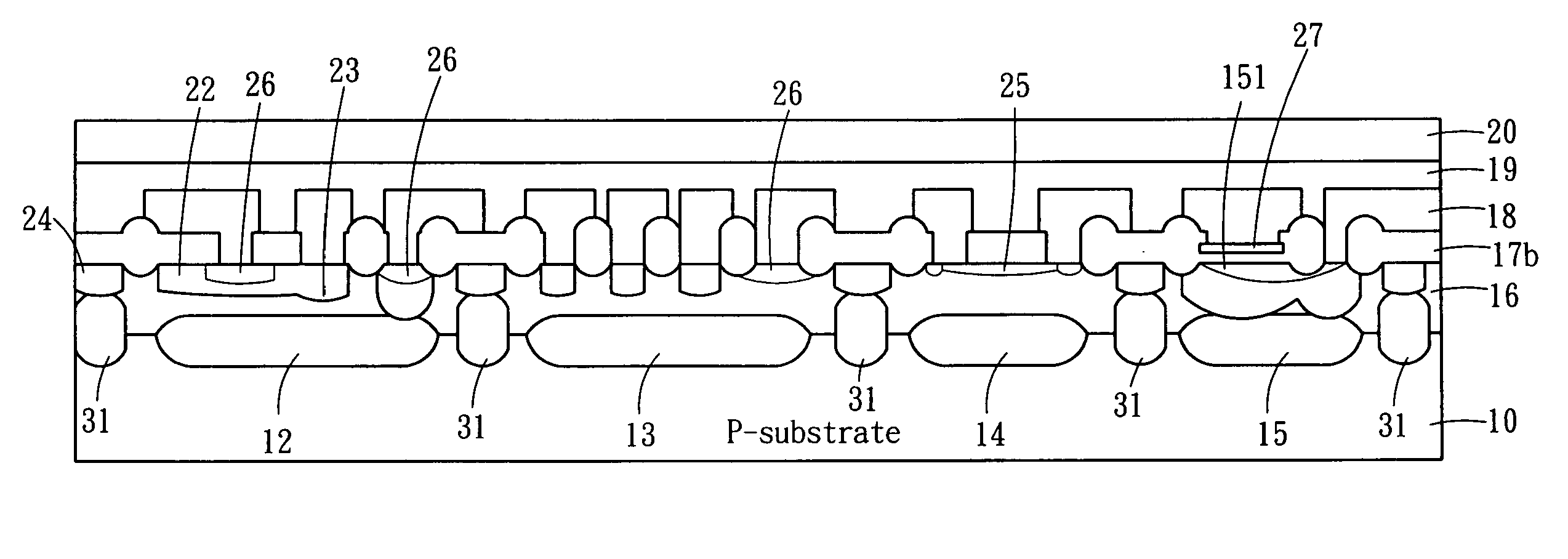

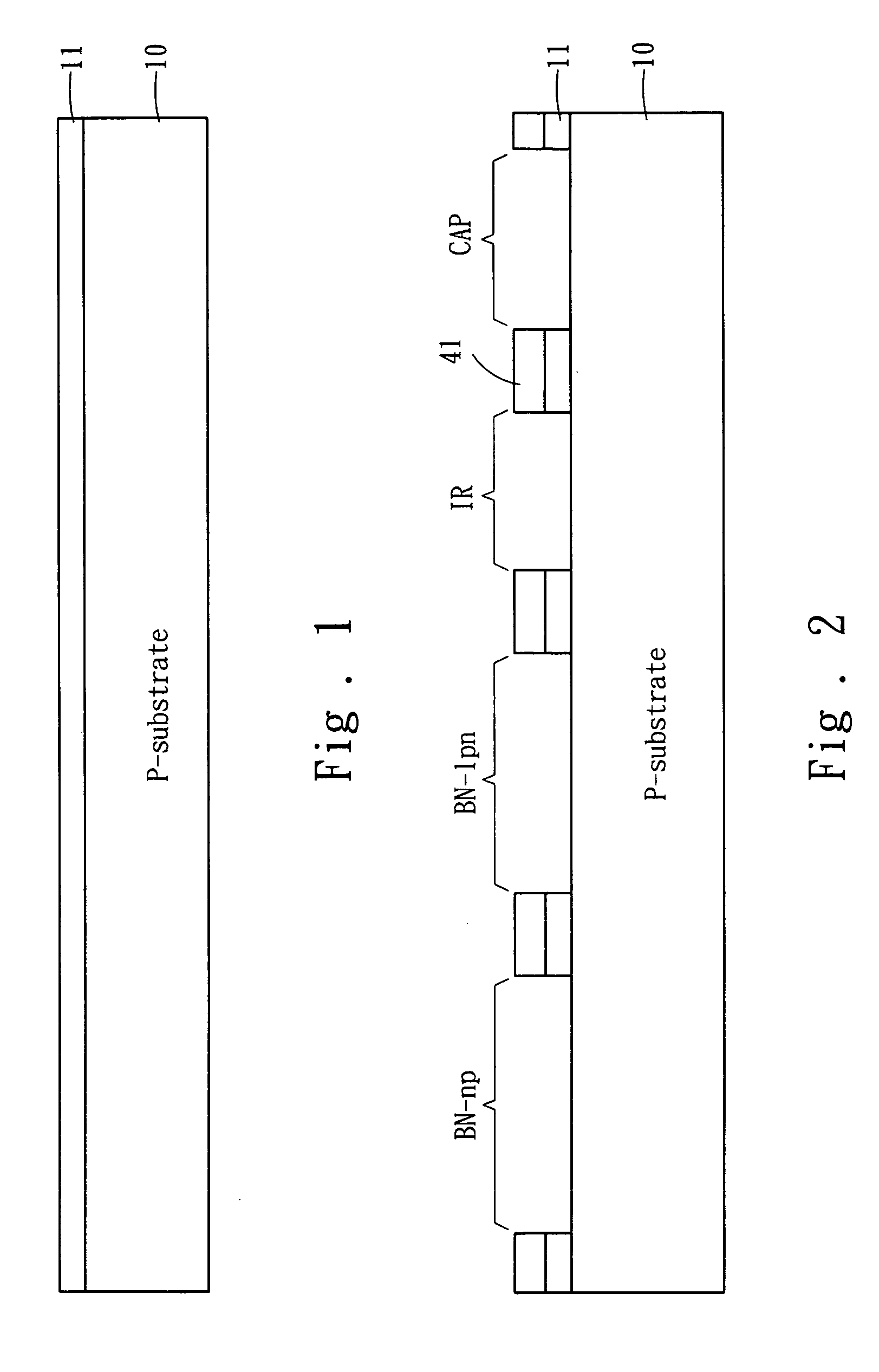

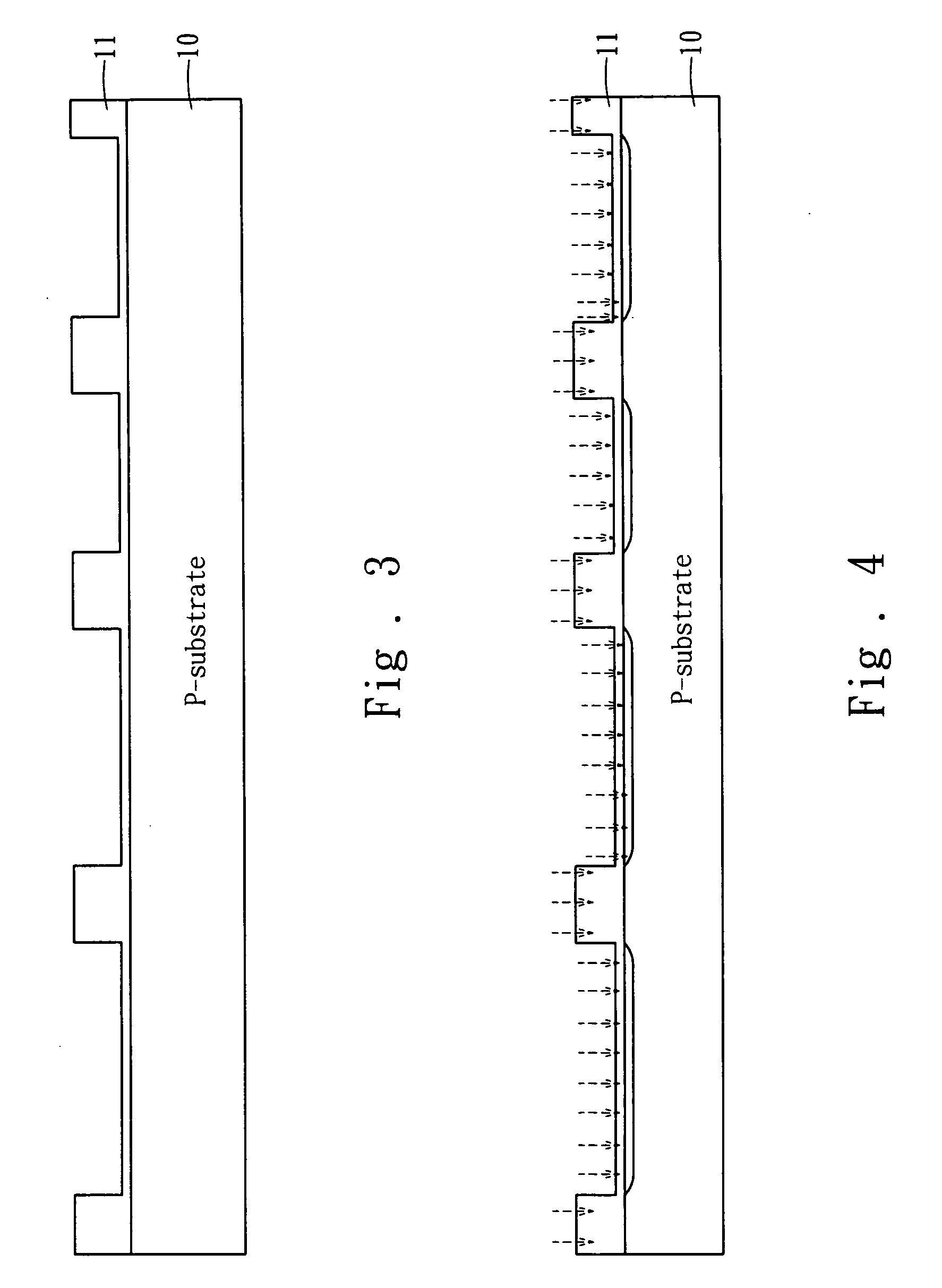

Method for fabricating bipolar integrated circuits

InactiveUS20070173026A1Improve the level of integrationEliminate alignment errorsTransistorSolid-state devicesLOCOSDielectric layer

The present invention discloses a method for fabricating bipolar integrated circuits, wherein LOCOS technology is used to define the active regions needed by all elements so that the self-alignment of the associated layers can be realized, and implant resistor regions are also directly defined in the active regions by local oxide layers; after base regions have been driven in the wafer, the resistors are implanted into the wafer so that the cost of resistor photomasks can be saved; silicon nitride is adopted to be the material of the dielectric layers of the capacitors, and with the characteristic of a buffering oxide etchant that etches oxide faster than it etches silicon nitride, the conventional deposition sequence of the dielectric layer is changed so that the formation of the dielectric layer needs only a single photomask.

Owner:BCD SEMICON MFG

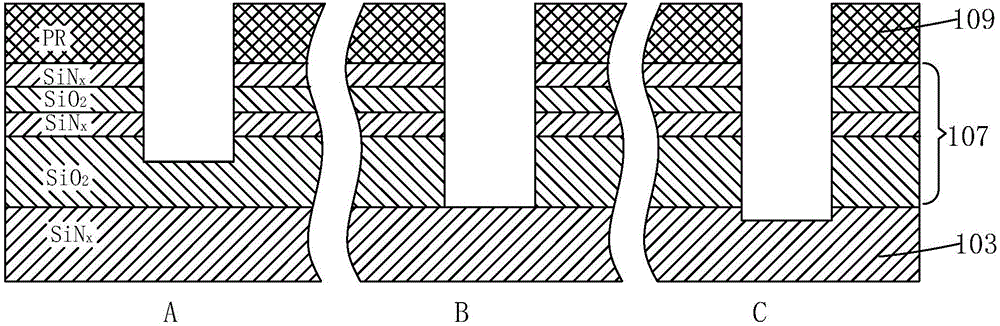

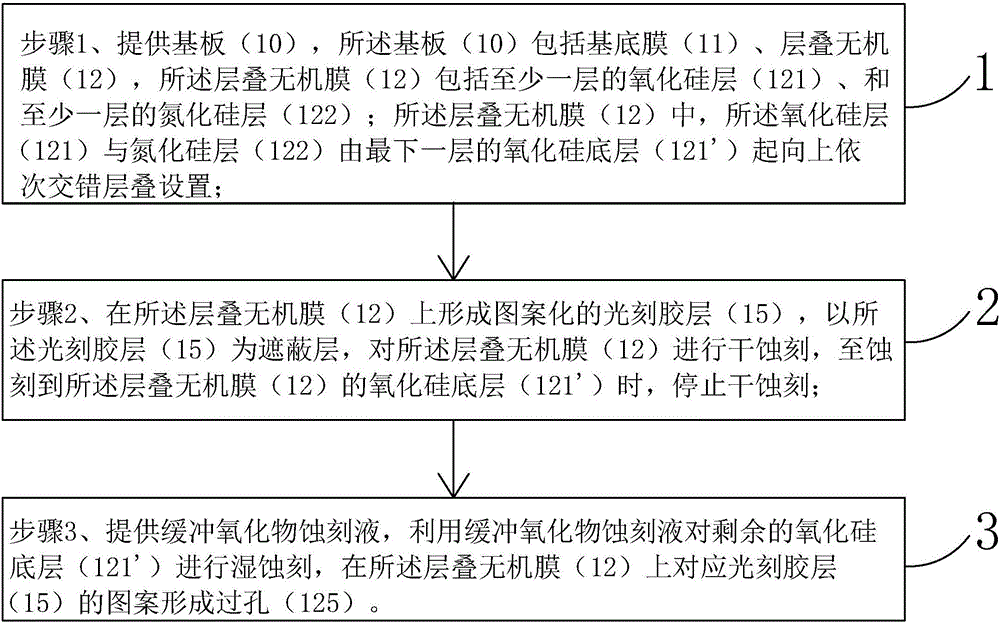

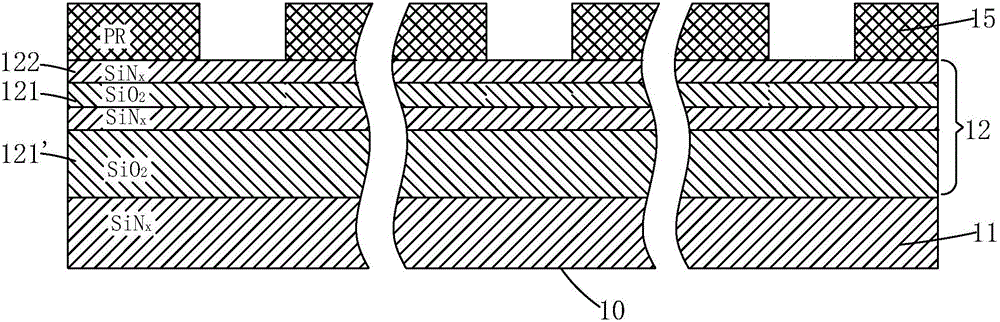

Etching method for laminated inorganic membrane

InactiveCN106548979AImprove uniformityAvoid etching into the underlying filmSolid-state devicesSemiconductor/solid-state device manufacturingSilicon oxidePhotoresist

The invention provides an etching method for a laminated inorganic membrane, which combines dry etching and wet etching for etching of the laminated inorganic membrane. The method comprises the following steps: a patterned photoresist layer is firstly formed on the laminated inorganic membrane, the dry etching of the laminated inorganic membrane is carried out in a manner that the photoresist layer serves as a shielding layer, and the dry etching is stopped when a silicon oxide bottom layer at the bottommost layer of the laminated inorganic membrane is to be etched; and the wet etching is then carried out on the remaining silicon oxide bottom layer through a buffered oxide etch (BOE), so that via holes are formed in the laminated inorganic membrane corresponding to patterns of the photoresist layer. The method provided by the invention has the advantages that the uniformity of etching effects for various areas of a same substrate can be improved, so that the phenomenon in the prior art that a lower membrane is etched due to non-uniform etching of the various areas when the via holes, especially deep via holes, are formed in the laminated inorganic membrane is prevented.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

A kind of mems microphone and its making method

ActiveCN107548000BPrevent side draw problemImprove APT performanceElectrostatic transducer microphonesCapacitanceEngineering

The invention provides an MEMS microphone and a production method thereof. The microphone comprises a substrate with a first surface and a second surface opposite to the first surface; a capacitor structure positioned on the first surface of the substrate, wherein the capacitor structure comprises a cavity, fixed electrodes positioned in the cavity, a vibrating diaphragm opposite to the fixed electrodes, sound holes distributed at intervals in the fixed electrodes, and amplitude limiting structures positioned in the sound holes, wherein polycrystalline silicon spacing layers are arranged around the fixed electrode; and a back cavity positioned in the substrate, wherein the top of the back cavity is exposed from the second surface of the substrate, and the capacitor structure is exposed from the bottom of the back cavity. According to the MEMS microphone and the production method thereof provided by the invention, the problem that in the prior art, when oxide spacing layers are used forimproving APT performance, after a final buffer oxide etching technology, a side excavating phenomenon occurs in an area adjacent to the connection end of the fixed electrode due to siphonic effect brought by the oxide spacing layers is solved.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

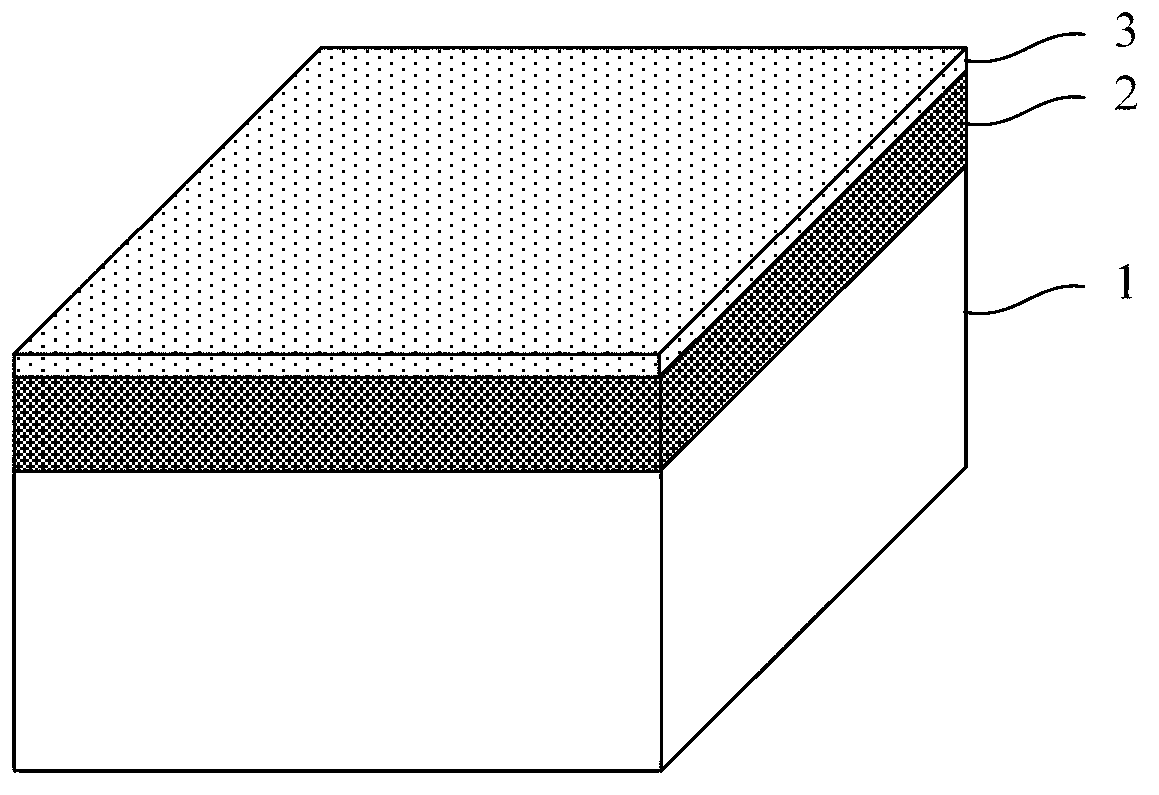

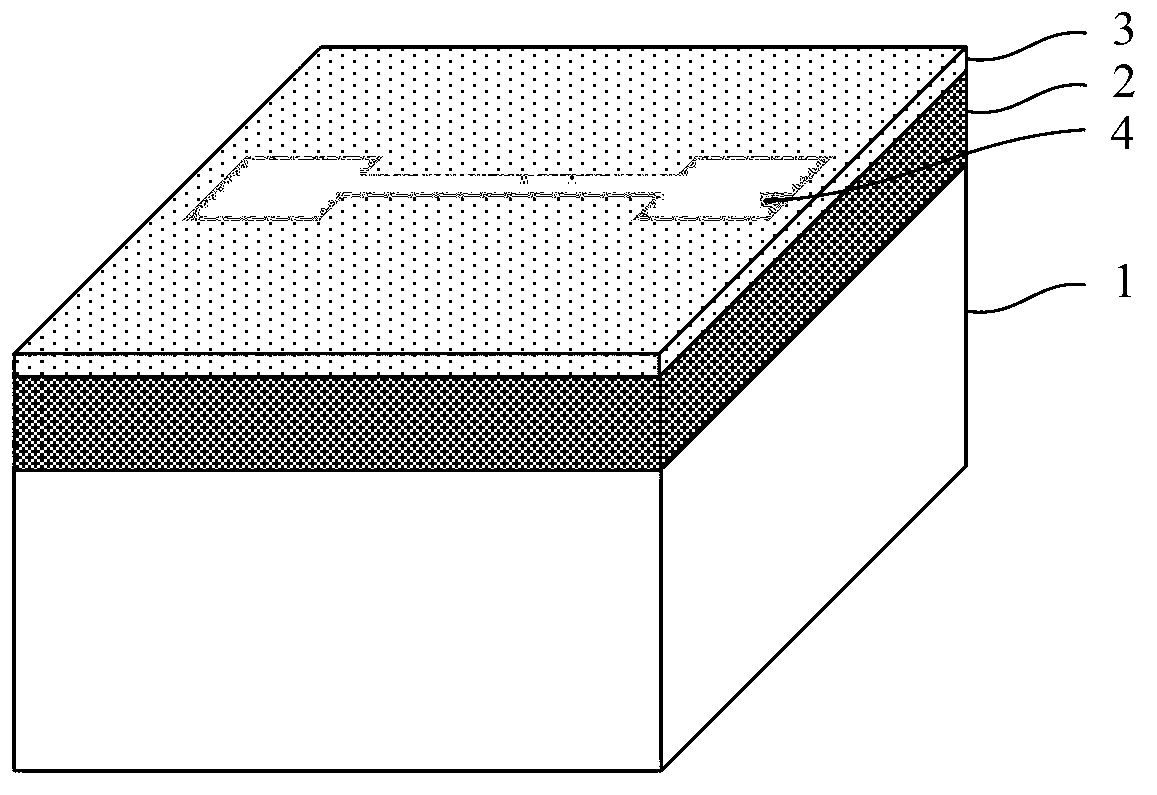

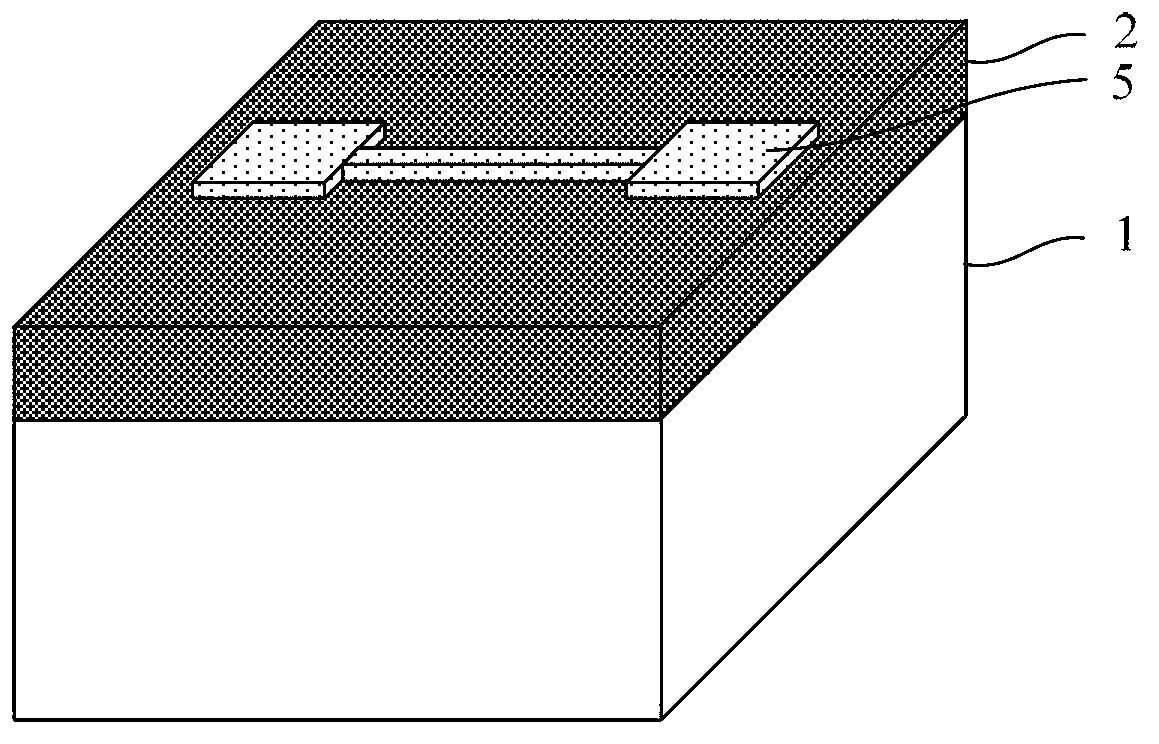

Conformal microstructure transfer method

ActiveCN103021818AReduce complexityConformal Transfer RealizationSemiconductor/solid-state device manufacturingHydrofluoric acidPhysical chemistry

The invention provides a conformal microstructure transfer method. The method at least includes: providing an XOI (X on insulator) substrate comprising bottom silicon, an buried oxide layer and a top X nano-film sequentially from top to bottom, coating the top X nano-film with dumbbell-shaped photoresist used as a mask, and etching to obtain a dumbbell-shaped microstructure; corroding the buried oxide layer by hydrofluoric acid solution or BOE (buffer oxide etch) solution until a middle patterned microbelt part of the microstructure is totally suspended in air and part of the buried oxide layer not completely corroded below two end areas of the microstructure remains, and forming fixed junctions; and providing a base plate to contact with the microstructure, and quickly lifting the base plate to transfer the microstructure to the base plate. The microstructure nano-film is fixed according to the simple design of graph fixation by ends, full conformal transfer is achieved, complexity in conformal transfer process is lowered greatly, and process cost is lowered.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

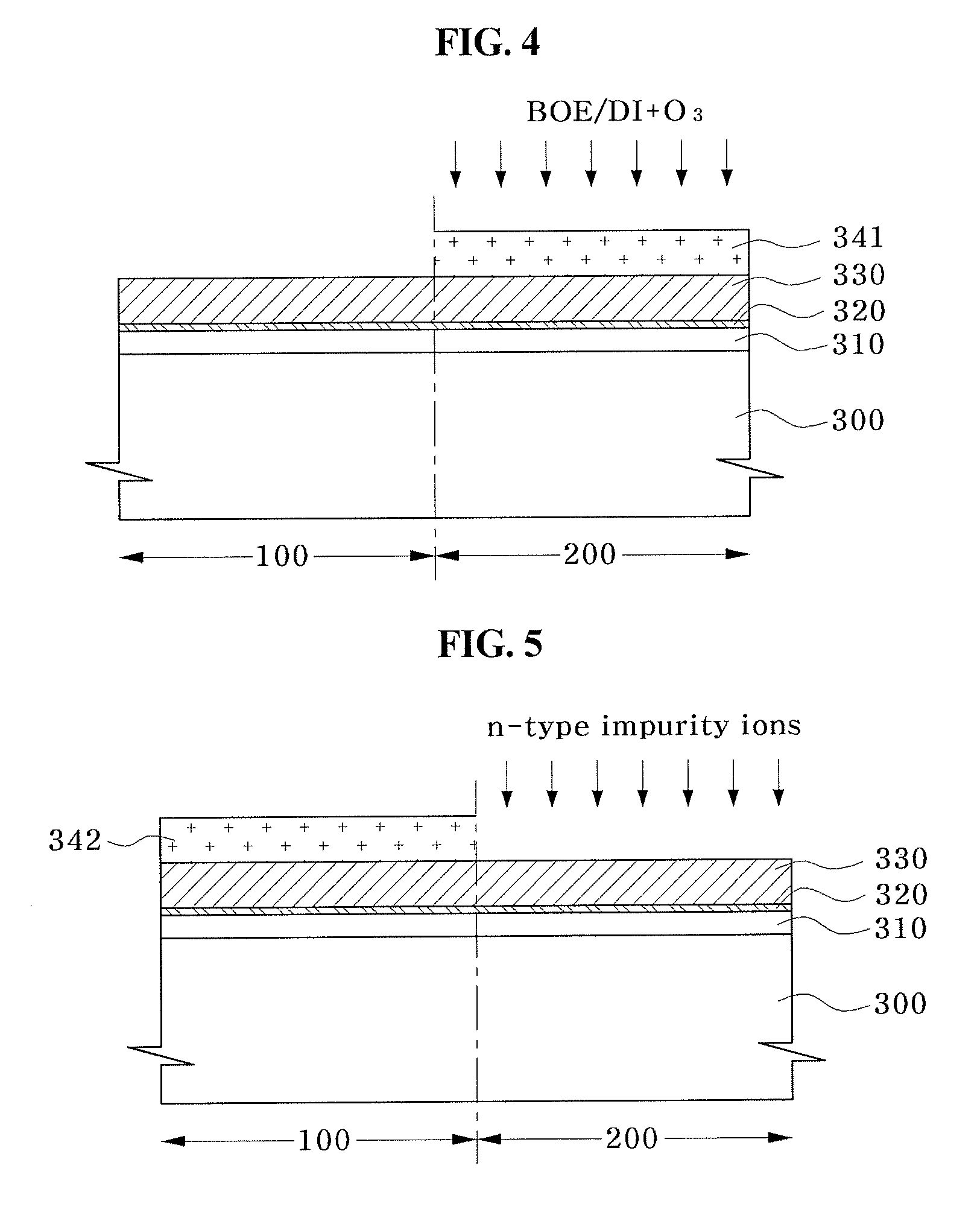

Methods of forming dual gate of semiconductor device

InactiveUS20110212611A1Semiconductor/solid-state device manufacturingPower semiconductor deviceImpurity ions

Disclosed herein is a method for forming a dual gate of a semiconductor device. The method comprises the steps of forming a first polysilicon layer doped with p-type impurity ions and a second polysilicon layer doped with n-type impurity ions on a first region and a second region of a semiconductor substrate, respectively, and sequentially subjecting the surfaces of the first and second polysilicon layers to wet cleaning, drying, and dry cleaning. The wet cleaning is performed by using a sulfuric acid peroxide mixture (SPM), a buffered oxide etchant (BOE), and Standard Clean-1 (SC-1) as cleaning solutions.

Owner:SK HYNIX INC