Gate-oxide etching method and multi-grid-electrode manufacturing method

A multi-gate and gate oxide technology, applied in the field of process technology and gate oxide layer etching, can solve serious problems such as image device quality, large particle defects, poly layer snowball effect, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

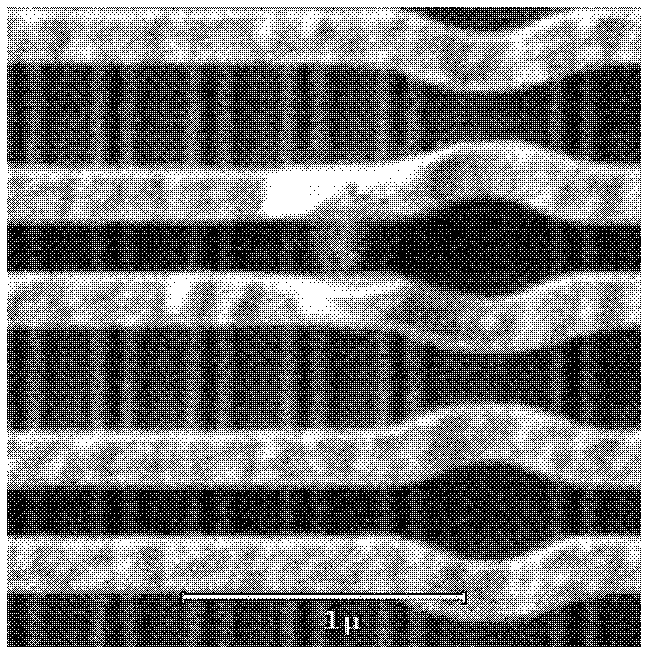

[0042] As mentioned in the background technology, in the fabrication of multi-gate process, due to the need to etch the previous gate oxide layer, and the current etching method is easy to introduce residue defects or large particle defects, resulting in multi-gate device performance is affected.

[0043] In view of this, an etching method for the gate oxide proposed by the present invention can reduce the damage to the substrate surface under the condition of completely etching the gate oxide, thereby reducing the generation of particle defects and making the multi-gate The quality of the pole workmanship has been improved.

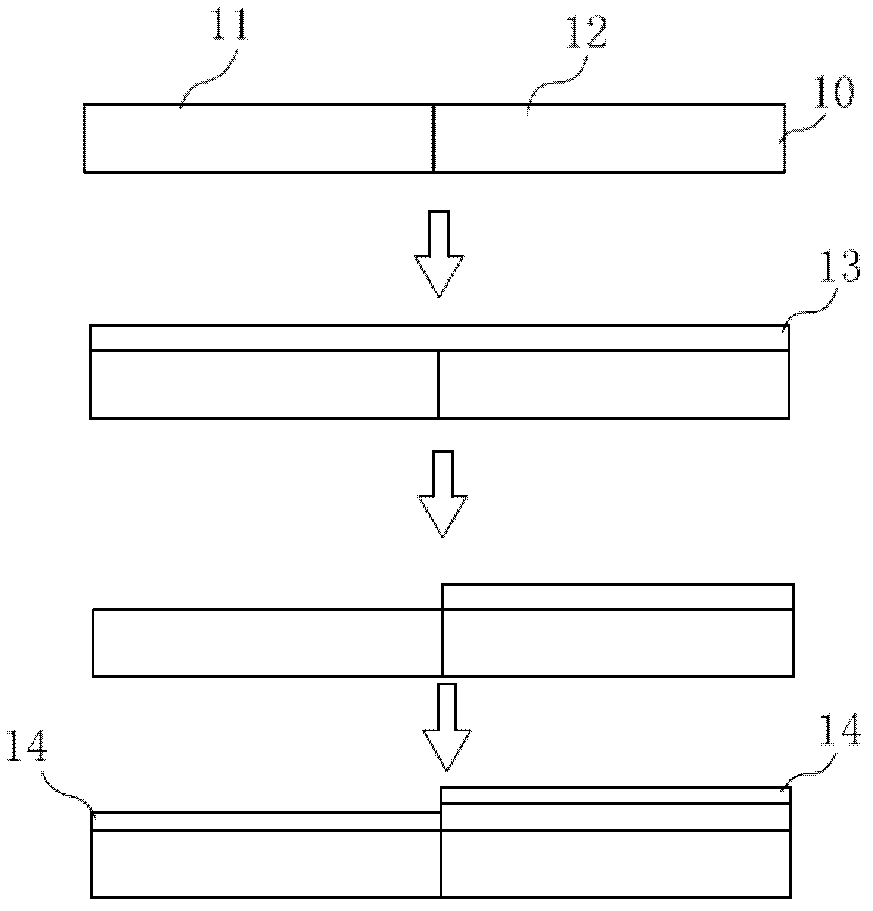

[0044] The gate oxide etching method of the present invention will be described in detail below. It should be noted that the gate oxide layer etched by the etching method of the present invention refers to the pre-sequence gate oxide layer used in the multi-gate process. The purpose of etching is to pattern the gate oxide layer so that the surface of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More