Patents

Literature

193 results about "Multi grid" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

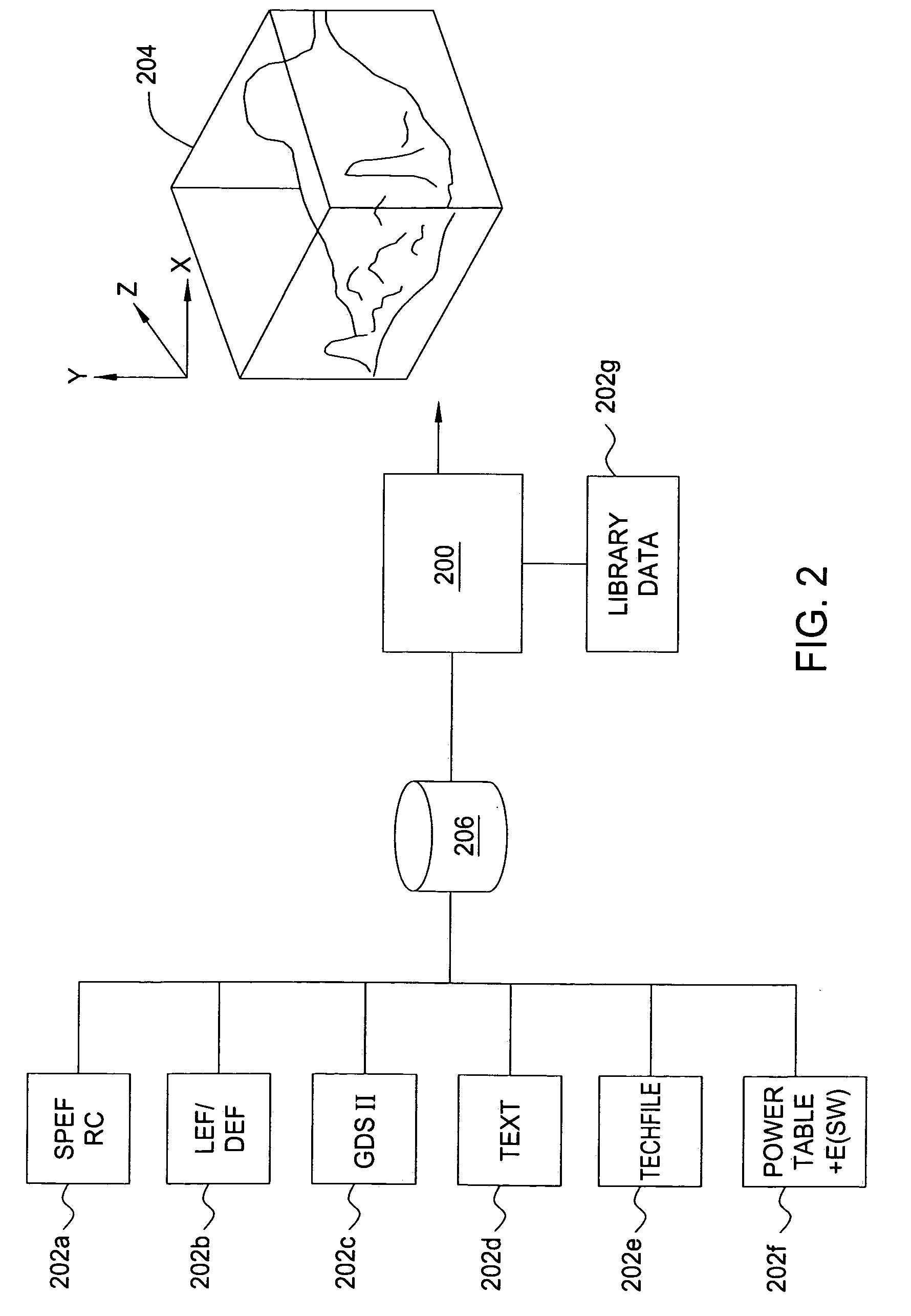

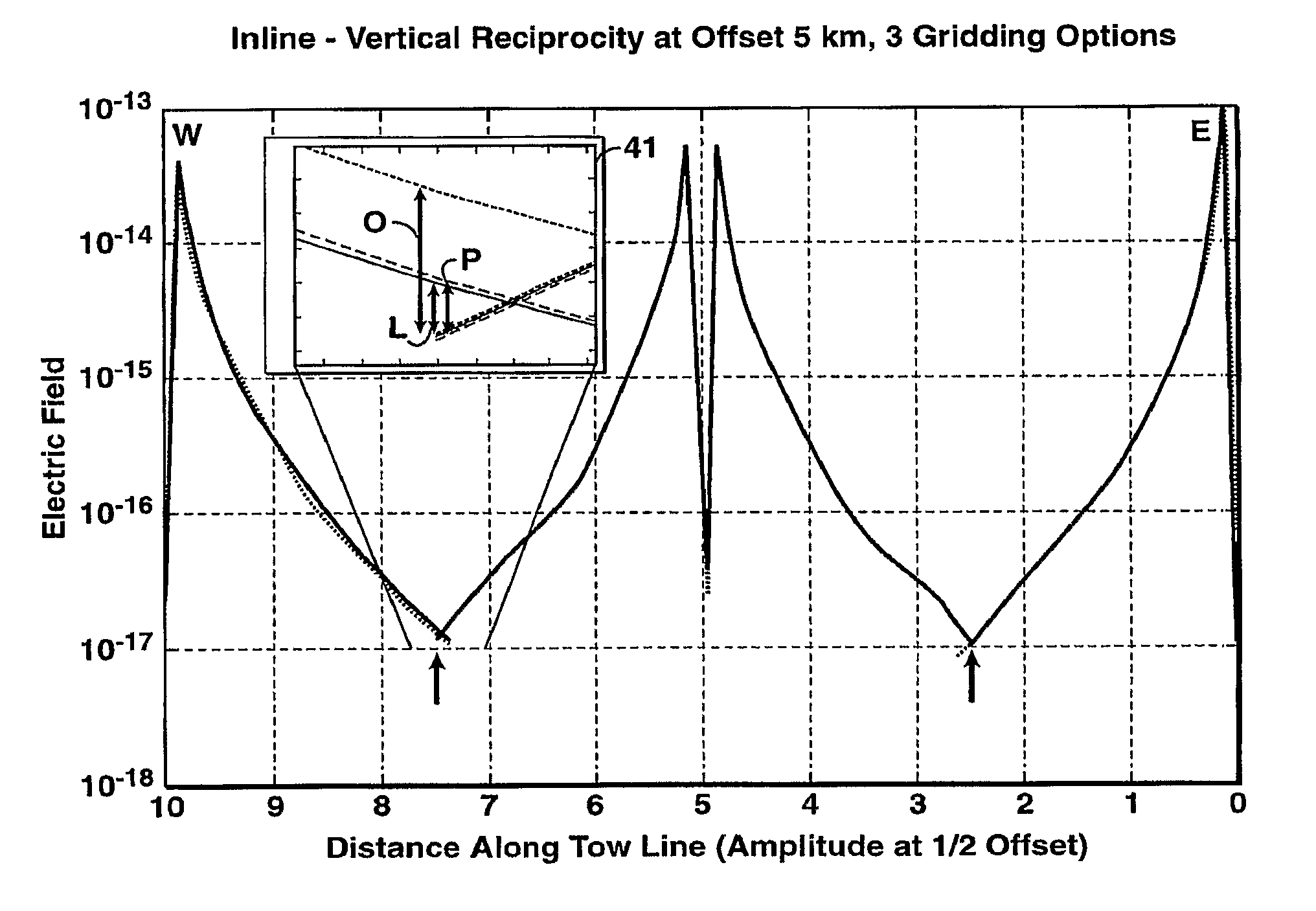

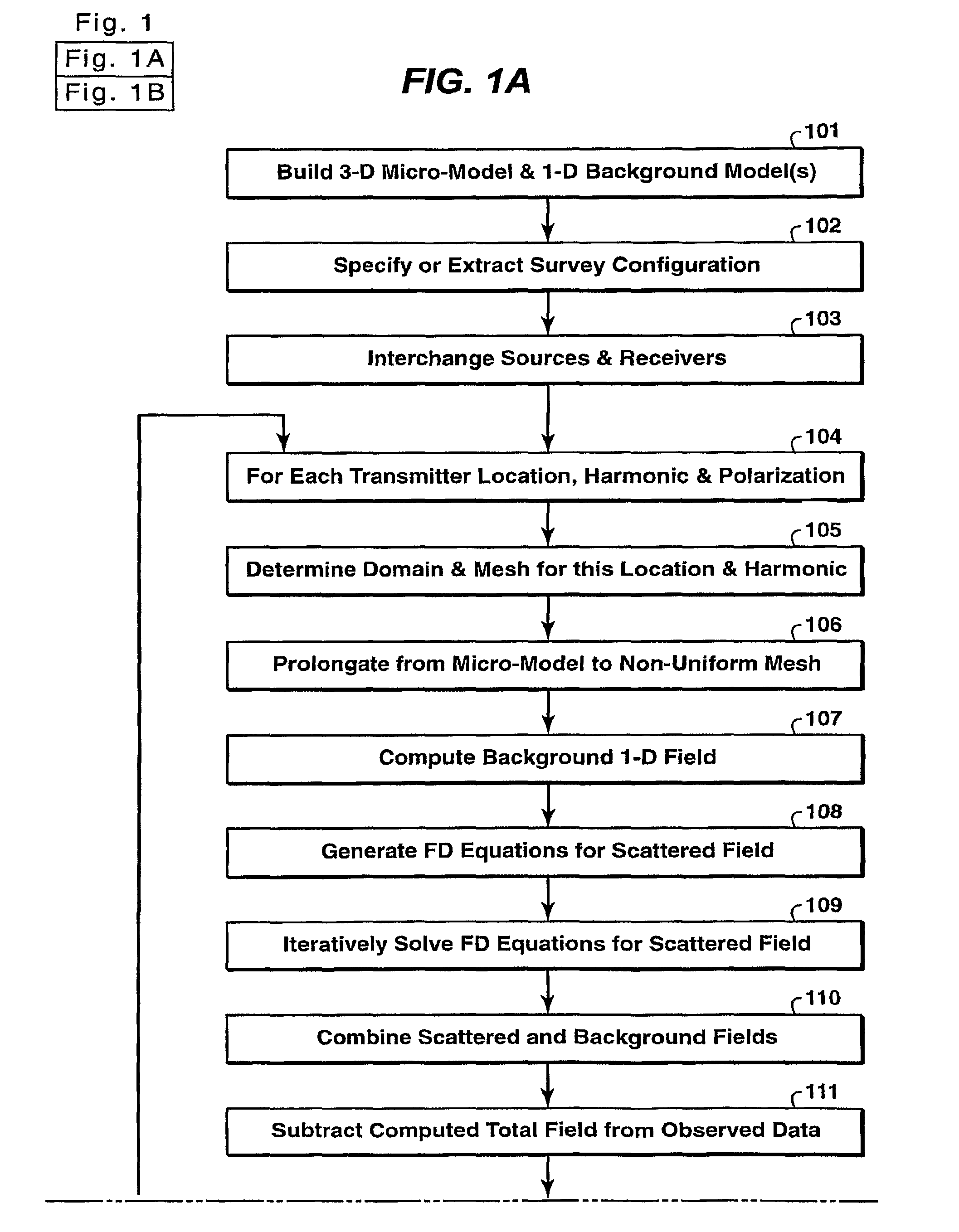

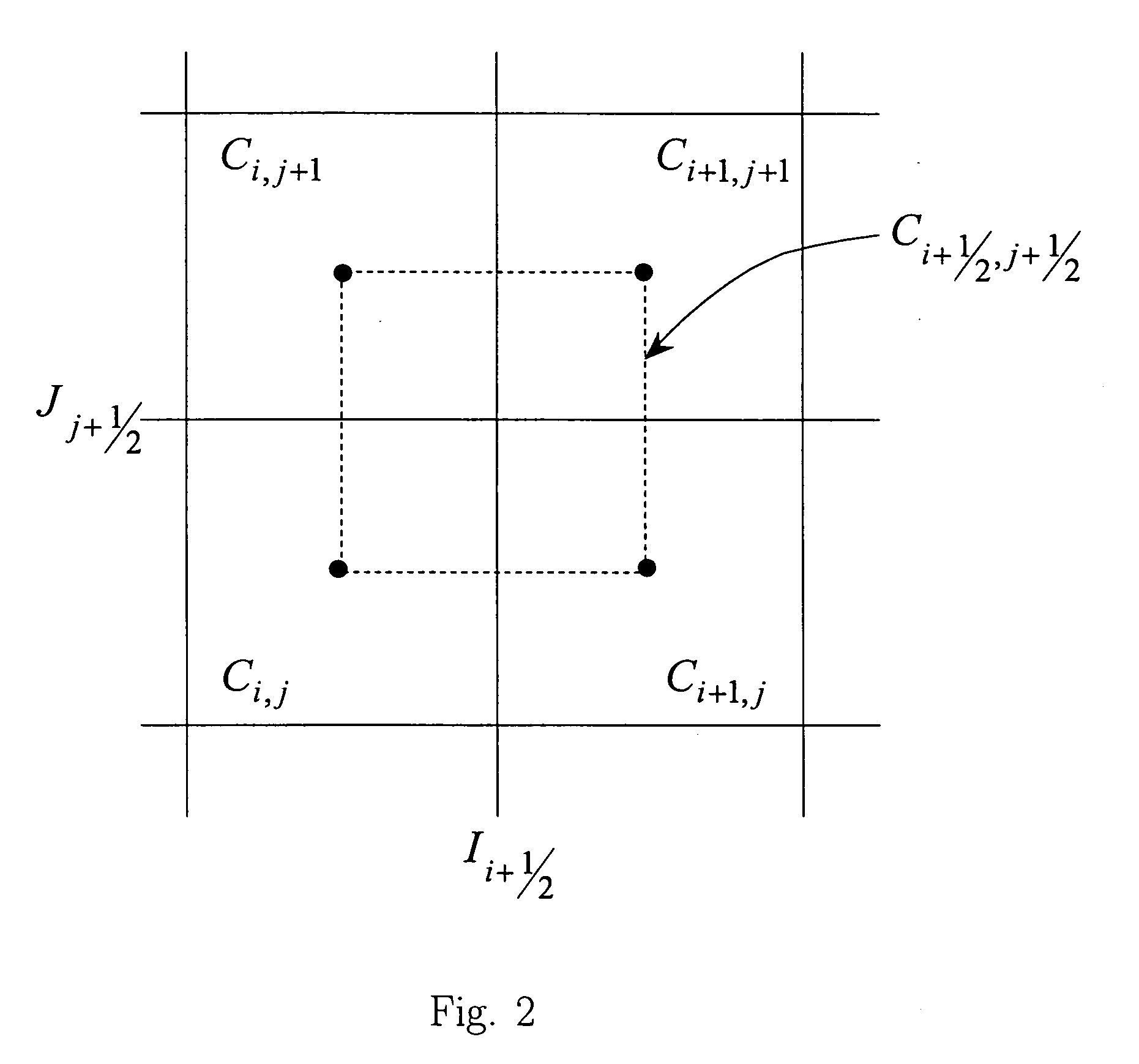

Efficient Computation Method for Electromagnetic Modeling

ActiveUS20090006053A1InsulationFluid removalControlled source electro-magneticElectromagnetic shielding

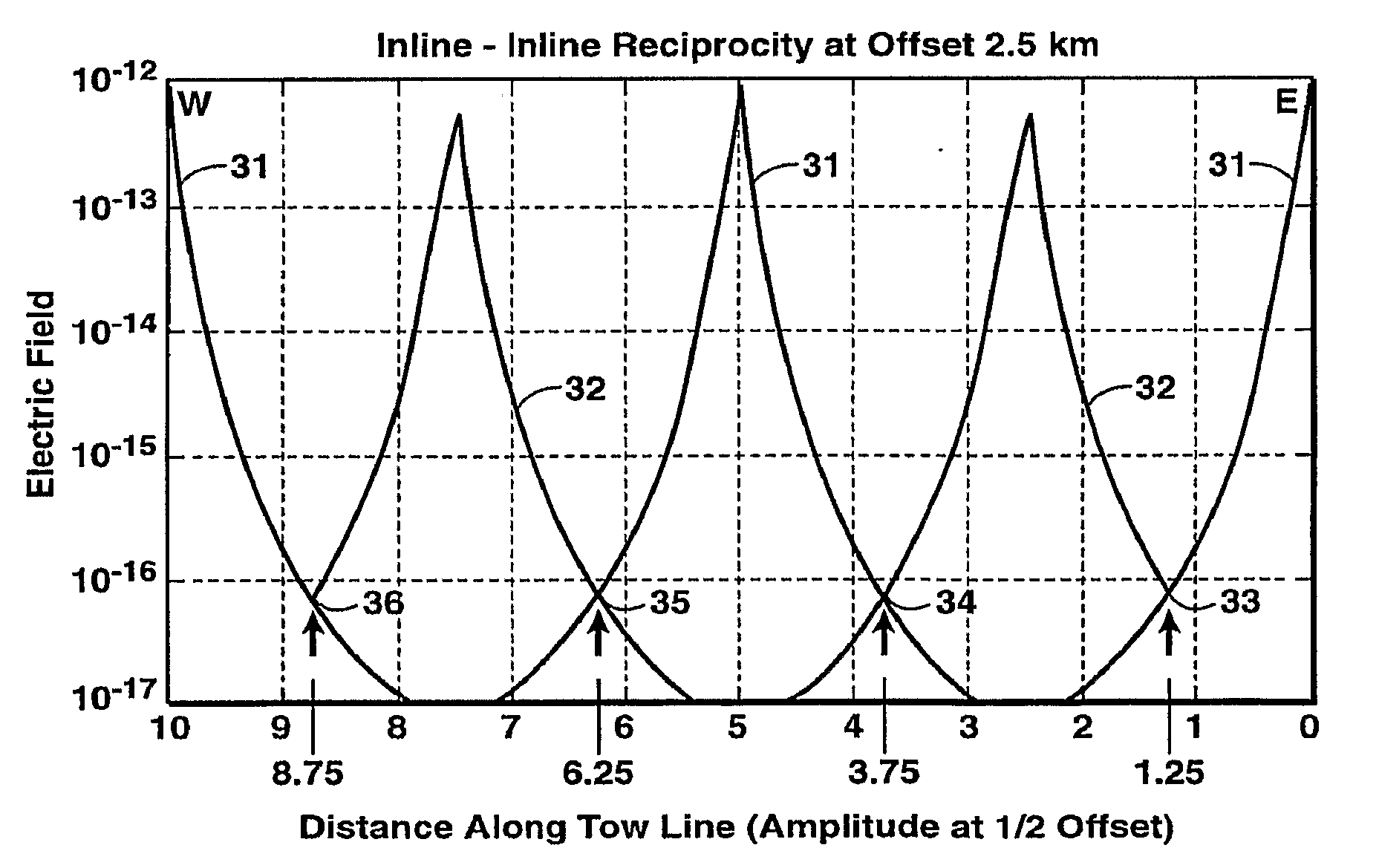

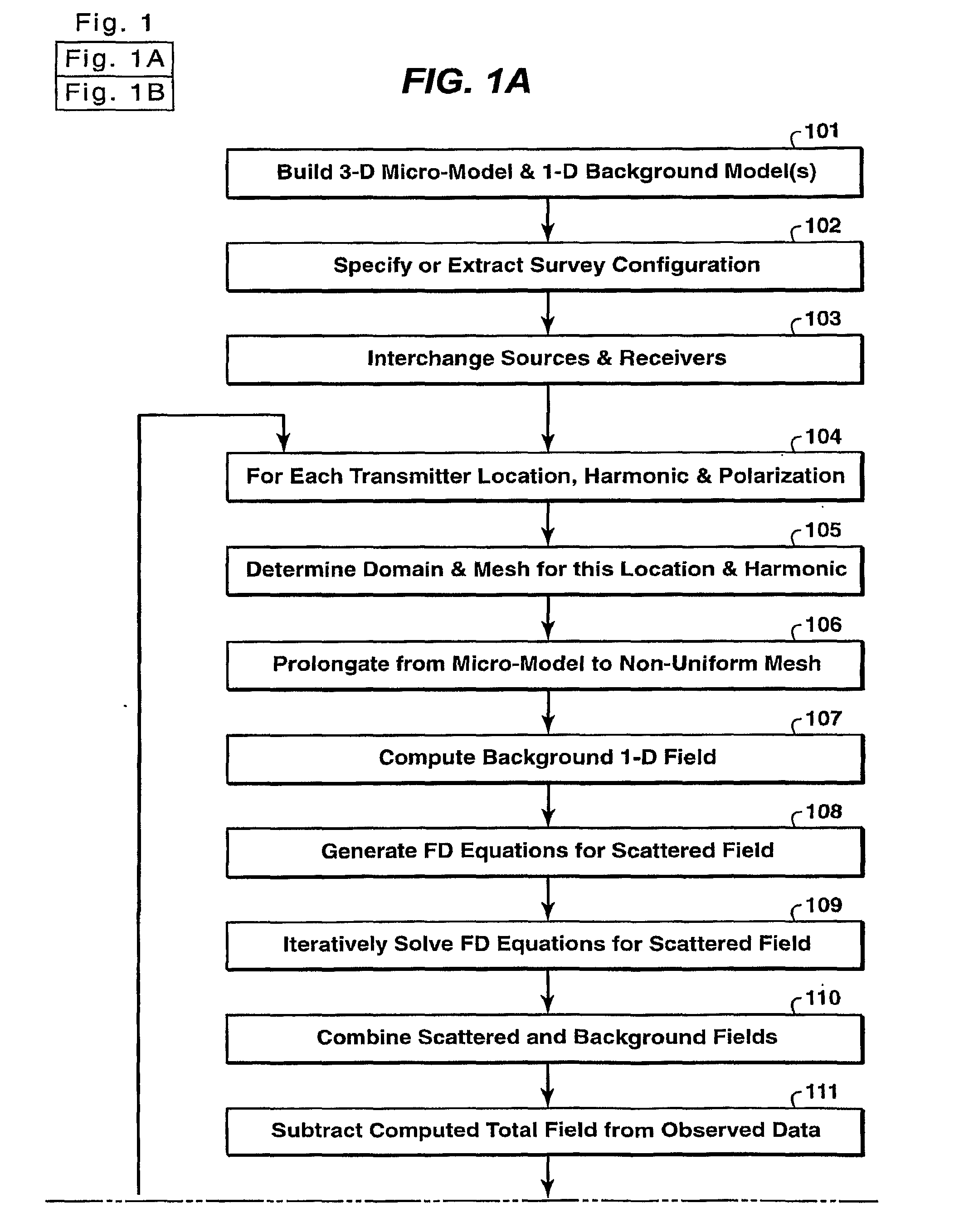

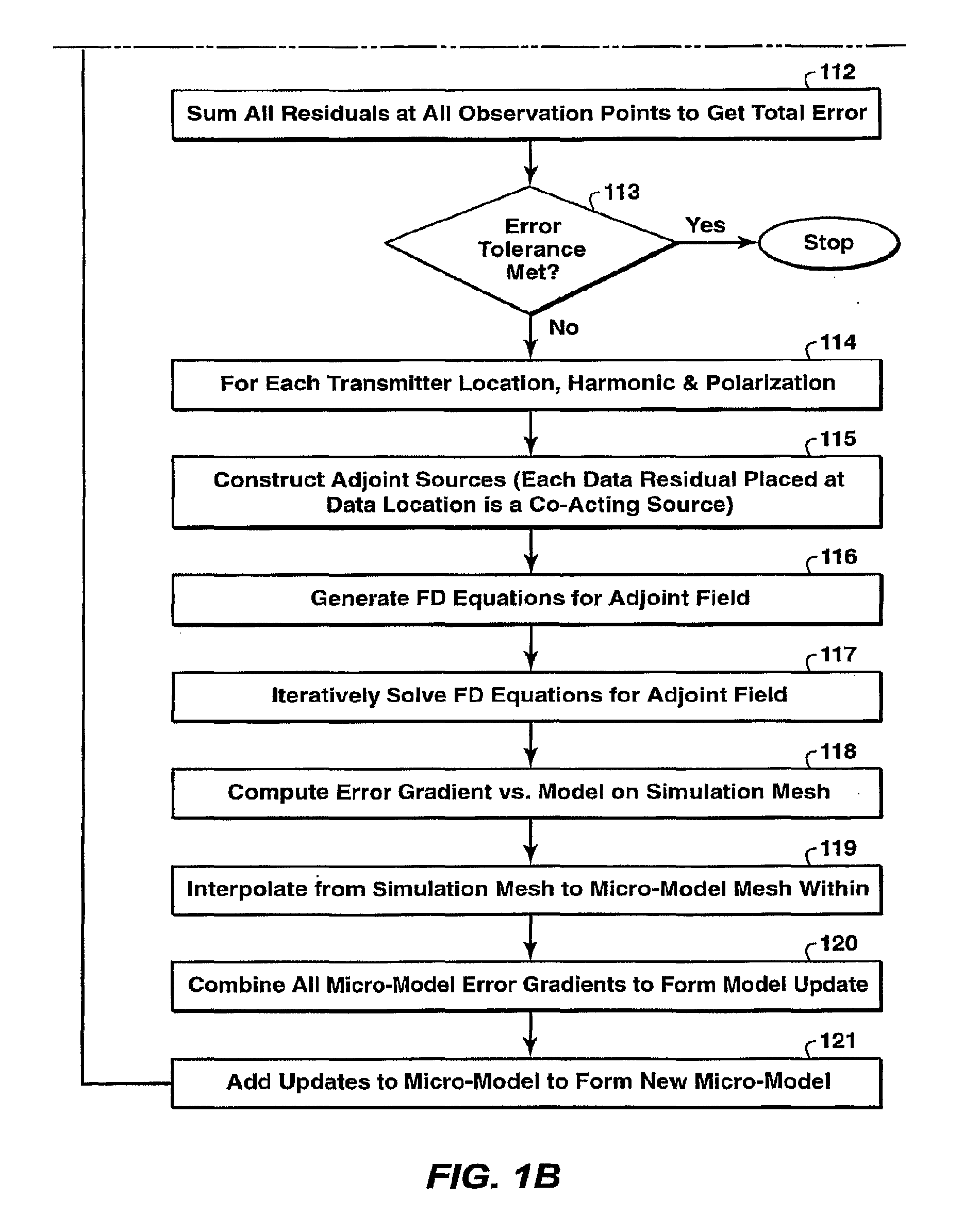

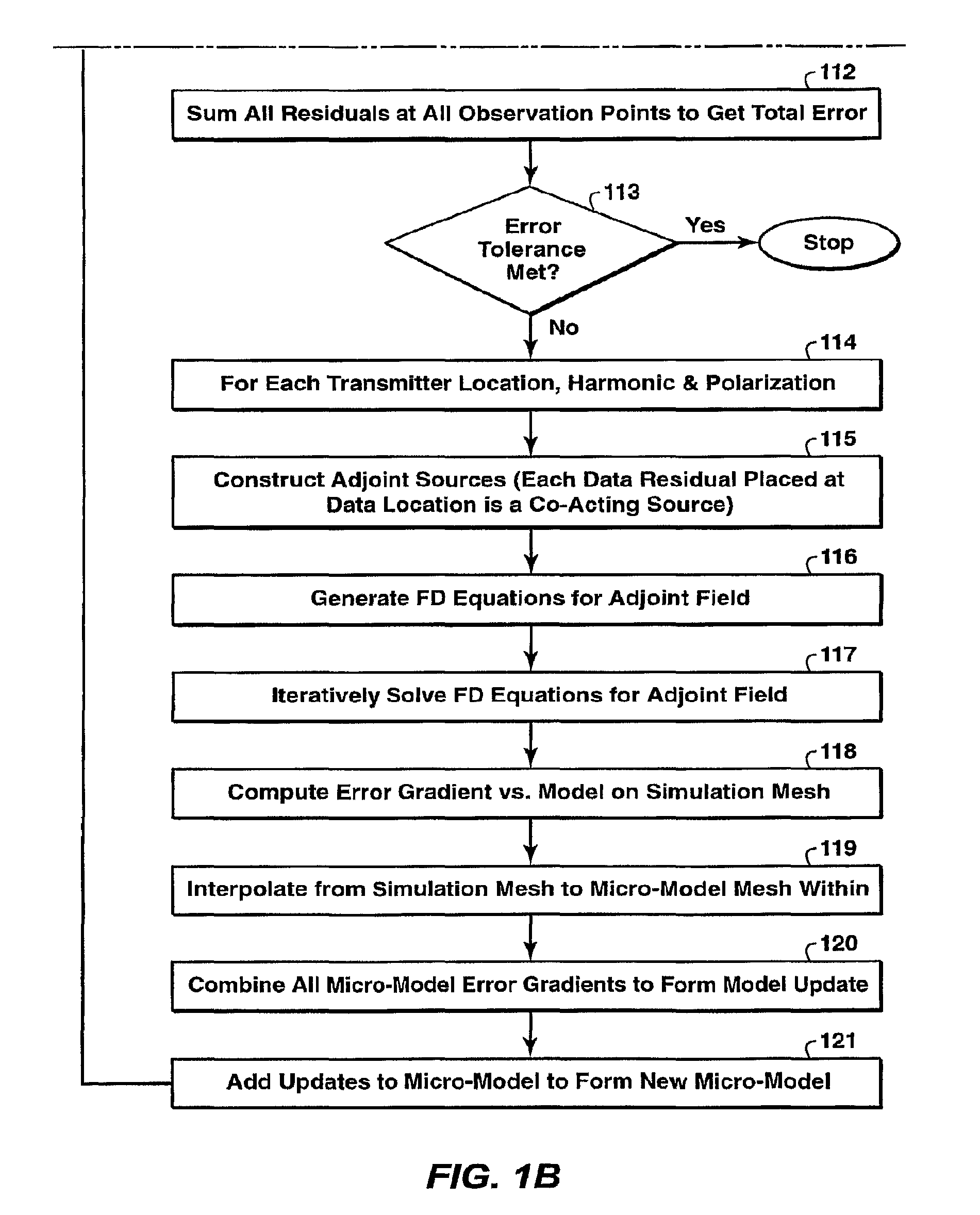

Method for efficient processing of controlled source electromagnetic data, whereby Maxwell's equations are solved [107] by numerical techniques [109] such as finite difference or finite element in three dimensions for each source location and frequency of interest. The Reciprocity Principle is used [103] to reduce the number of computational source positions, and a multi-grid is used [105] for the computational grid to minimize the total number of cells yet properly treat the source singularity, which is essential to satisfying the conditions required for applicability of the Reciprocity Principle. An initial global resistivity model [101] is Fourier interpolated to the computational multi grids [106]. In inversion embodiments of the invention, Fourier prolongation is used to update [120] the global resistivity model based on optimization results from the multi-grids.

Owner:EXXONMOBIL UPSTREAM RES CO

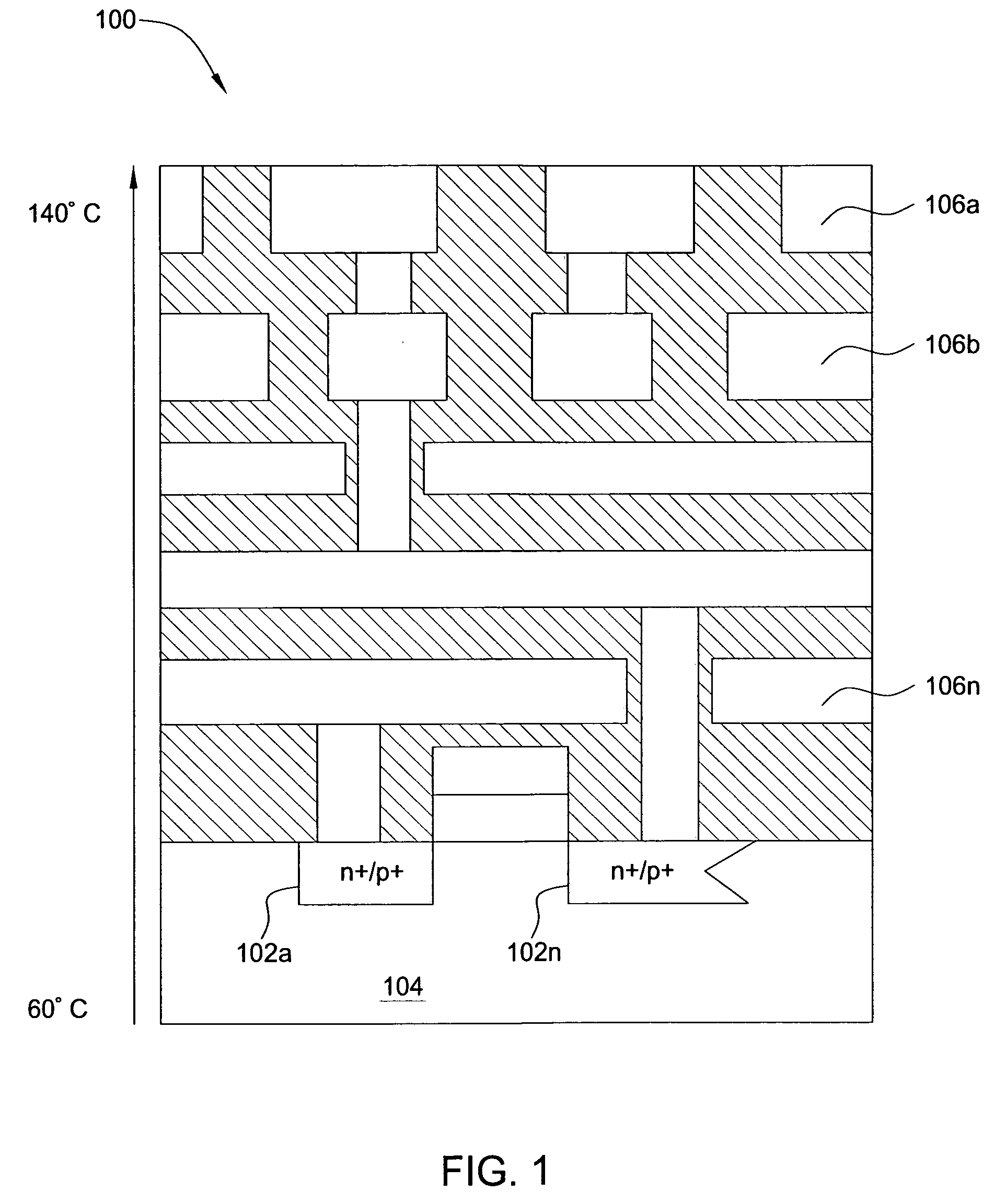

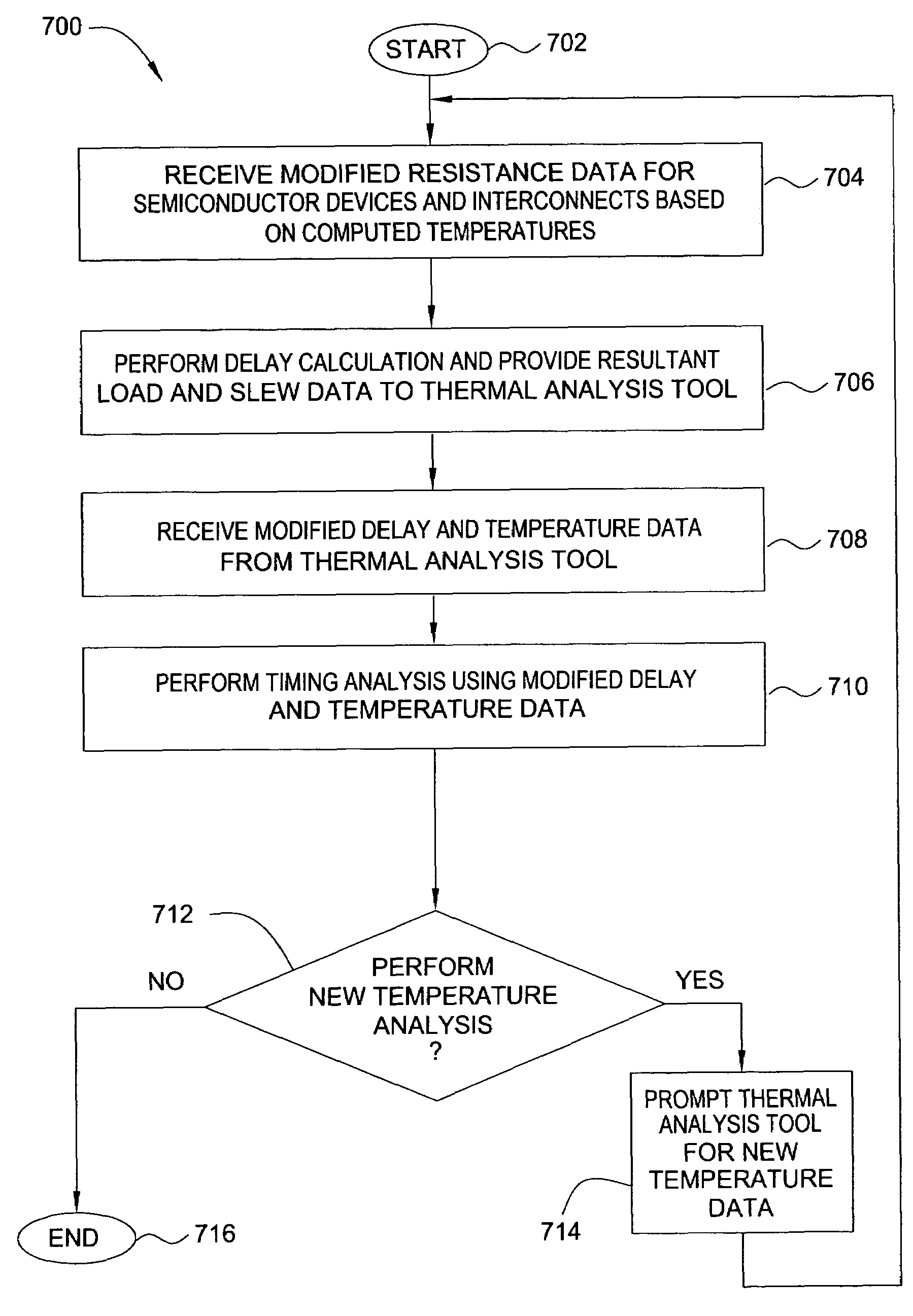

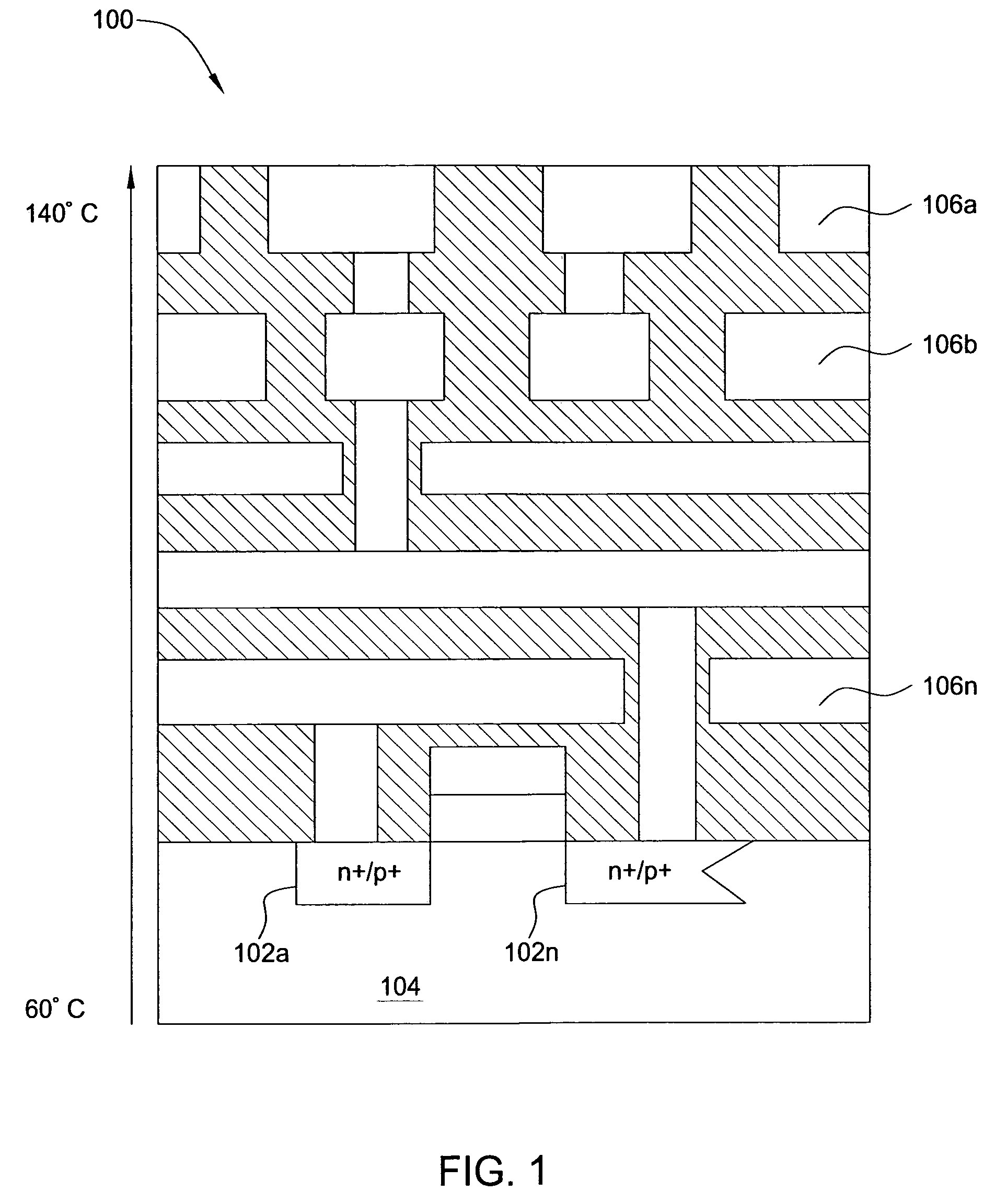

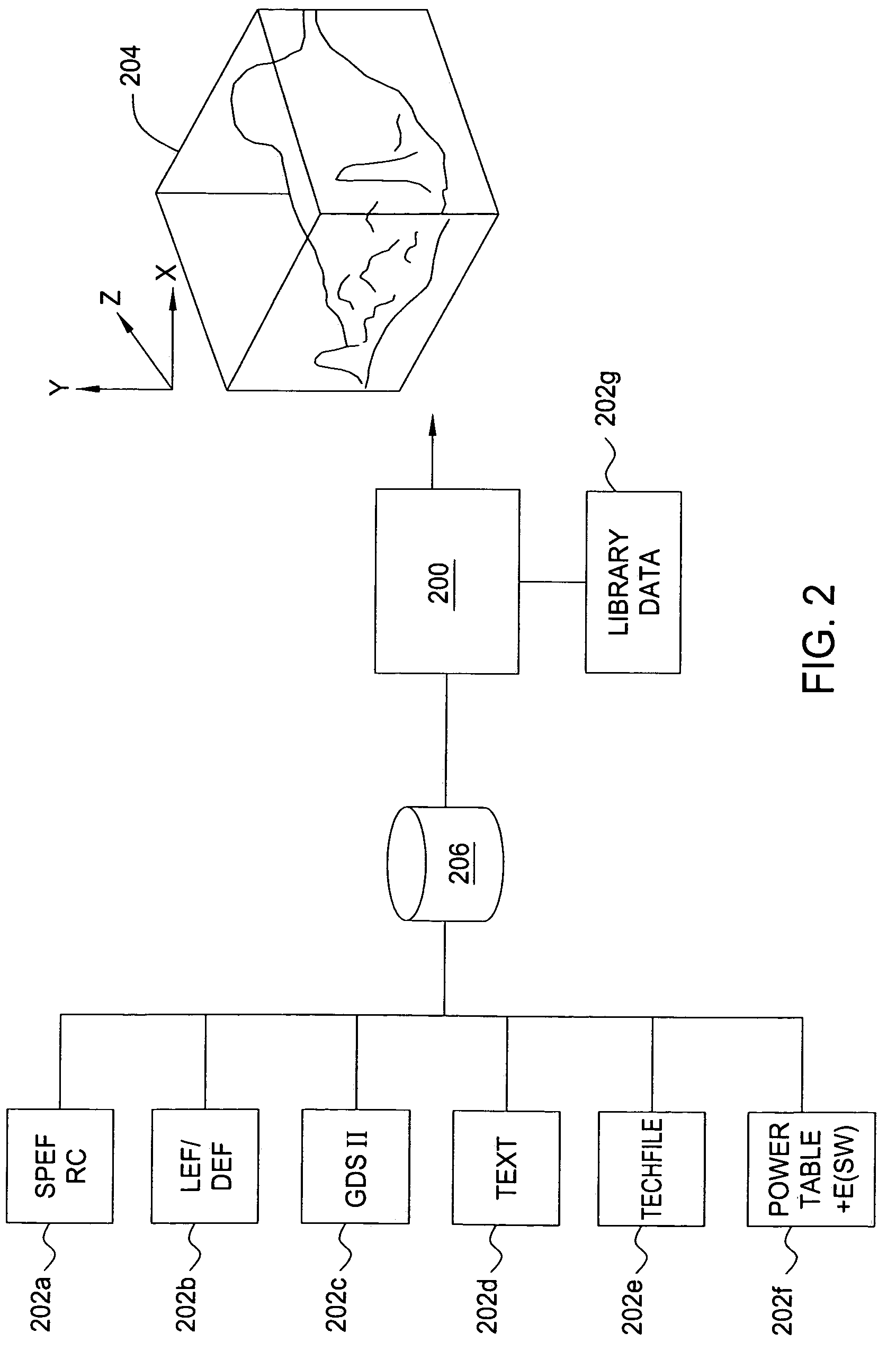

Method and apparatus for thermal modeling and analysis of semiconductor chip designs

ActiveUS20060031794A1Computation using non-denominational number representationDesign optimisation/simulationSemiconductor chipEngineering

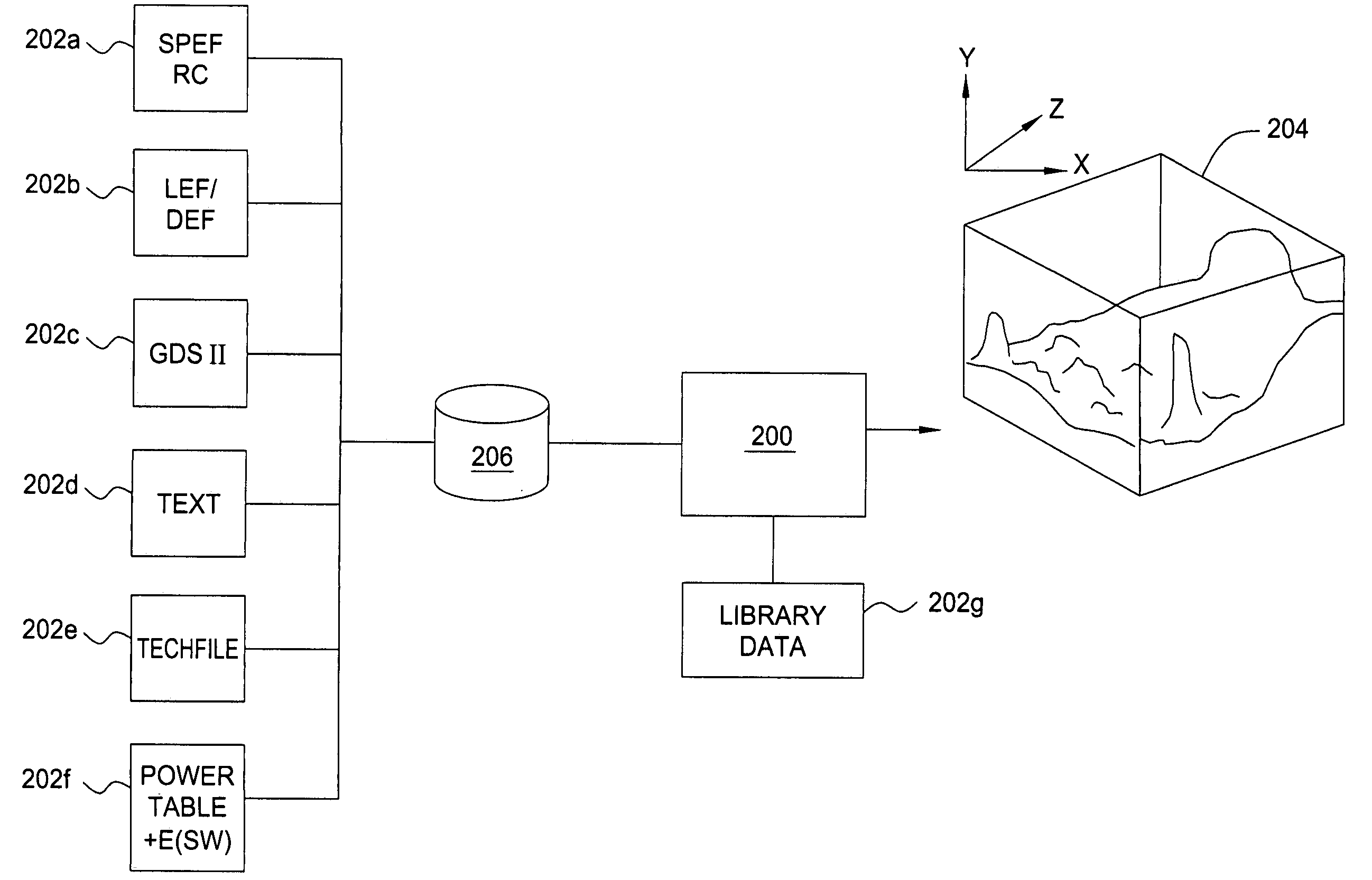

A method and apparatus for modeling and thermal analysis of semiconductor chip designs is provided. One embodiment of a novel method for performing thermal testing of a semiconductor chip design includes calculating full-chip temperatures over the semiconductor chip design (e.g., to identify steep thermal gradients) and modeling the full-chip temperatures in accordance with a geometric multi-grid technique. The geometric multi-grid technique is tailored to determine temperatures within the semiconductor chip design based at least in part on the physical attributes or geometry of the design.

Owner:KEYSIGHT TECH

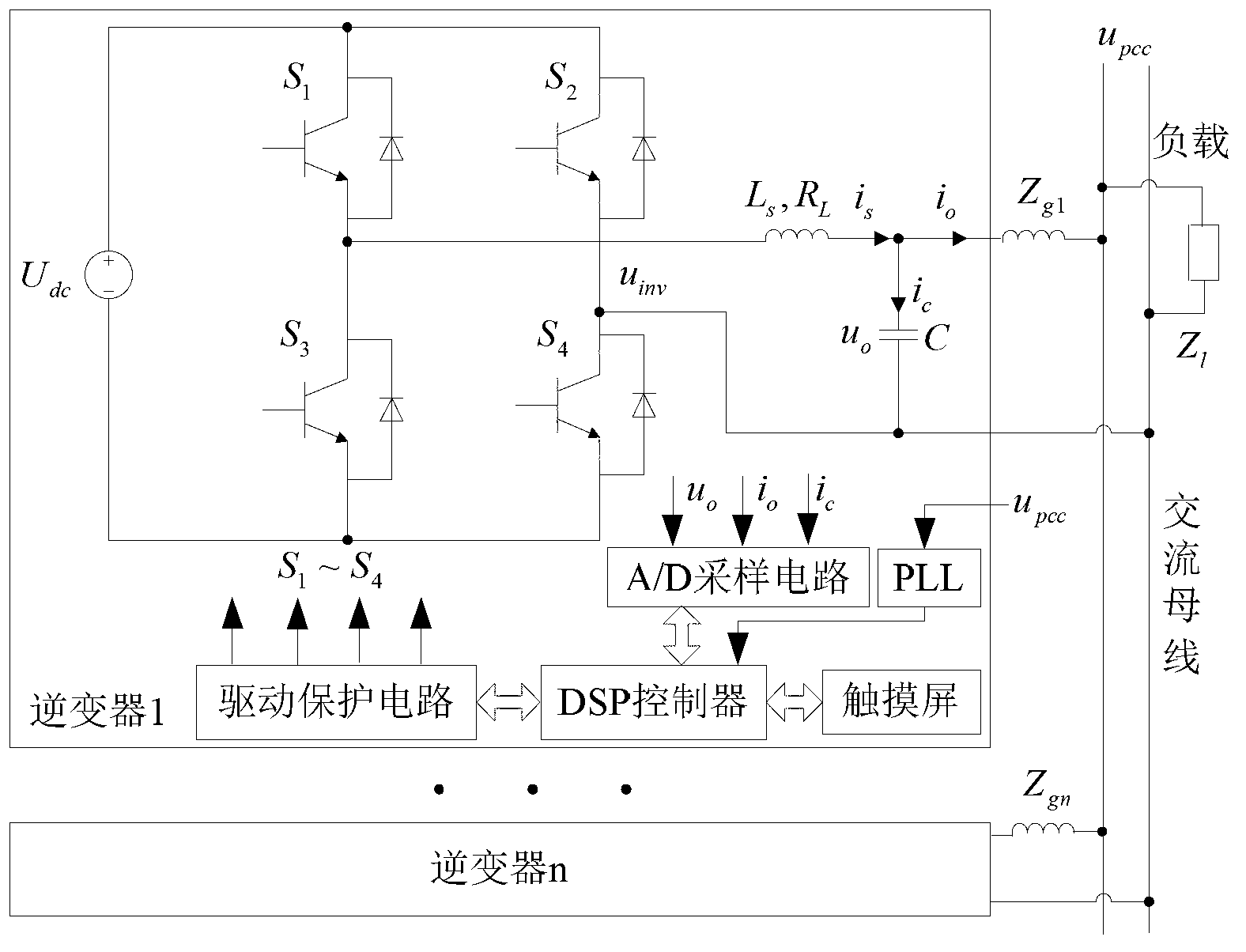

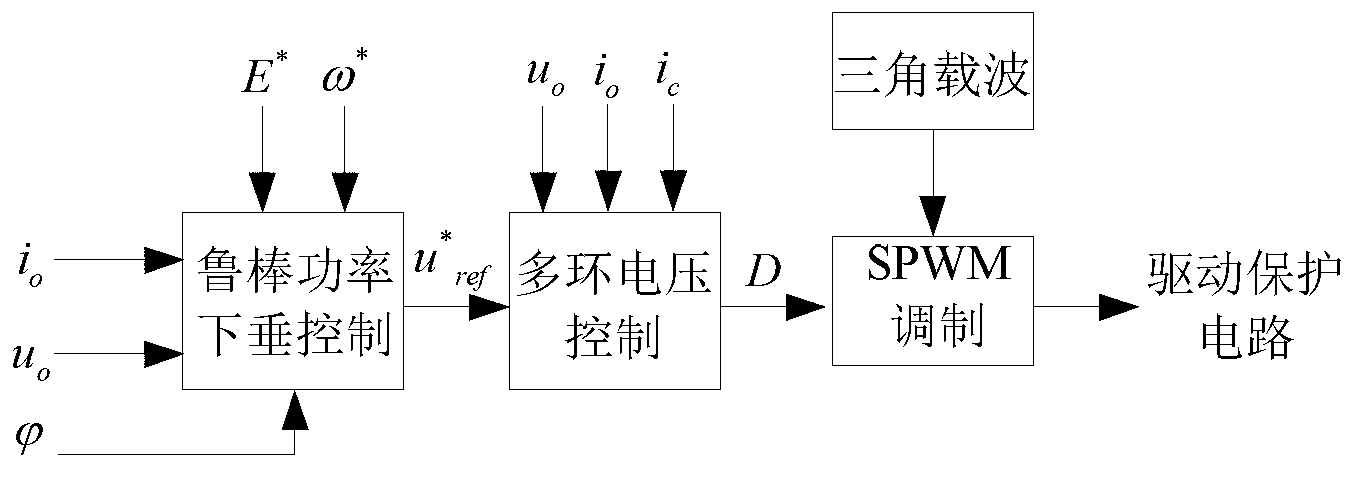

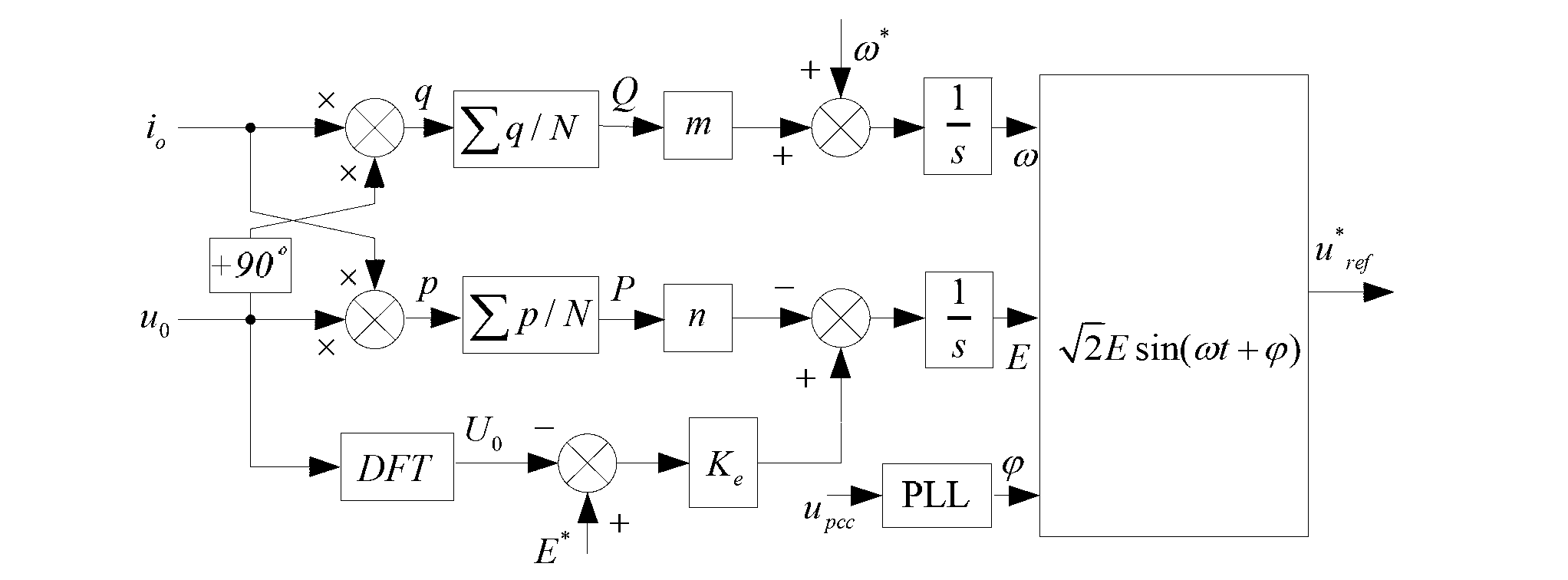

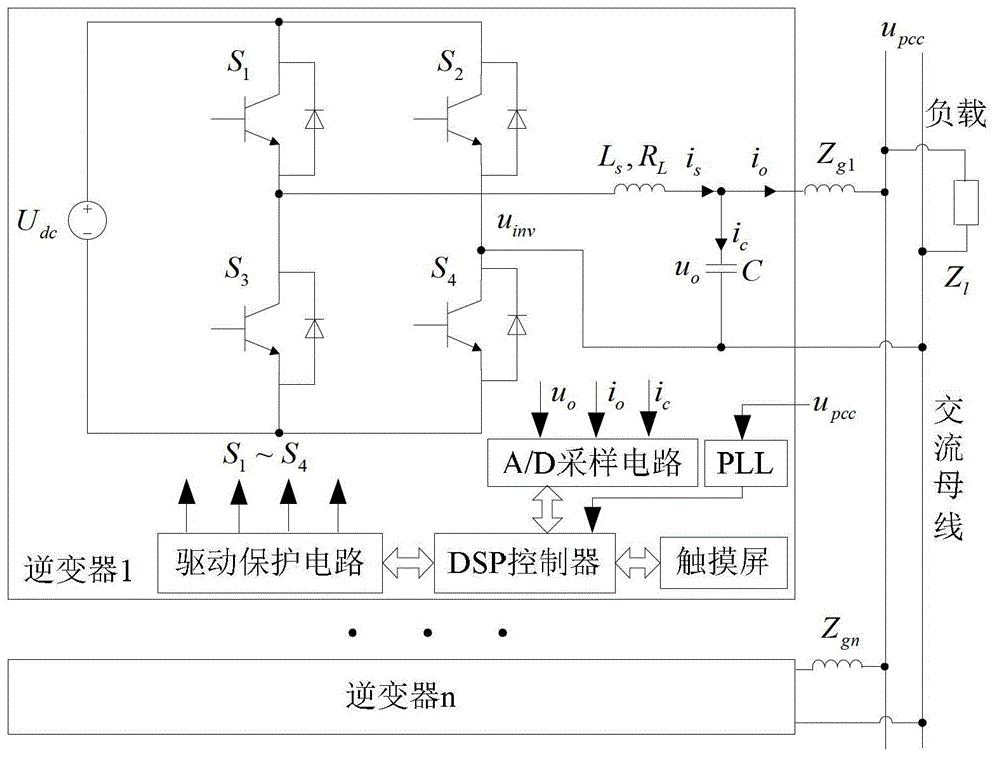

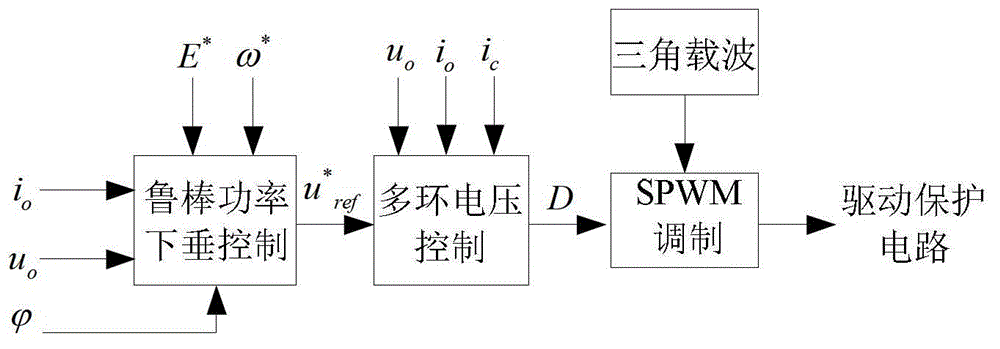

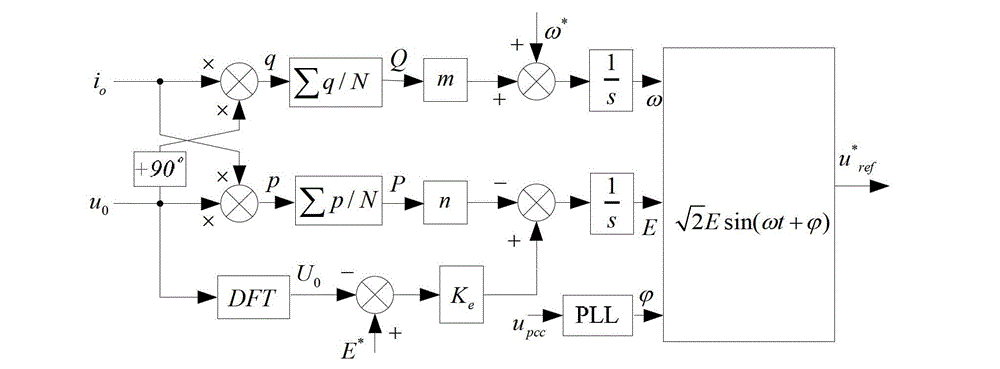

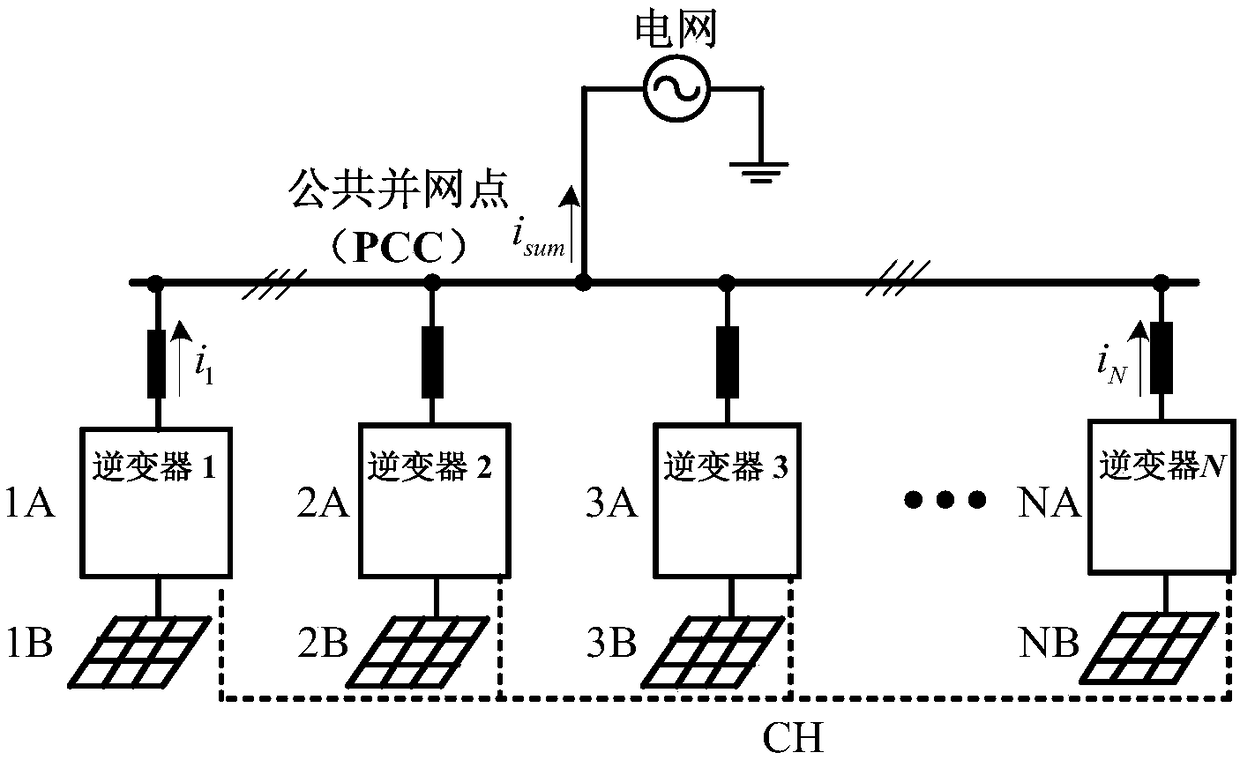

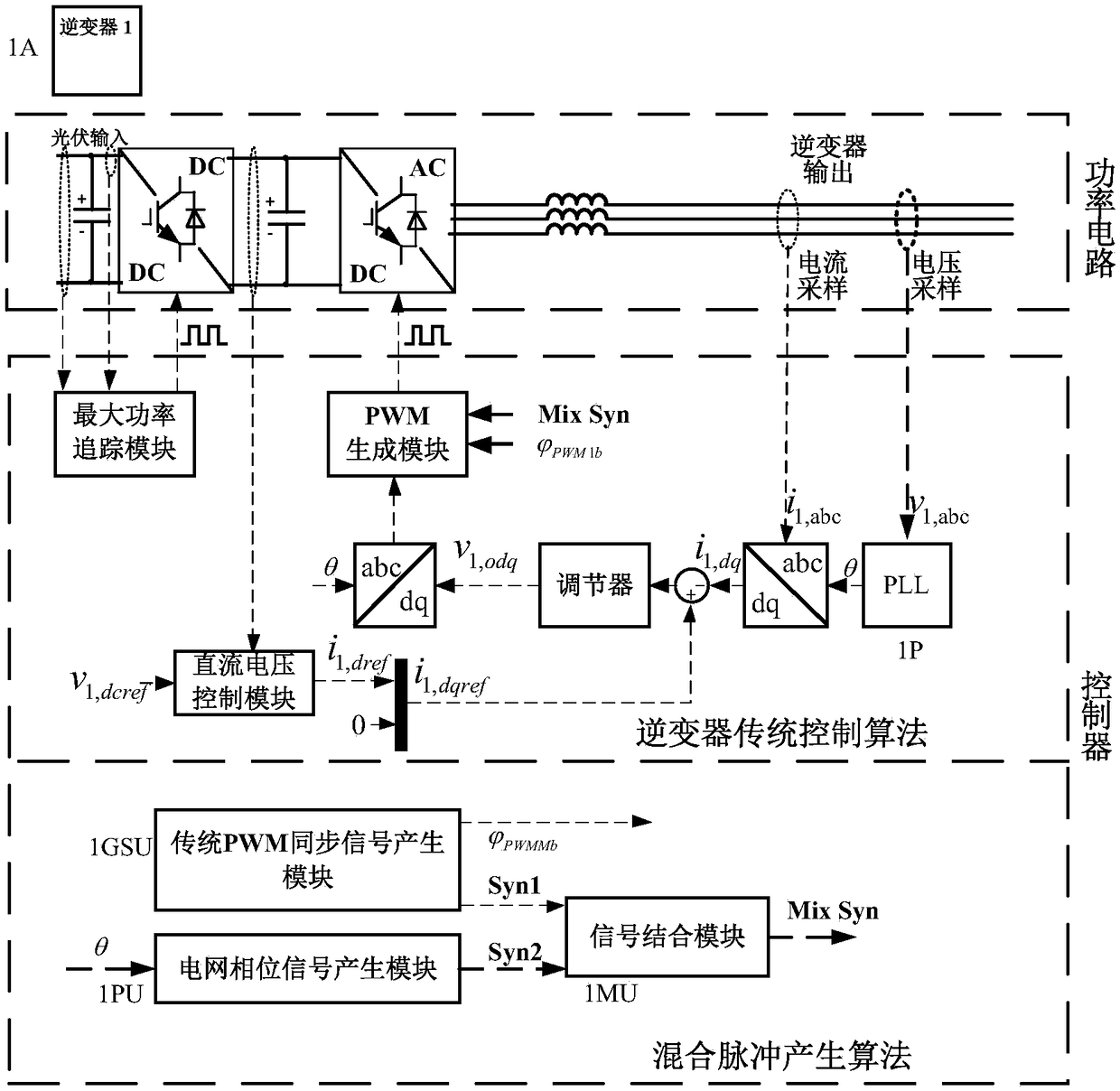

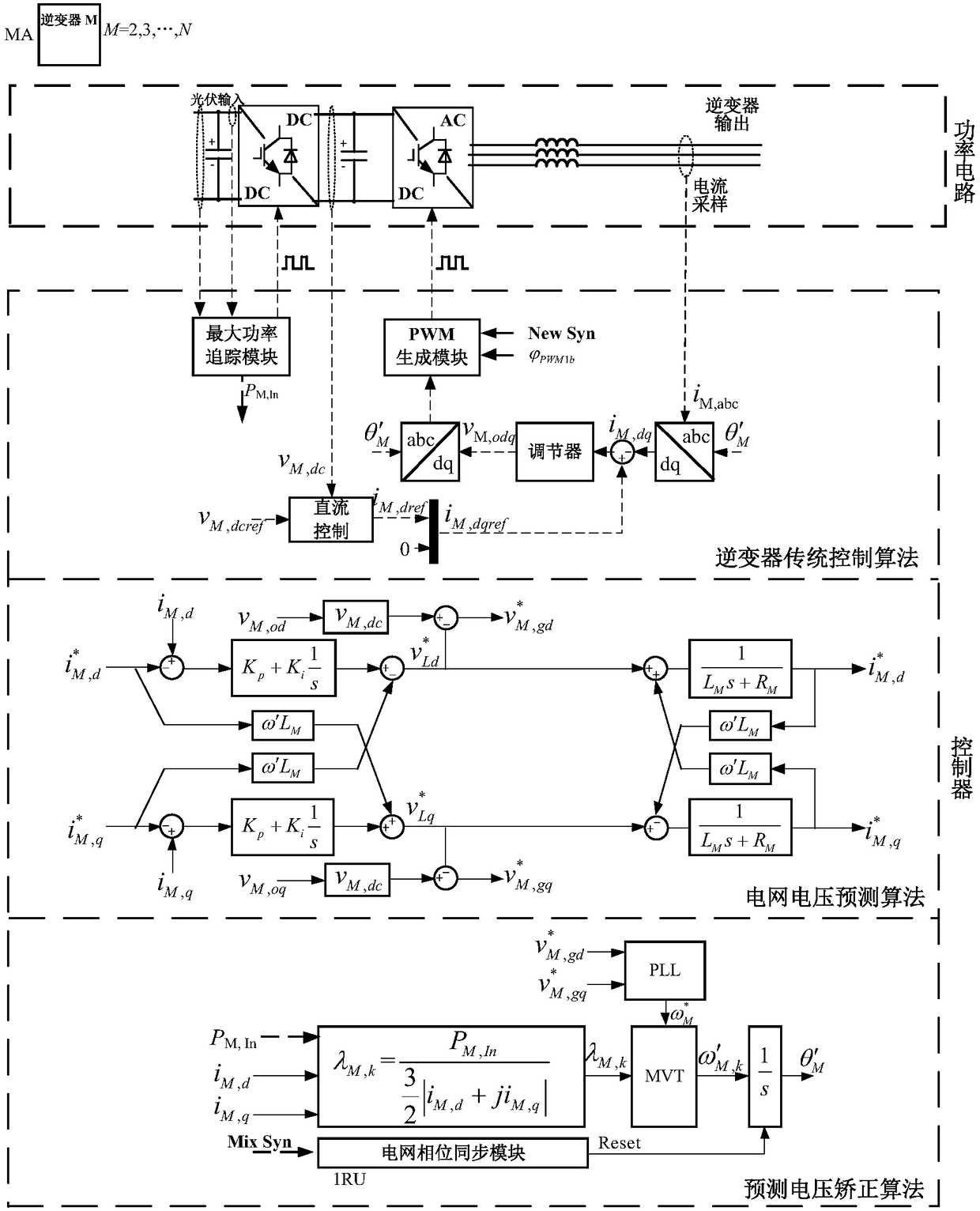

Micro-grid multi-inverter parallel voltage control method for droop control of robust power

ActiveCN102842921AIncrease the output resistanceSmall output resistanceSingle network parallel feeding arrangementsLow voltageVoltage reference

The invention discloses a micro-grid multi-inverter parallel voltage control method for droop control of robust power. The method comprises the following steps of: specific to each inverter in a micro-grid, computing and synthesizing an inverter output reference voltage by adopting a robust power droop controller; and introducing virtual complex impedance containing a resistance component and an inductive impedance component, and keeping inverter output impedance in a pure resistance state under a power frequency condition by adopting a multi-loop voltage control method based on virtual impedance and quasi-resonance PR (Proportional-Resonant) control, thereby realizing micro-grid multi-inverter parallel running and power equation, wherein the robustness of a micro-grid parallel system on numeric value computing errors, parameter drift, noise interference and the like is enhanced. Due to the adoption of the method, the defects of larger loop current of a parallel system, non-uniform power distribution and the like caused by the inductivity of the impedance output by inverters in the conventional droop method are overcome; and the method is suitable for multi-grid parallel uniform current control in a low-voltage micro-grid.

Owner:HUNAN UNIV

Spectral mixture process conditioned by spatially-smooth partitioning

InactiveUS20050047663A1Accurate global labelingImprove global labelingScene recognitionClassification methodsEnergy functional

A method that facilitates identification of features in a scene enables enhanced detail to be displayed. One embodiment incorporates a multi-grid Gibbs-based algorithm to partition sets of endmembers of an image into smaller sets upon which spatial consistency is imposed. At each site within an imaged scene, not necessarily a site entirely within one of the small sets, the parameters of a linear mixture model are estimated based on the small set of endmembers in the partition associated with that site. An, enhanced spectral mixing process (SMP) is then computed. One embodiment employs a simulated annealing method of partitioning hyperspectral imagery, initialized by a supervised classification method to provide spatially smooth class labeling for terrain mapping applications. One estimate of the model is a Gibbs distribution defined over a symmetric spatial neighborhood system that is based on an energy function characterizing spectral disparities in both Euclidean distance and spectral angle.

Owner:UNIV OF VIRGINIA ALUMNI PATENTS FOUND

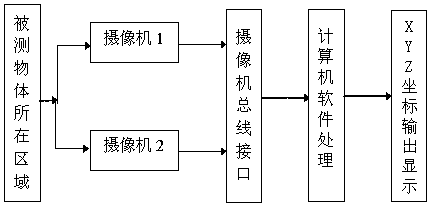

Three-dimensional reconstruction method for binocular stereo vision

InactiveCN108335350AAvoid excessive dependenceNarrow searchImage analysisImage renderingComponent Object ModelTriangulation

The invention provides a three-dimensional reconstruction method for binocular stereo vision. The method comprises the steps of performing image pair collection: obtaining images of a calibration plate and an object; performing camera calibration: performing calibration on a camera based on a Zhengyou Zhang calibration method to obtain initial internal and external parameters of the camera; performing stereo rectification: performing rectification on a distortion parameter through epipolar constraint to obtain a rectified image pair; performing image processing: obtaining a region of interest,and balancing brightness difference between left and right images, thereby searching for matching points; performing stereo matching: implementing a multi-grid intensive stereo matching algorithm toobtain a continuous smooth disparity map; and performing point cloud rebuilding and model rebuilding: obtaining a point cloud chart of the object, performing point cloud optimization, and obtaining acomplete object model through triangulation of a greedy algorithm. The smooth model with no obvious difference with the real object can be obtained; and the method can be used for three-dimensional reconstruction of multiple scenes.

Owner:LIAOCHENG UNIV

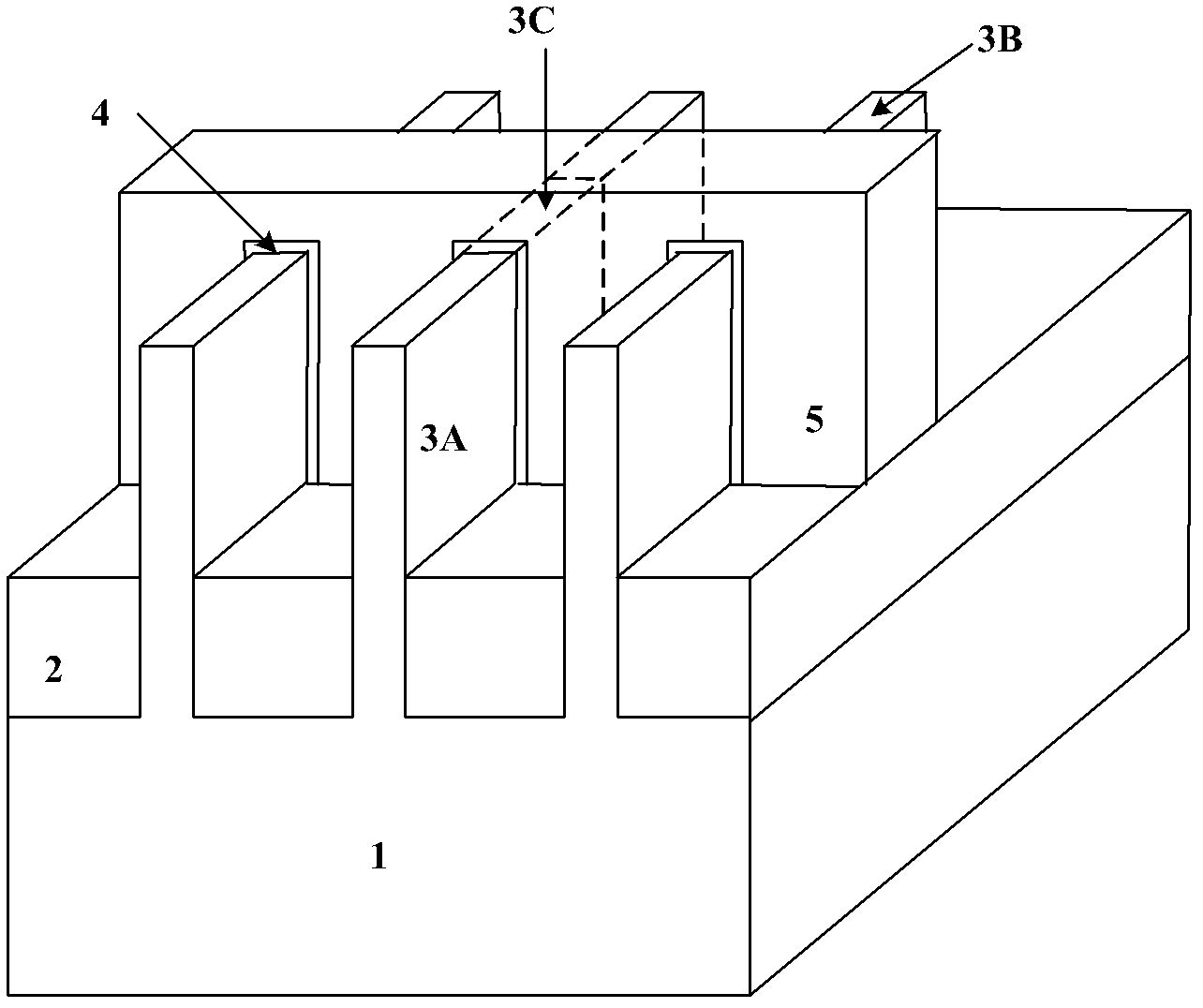

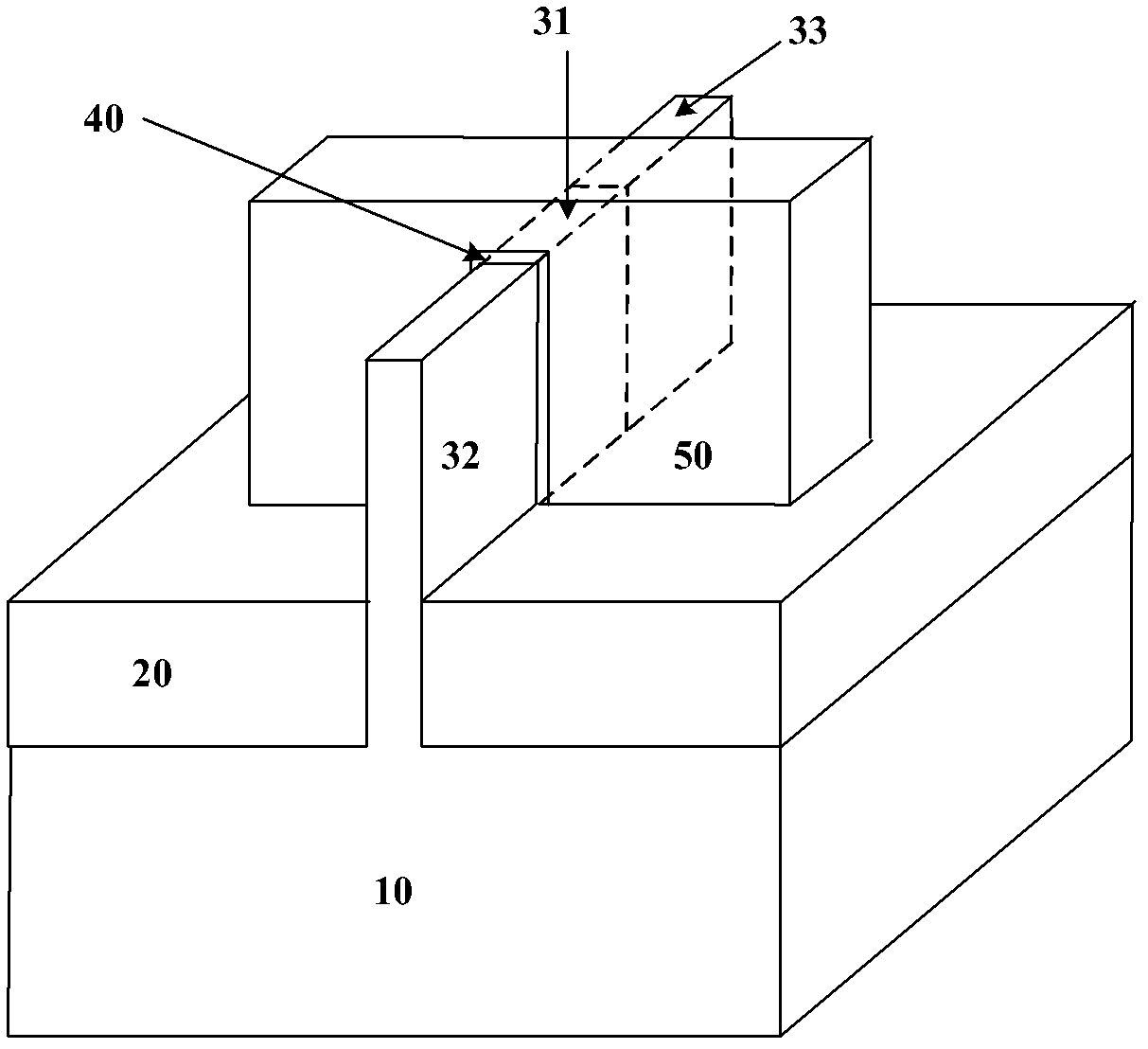

Three-dimensional semiconductor device and manufacturing method thereof

ActiveCN104022121AImprove reliabilityImprove control characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETVertical channel

The invention discloses a three-dimensional semiconductor device comprising a plurality of memory unit transistors and a plurality of selection transistors, wherein the plurality of memory unit transistors are at least partially overlapped in the vertical direction; each selection transistor comprises a first drain electrode distributed along the vertical direction, an active region, a common source electrode formed in a substrate and a metal grid electrode distributed around the active region; each memory unit transistor comprises a channel layer distributed vertical to the surface of the substrate, wherein a plurality of interlayer insulating layers and a plurality of grid electrode stacking structures are alternately stacked along the side wall of the channel layer, and a second drain electrode is located at the top of the channel layer; the channel layer is electrically connected with the first drain electrode. According to the three-dimensional semiconductor device and a manufacturing method thereof disclosed by the invention, multi-grid MOSFETs (Metal-Oxide-Semiconductor Field Effect Transistors) are formed below memory unit string stacks comprising vertical channels so as to be used as the selection transistors, thus the threshold voltage control characteristic of the grid electrode is improved, the off-state leakage current is reduced, the over-etching for the substrate is avoided, and the reliability of the device is effectively improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

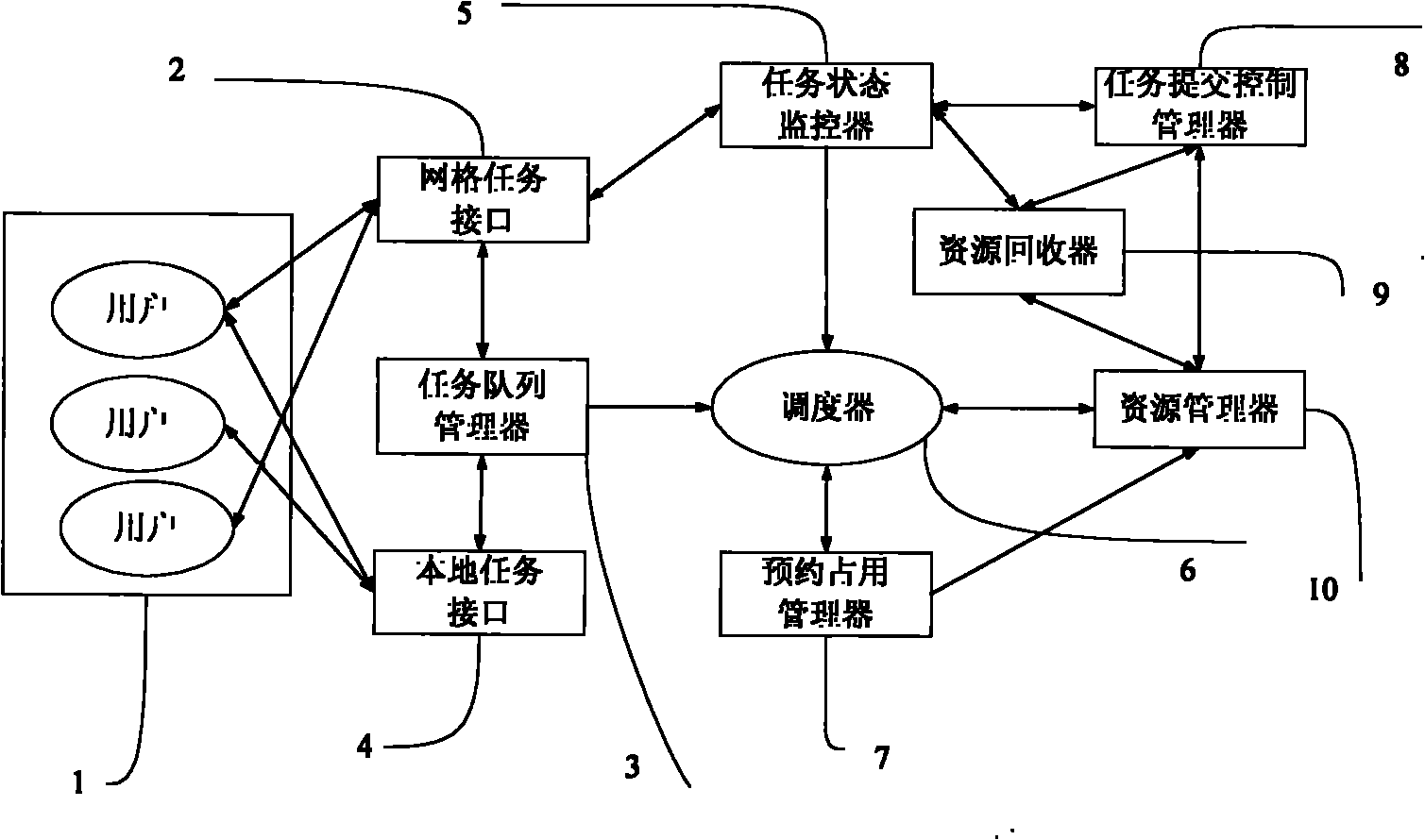

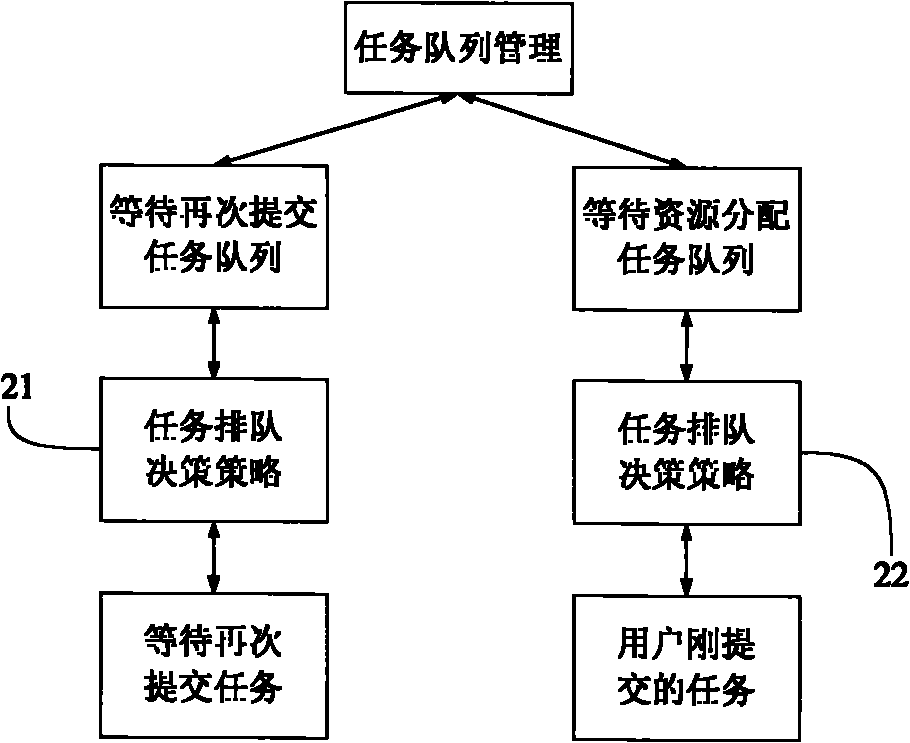

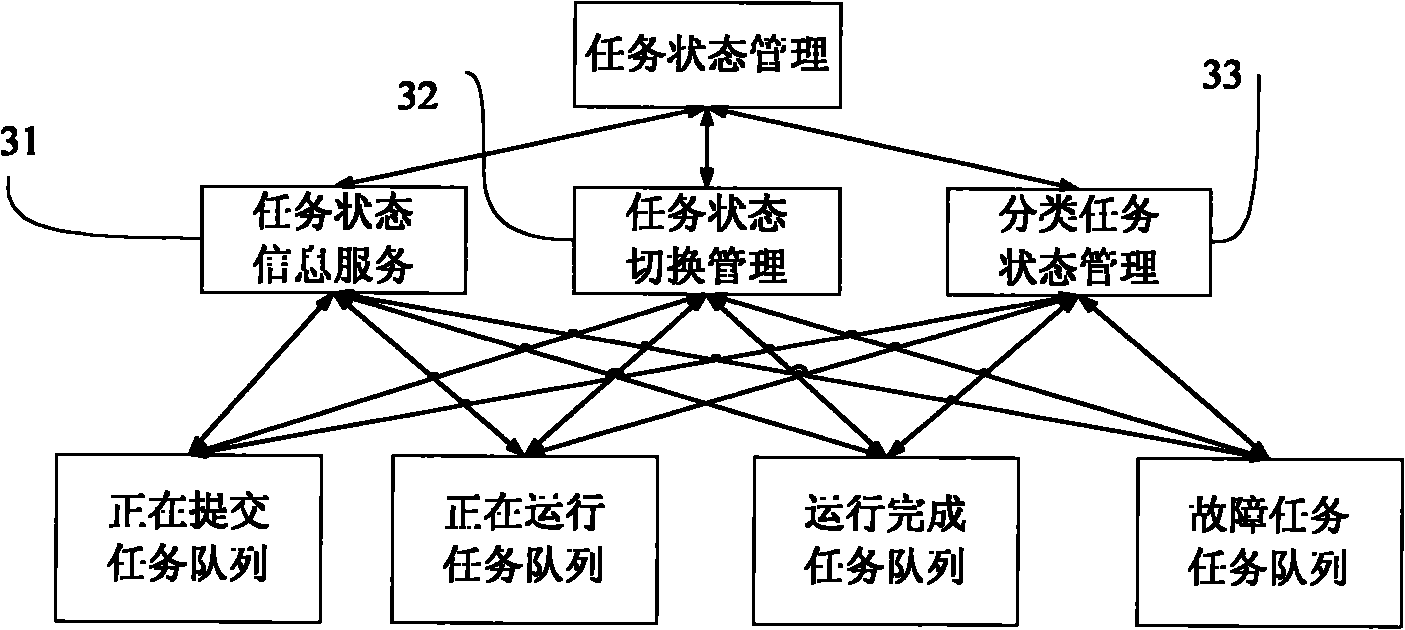

Cluster task dispatching manager used for multi-grid access

InactiveCN101958808AGuaranteed right of priorityTake advantage ofData switching networksWireless communicationCluster systemsResource allocation

The invention discloses a cluster task dispatching manager used for multi-grid access. Tasks on a cluster system are divided into local tasks and grid tasks, and a grid corresponding to the grid task is determined.Priority classification is carried out on the tasks, so as to ensure that cluster resource is allocated to the tasks according to task priority while the tasks are submitted. Meanwhile local task reservation resource occupying strategy is adopted, so as to ensure that the task from the grid can not contend cluster resource with the local task within valid reservation holding time when the local task has a great demand on resource. On the basis, a task dispatching and resource allocation strategy algorithm is provided, so as to ensure that required resource is timely and effectively allocated to the task. The invention can cause cluster task dispatching and management to be adaptive to that a cluster is simultaneously accessed by multiple grid systems, availability factor of cluster resource is fully improved, and task dispatching and management of cluster system are more flexible and convenient.

Owner:EAST CHINA JIAOTONG UNIVERSITY

Method and apparatus for thermal modeling and analysis of semiconductor chip designs

ActiveUS7401304B2Design optimisation/simulationSoftware simulation/interpretation/emulationSemiconductor chipEngineering

Owner:KEYSIGHT TECH

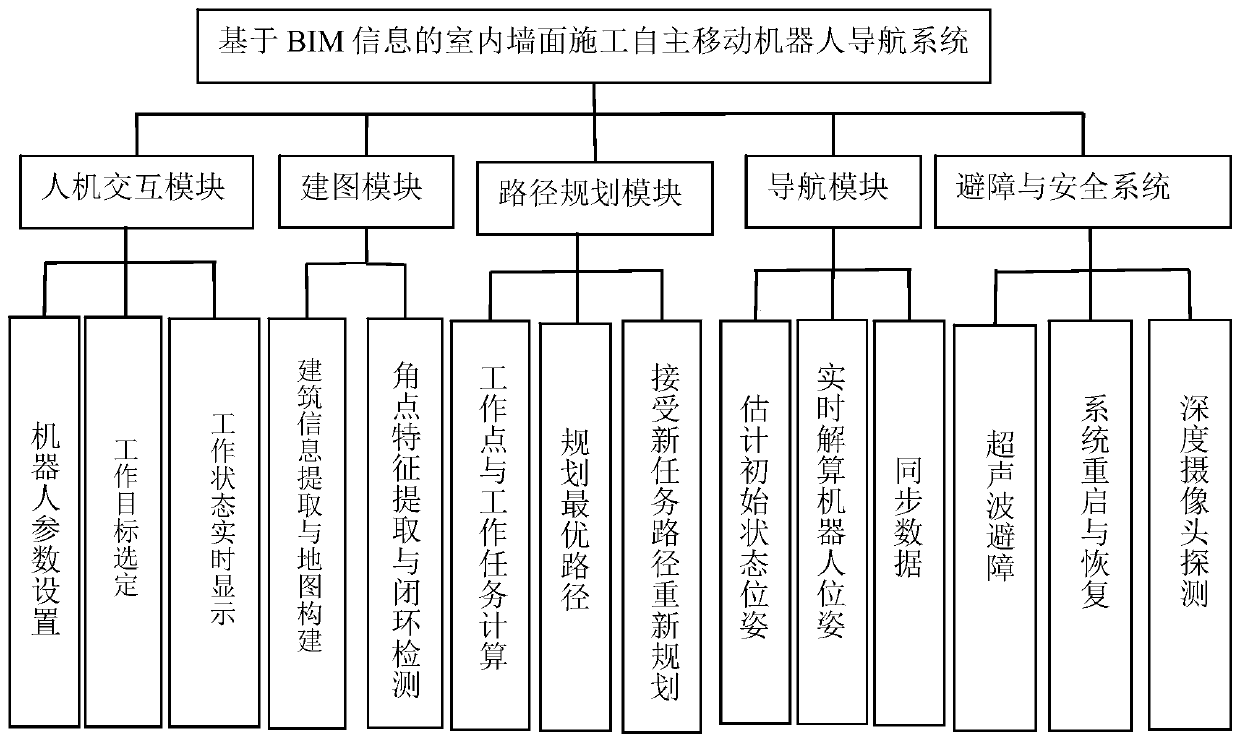

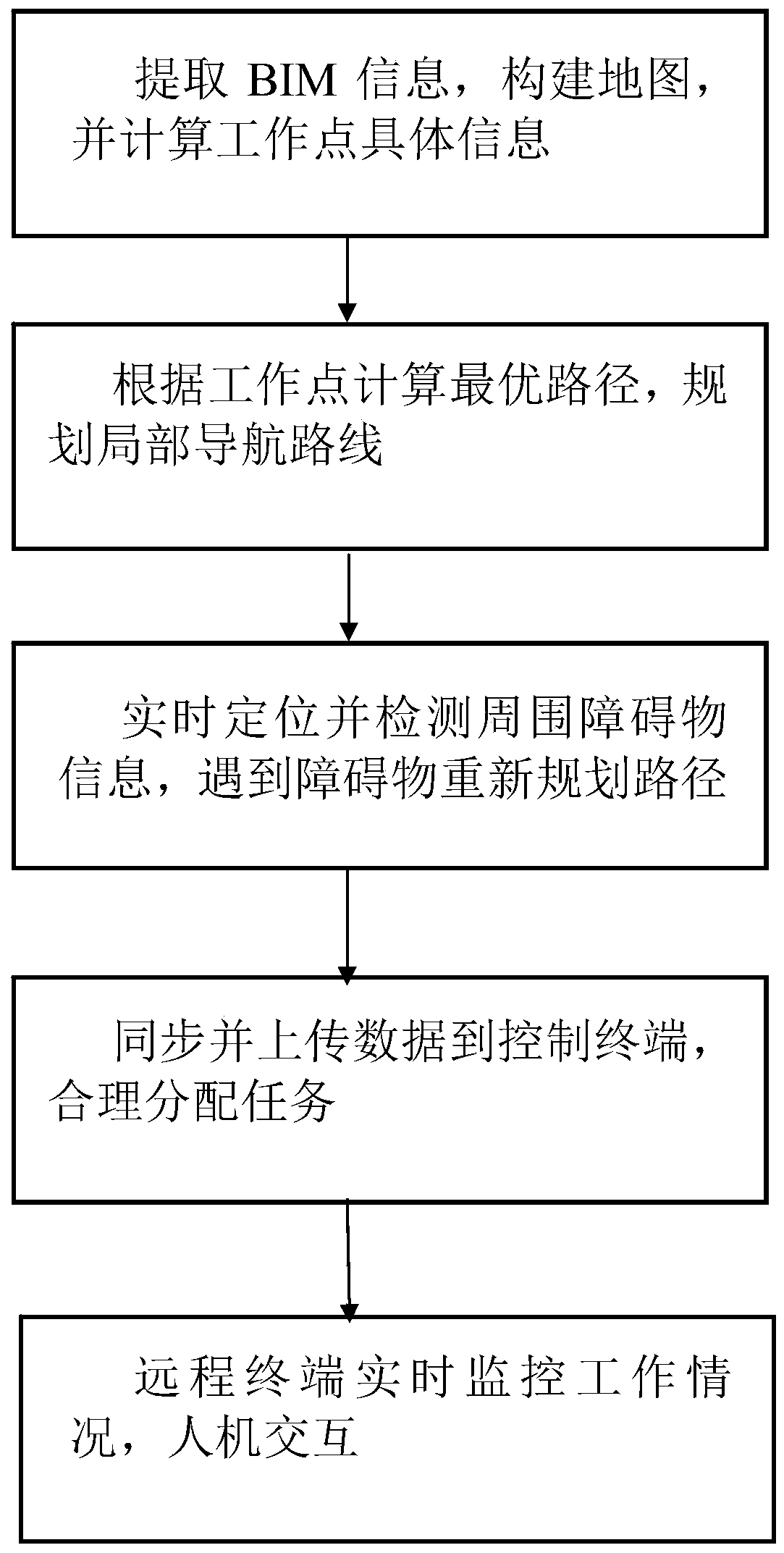

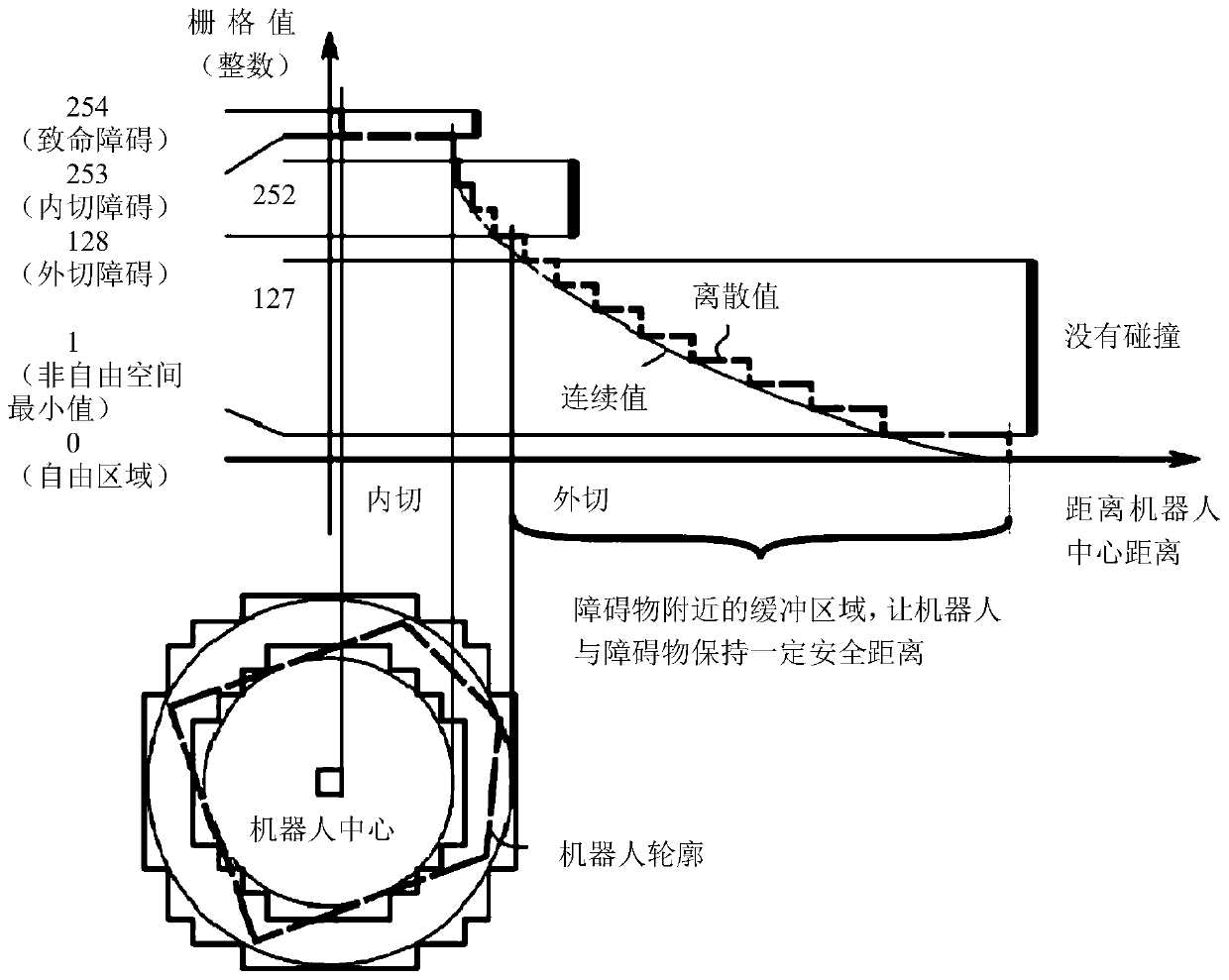

Multi-grid value navigation method based on robot pose and application thereof

ActiveCN109916393AExpand the passable areaImprove connectivityNavigation by speed/acceleration measurementsElectromagnetic wave reradiationWork taskComputer science

The invention discloses a multi-grid value navigation method based on the robot pose and an application thereof and belongs to the technical field of robot navigation. The method is characterized in that the accessible area of the robot in the grid map is expanded, and connectivity of topology maps is enhanced, moreover, through the indoor wall construction autonomous mobile robot navigation method based on the BIM information, working points are calculated based on the extracted BIM information, according to the position information of the working points and the order of work tasks, the multi-grid value navigation method based on the robot pose is utilized to set local navigation routes between the adjacent working points; real-time positioning is performed, and the obstacle information around an indoor wall construction autonomous mobile robot is detected, the grid map is updated, and the local navigation routes between the adjacent working points are reset based on the updated gridmap. The method is advantaged in that navigation work efficiency and accuracy are improved.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

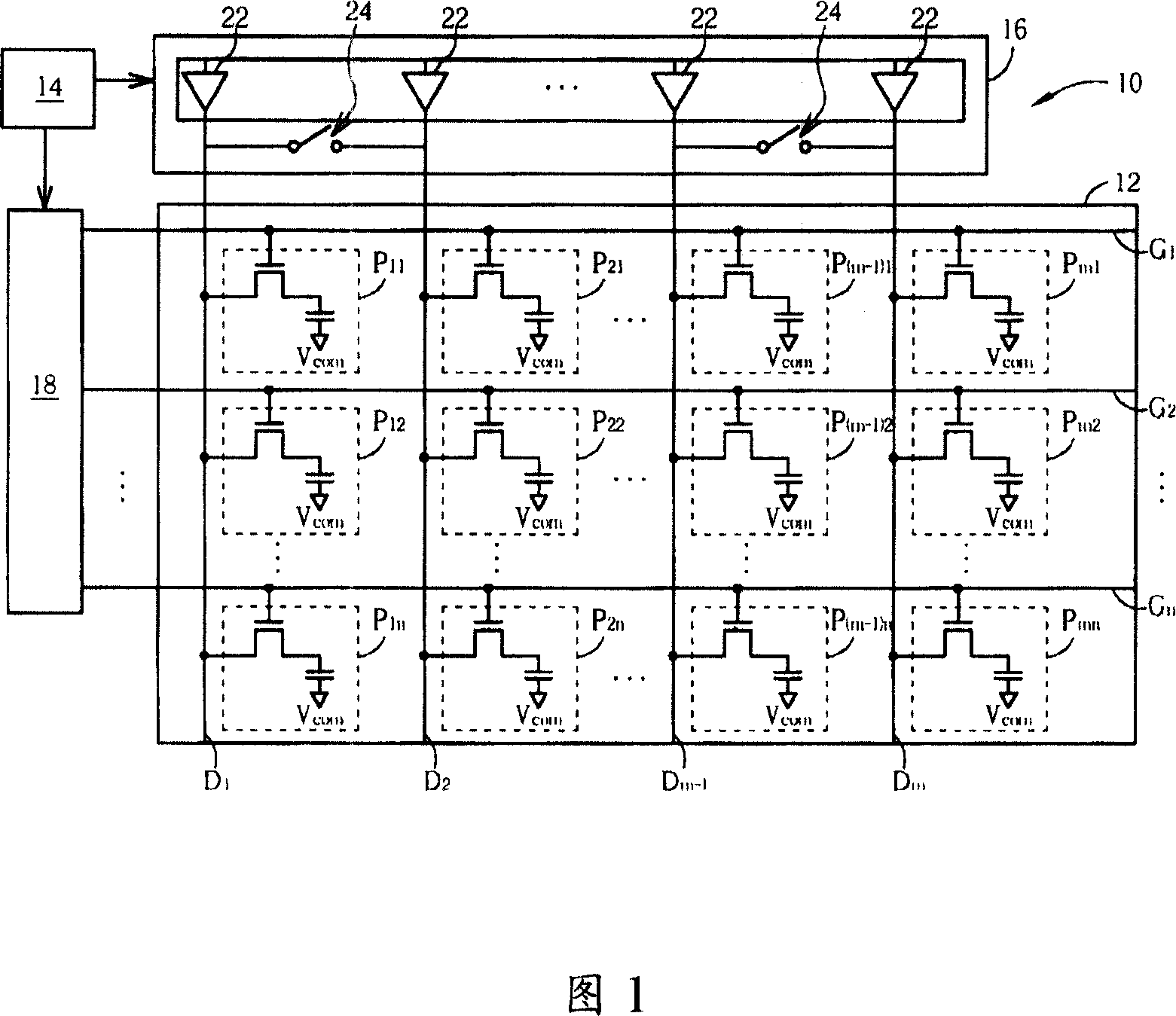

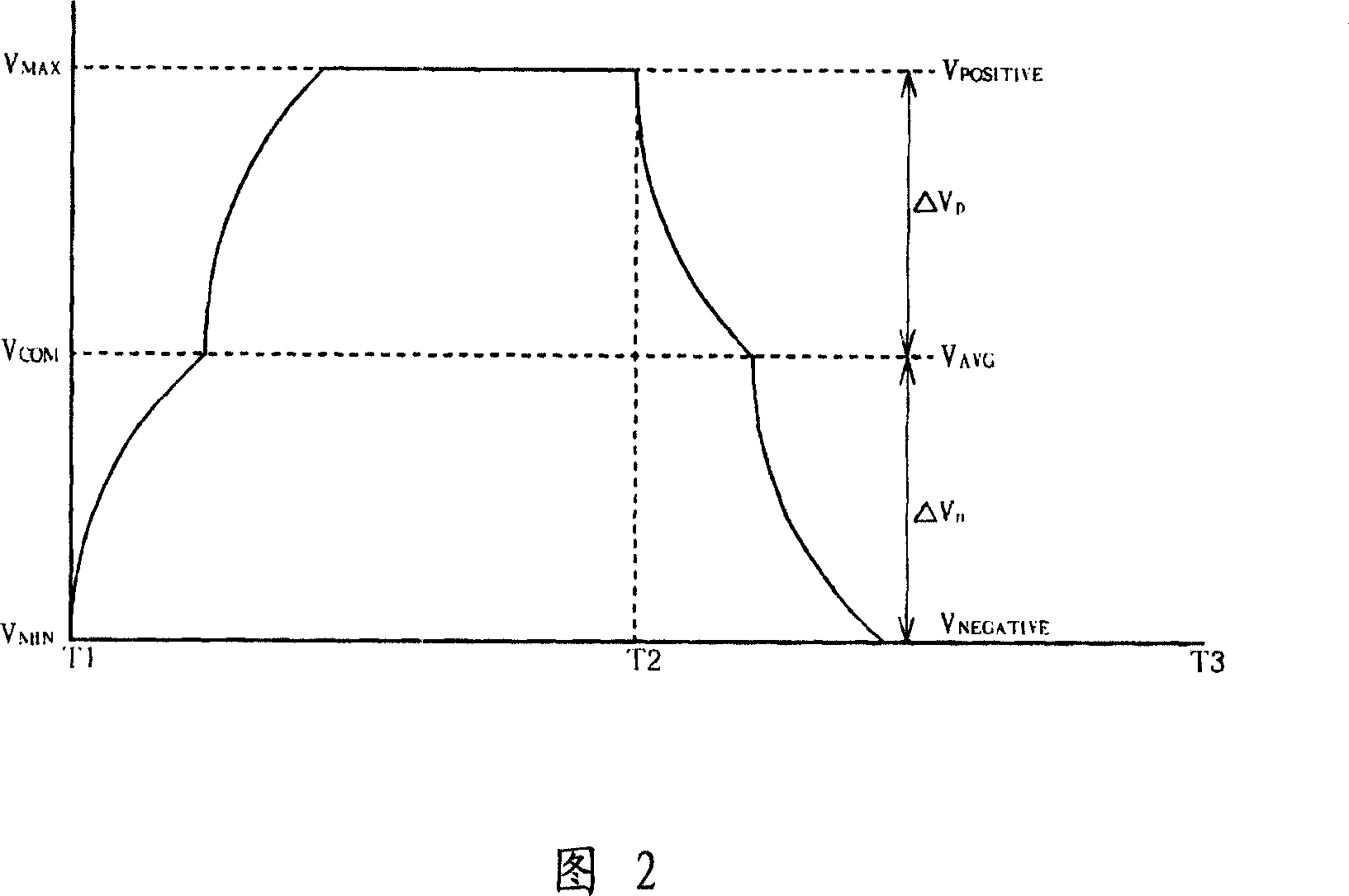

LCD device capable of sharing electric charge to reduce consumption of energy

The LCD display comprises multi data lines, multi grid lines, multi display units, two virtual grid lines and multi virtual switches. In positive polarity cycle, using the virtual grid lines and virtual switches to connect the corresponding data lines to the positive source in order to execute the charge sharing; in negative polarity cycle, using the virtual grid lines and virtual switches to connect the corresponding data lines to the negative voltage source to execute the charge sharing.

Owner:NOVATEK MICROELECTRONICS CORP

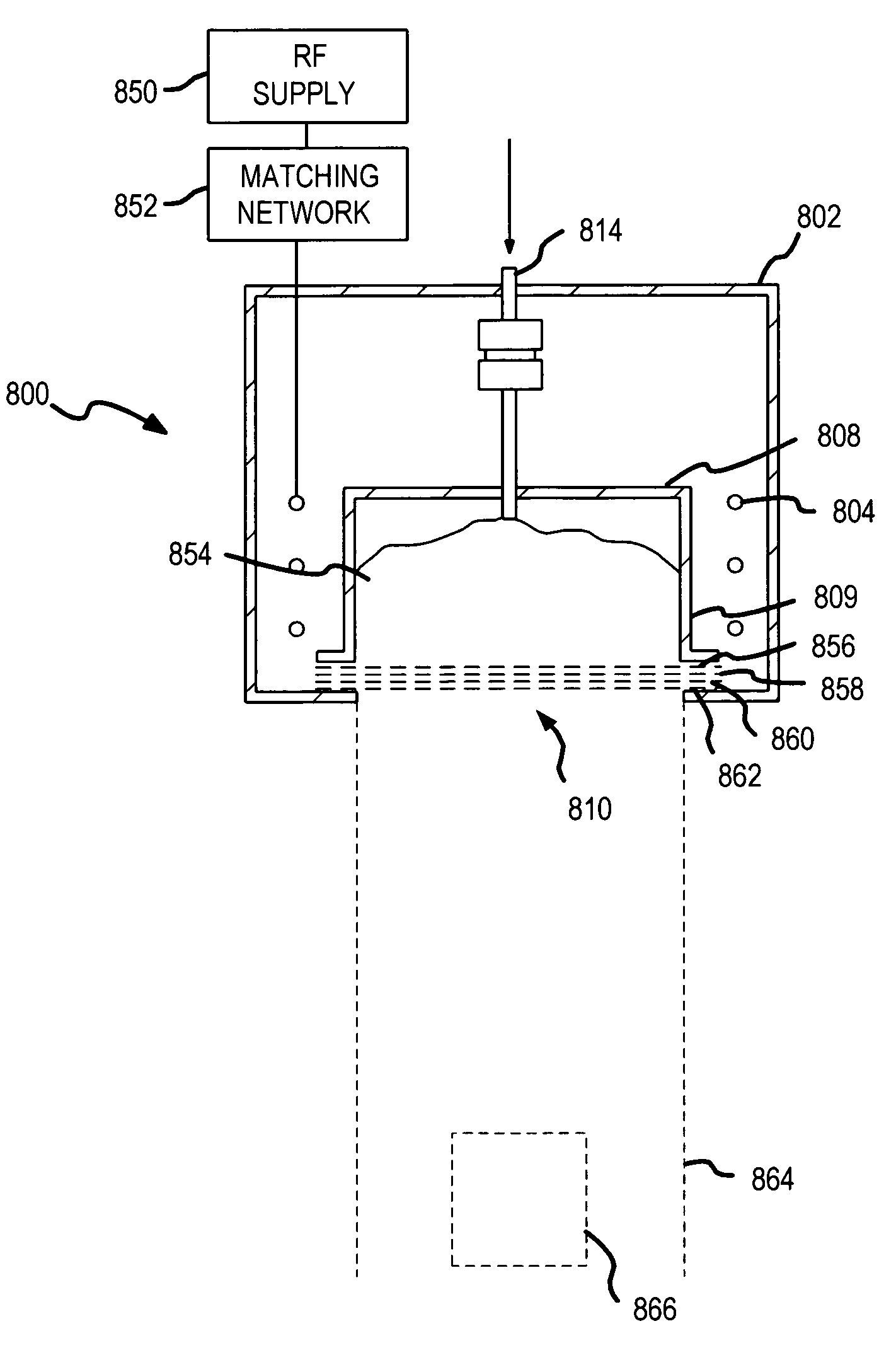

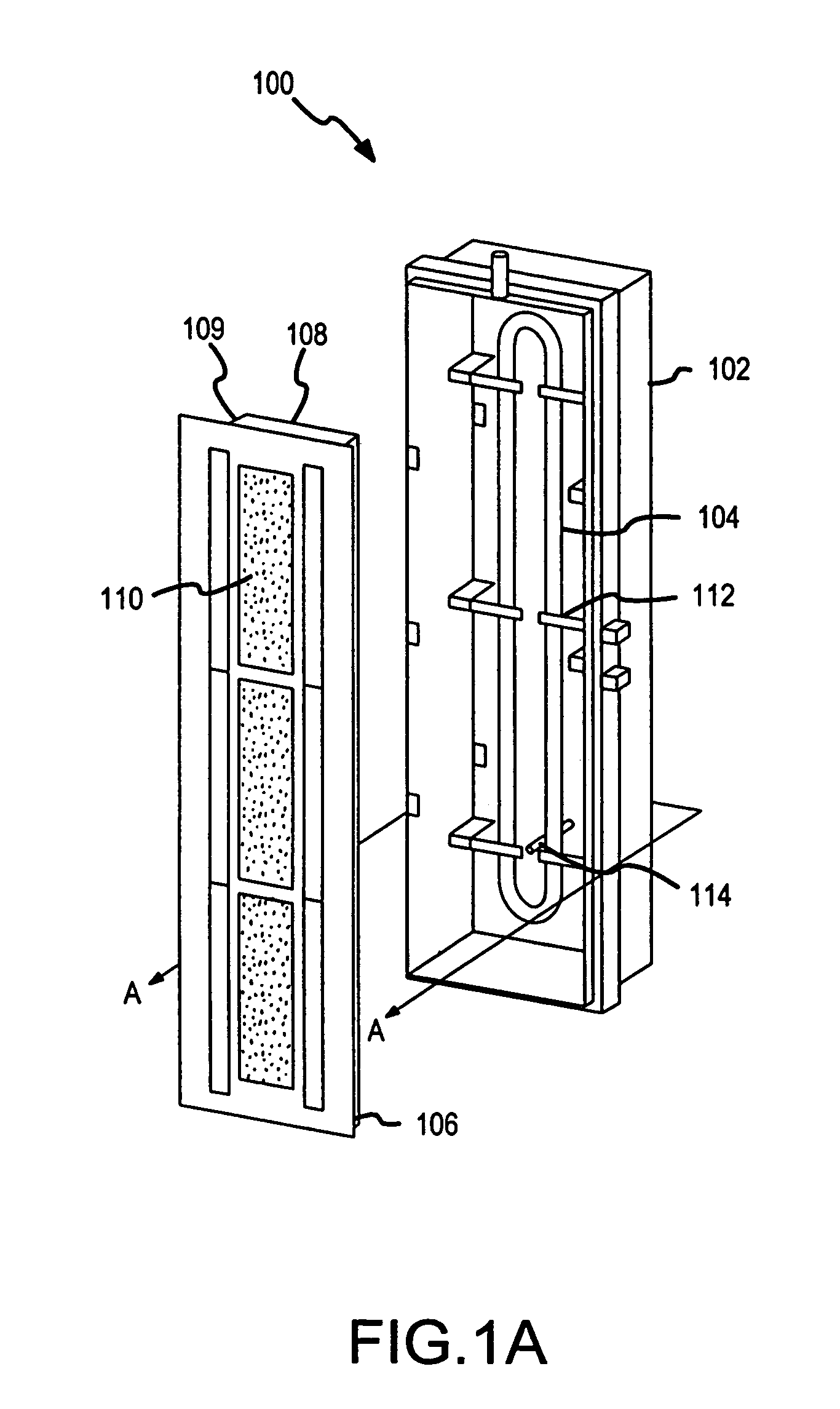

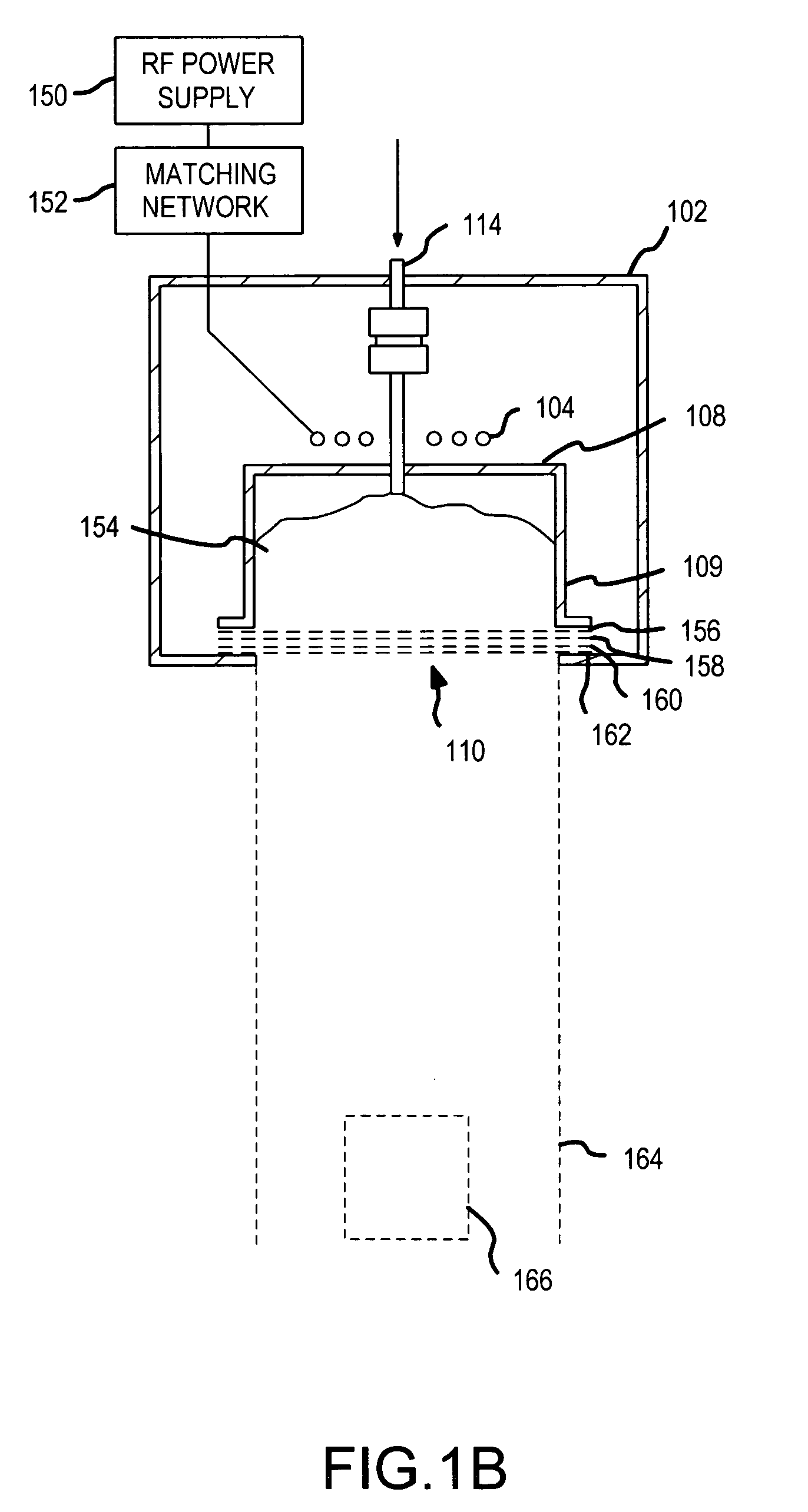

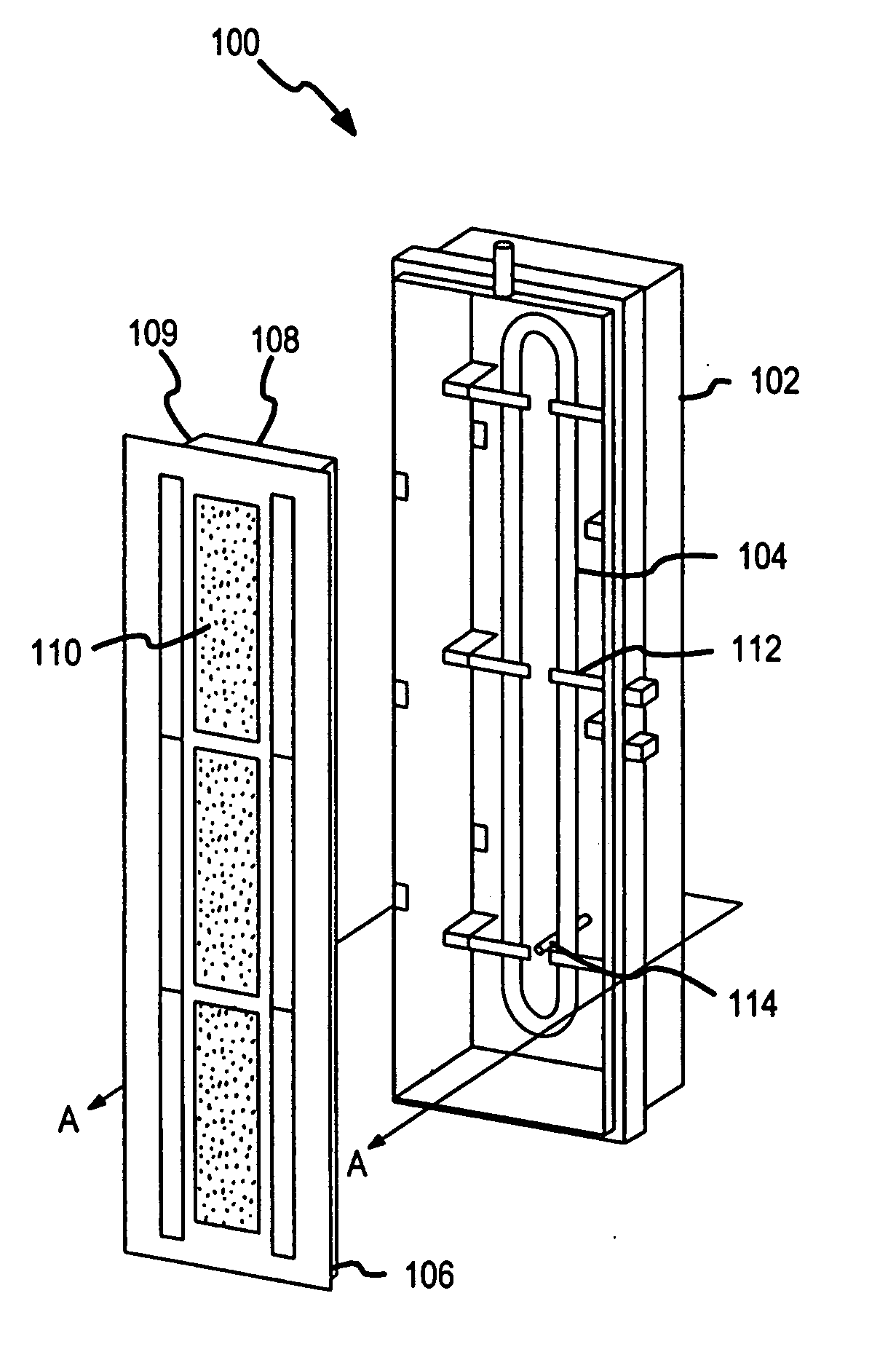

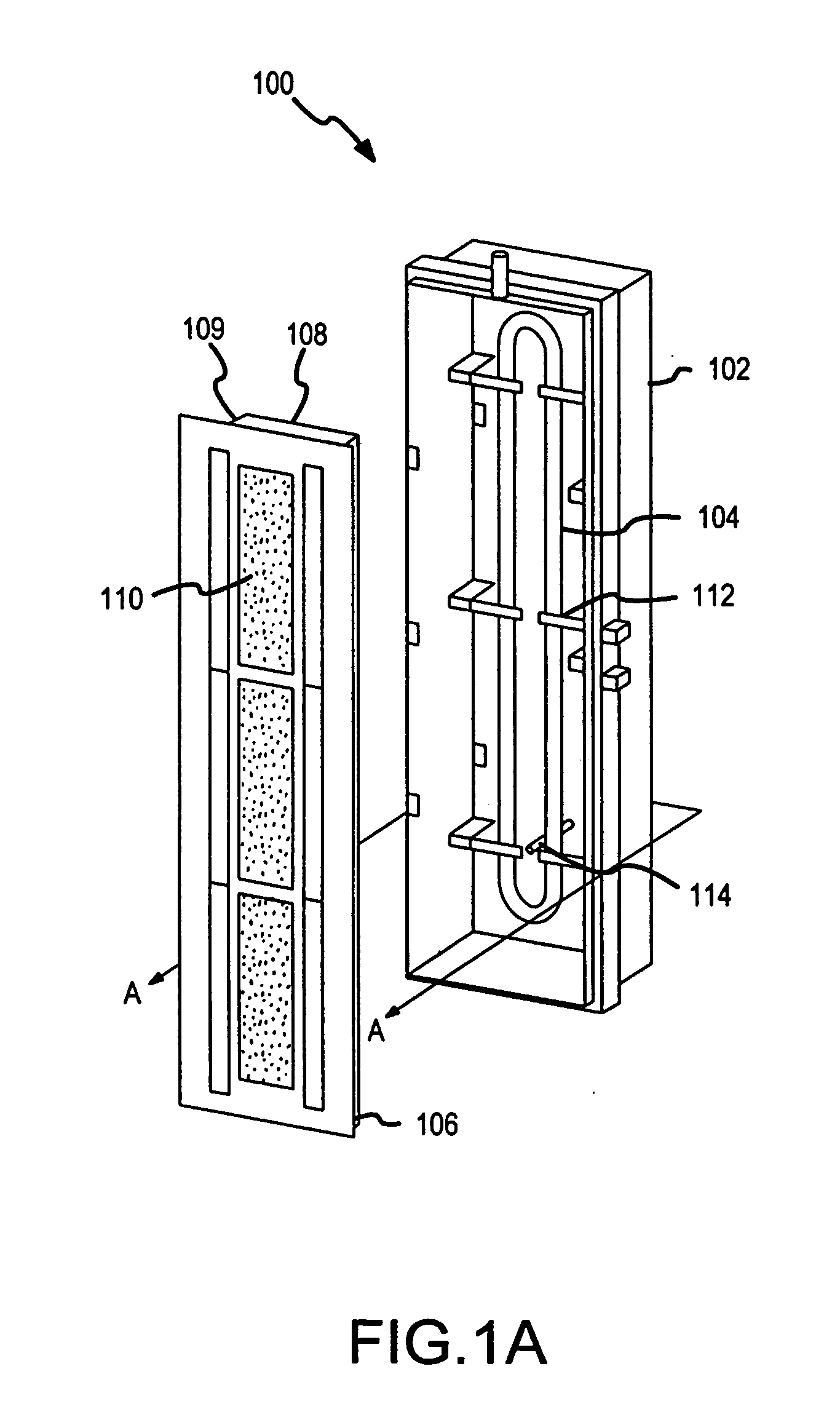

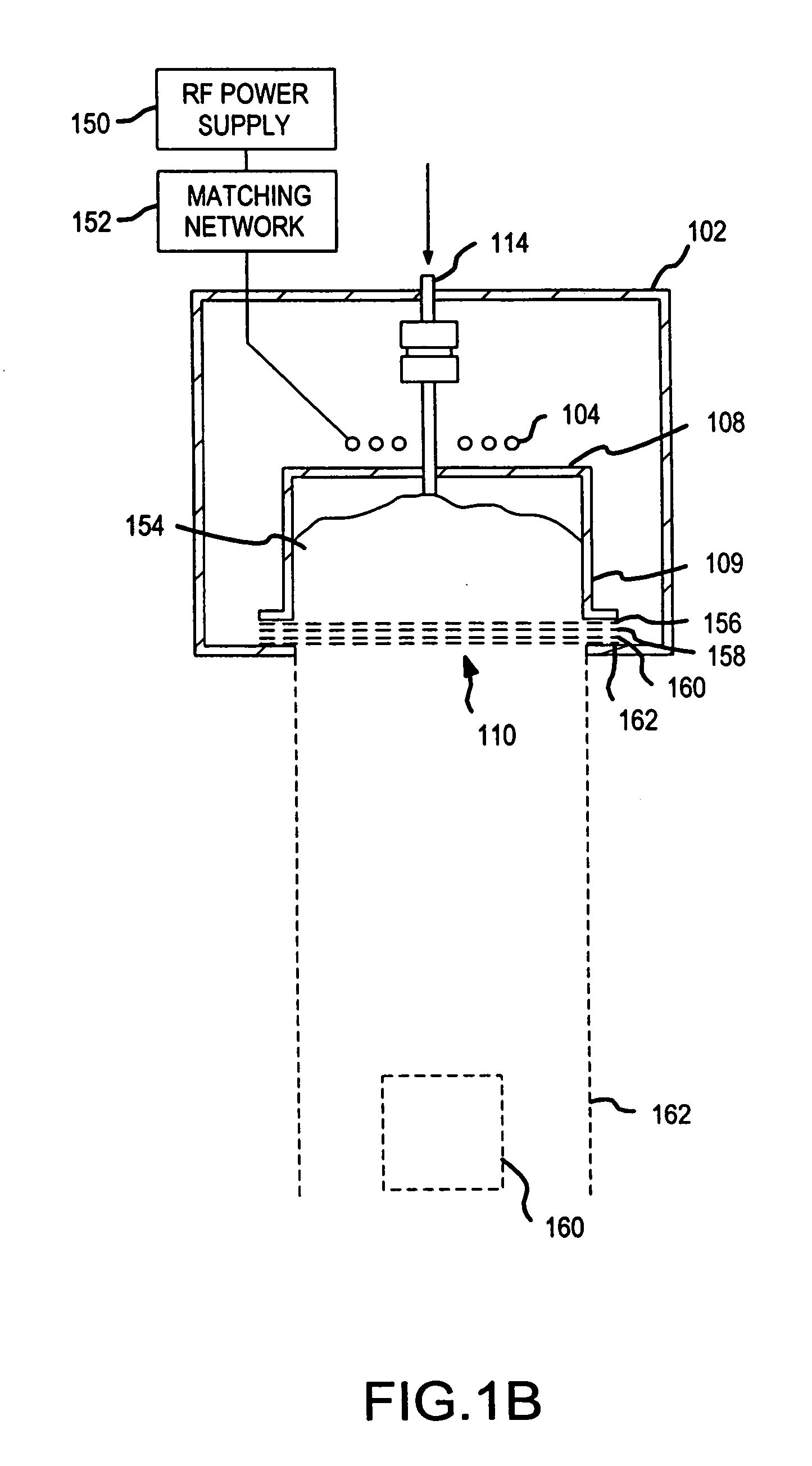

Multi-grid ion beam source for generating a highly collimated ion beam

InactiveUS7045793B2Stability-of-path spectrometersBeam/ray focussing/reflecting arrangementsMomentumIon beam

A multi-grid ion beam source has an extraction grid, an acceleration grid, a focus grid, and a shield grid to produce a highly collimated ion beam. A five grid ion beam source is also disclosed having two shield grids. The extraction grid has a high positive potential and covers a plasma chamber containing plasma. The acceleration grid has a non-positive potential. The focus grid is positioned between the acceleration grid and the shield grid. The combination of the extraction grid and the acceleration grid extracts ions from the plasma. The focus grid acts to change momentum of the ions exiting the acceleration grid, focusing the ions into a more collimated ion beam than previous approaches. In one embodiment, the focus grid has a large positive potential. In another embodiment, the focus grid has a large negative potential.

Owner:VEECO INSTR

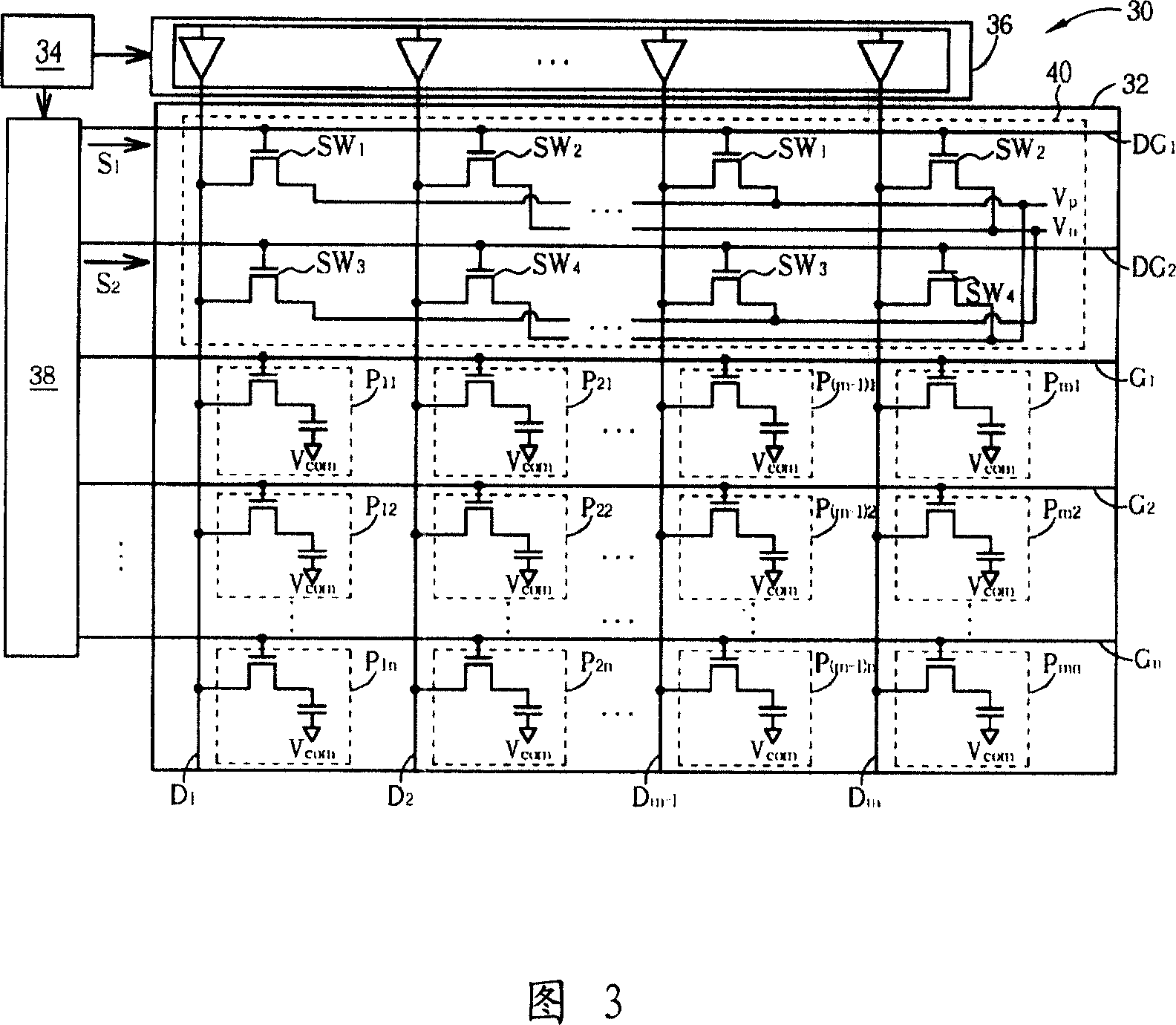

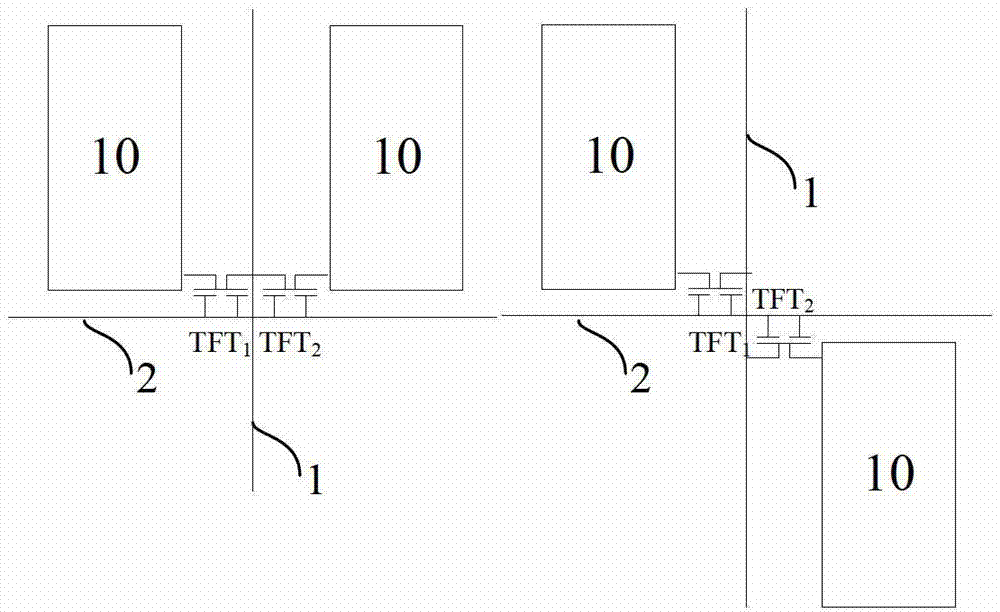

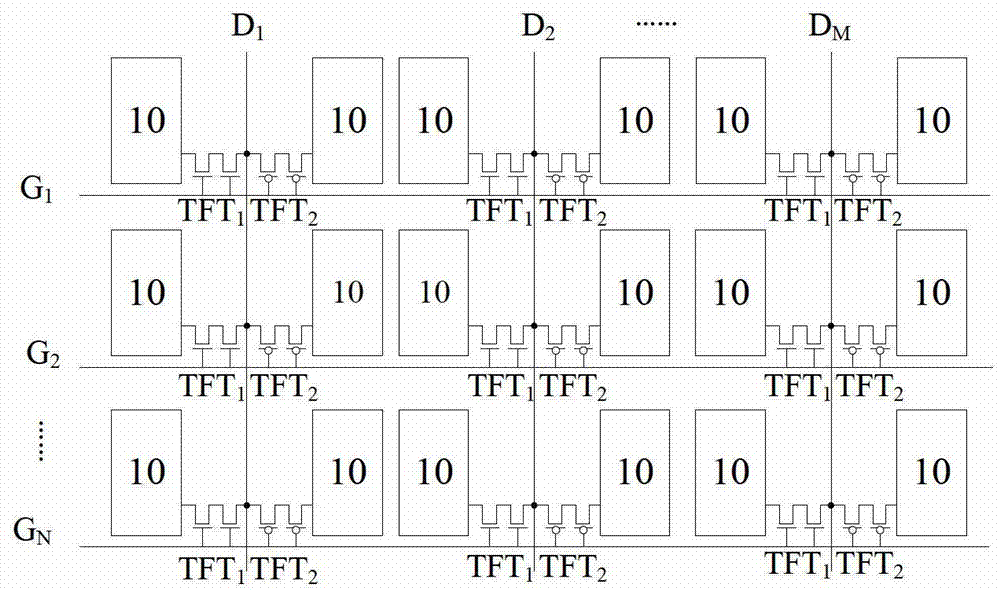

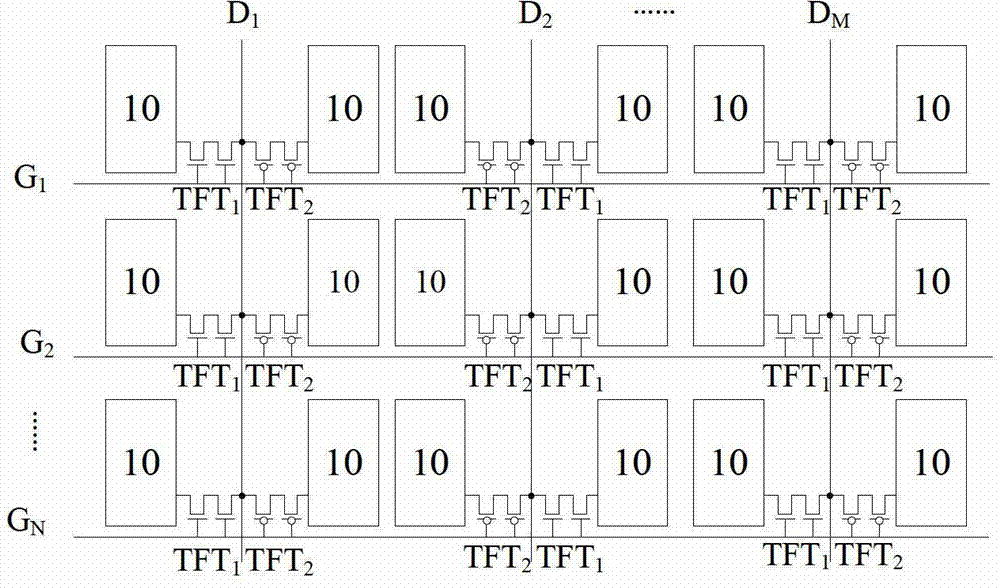

Array substrate, display device and drive method thereof

InactiveCN102832212ASuppress leakage currentAchieve beneficial effectsTransistorStatic indicating devicesDisplay deviceDrain current

The invention discloses an array substrate, a display device and a drive method thereof, relating to the technical field of display. The array substrate comprises grid lines, data lines and pixel electrodes, and also comprises two pixel switches with multi-gate structures, wherein the pixel switches are arranged on cross joints of the grid lines and the data lines, one pixel switch is opened by a positive voltage of a grid, the other one pixel switch is opened by a negative voltage of the grid, the two pixel switches with multi-grid structures on the cross joint of one grid line and one data line are used for driving two pixel electrodes arranged on two sides of the data line and connected with the data line; and all grids of the two pixel switches with multi-grid structures on the cross joint of one grid line and one data line are connected with the grid line. Because the pixel switch opened by the negative voltage of the grid and the pixel switch opened by the positive voltage of the grid are of a multi-grid structure, according to the array substrate provided by the invention, a leak current can be effectively inhibited.

Owner:BOE TECH GRP CO LTD +1

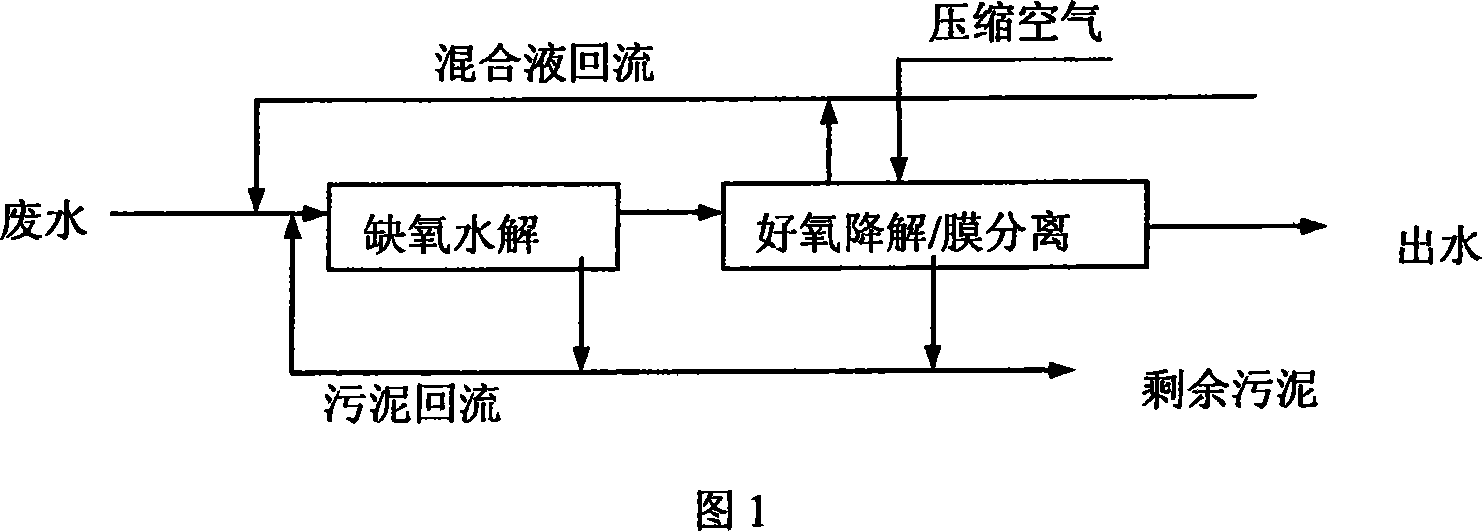

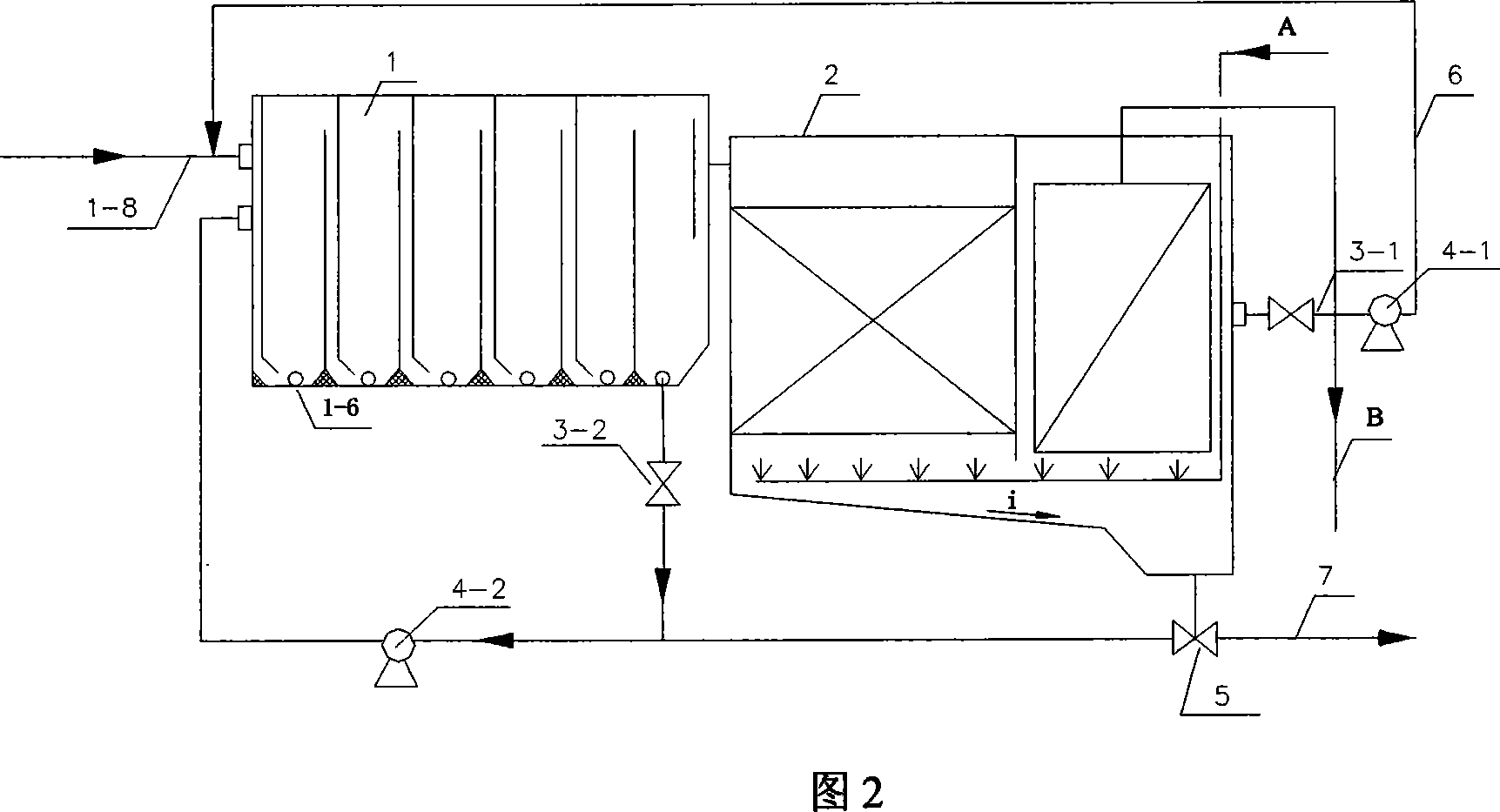

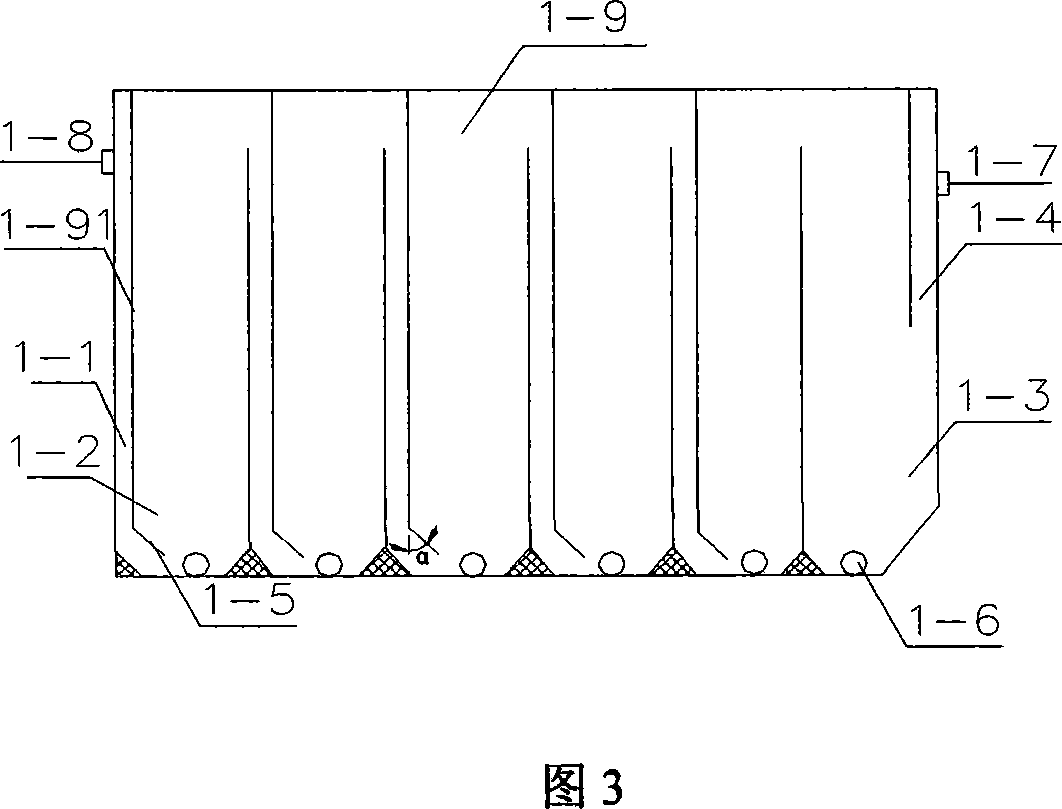

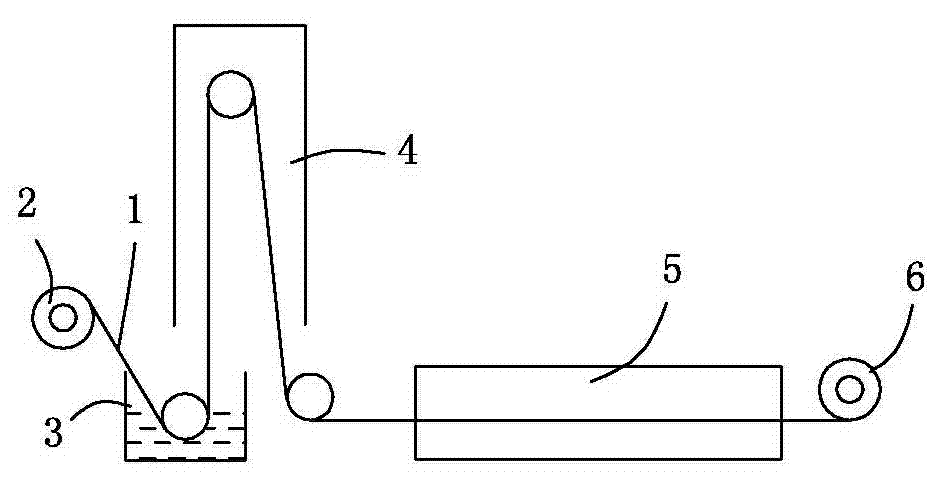

Equipment and method for treating wastewater difficult to be degraded by biology method of hydrolysis composite membrane

InactiveCN101050042AEnsure processing performanceClear functionWater contaminantsWater/sewage treatment bu osmosis/dialysisSludgeWastewater

This invention relates to apparatus and method for treating wastewater by hydrolysis-composite membrane biological method. The apparatus comprises: a multi-grid hydrolysis reactor and a composite membrane bioreactor. The method comprises: (1) introducing wastewater into the multi-grid hydrolysis reactor, and hydrolyzing in an anaerobic condition; (2) introducing the hydrolyzed wastewater into the contact oxidation region of the composite membrane reactor, and performing aerobic biological treatment; (3) introducing wastewater into the membrane separation region of the composite membrane bioreactor, and performing further aerobic biological treatment; (4) returning the sludge produced in the multi-grid hydrolysis reactor and the composite membrane bioreactor to the flow-guide region.

Owner:SOUTHEAST UNIV

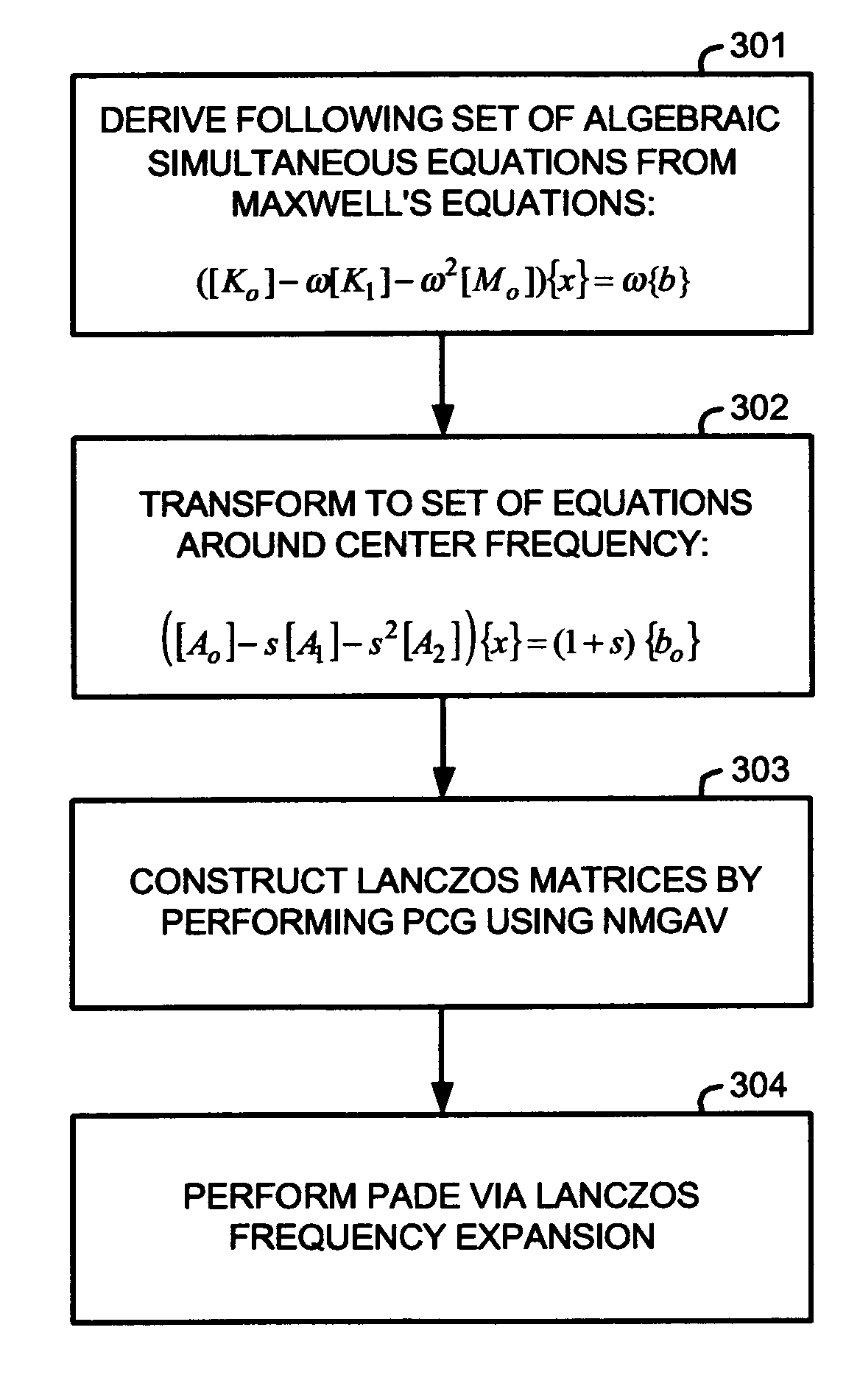

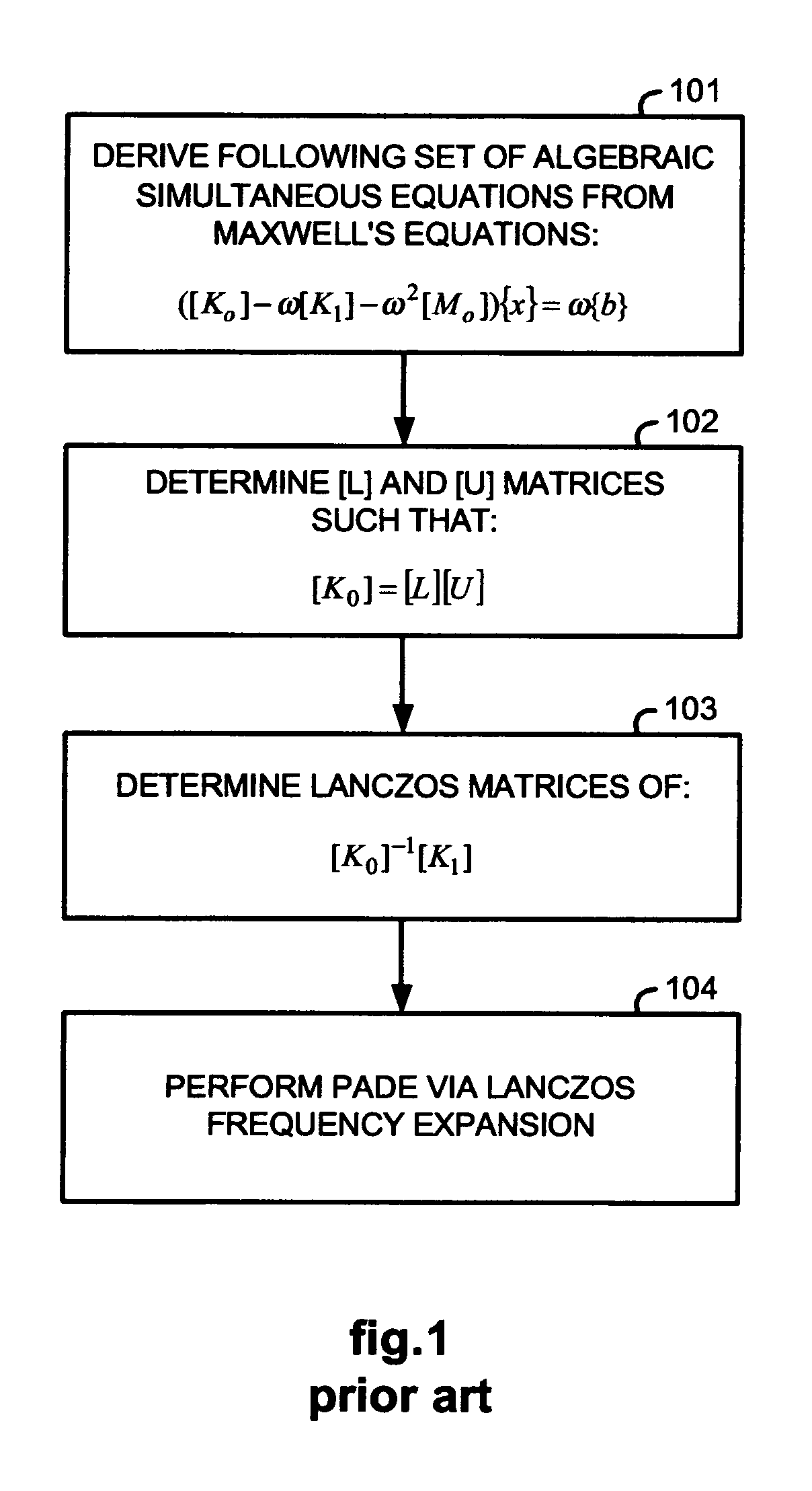

Method for determining electrical and magnetic field effects

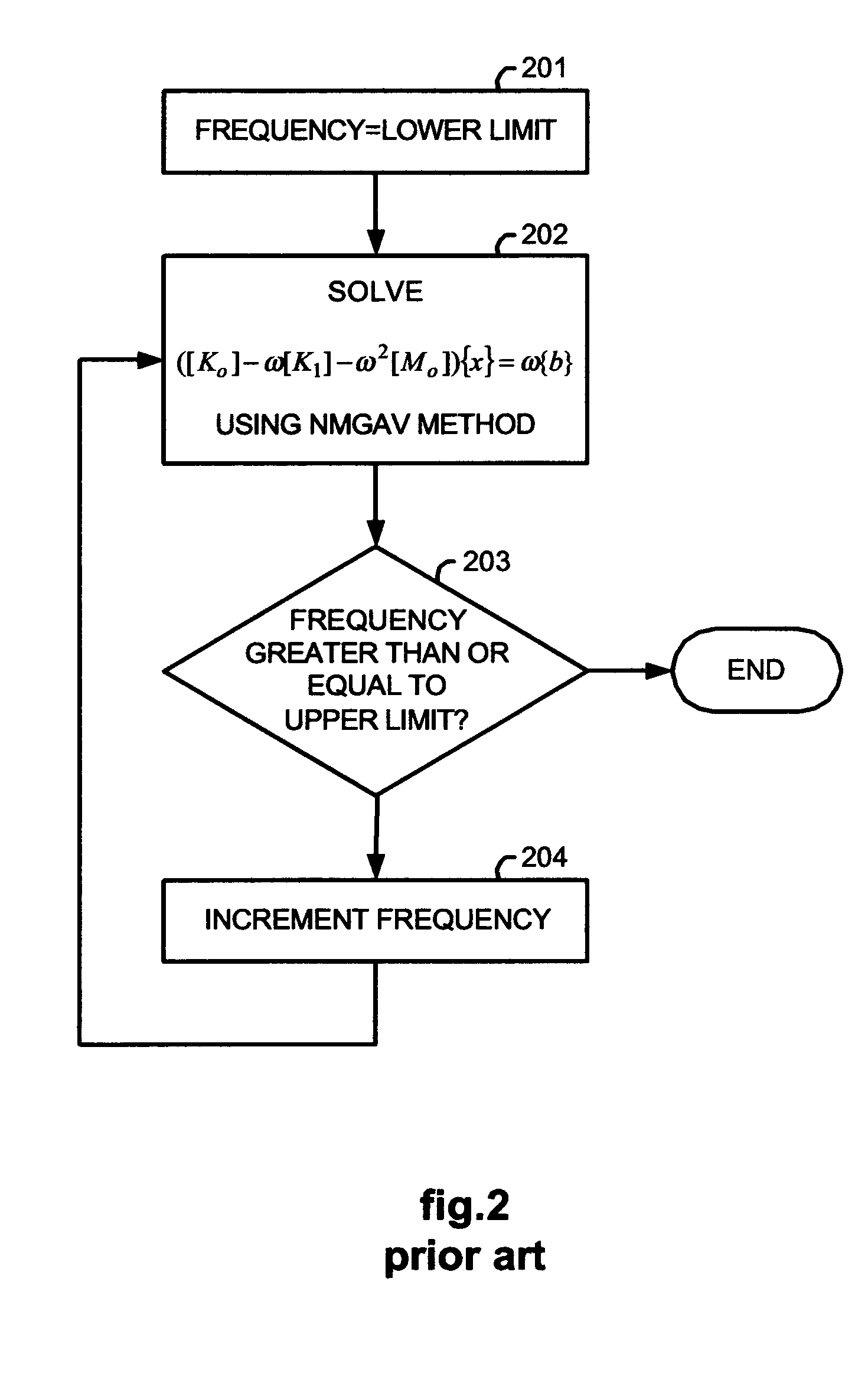

InactiveUS20050197808A1Computation using non-denominational number representationComplex mathematical operationsMatrix decompositionScalar potential

A method for determining electrical and magnetic field effects determines Lanczos matrices by performing a preconditioned conjugate gradient method using a nested multi-grid, vector and scalar potential preconditioner so that Pade via Lanczos frequency expansion may be used to determine the electrical and magnetic field effects over a frequency range without having to perform computationally slow and memory intensive matrix decomposition.

Owner:OPTIMAL CORP

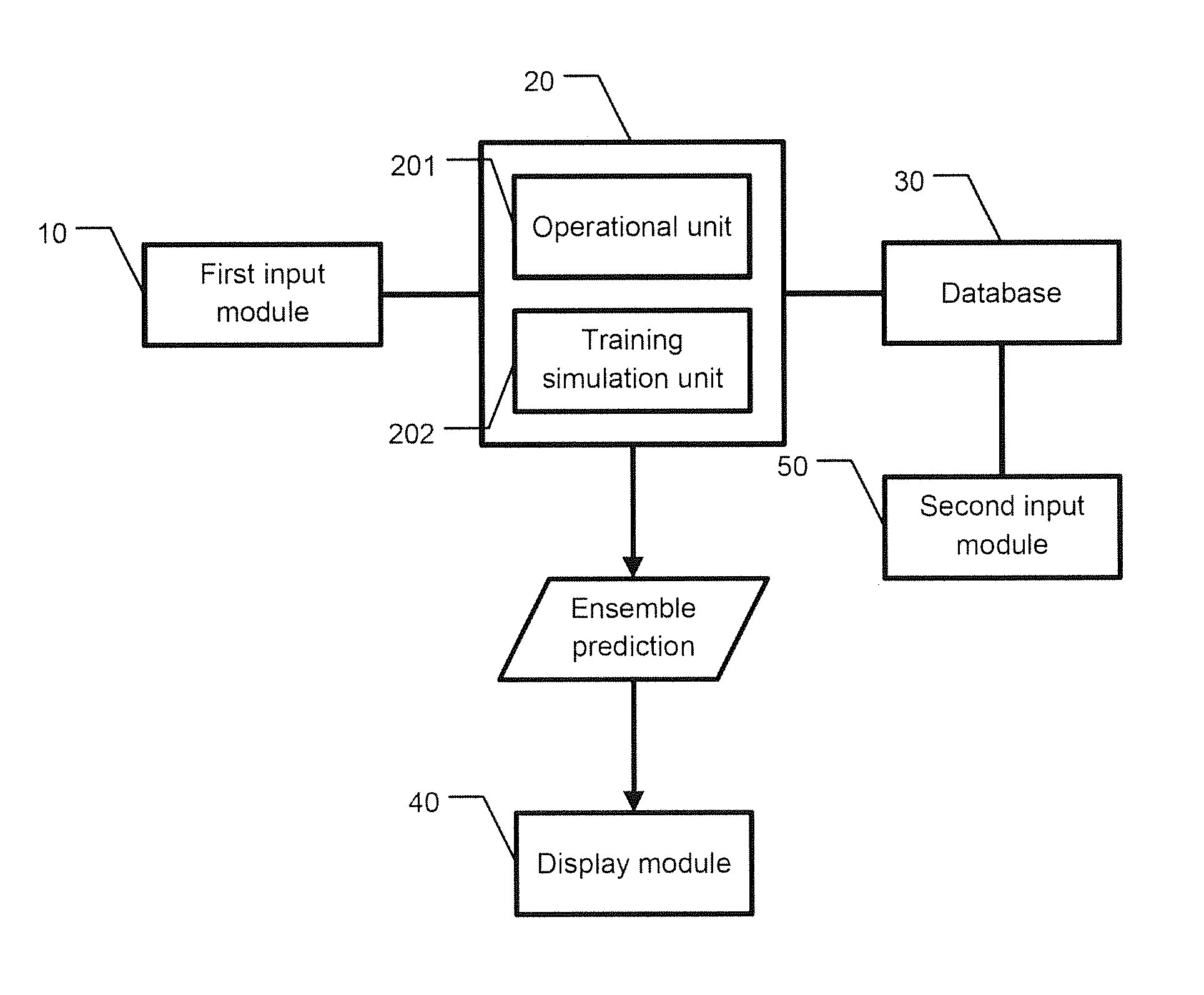

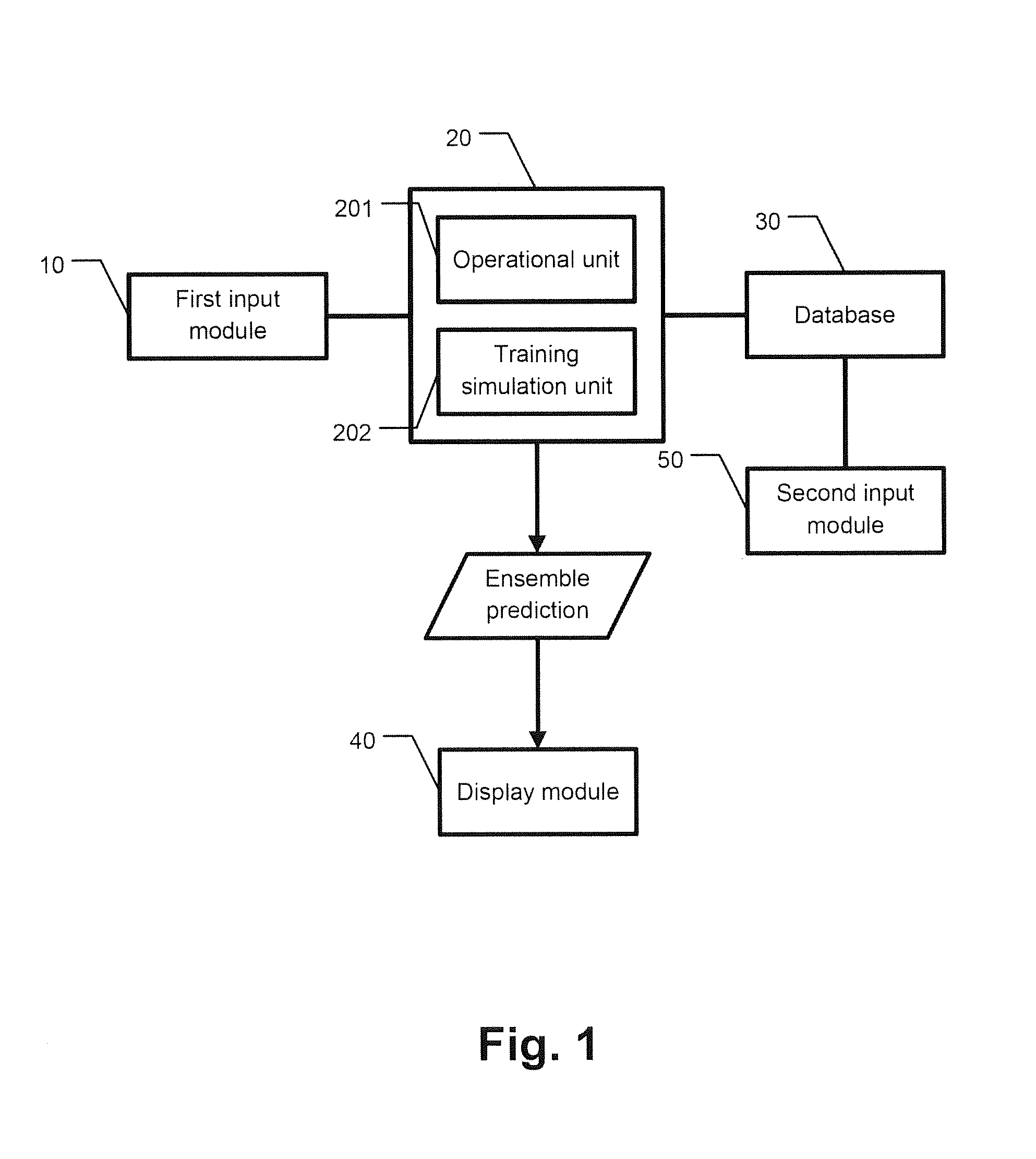

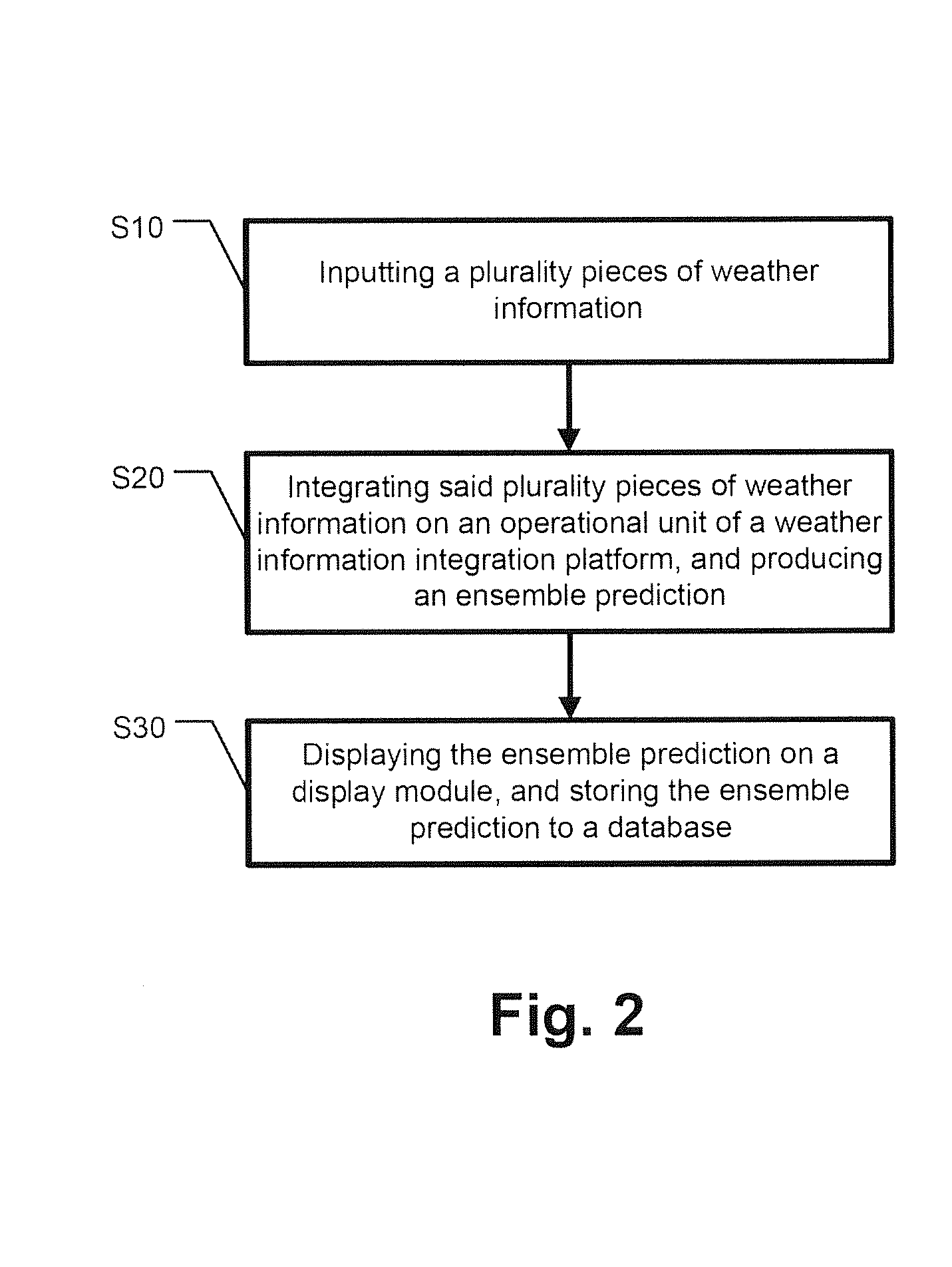

Ensemble wind power forecasting platform system and operational method thereof

InactiveUS20140336934A1Improve predictabilityImprove the level ofWeather condition predictionSpecial data processing applicationsElectricityNumerical weather prediction

The present invention relates to an ensemble wind power forecasting platform system and the operational method thereof. According to the present invention, a great amount of wind energy predictions from multiple sources, including numerical weather prediction information, multi-grid prediction information, and multiple wind-energy predicting methods, are integrated and processed for providing users with an ensemble prediction. Thereby, the trend and the possible variation range of the output capacity of a wind farm can be mastered. In addition, by means of the integration platform, the predicted results by different prediction modes can be compared and the history data and the predicted results can be compared as well, which can be used as a basis for improving modes for prediction-mode developers.

Owner:INST NUCLEAR ENERGY RES ROCAEC

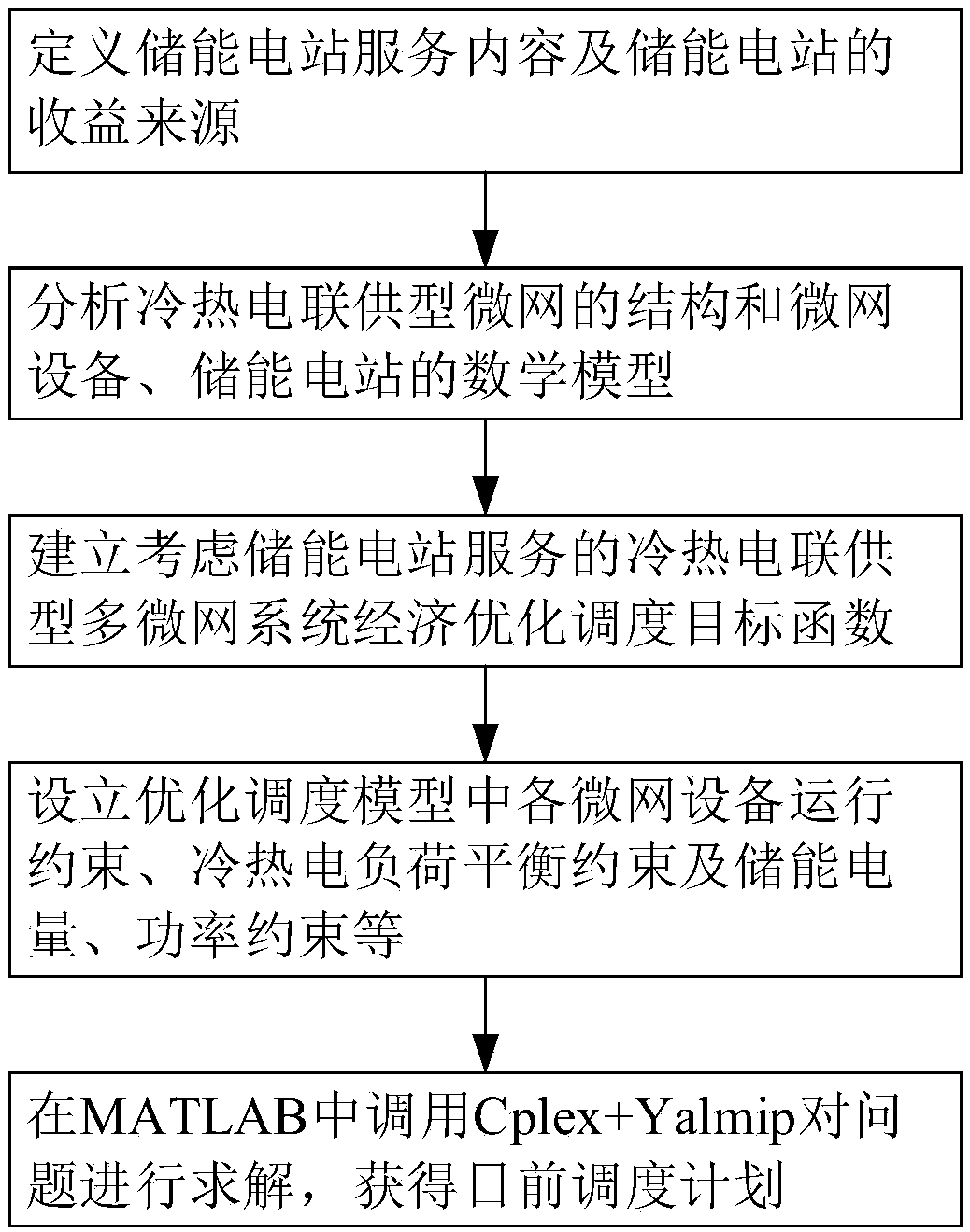

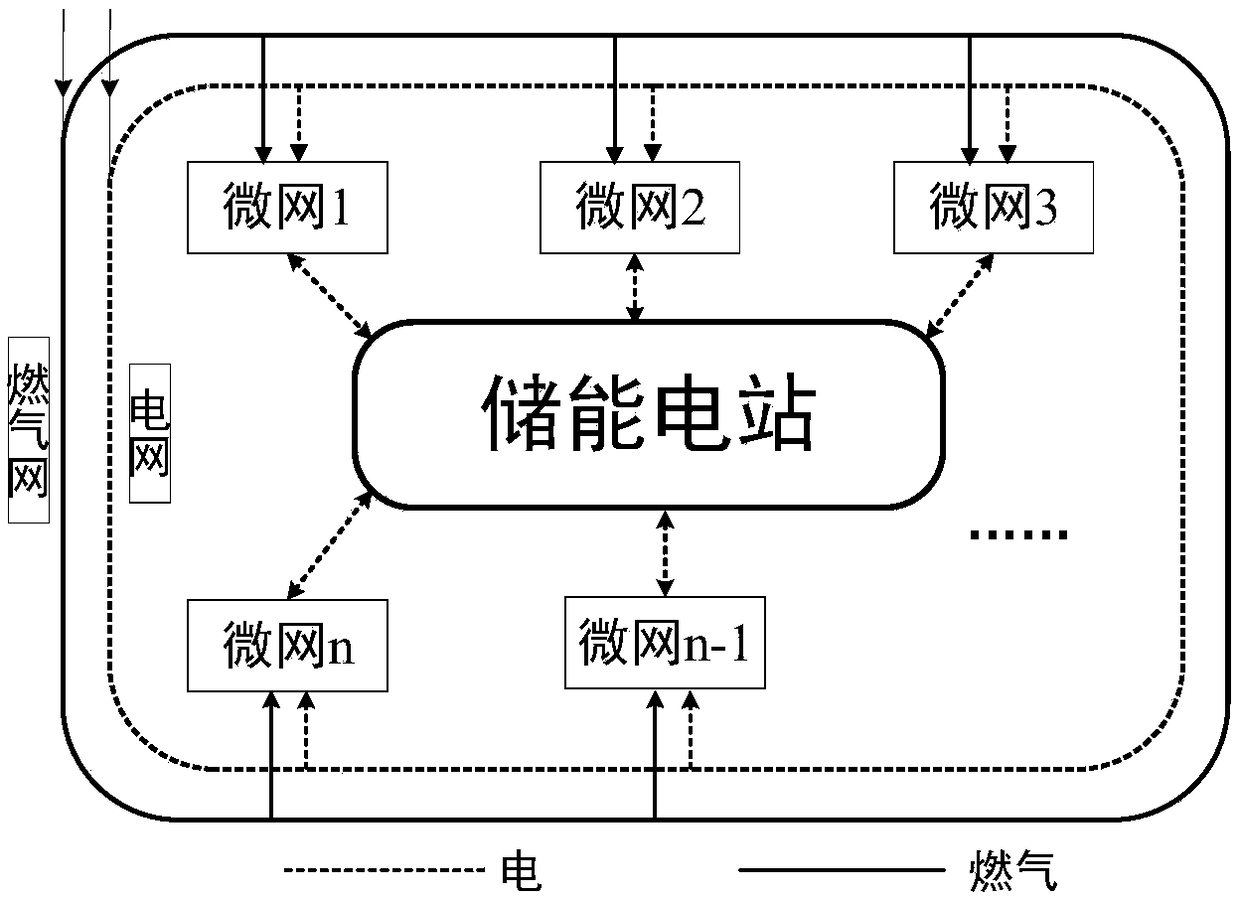

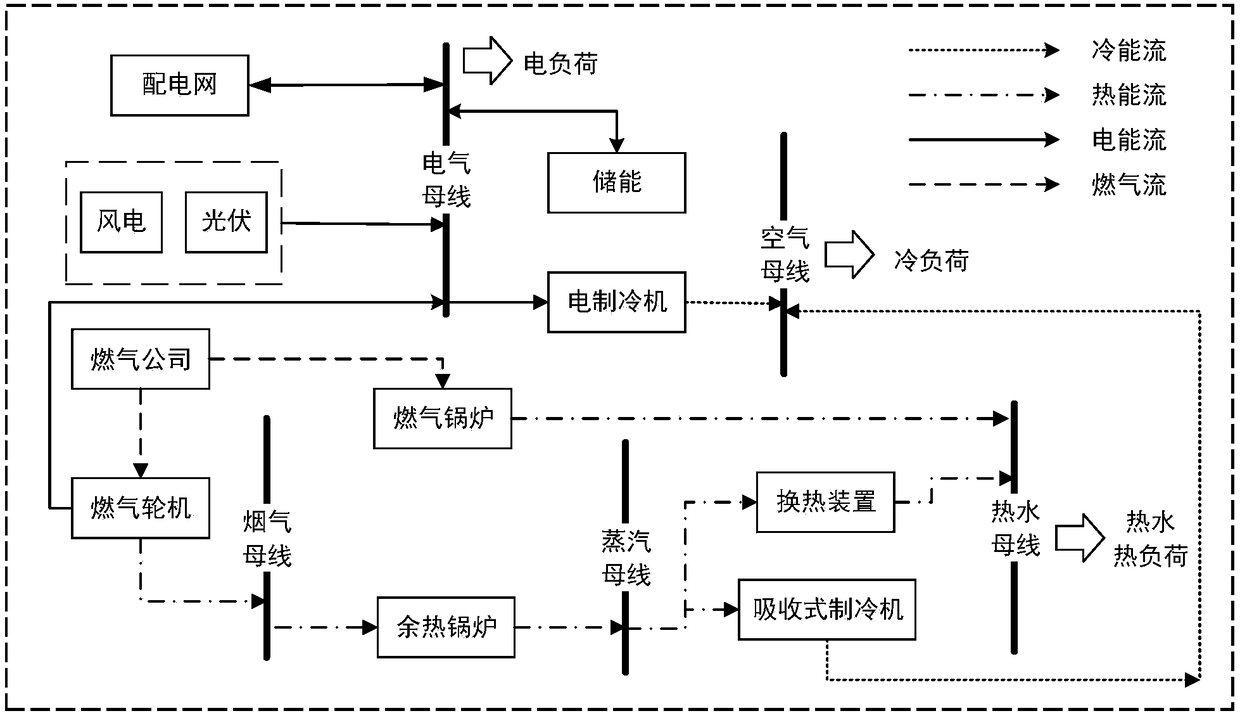

Cooling-heating-power combined supply type multi-microgrid system and economic optimal dispatching method thereof

InactiveCN109190859AAvoid Curtailment ScenariosMeet the demand of cooling, heating and electrical loadsForecastingResourcesDaily operationMicrogrid

The invention discloses a cooling-heating-power combined supply type multi-microgrid system and an economic optimal dispatching method thereof. The system comprises an energy storage power station anda plurality of microgrids connected with the energy storage power station. The energy storage power station is provided with an energy management system of the energy storage power station, and the micro-grid is provided with an energy management system of the micro-grid. An electric tie line is set up between each micro-grid and the energy storage power station, and the electric bus bar of the micro-grid is connected with the electric tie line so as to be connected to the common connection point of the energy storage power station, so that the electric energy between the energy storage powerstation and each micro-grid flows mutually; the energy management system of the energy storage power station formulates the economic optimal dispatching plan of the multi-grid system of the combinedcooling, heating and power supply, and the micro-grid energy management system of each micro-grid executes the economic optimal dispatching plan, so as to realize the overall economic optimization ofthe operation of the multi-grid system of the combined cooling, heating and power supply. The method not only meets the demand of cooling and heating power load of each micro-grid, but also has no waste of cold, heat and power, and can significantly reduce the economic cost of daily operation.

Owner:STATE GRID JIANGSU ELECTRIC POWER CO ELECTRIC POWER RES INST +3

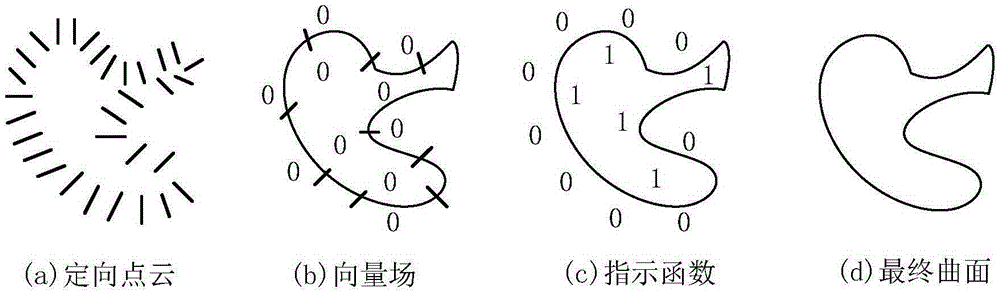

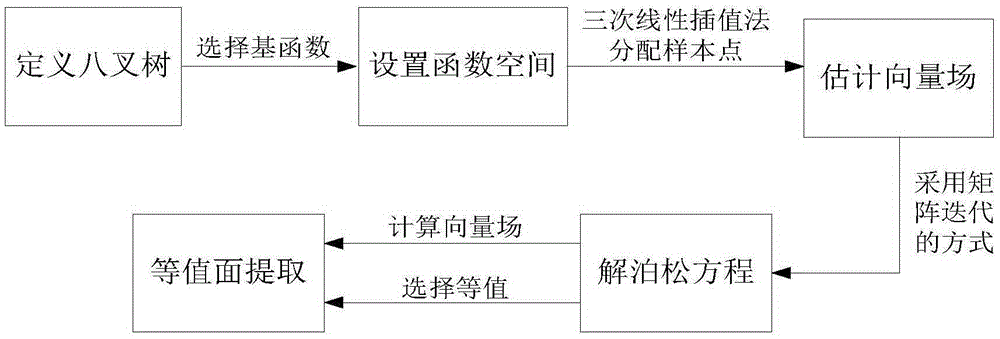

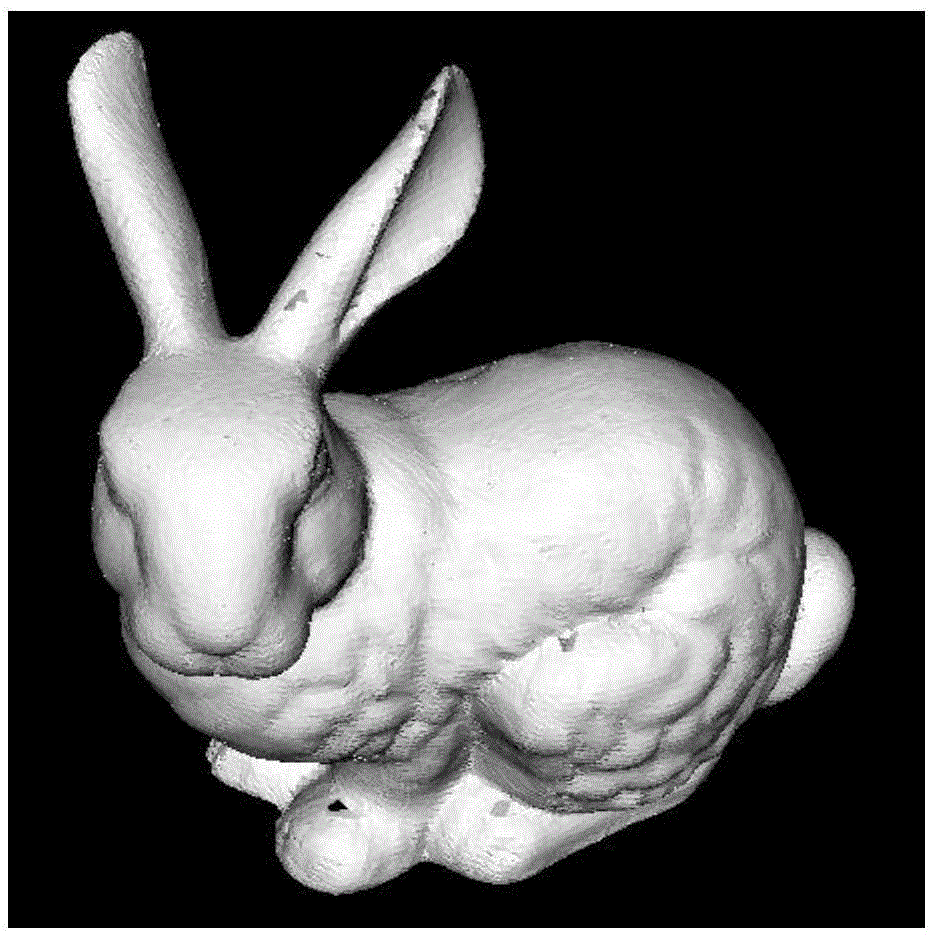

Complex structure point cloud processing algorithm bases on Poisson reconstruction

The invention discloses a complex structure point cloud processing algorithm bases on Poisson reconstruction. Curved surface reconstruction carried out through a point cloud processing technical method based on Poisson reconstruction adopts an indicator function to describe a curved surface; a vector field based on normal vector is constructed through Gaussian filtering; and a Poisson equation is solved through a multi-grid method to obtain a transition portion of the indicator function of directional point cloud to finish the curved surface reconstruction. The curved surface reconstruction technology based on Poisson is mainly formed by five parts: defining an octree, setting function space, estimating the vector field, solving the Poisson equation and extracting contour surface. With the fast development of a 3D laser scanning device, the point cloud obtaining technology also has considerable progress. The point cloud processing algorithm can be widely applied to the fields of reverse engineering, hybrid modeling, visual inspection, medical images and archaeological and cultural relic modeling and the like.

Owner:YANSHAN UNIV

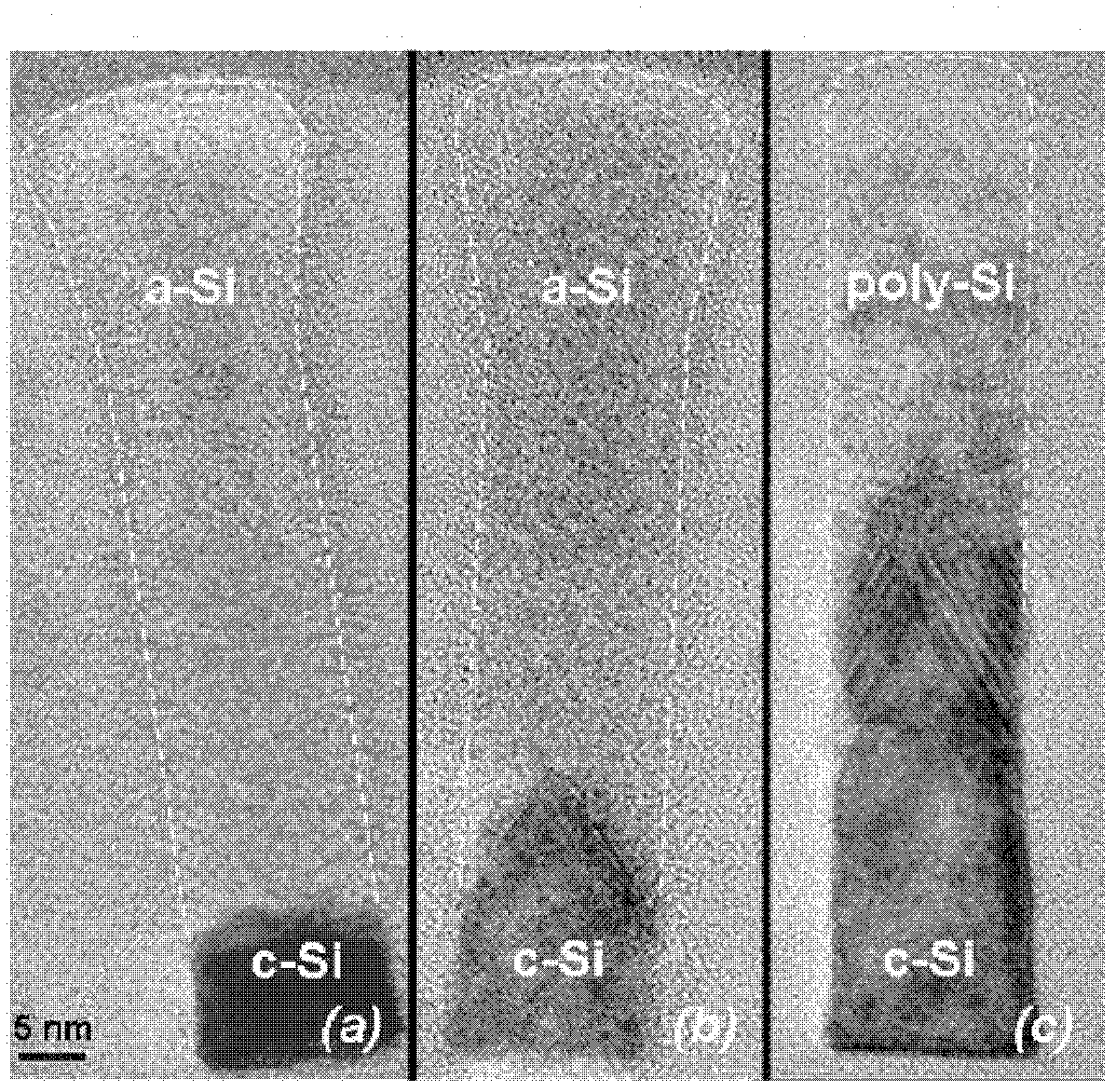

Multi-grid transistor and manufacturing method thereof

ActiveCN102881724AImprove performanceLower the altitudeSemiconductor/solid-state device manufacturingSemiconductor devicesSalicideSchottky barrier

The invention discloses a multi-grid transistor, which comprises a substrate, an oxide layer positioned on the substrate, a fin-shaped structure which is positioned on the oxide layer, is connected with the substrate and comprises a trench region and a source region and a drain region which are positioned at two ends of the trench region, a grid dielectric layer which is positioned on the fin-shaped structure and wraps the trench region, and a grid which is positioned on the oxide layer and the grid dielectric layer and is perpendicular to the fin-shaped structure. The multi-grid transistor is characterized in that the source region and the drain region consist of metal silicate. According to a semiconductor device and a manufacturing method thereof, the metal silicate is completely used as the source region and the drain region of the fin-shaped structure of the multi-grid transistor, so that source and drain serially connected resistance is effectively reduced, and the problem that a non-crystallized region cannot be crystallized after being quenched because of doping of a source and a drain is solved; and furthermore, doped ion gathering regions are arranged at interfaces between the trench region and the metal silicate, so that the Schottky barrier height is effectively reduced, and the device performance is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

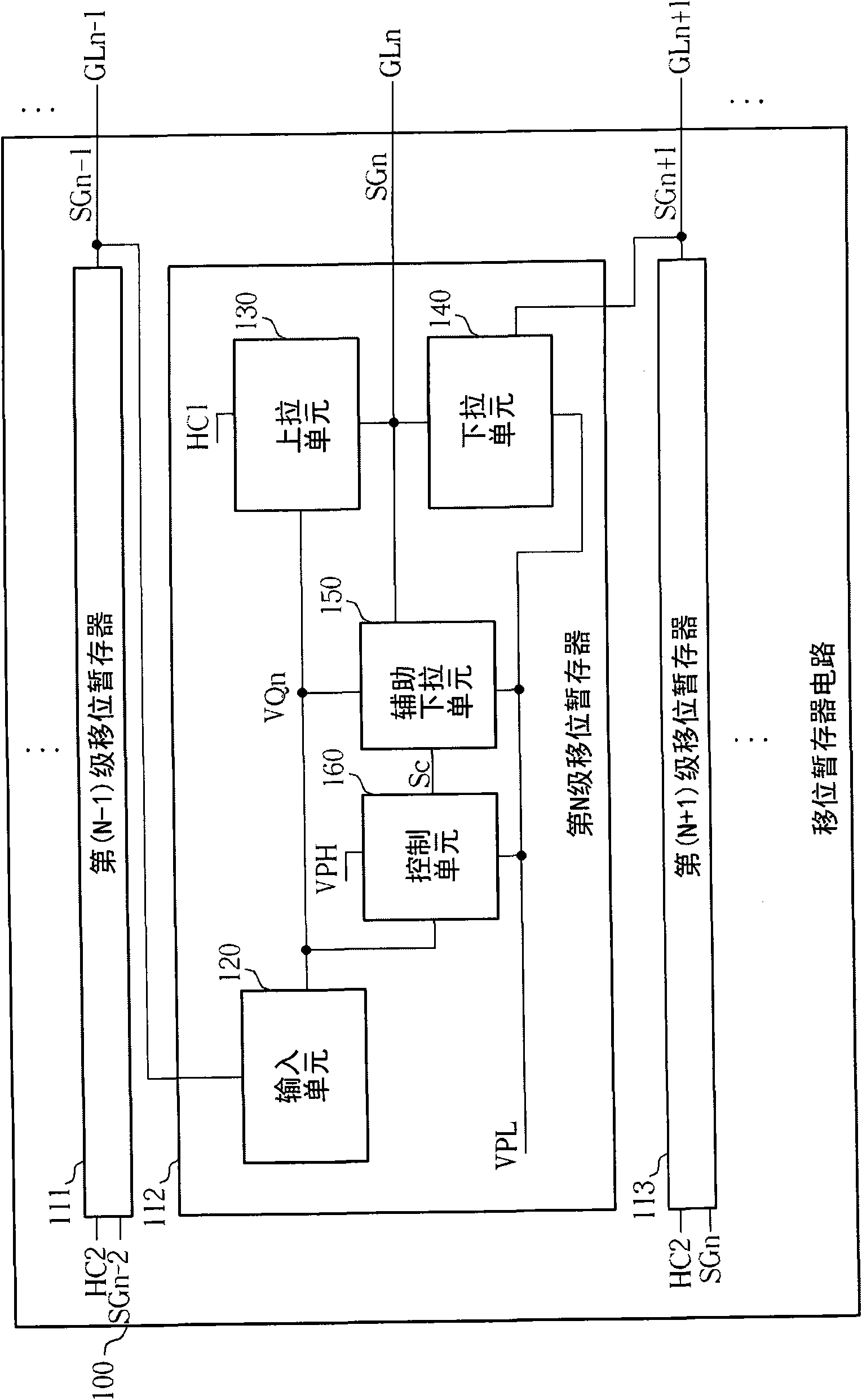

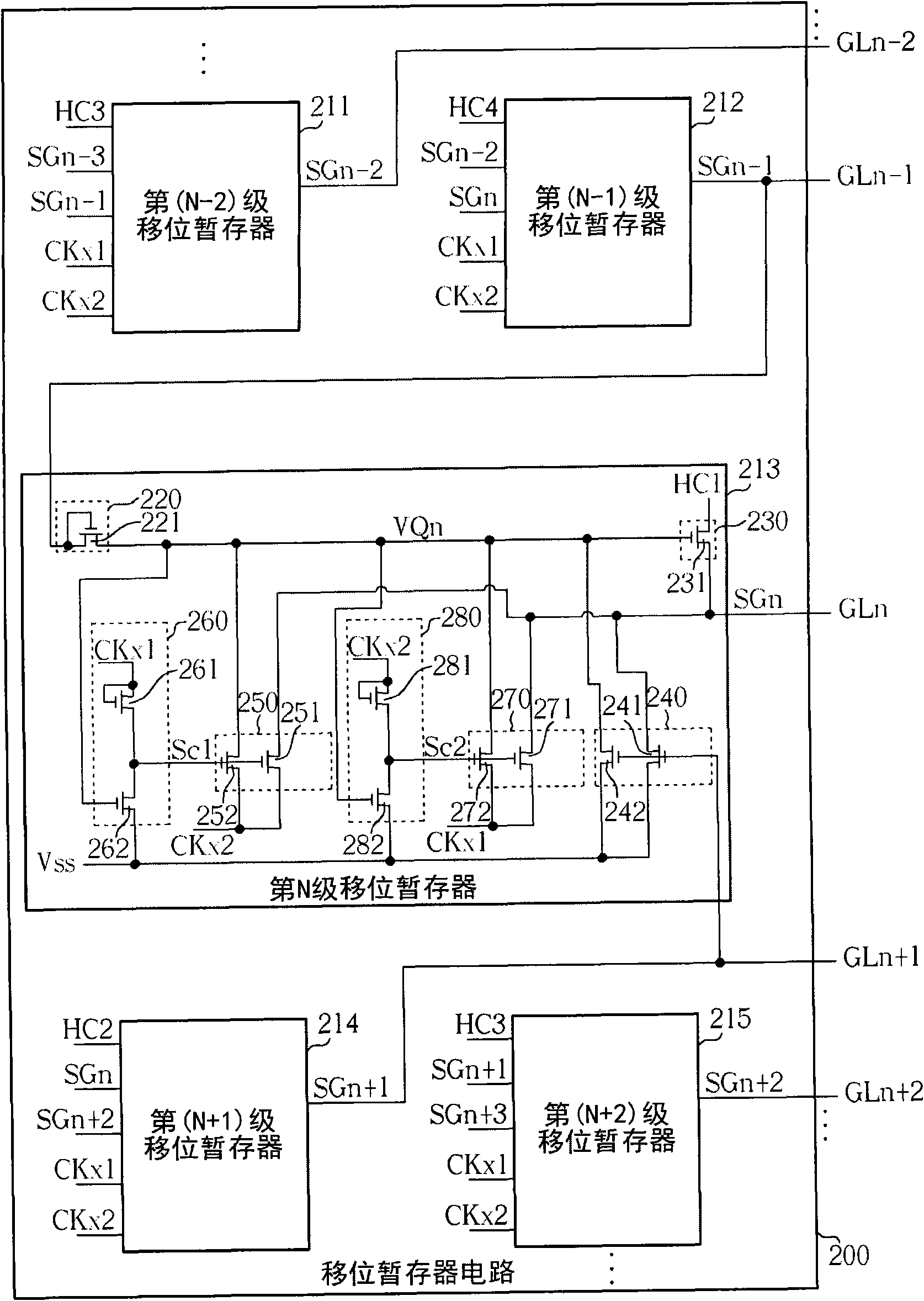

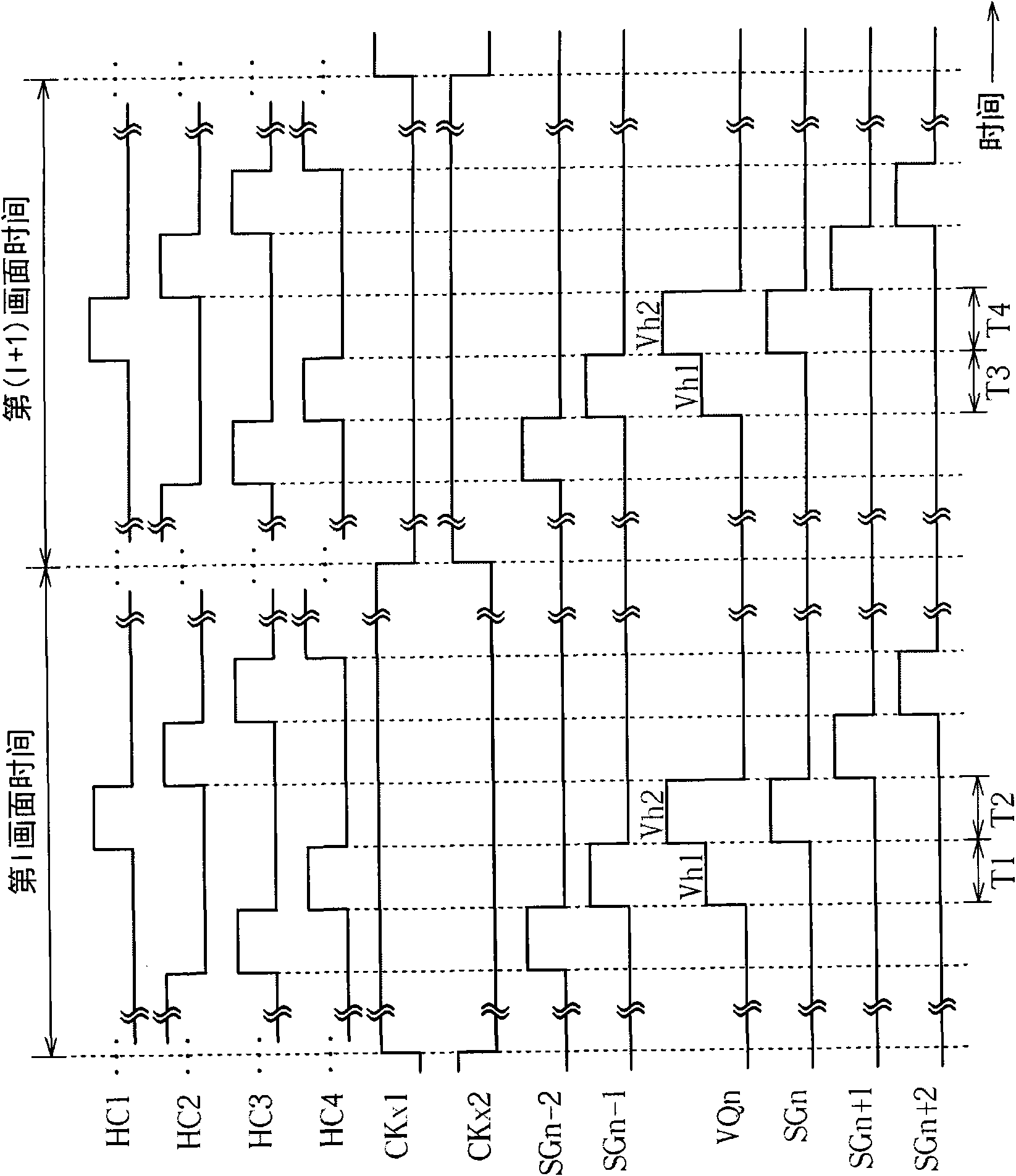

Shift registor circuit

A shift registor circuit comprises multi-stage shift registors in order to provide multi-grid signals. Each stage shift registor comprises an input unit, a pull-up unit, a pull-down unit, a control unit and an assistant pull-down unit, wherein, the input unit is used for outputting a driving control voltage based on a first input signal. The pull-up unit is used for pulling up corresponding grid signals on the basis of the driving control voltage and a system sequential pulse. The pull-down unit is applied for pulling down the corresponding grid signals and driving control voltages according to the first input signal. The control unit is used for generating a control signal according to a first auxiliary sequential pulse. The assisting pull-down unit is applied for pulling down corresponding grid signals and driving control voltages on the basis of the control signal and a second auxiliary sequential pulse which has a reversed phase relative to the first auxiliary sequential pulse.

Owner:AU OPTRONICS CORP

Micro-grid multi-inverter parallel voltage control method for droop control of robust power

ActiveCN102842921BIncrease the output resistanceSmall output resistanceSingle network parallel feeding arrangementsLow voltageVoltage reference

The invention discloses a micro-grid multi-inverter parallel voltage control method for droop control of robust power. The method comprises the following steps of: specific to each inverter in a micro-grid, computing and synthesizing an inverter output reference voltage by adopting a robust power droop controller; and introducing virtual complex impedance containing a resistance component and an inductive impedance component, and keeping inverter output impedance in a pure resistance state under a power frequency condition by adopting a multi-loop voltage control method based on virtual impedance and quasi-resonance PR (Proportional-Resonant) control, thereby realizing micro-grid multi-inverter parallel running and power equation, wherein the robustness of a micro-grid parallel system on numeric value computing errors, parameter drift, noise interference and the like is enhanced. Due to the adoption of the method, the defects of larger loop current of a parallel system, non-uniform power distribution and the like caused by the inductivity of the impedance output by inverters in the conventional droop method are overcome; and the method is suitable for multi-grid parallel uniform current control in a low-voltage micro-grid.

Owner:HUNAN UNIV

Method for fitting complex space curved surfaces

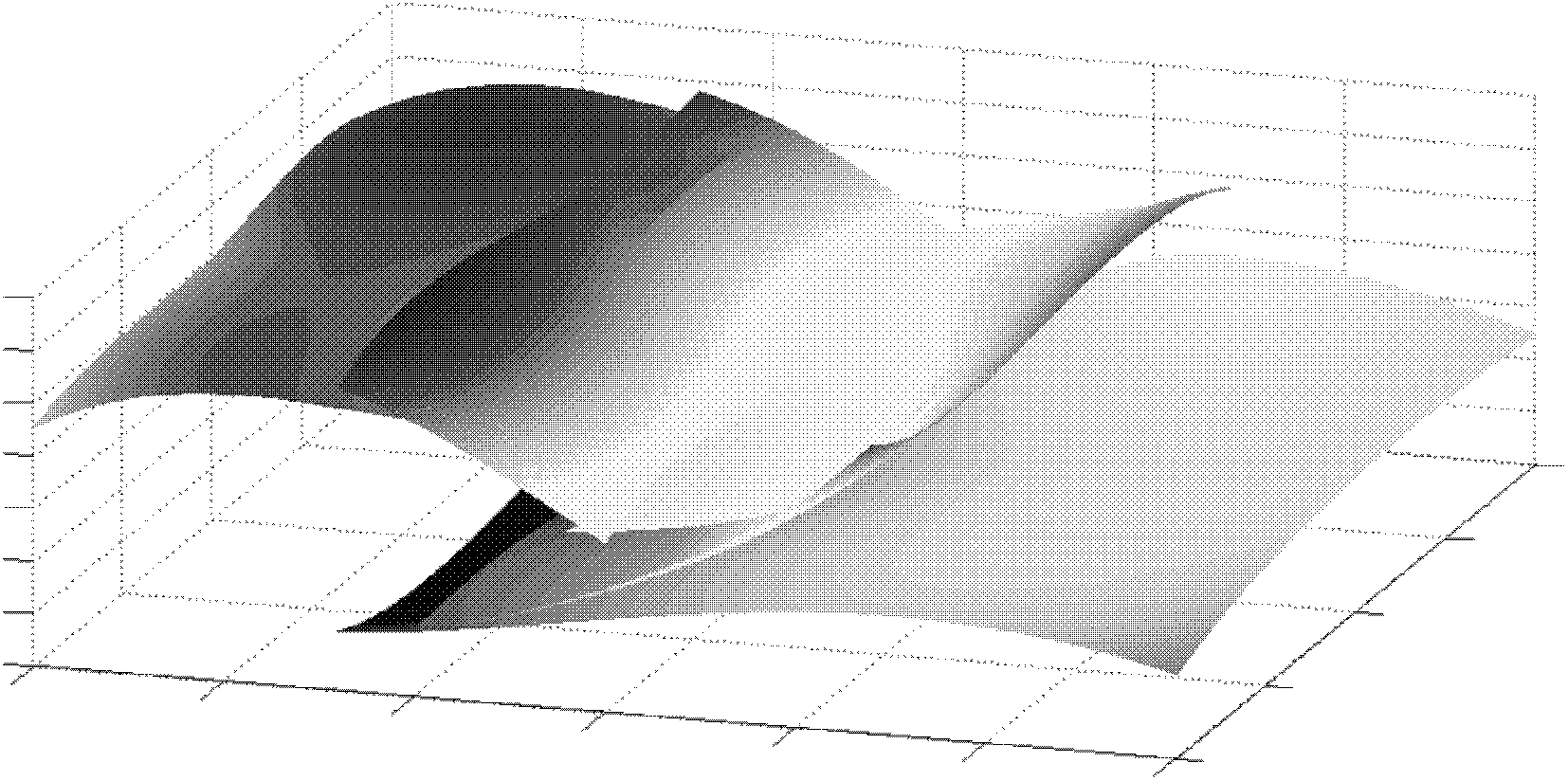

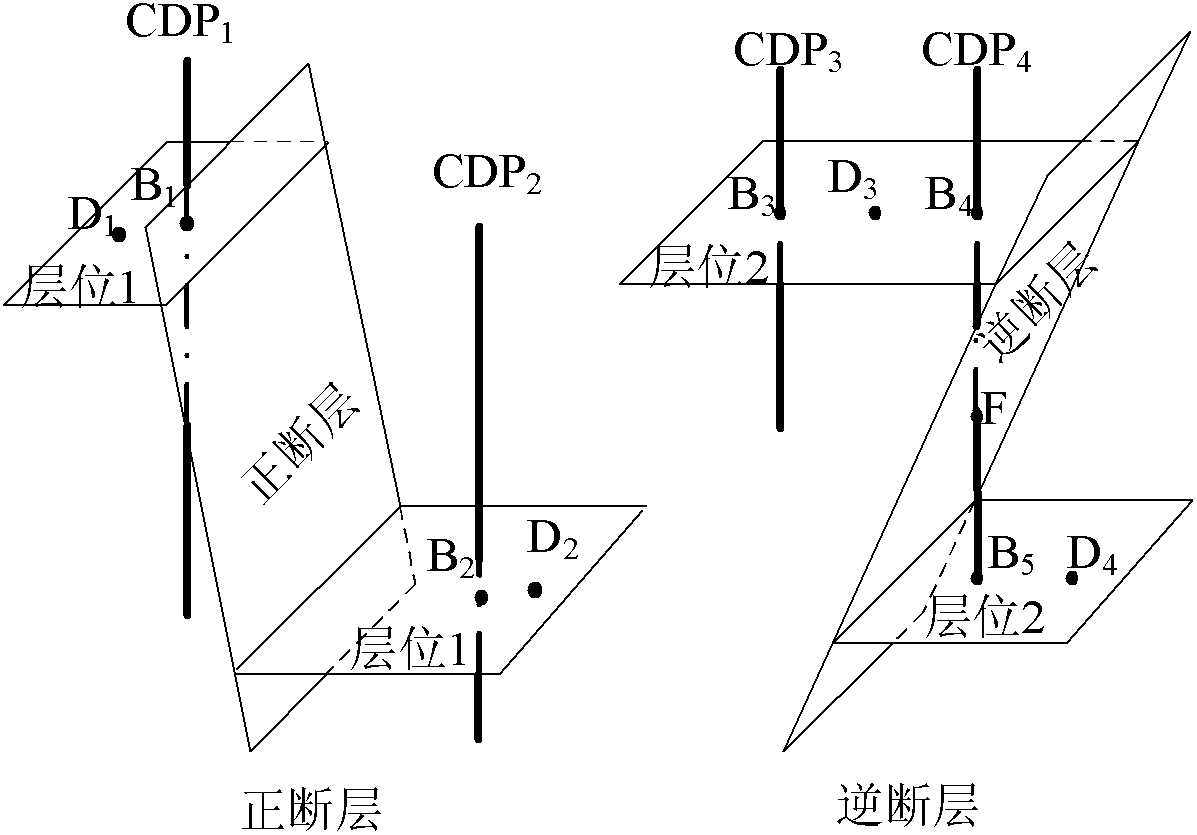

ActiveCN102222366AInterpolation EliminationRemove the effects of interpolation3D modellingNormal faultComputer science

The invention discloses a method for fitting complex space curved surfaces. The method eliminates the influence of a fault on the interpolation of grid points by fitting a fault projection of a plane to a fault surface in a space and by utilizing fault information as constraint conditions to carry out the interpolation on the grid points, thus solving the problem of gridding of the discontinuouscurved surfaces containing any complex fault (comprising normal fault and reverse fault), and achieving fast gridding through a fast search algorithm of rectangular multi-grid subdivisions so as to realize the fitting of the complex space curved surfaces containing any fault. The efficiency of the method is high.

Owner:四川智联科创科技有限公司

Efficient computation method for electromagnetic modeling

Method for efficient processing of controlled source electromagnetic data, whereby Maxwell's equations are solved [107] by numerical techniques [109] such as finite difference or finite element in three dimensions for each source location and frequency of interest. The Reciprocity Principle is used [103] to reduce the number of computational source positions, and a multi-grid is used [105] for the computational grid to minimize the total number of cells yet properly treat the source singularity, which is essential to satisfying the conditions required for applicability of the Reciprocity Principle. An initial global resistivity model [101] is Fourier interpolated to the computational multi grids [106]. In inversion embodiments of the invention, Fourier prolongation is used to update [120] the global resistivity model based on optimization results from the multi-grids.

Owner:EXXONMOBIL UPSTREAM RES CO

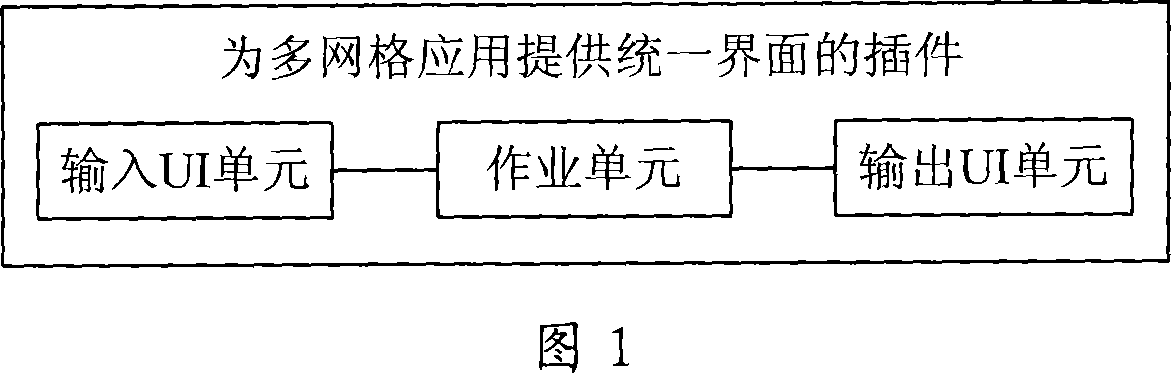

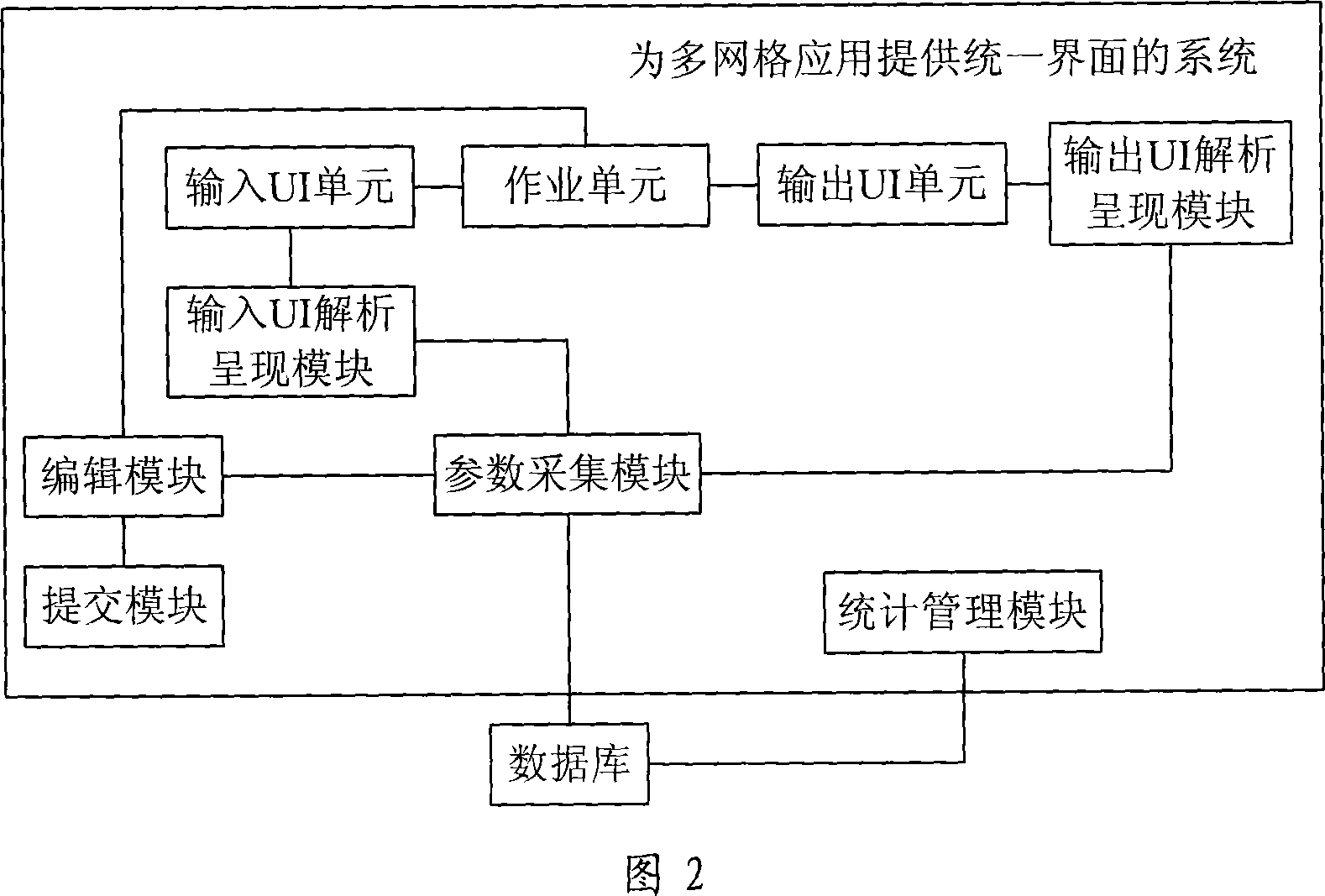

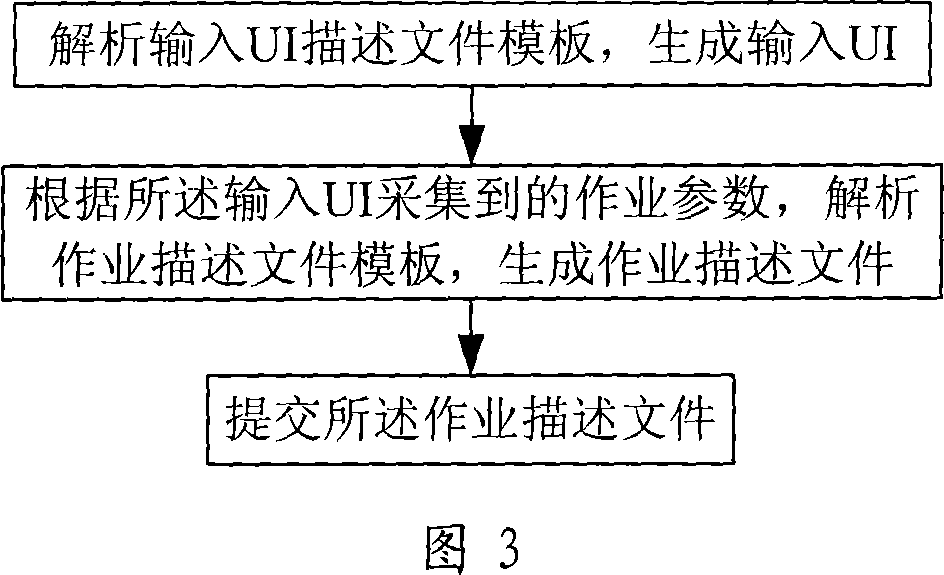

Plug-in component, system and method for providing unionize interface for multicell application

InactiveCN101042648AEasy to useStrong scalabilitySpecific program execution arrangementsClient-sideMiddleware

This invention provides one plug part for multiple-grid application, which comprises operation unit for operation description file mode, U1 unit for description file mode and the output U1 unit for U1 description file mode, the operation unit is connected to the U1 unit and output U1. Based on above part, this invention provides one multi-grid application for integral interface. This invention seals the operation description and interface for multiple customer ends.

Owner:BEIHANG UNIV

Multi-grid ion beam source for generating a highly collimated ion beam

InactiveUS20050017645A1Great momentumElectric arc lampsMaterial analysis by optical meansMomentumIon beam

A multi-grid ion beam source has an extraction grid, an acceleration grid, a focus grid, and a shield grid to produce a highly collimated ion beam. A five grid ion beam source is also disclosed having two shield grids. The extraction grid has a high positive potential and covers a plasma chamber containing plasma. The acceleration grid has a non-positive potential. The focus grid is positioned between the acceleration grid and the shield grid. The combination of the extraction grid and the acceleration grid extracts ions from the plasma. The focus grid acts to change momentum of the ions exiting the acceleration grid, focusing the ions into a more collimated ion beam than previous approaches. In one embodiment, the focus grid has a large positive potential. In another embodiment, the focus grid has a large negative potential.

Owner:VEECO INSTR

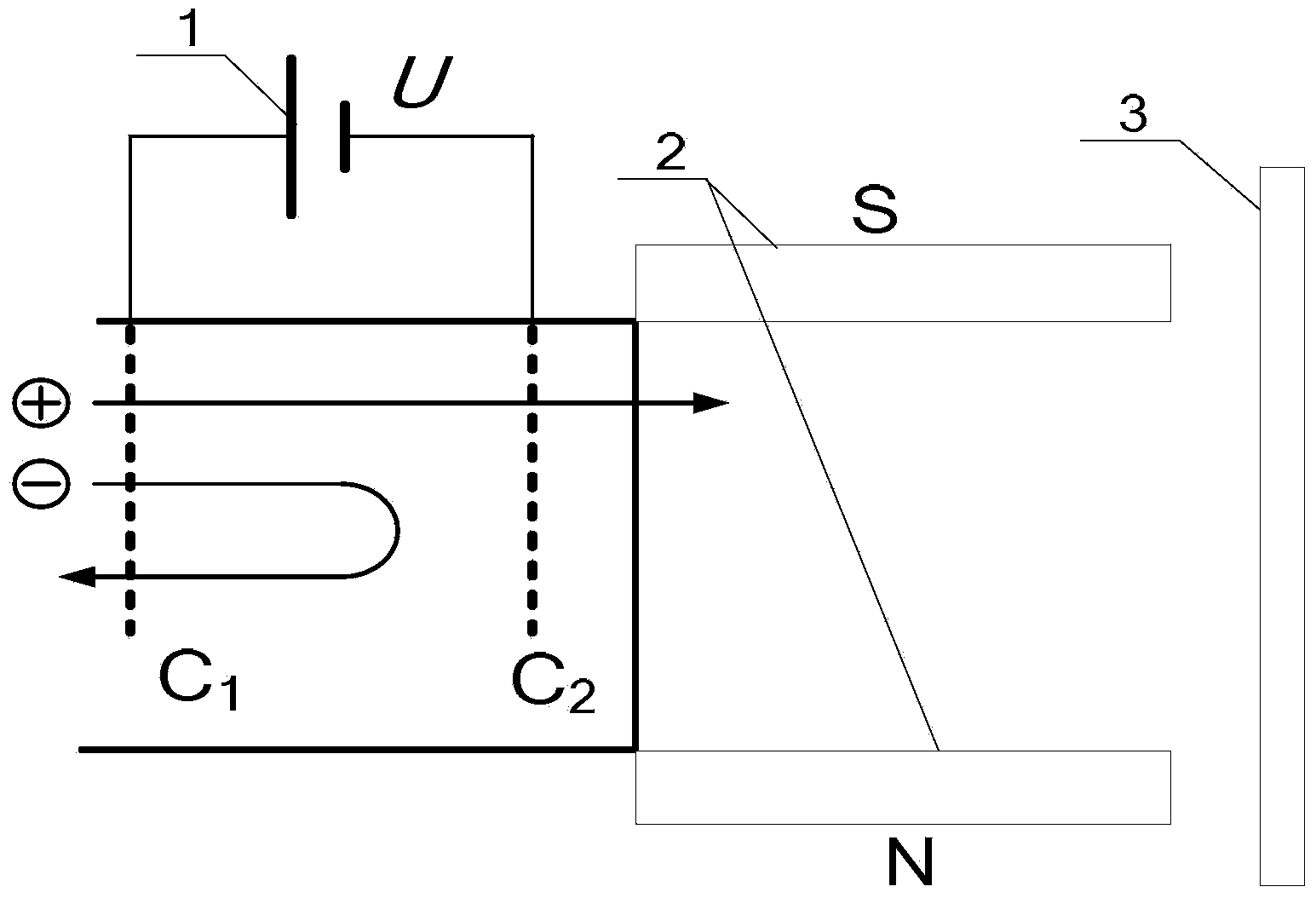

Device and method for instantaneous measurement of ion velocity distribution function

InactiveCN103954789ASimple structureAccurate measurementDevices using electric/magnetic meansIon distributionParticle beam

The invention discloses a device and method for instantaneous measurement of an ion velocity distribution function and belongs to the technical field of measurement of ion velocity distribution functions. The device and method for instantaneous measurement of the ion velocity distribution function aim to solve the problem that according to an existing multi-grid probe measurement method, in order to depict an iron distribution function, current is measured by continuously changing the adjustable voltage, and thus the iron distribution function cannot be measured in real time. According to the device for instantaneous measurement of the ion velocity distribution function, a direct-current power supply supplies an accelerating field to particles, a magnetic field coil provides a magnetic deflection field for the particles which are accelerated through the accelerating field, and a charge collection plate collects the moving particles with the moving direction changed through the magnetic deflection field. According to the method for instantaneous measurement of the ion velocity distribution function, the current density of particle beams at different positions is obtained through currents sensed by different particle collection areas on the charge collection plate, and thus the real-time ion velocity distribution function is obtained. The device and method are used for instantaneous measurement of the ion velocity distribution function.

Owner:HARBIN INST OF TECH

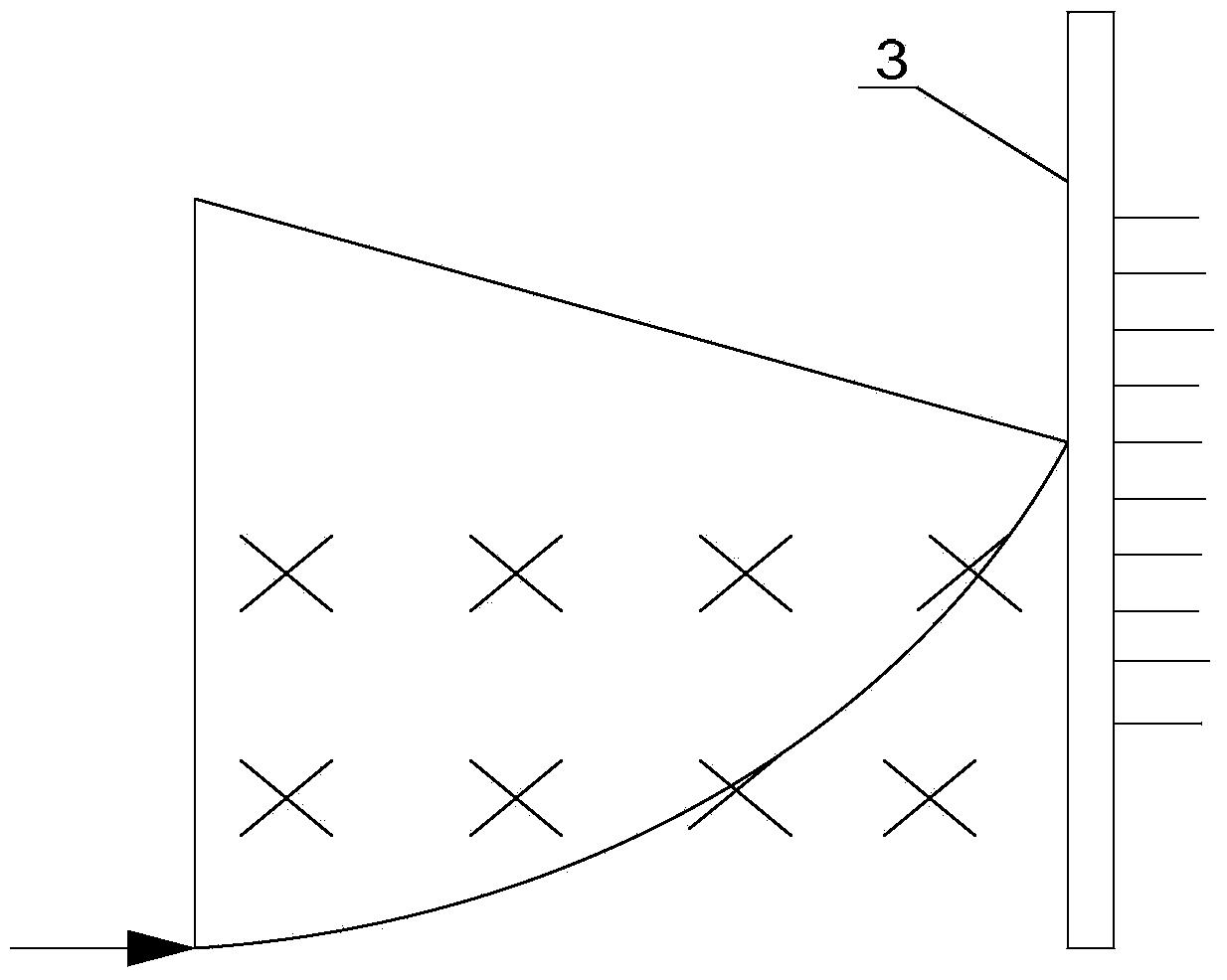

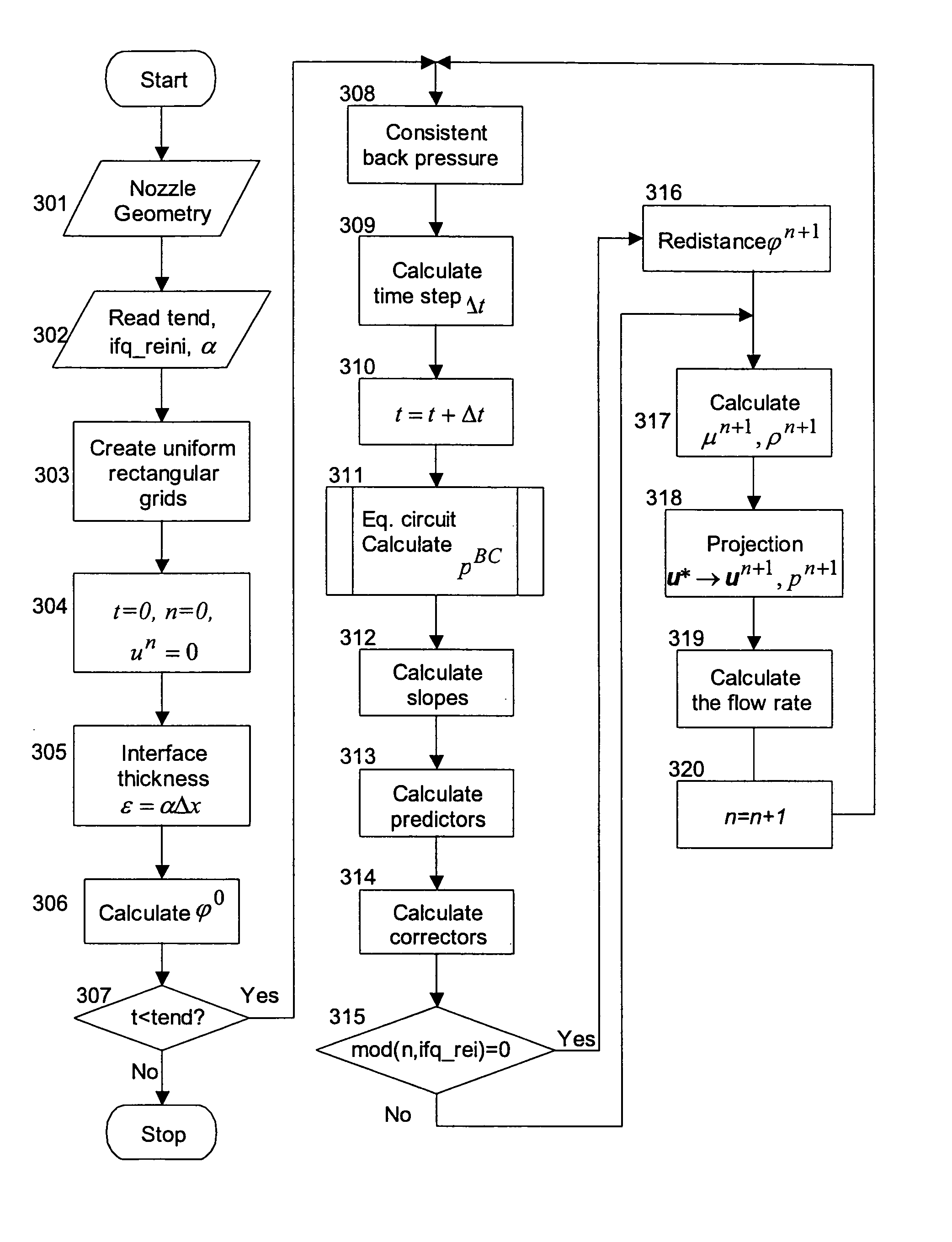

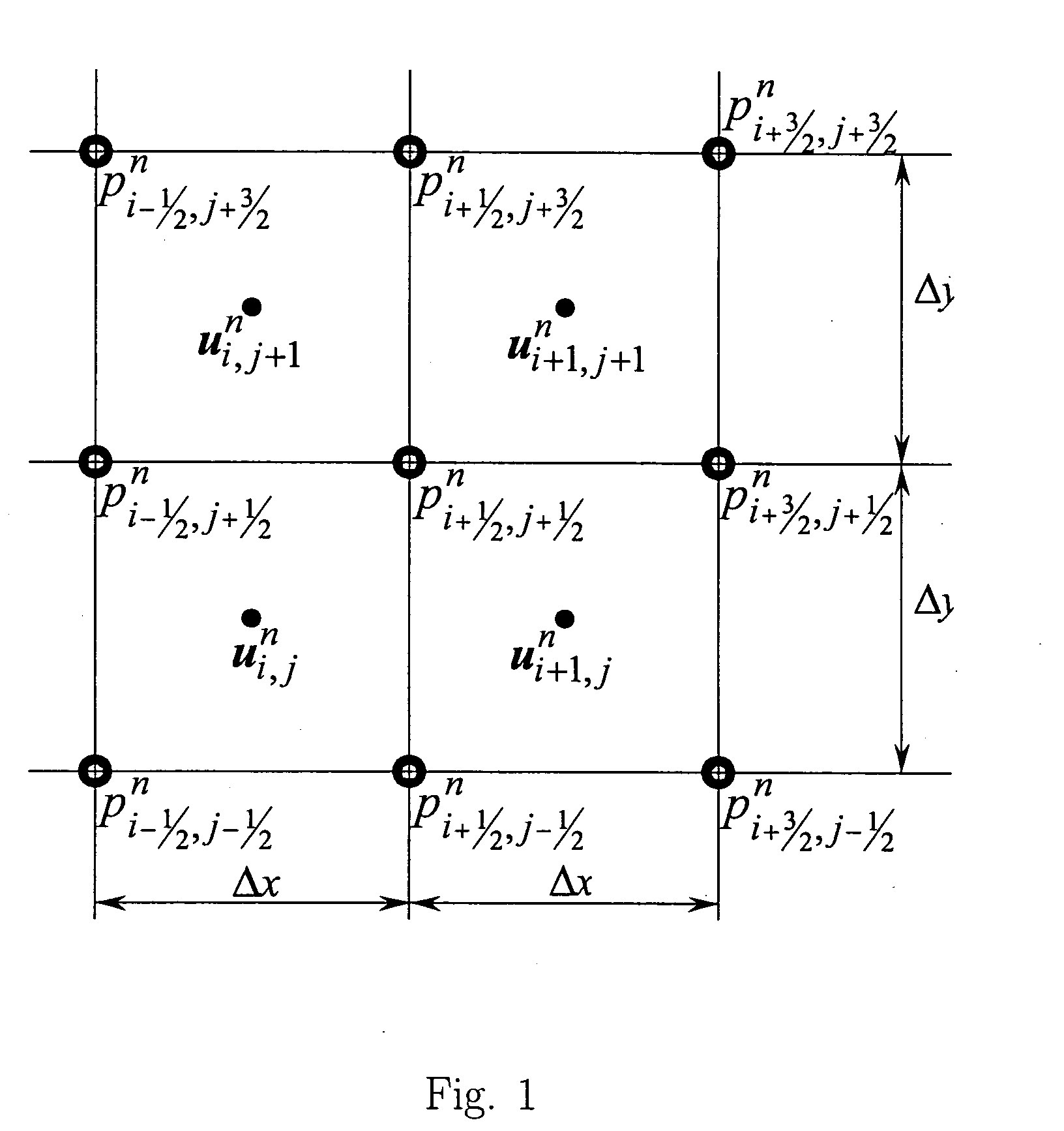

2D central difference level set projection method for ink-jet simulations

ActiveUS20060070434A1Easy to implementImprove performanceSurveyComputation using non-denominational number representationDiscretizationLinearity

A coupled level set projection method is incorporated into a finite-difference-based ink-jet simulation method to make the simulation easier and faster to run and to decrease the memory requirements. The coupled level set projection method is based on a central difference discretization on uniform rectangular grids. A constructed numerical projection operator, in the form of either a finite difference projection operator or a finite element projection operator, can be used in the central difference scheme, in which case the resulting linear systems can be solved by a multi-grid method. The finite difference projection operator is used when the fluid velocity is located at grid points and the pressure at cell centers, whereas the finite element projection operator is used when the fluid velocity is located at cell centers and the pressure at grid points.

Owner:KATEEVA

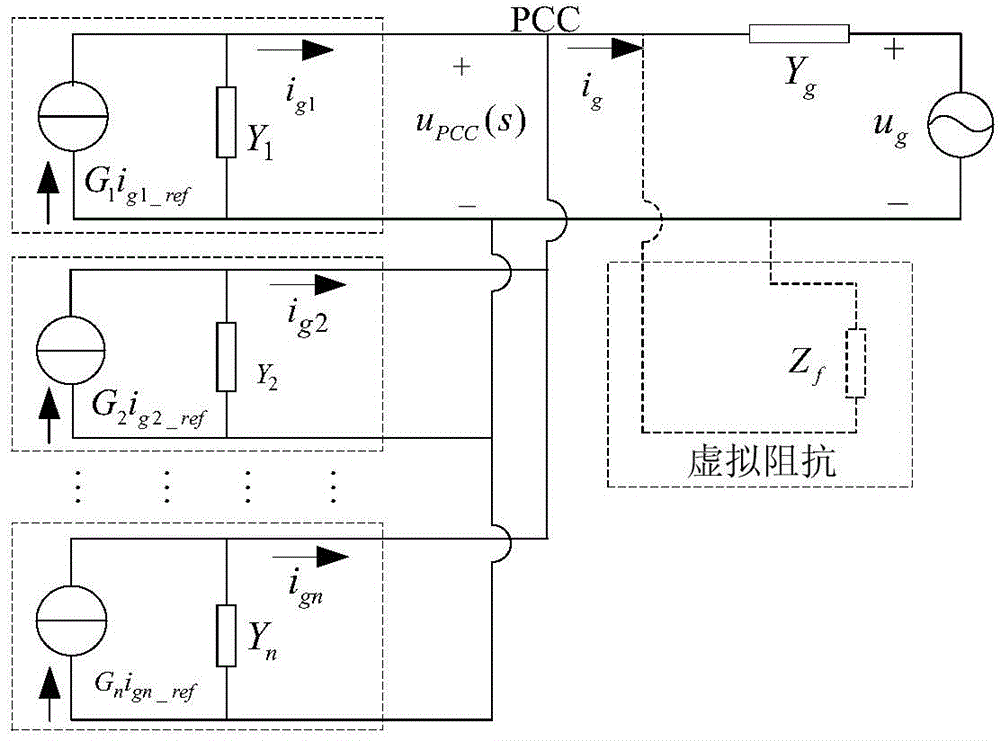

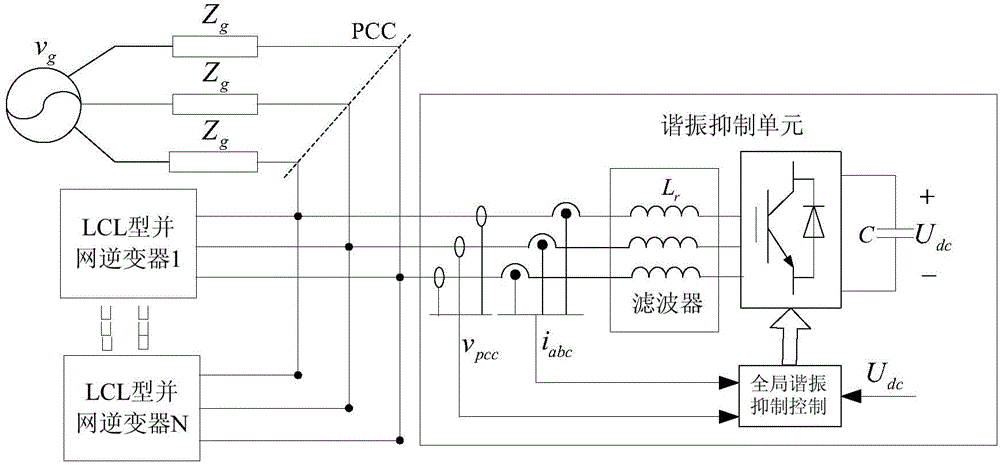

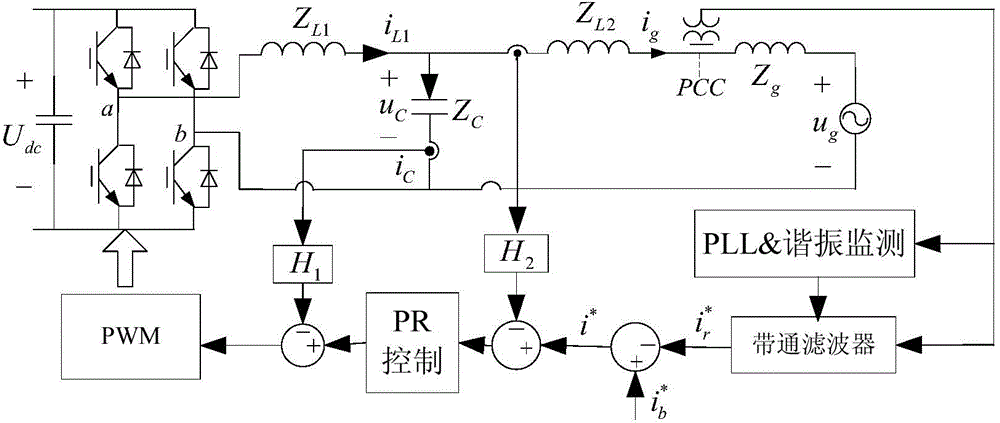

Global resonance inhibition device and method of multi grid-connected inverter system based on virtual impedance

ActiveCN104836229AReduce voltageSuppress resonanceAc network circuit arrangementsGrid connected inverterResonance

The invention relates to a global resonance inhibition device and method of a multi grid-connected inverter system based on the virtual impedance, and belongs to the field of power and electronics. An inverter is independently added and serves as a resonance inhibition unit to generate a virtual impedance unit, and the virtual impedance unit is connected in parallel to a coupling point PCC between the grid-connected inverters and the common electrical network. The method is characterized in that the frequency of a resonant point and the impedance of the frequency near the resonant point are very low, and the resonant point of the PCC point and voltage near the resonant point are reduced. The method can be used to effectively inhibit the resonance of the electrical network without influence on fundamental wave control of the grid-connected inverters.

Owner:WUHAN UNIV

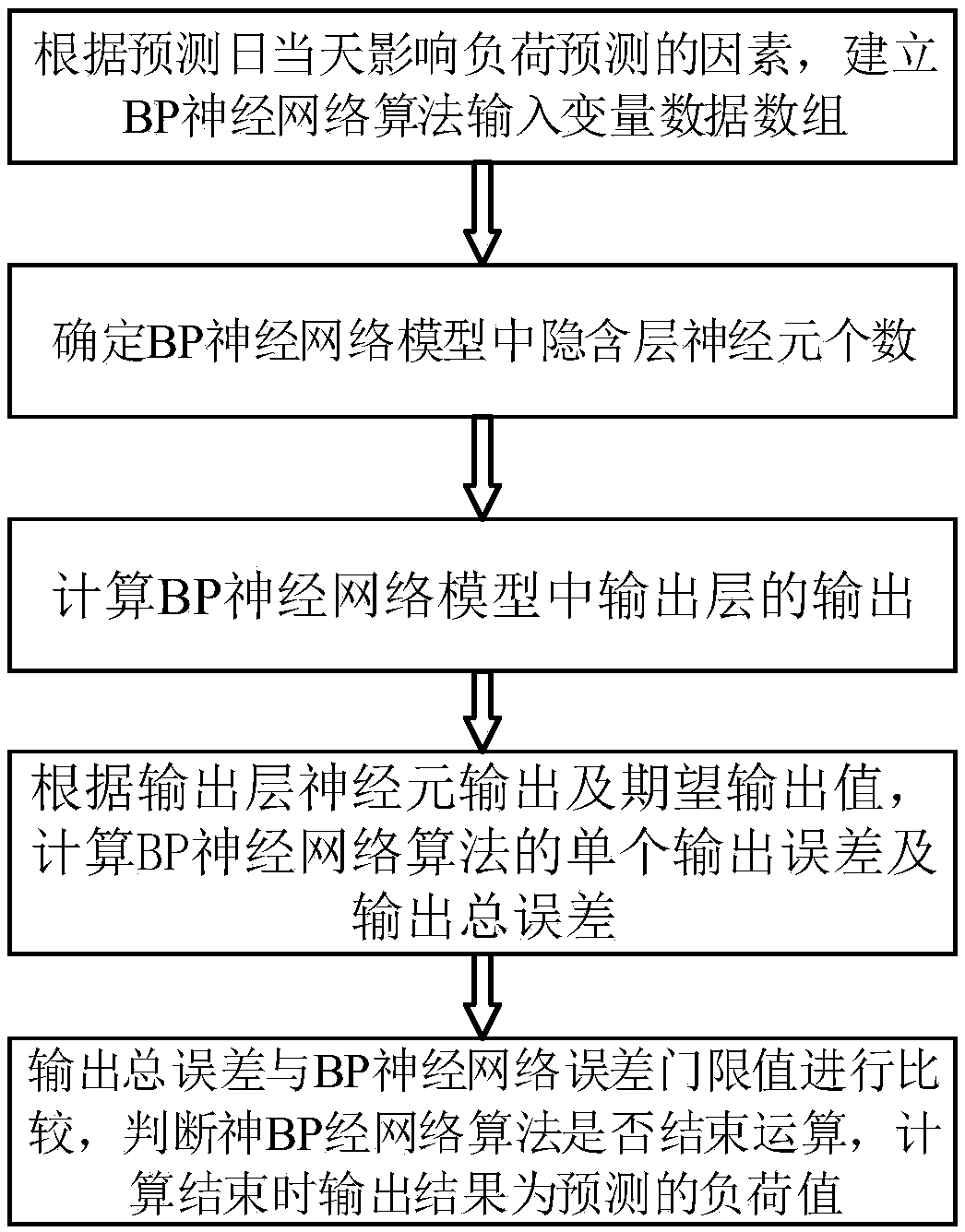

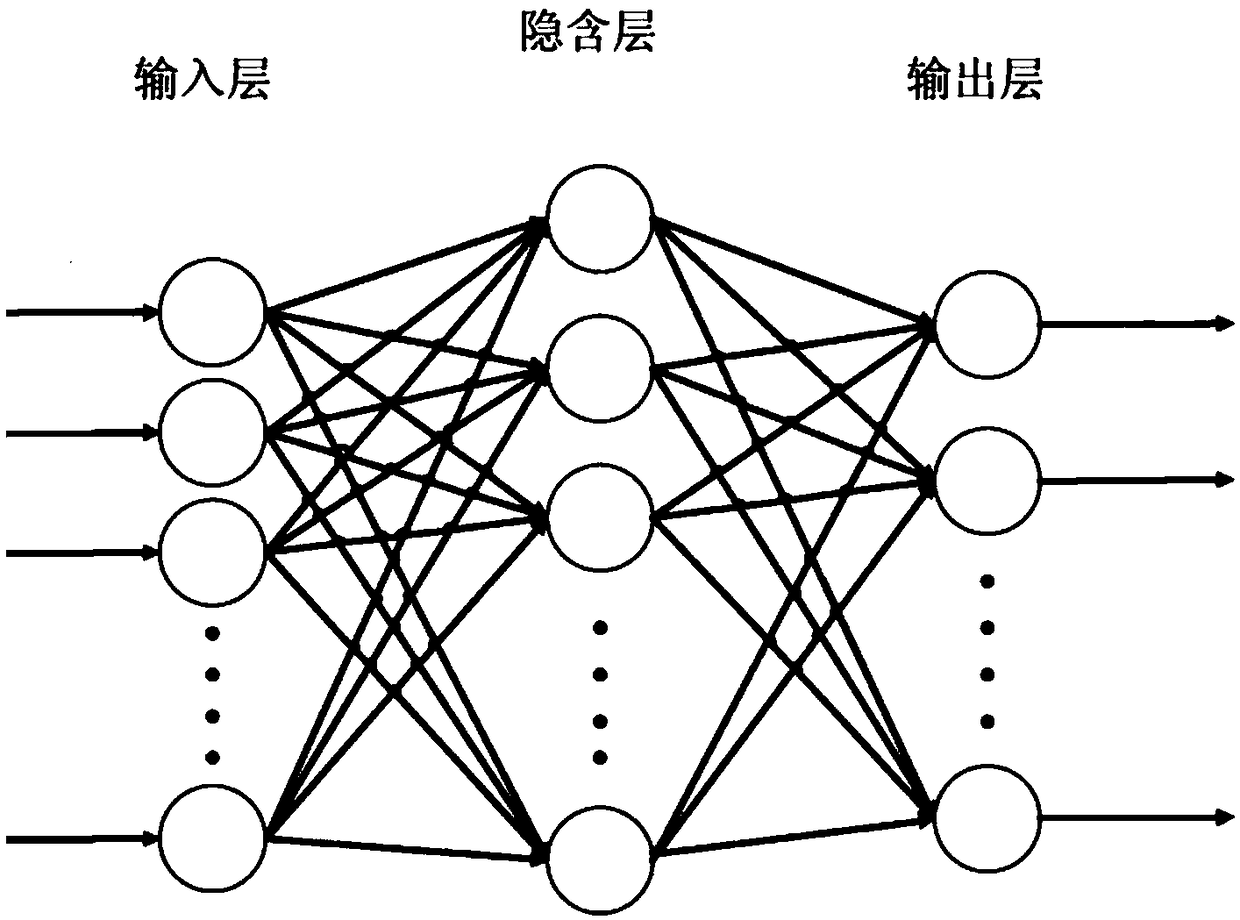

multi-grid load forecasting method based on BP neural network

InactiveCN109376950AImprove generalization abilityFast convergenceForecastingNeural architecturesSingle sampleHidden layer

The invention discloses a multi-grid load forecasting method based on BP neural network, which comprises the following steps: calling data from a multi-grid historical database to establish a BP neural network sample input variable data array; Determine the number of hidden layer neurons in BP neural network model; Calculate the output of output layer in BP neural network model; The output error of single sample and the total output error of all samples in BP neural network sample training are calculated. Judge the end condition of sample training; The predicted load value is output by the model after training. The method of the invention is based on a BP neural network model, has good generalization and convergence, and can more accurately meet the actual prediction requirements.

Owner:STATE GRID SHAANXI ELECTRIC POWER RES INST +3

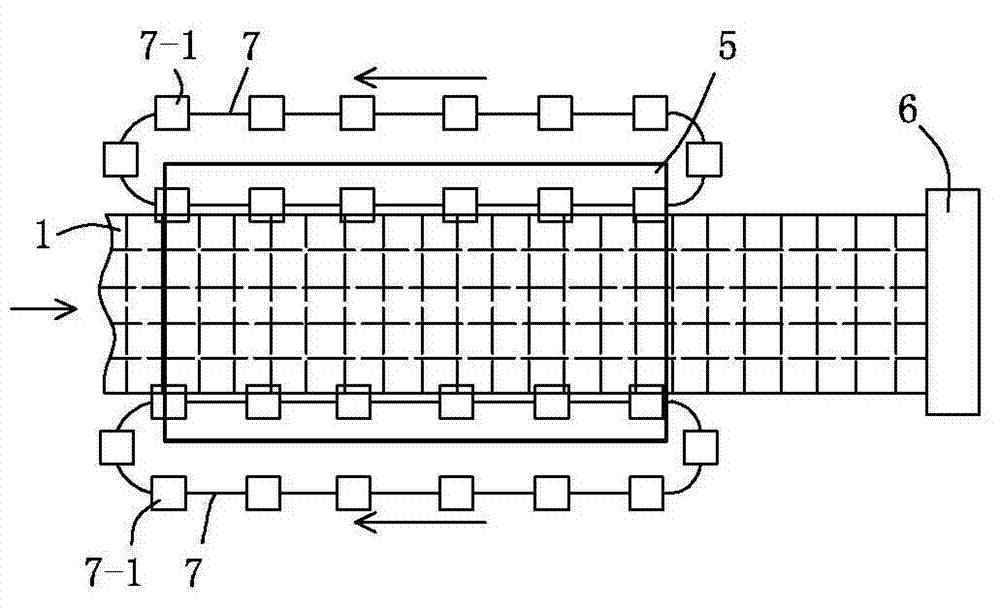

System and method for voltage-free sampling coordination control for multi-grid-connected inverter

ActiveCN108336760ALow costImprove responsivenessAc-dc conversionSingle network parallel feeding arrangementsGrid connected inverterControl system

The invention discloses a system and method for voltage-free sampling coordinated control for a multi-grid-connected inverter. The system comprises a plurality of grid-connected inverters and a network voltage collecting device, an input end of each grid-connected inverter is connected to a power generating unit, an output end of each grid-connected inverter is connected to a power grid through acommon grid connection point, each grid-connected inverter is connected to a communication line, the network voltage collecting device is arranged on one of the grid-connected inverters, the grid-connected inverter collects network voltage information through the network voltage collecting device, shares the network voltage information to the other grid-connected inverters through the communication line, and the other grid-connected inverters achieve the grid-connected operation of a voltage-free sensor by using the received shared network voltage information and voltage, current and power information which are collected locally.

Owner:SHANDONG UNIV

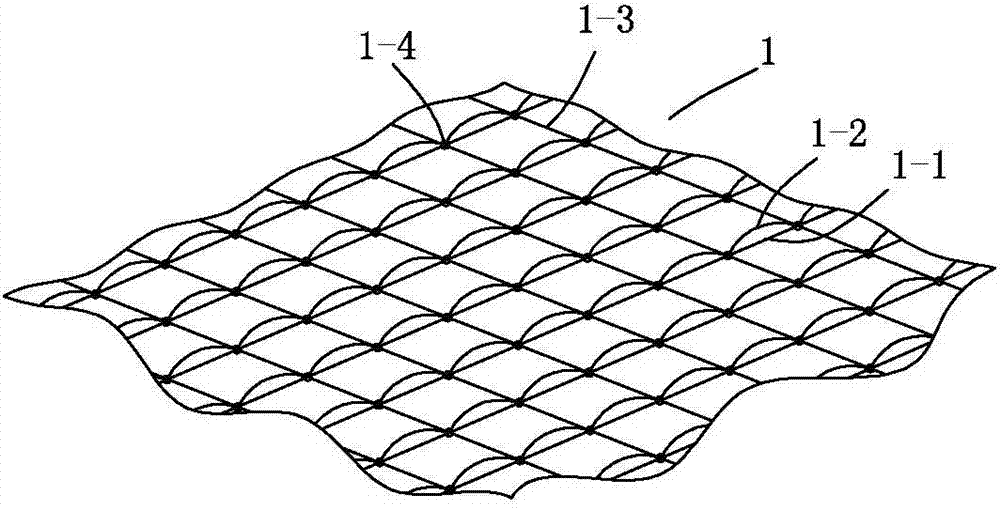

Warp-knitted polyester glass fiber three-dimensional slope protection soil fixation grating and preparation method thereof

InactiveCN103174127AGood width stabilityStrong enoughRoadwaysSynthetic resin layered productsGlass fiberYarn

The invention relates to a warp-knitted polyester glass fiber three-dimensional slope protection soil fixation grating and a preparation method thereof, and in particular relates to a multi-grid grating formed by weaving polyester fiber yarns and glass fiber yarns and a preparation method thereof. Transverse gratings of the grating are formed by arranging glass fiber yarns and polyester fiber yarns; longitudinal gratings of the grating are glass fiber yarns; joints of transverse gratings and longitudinal gratings of grids are bound by polyester wires; after the grating is heated, the glass fiber yarns of the transverse gratings of the grids are upwards bent and protruded from binding points on two sides to form a three-dimensional state of the grating; and a solidification layer formed by waterproof adhesive emulsion is arranged on the surface of the grating. The grating in the preparation method is easy in production and manufacture and high in efficiency; in a construction paving process, the stability of the length and the width of the grating is good; a large area of gratings are paved; the construction difficulty is low; the warp-knitted polyester glass fiber three-dimensional slope protection soil fixation grating is used on the surface of a slope body, and a slope fixing effect is good; and even if the grating is corroded by rainwater for a long time and is immersed in water, the grating still has enough strength.

Owner:泰安三英新材料股份有限公司