Configurable matrix register unit for supporting multi-width SIMD and multi-granularity SIMT

A technology for configuring matrices and registers, applied in machine execution devices, concurrent instruction execution, etc., can solve problems such as inability to develop parallelism, inability to support multi-width SIMD processing, inability to flexibly process matrix data, etc., to achieve block size and number of threads Flexible configuration, efficient and flexible processing, simple principle effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

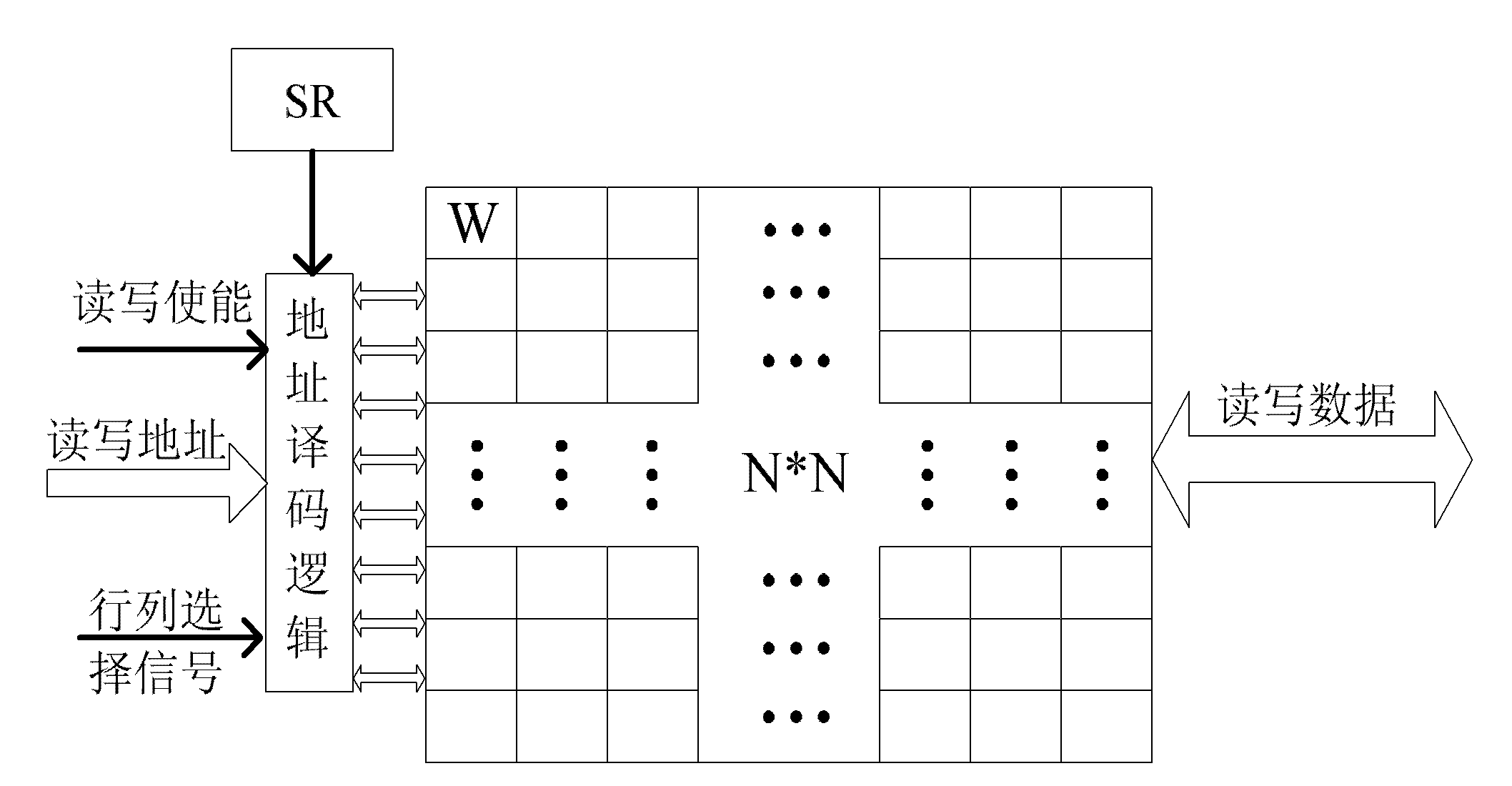

[0027] like figure 1 Shown is a schematic diagram of the overall structure of the matrix register of the present invention. The configurable matrix register unit supporting multi-width SIMD and multi-granularity SIMT of the present invention includes a matrix register and a control register SR.

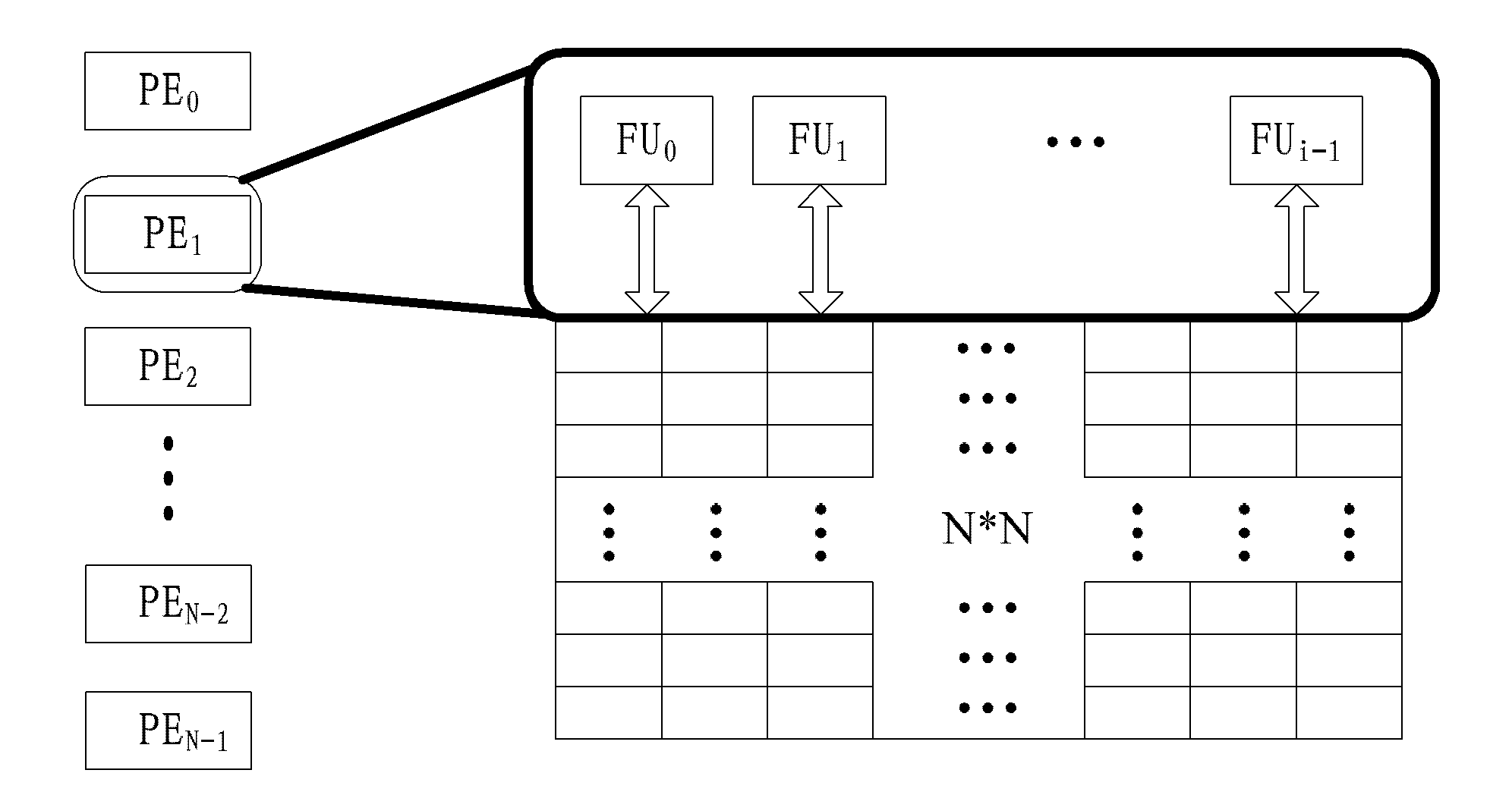

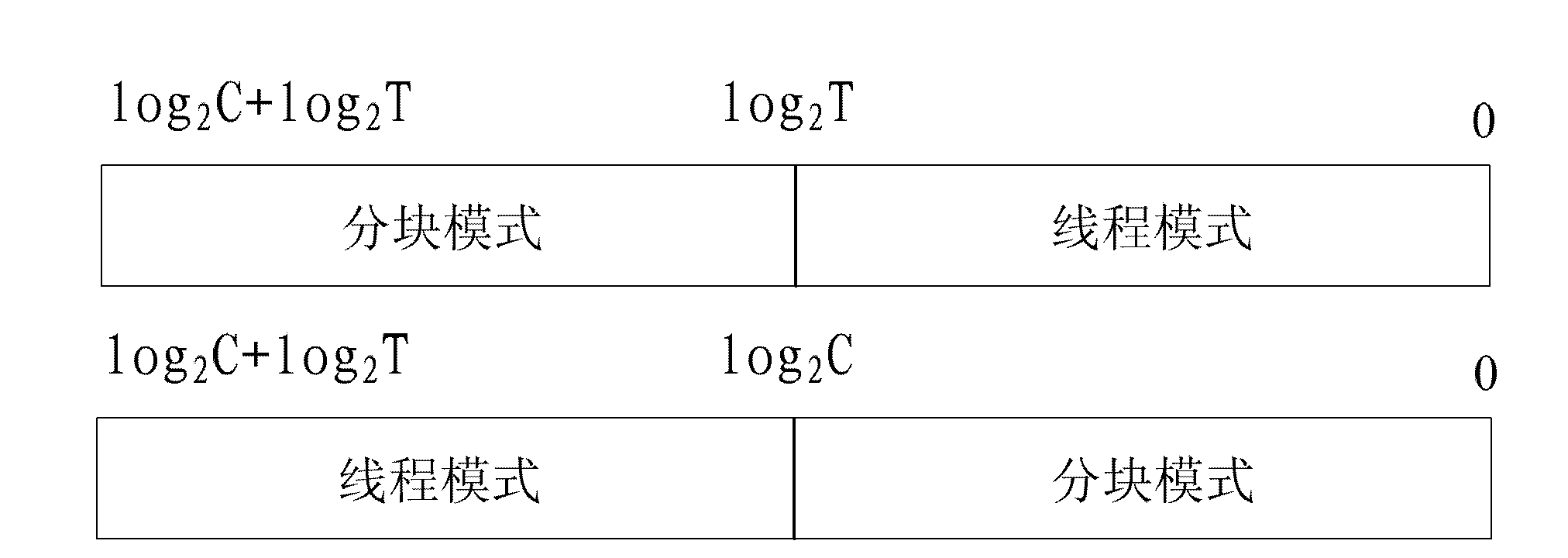

[0028] When the read and write enable signal is valid, the address decoding logic unit performs decoding under the control of the row and column selection signal and the control register SR according to the content of the read and write address, and selects a row vector or column vector of the matrix register to read and write. Or select one or more sub-row vectors or sub-column vectors to read and write. The matrix register is composed of N*N storage unit arrays, each unit has a bit width of W and a storage capacity of (N*N*W) bits. By co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More