Rack-mount synchronous Ethernet architecture and clock synchronization control method

A technology of synchronous clock and synchronous clock source, which is applied in the field of Ethernet data communication to achieve reliable clock recovery, reduce equipment cost, and improve flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

[0037] The present invention aims to provide a rack-mounted synchronous Ethernet solution, and its specific implementation will be described in detail below.

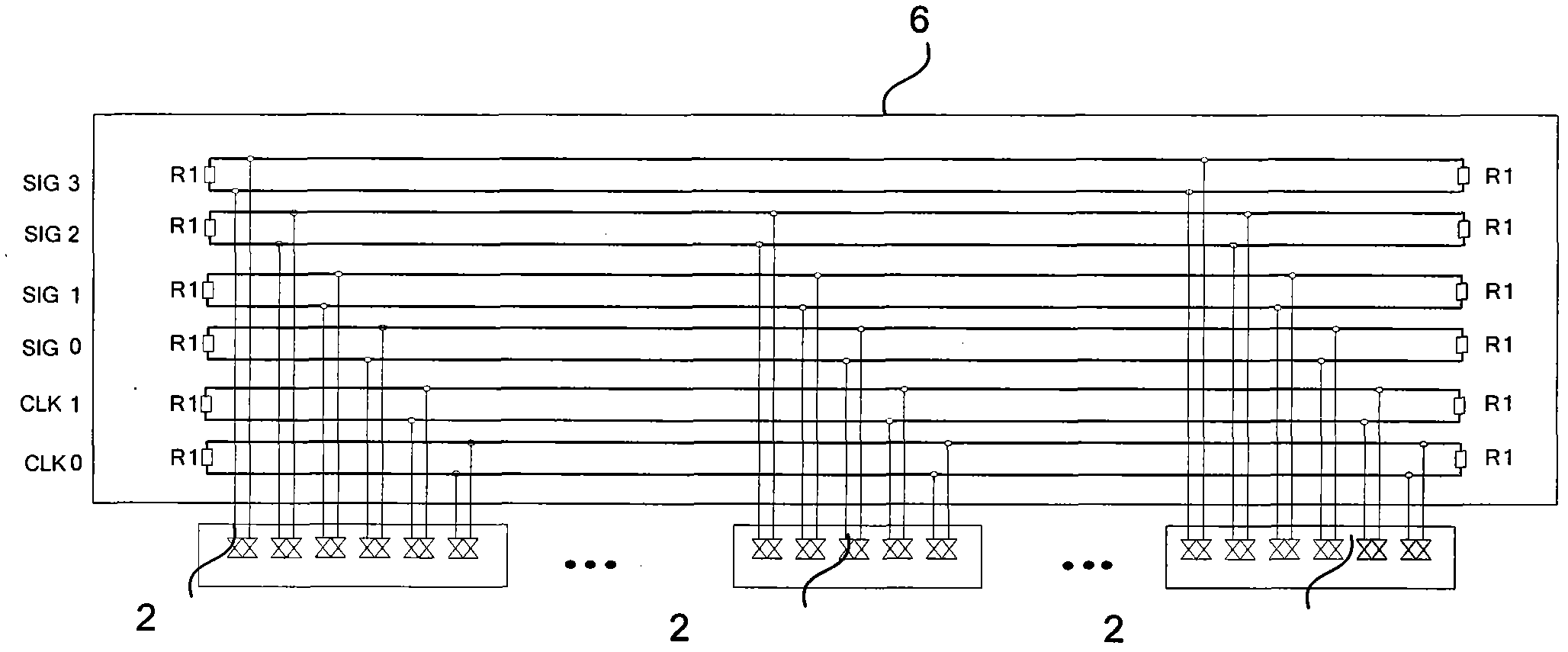

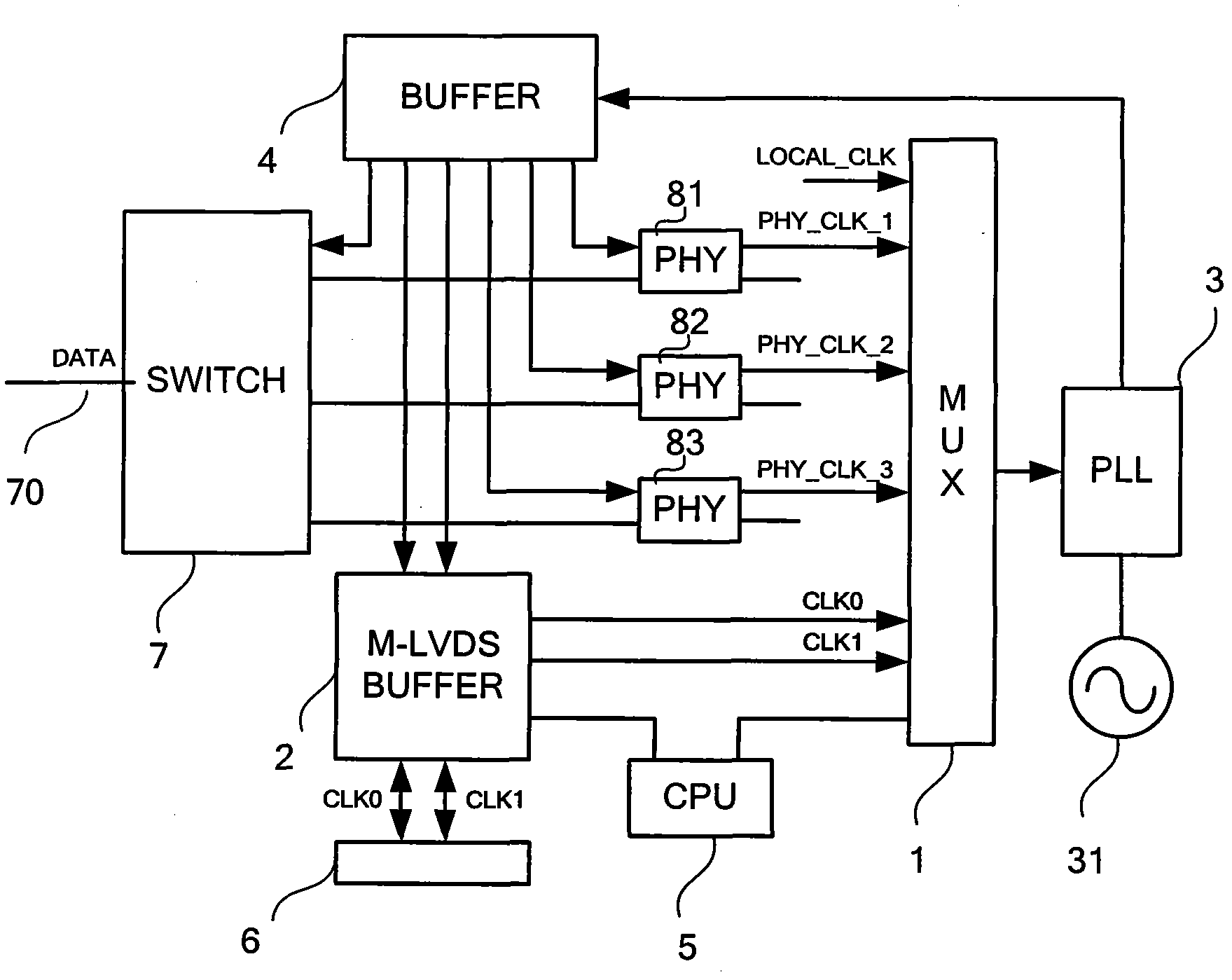

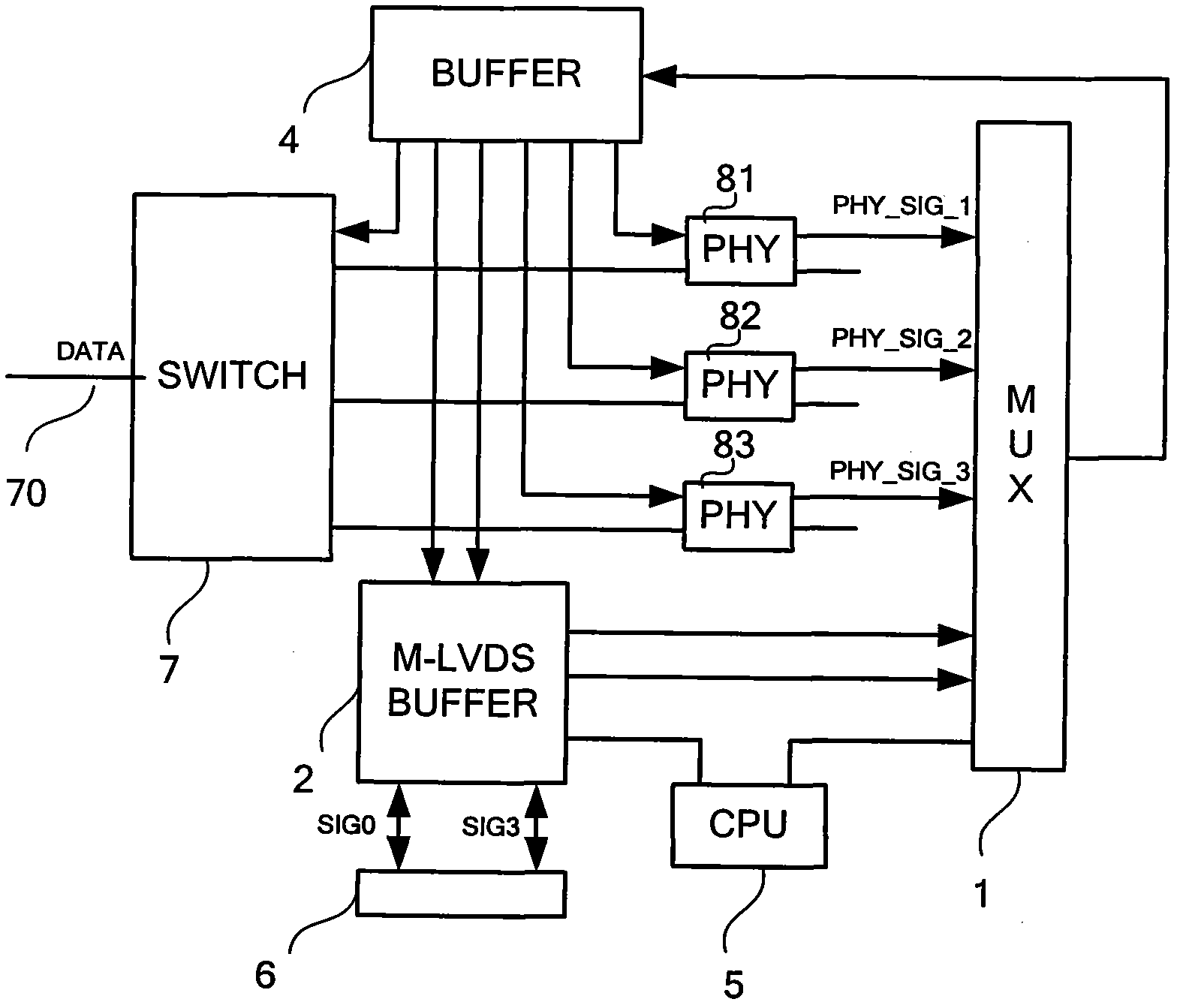

[0038] The invention mainly proposes the M-LVDS solution for the backplane circuit of the synchronous Ethernet aiming at the rack-type switch. The topology of the above M-LVDS solution includes one or more synchronous recovered clock wiring topologies, one or more synchronous time stamp wiring topologies, and may also include one or more synchronous recovered clock event alarm information wiring topologies.

[0039] Such as figure 1 , as an embodiment of the synchronous Ethernet clock backplane topology, a plurality of differential signals CLK0 (main synchronous clock), CLK1 (standby synchronous clock), SIG0, SIG1, SIG2 driven by the M-LVDS driver 2 are introduced on the backplane , SIG3 (other...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More