Rack-mount synchronous Ethernet architecture and clock synchronization control method

A synchronous clock and Ethernet technology, applied in the field of Ethernet data communication, to achieve reliable clock recovery, improve flexibility, and reduce equipment costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention will be further described below with reference to the drawings and embodiments.

[0037] The present invention aims to provide a solution for rack-mounted synchronous Ethernet, and its specific implementation will be described in detail below.

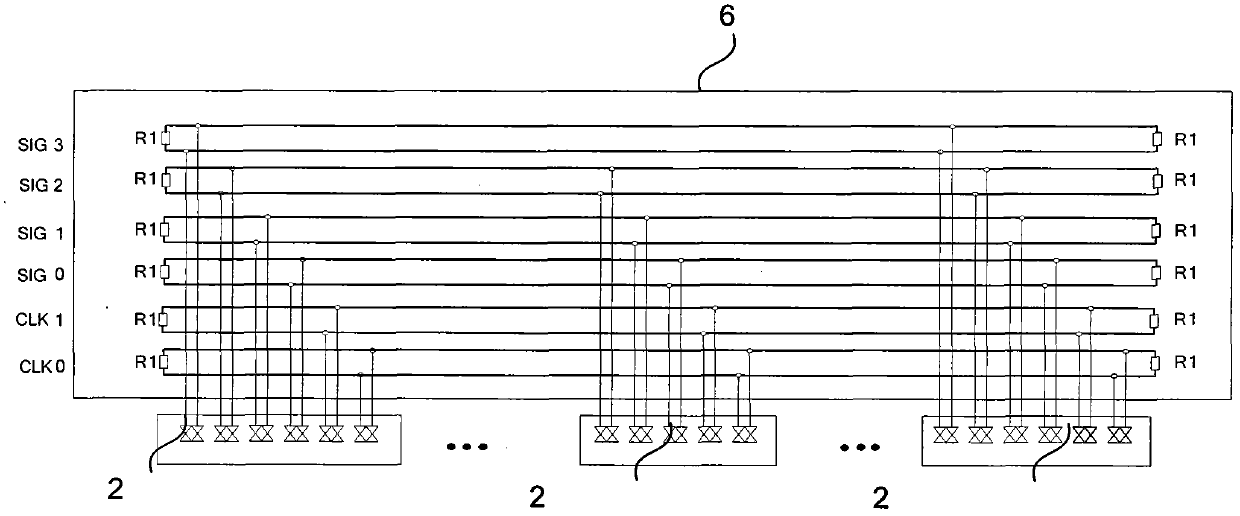

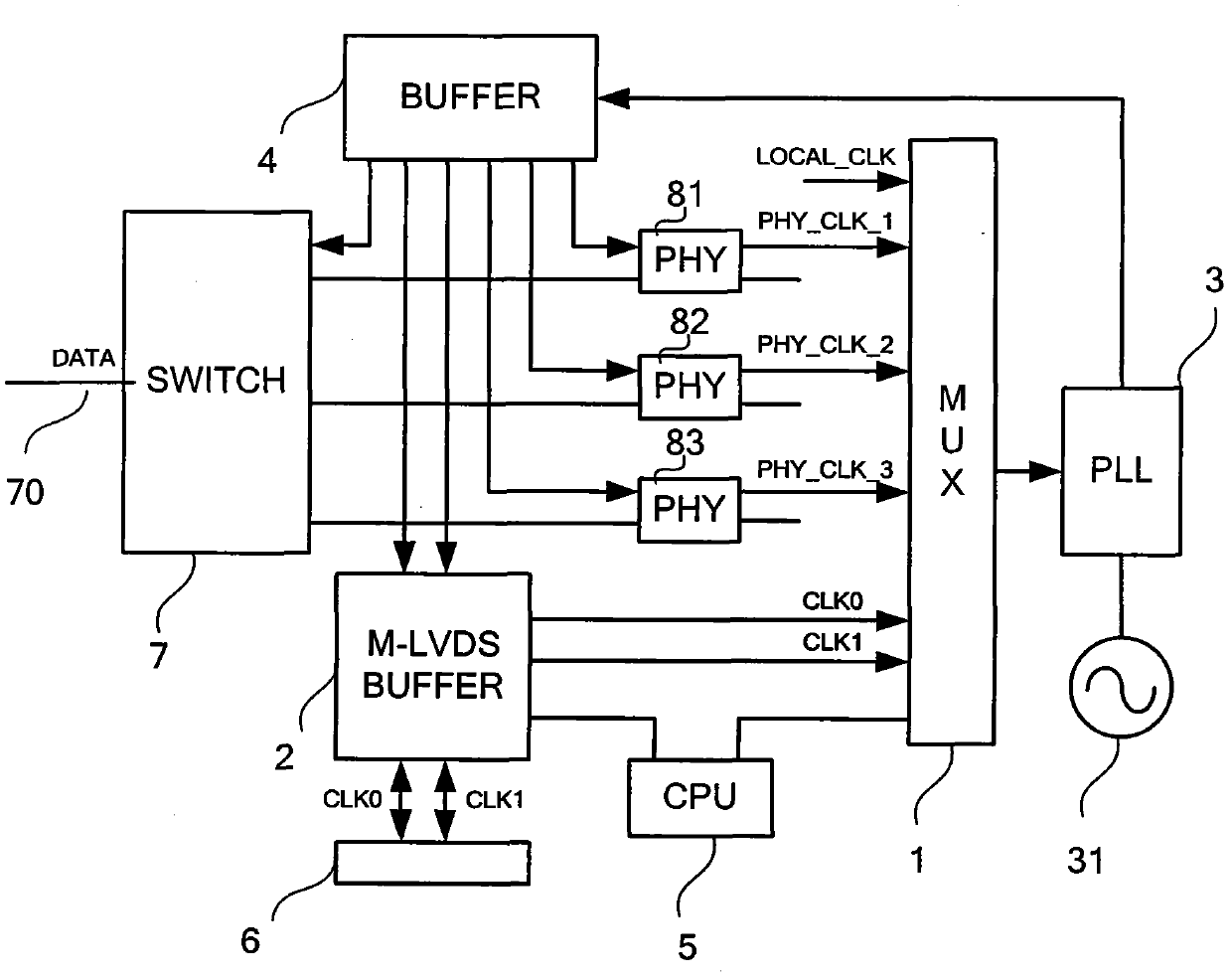

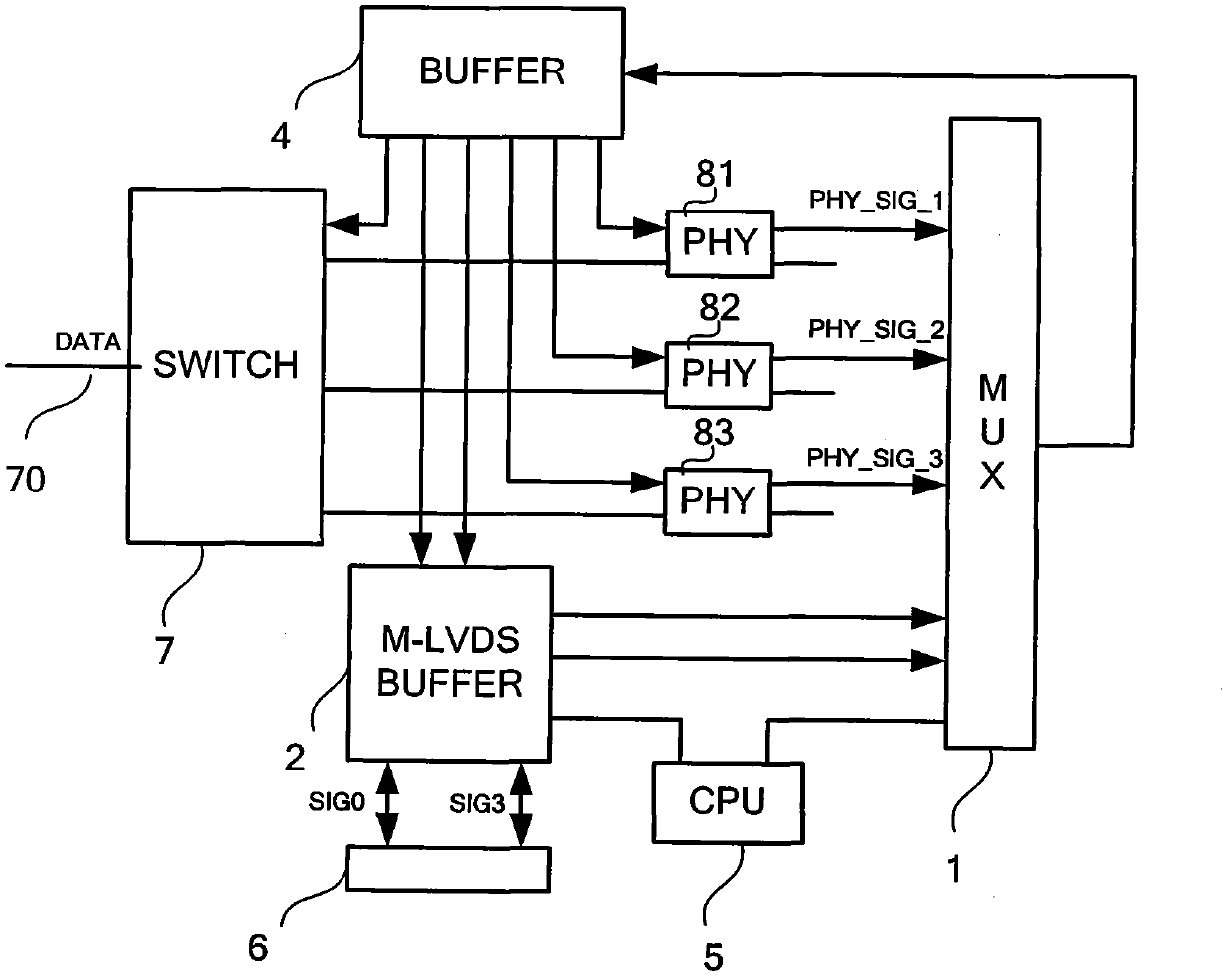

[0038] The present invention mainly proposes a M-LVDS solution of the backplane circuit of the synchronous Ethernet for the rack-mounted switch. The topology of the above-mentioned M-LVDS solution includes one or more synchronous recovery clock wiring topologies, one or more synchronous timestamp wiring topologies, and one or more synchronous recovery clock event alarm information wiring topologies.

[0039] Such as figure 1 As an embodiment of the synchronous Ethernet clock backplane topology, multiple differential signals CLK0 (main synchronous clock), CLK1 (standby synchronous clock), SIG0, SIG1, SIG2 driven by M-LVDS driver 2 are introduced on the backplane , SIG3 (other synchronous trigger signals), etc. Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More