Systematized RISC CPU (Reduced Instruction-Set Computer Central Processing unit) production line control method

A RISCCPU and control method technology, applied in machine execution devices, concurrent instruction execution, etc., can solve problems such as increasing the difficulty of pipeline control logic circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

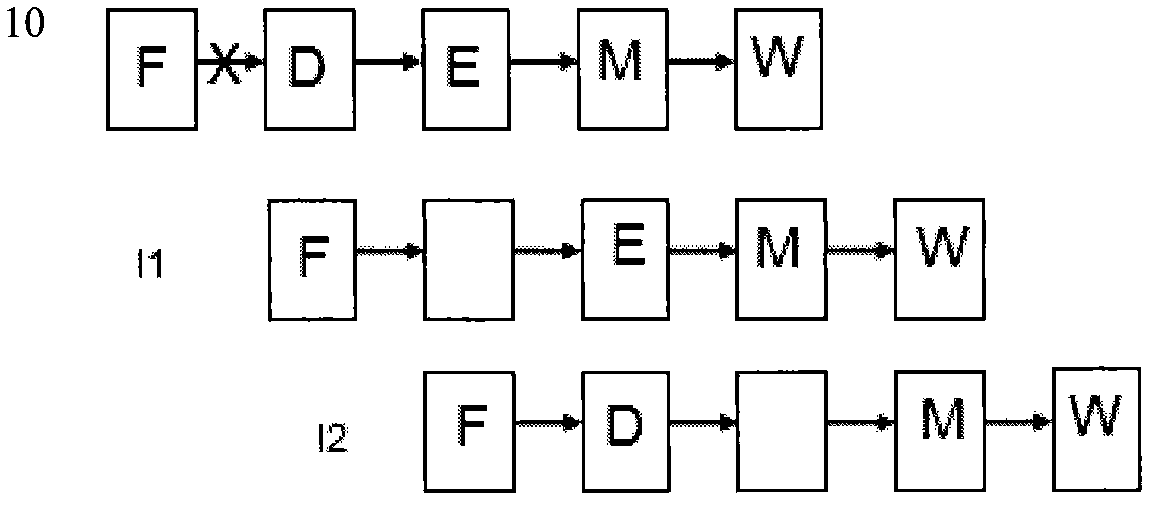

[0027] Such as image 3 As shown, the schematic diagram of the pipeline execution for the F-level exception can be seen: when the instruction cache does not hit, the instruction fetch operation fails, that is, there is no instruction in this cycle, and the F-level inserts a bubble, but the D-level pipeline will not be executed in the next clock cycle; just The pipeline enable signal E 1 Set to 0, N 1 Set to 1 (empty state).

Embodiment 2

[0029] Such as Figure 4 As shown, the schematic diagram of the pipeline execution for D-level exceptions can be seen: since the register bank has only three read ports, when the instruction needs to read four registers, the pipeline stalls; only need to turn the pipeline self-locking signal L 1 set to 1.

Embodiment 3

[0031] Such as Figure 5 As shown, the schematic diagram of pipeline execution for E-level multi-cycle execution exception can be seen: when the instruction is multi-cycle execution end instruction such as multiplication, the front-stage pipeline will be stopped, and the subsequent-stage pipeline will start to execute in the last cycle, and the multiplication instruction will be in the pipeline E Level implementation requires 1 to 5 clock cycles. When it is not the last clock cycle, the enable signal E 3 Set to 0, self-locking signal L 3 Set to 1, otherwise solve according to the recursive formula;

[0032] Another example Figure 6 As shown, the schematic diagram of pipeline execution for E-level branch and jump exceptions can be seen: when the instruction is a branch or jump instruction, the instruction before the instruction runs normally, but the execution instruction after the instruction is an error instruction, that is, F, D The command being executed. Pipeline con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More