I2C (inter-integrated circuit) bus detection device

A detection device and bus technology, applied in error detection/correction, instruments, electrical digital data processing, etc., can solve the problems of complex circuit structure and high cost, and achieve the effect of simple circuit structure and low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

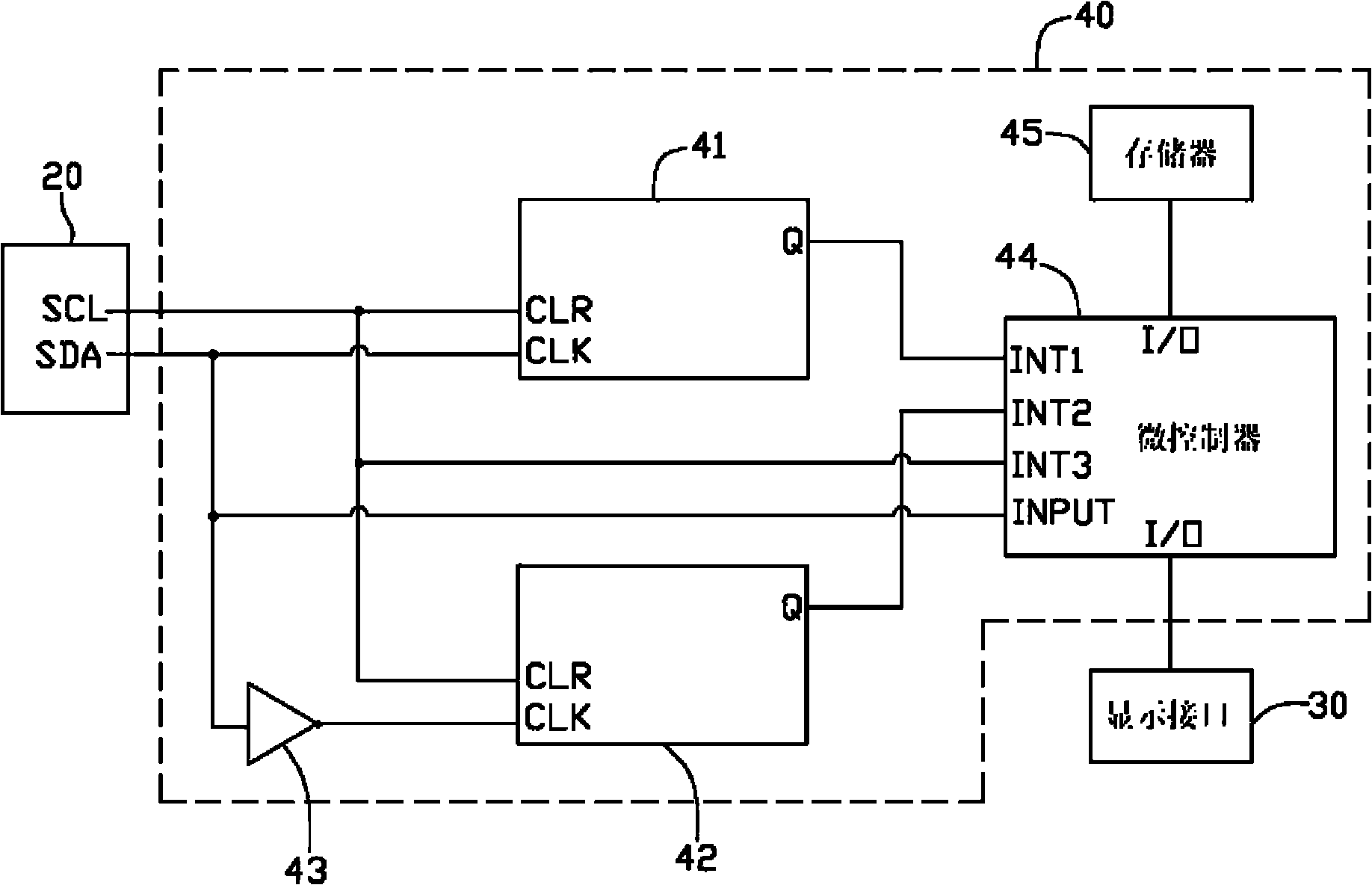

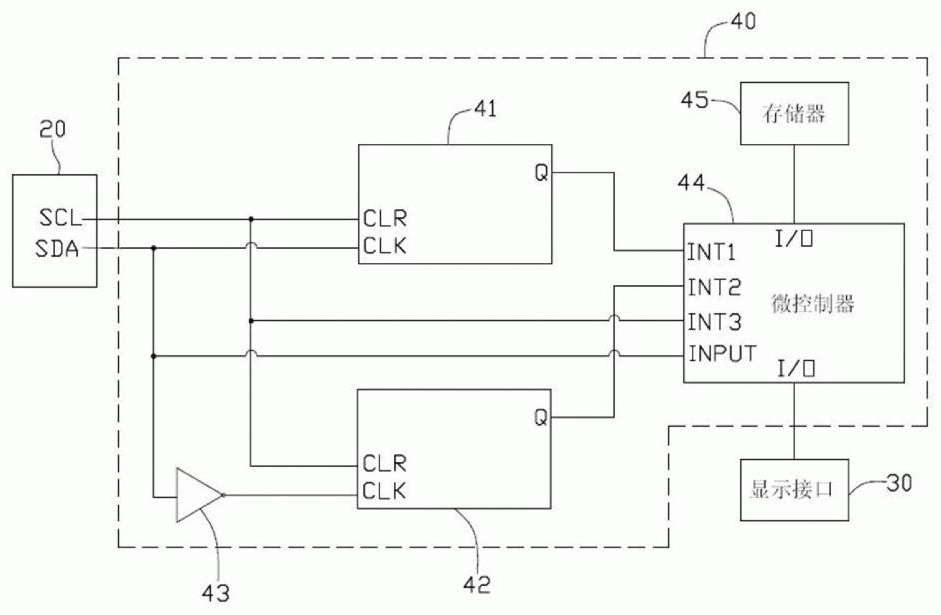

[0017] Please refer to figure 1 and figure 2 A preferred embodiment of the I2C bus detection device of the present invention includes a housing 10, a connector 20 connected to the housing 10, a display interface 30 arranged on the housing 10 such as a VGA interface and a setting A detection circuit 40 inside the housing 10 and connected to the connector 20 and the display interface 30 . The connector 20 is used to connect the connector of the I2C bus to be detected on the motherboard of an electronic device, and the connector 20 includes a clock pin SCL and a data pin SDA, which are respectively used to connect the clock signal lines on the I2C bus and data signal lines to receive clock signals and data signals thereon, and the display interface 30 is used to connect a display device to display the detection results processed by the detection circuit 40, so that the detection personnel can accurately Informed of a problem with the motherboard of an electronic device.

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com