Pin multiplexing verifying device and method for integrated circuit

A pin multiplexing and integrated circuit technology, which is applied in the field of pin multiplexing verification devices, can solve problems such as omissions by verification engineers and errors not being discovered in time, so as to avoid tedious work, reduce test time, and reduce errors. The effect of chance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention more clear, specific embodiments will be described in detail below with reference to the accompanying drawings.

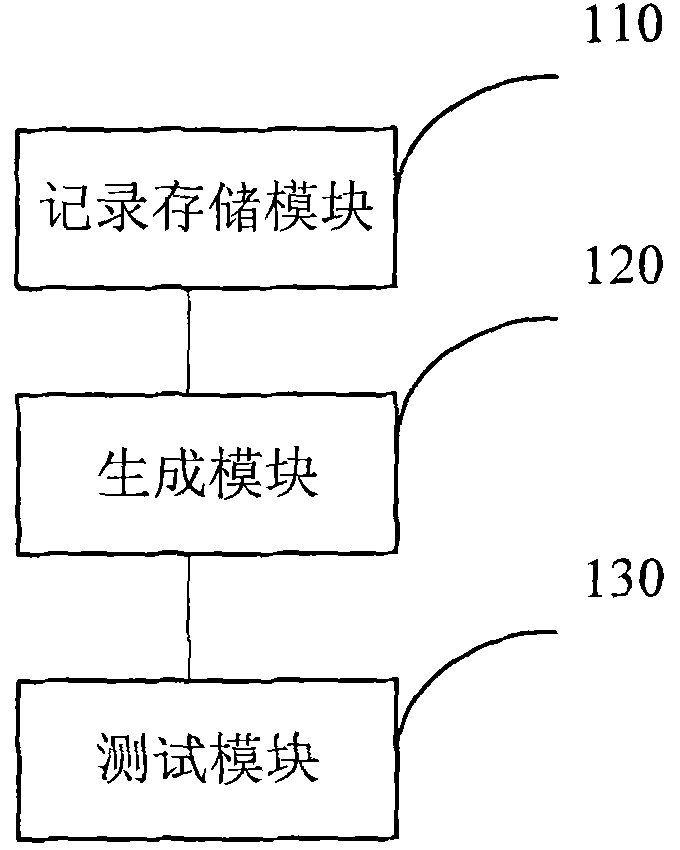

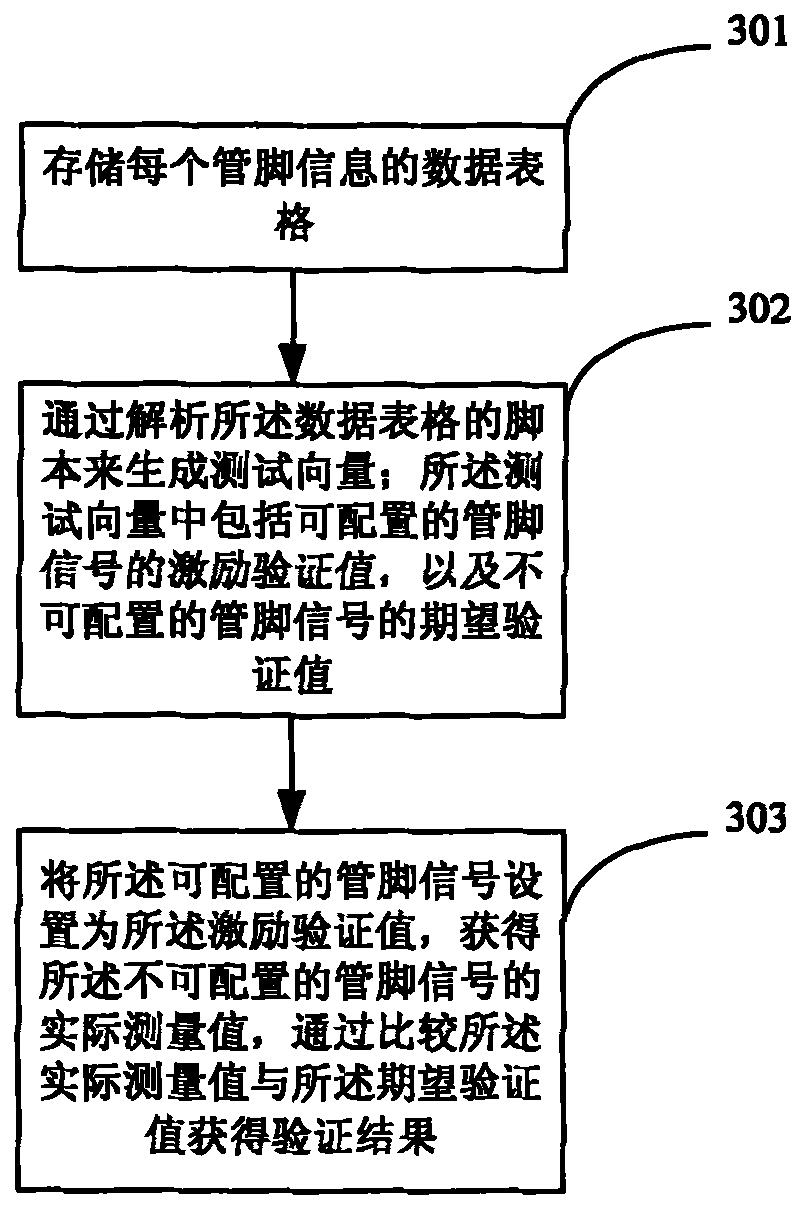

[0035] figure 1 The structural diagram of the verification device provided for the embodiment of the present invention, as shown in the figure, the verification device for multiplexing the pins of the integrated circuit includes:

[0036] A record storage module 110, configured to: store a data table of each pin information;

[0037] The generating module 120 is configured to: generate a test vector by parsing the script of the data table; the test vector includes the stimulus verification value of the configurable pin signal and the expected verification value of the non-configurable pin signal;

[0038] The test module 130 is configured to: set the configurable pin signal as the excitation verification value, obtain the actual measurement value of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More