MPSoC (multi-processor system-on-chip)-oriented multithread scheduling method

A scheduling method and multi-threading technology, applied in the directions of multi-program device, concurrent instruction execution, machine execution device, etc., to achieve the effect of improving execution efficiency, improving efficiency, and high communication efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0033] A multi-thread scheduling method for MPSoC. Its method is as figure 1 Steps shown:

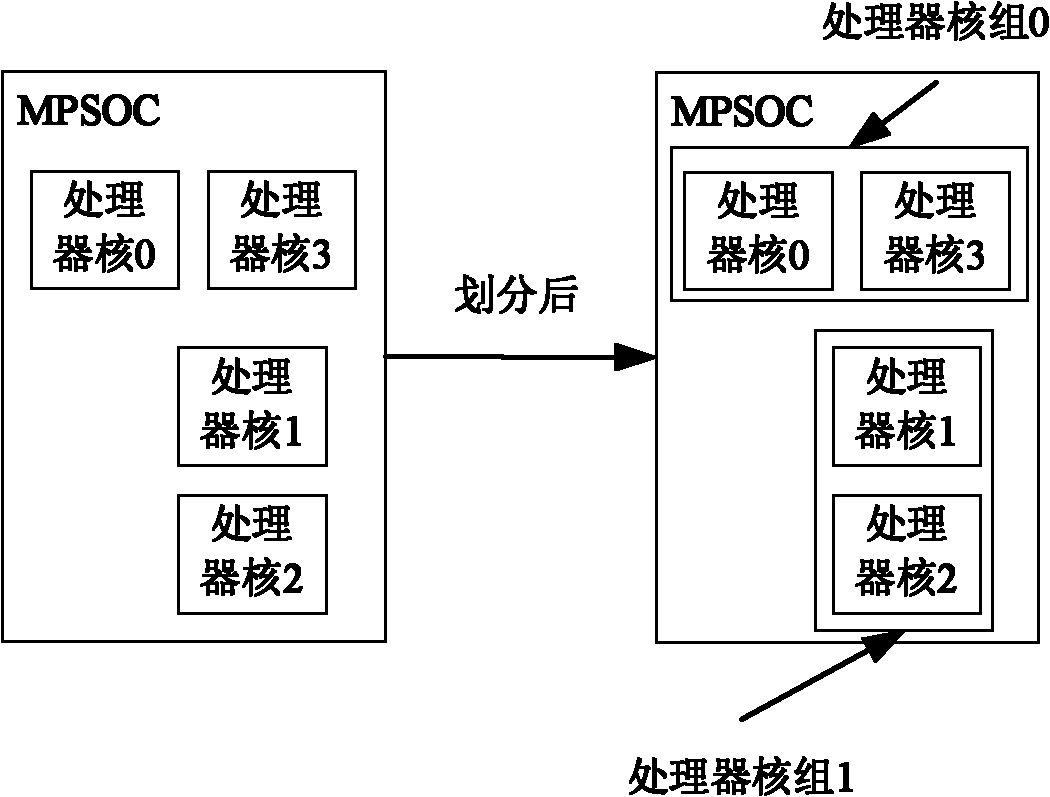

[0034] The first step, processor core group division

[0035] Divide multiple processor cores on the MPSoC into processor core groups according to their physical position, and divide adjacent processor cores into the same processor core group; adopt the form of processor core group configuration table, divide the divided The processor core group is provided to the embedded operating system; the basic content of the processor core group configuration table includes the number of processor core groups and the identification of each processor core group, and the additional content of the processor core group configuration table is the processor core group configuration table. One or more of frequency, number of processor cores, division basis of processor core groups, and temperature range of processor cores.

[0036] Multiple processor cores are integrated on the MPSoC. In order to ma...

Embodiment 2

[0064] A multi-thread scheduling method for MPSoC. The steps of this method are:

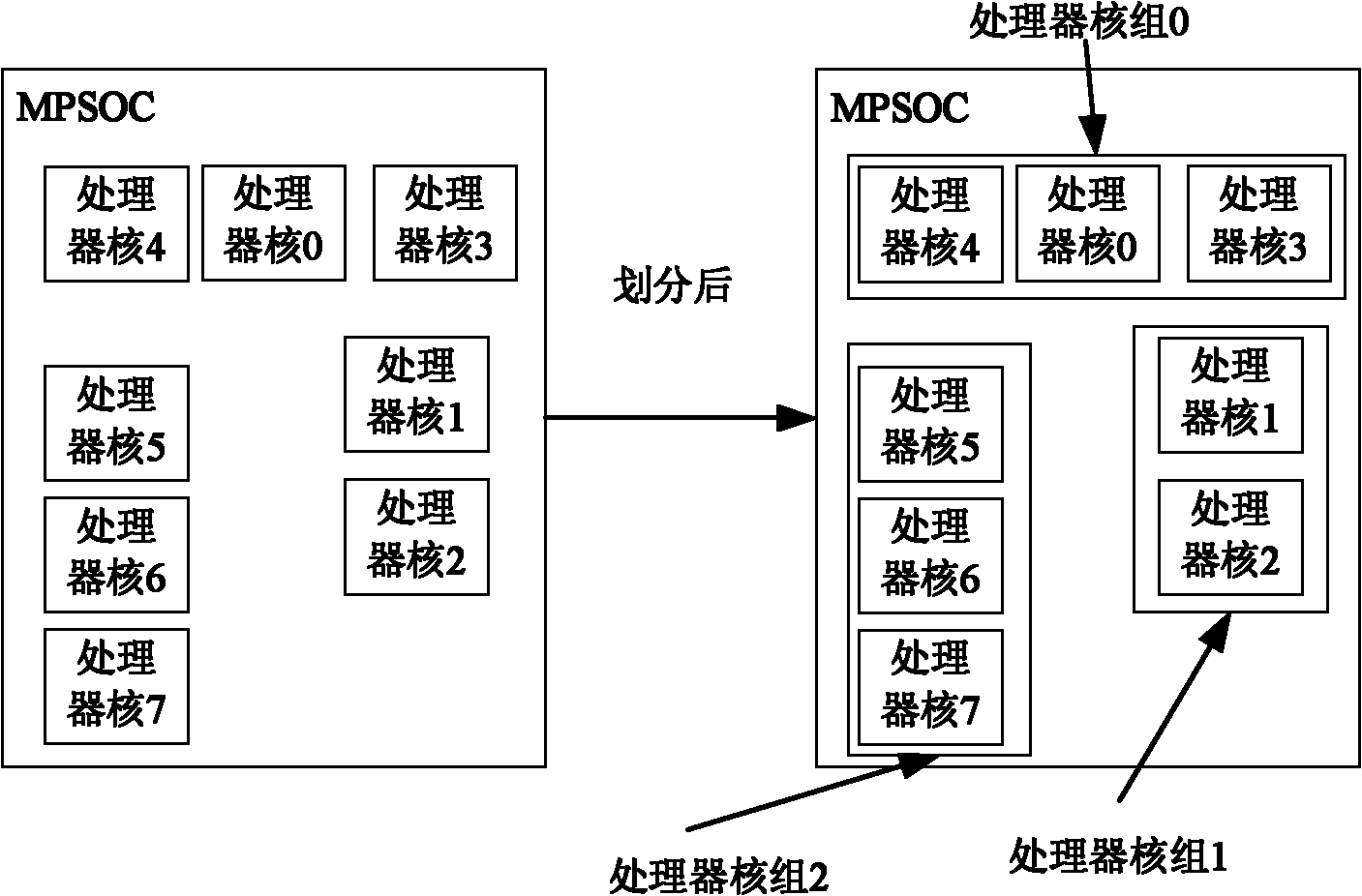

[0065] The first step is to divide the processor core group, and the processor has 8 processor cores. Its division method is as image 3 As shown, based on the physical location, processor core 0, processor core 3, and processor core 4 are divided into processor core group 0, processor core 1, and processor core 2 into processor core group 1. The processor core 5, the processor core 6, and the processor core 7 are divided into a processor core group 2.

[0066] In the fourth step, in thread scheduling, the same in-process thread is scheduled to the same ready queue. When dividing the processor core group, there are multiple processor cores in one processor core group. Therefore, when the multi-threads in the thread group are running, although the process can only use a certain processor core group, because the computing resources inside the processor core group are also abundant, when the pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More