Method for extracting and verifying latter interconnection delay model

A technology of delay model and verification method, which is applied in the field of extraction and verification of the delay model of the back-channel interconnection, can solve the problems of large calculation time and memory consumption, and achieves high parameter extraction accuracy, high speed, and easy extraction and verification methods. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The present invention will be further elaborated below in conjunction with the accompanying drawings and examples. The following examples do not limit the invention. Without departing from the spirit and scope of the inventive concept, changes and advantages that can be imagined by those skilled in the art are all included in the present invention.

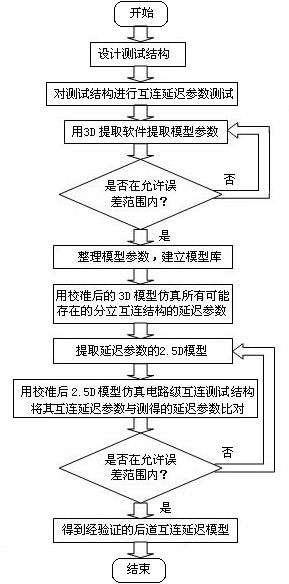

[0034] like figure 1 As shown, the method for extracting and verifying the back-channel interconnection delay model in this embodiment includes the following steps:

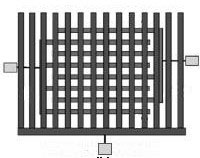

[0035] Step 1: Design a discrete interconnection test structure and a circuit-level interconnection test structure based on accurate integrated circuit process information. Among them, the integrated circuit process information includes the process conditions and process parameters adopted, such as the thickness of the electrical gate oxide E OT , channel doping concentration N CH and junction depth X j .

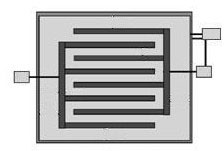

[0036] Wherein, the discrete interconnection te...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More