Method for analyzing chip failure

A failure analysis and chip technology, applied in electronic circuit testing, optical testing flaws/defects, non-contact circuit testing, etc., can solve problems such as difficult grinding and stripping accurate size parameters, save time and cost, and improve work efficiency Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

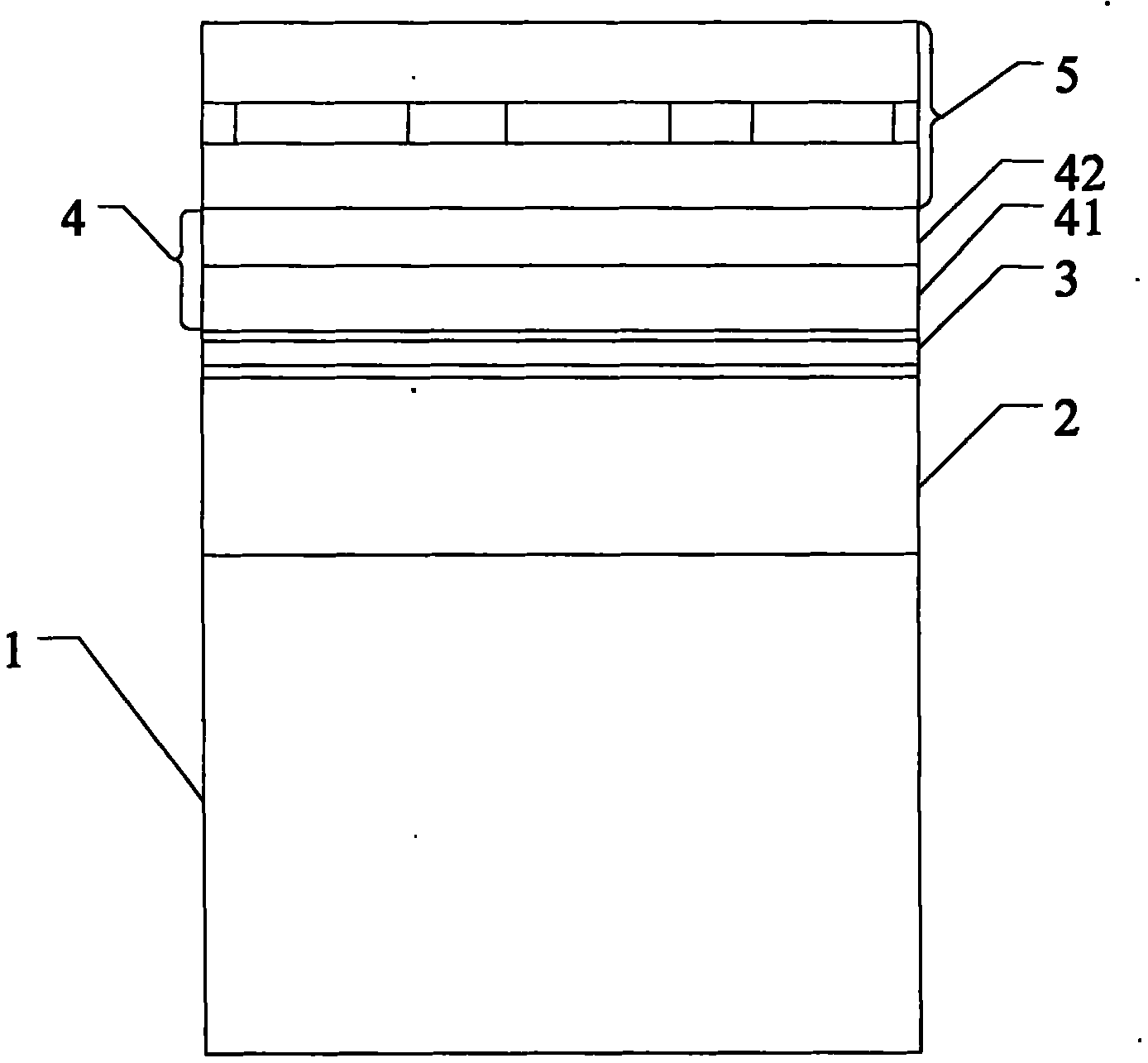

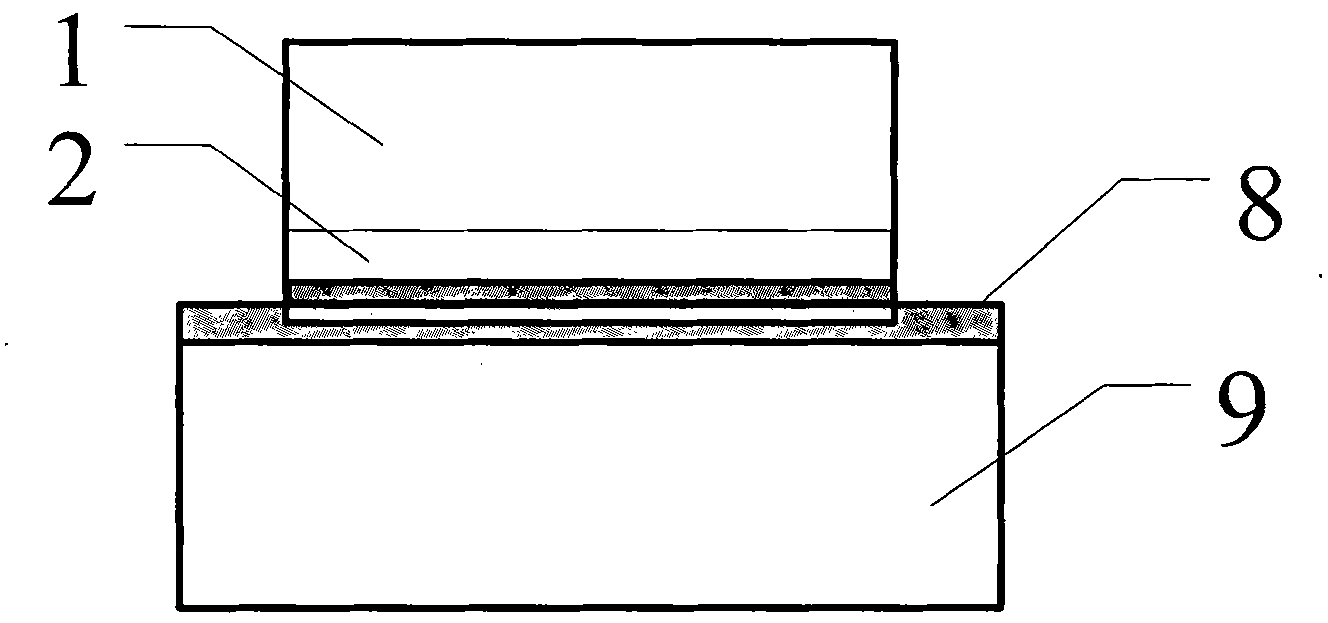

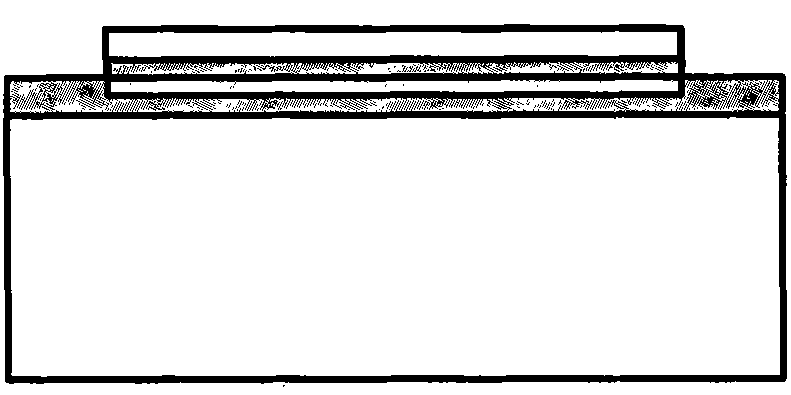

[0027] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0028] The chip failure analysis method described in the present invention can be widely used in the failure analysis of memory chips and other semiconductor chips, and can be realized in various alternative ways. The following is an illustration through a preferred embodiment, and of course the present invention is not limited In this specific embodiment, general substitutions known to those skilled in the art undoubtedly fall within the protection scope of the present invention.

[0029] Secondly, the present invention is described in detail using schematic diagrams. When describing the embodiments of the present invention in detail, for the convenience of illustration, the schematic diagrams are not partially enlarged according to th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More