Forming method of semiconductor structure and semiconductor structure

A technology of semiconductor and conductive structure, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as the influence of semiconductor electrical performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

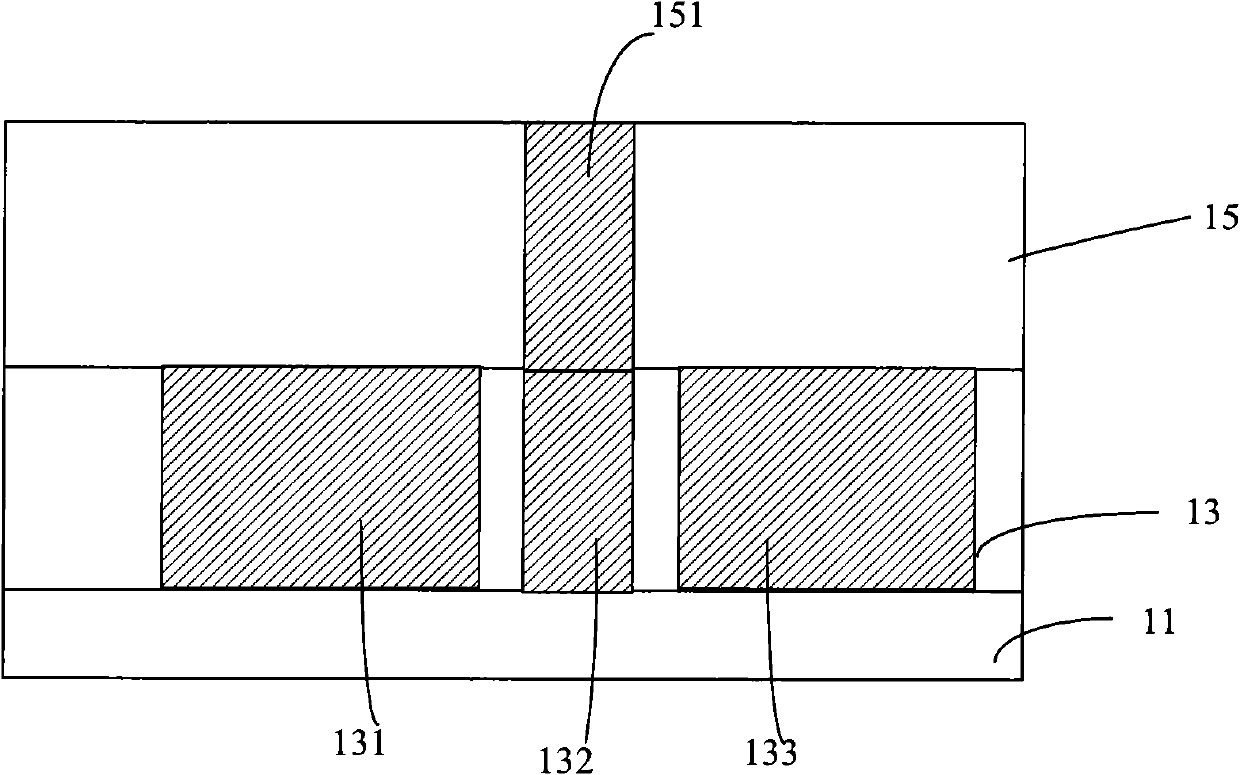

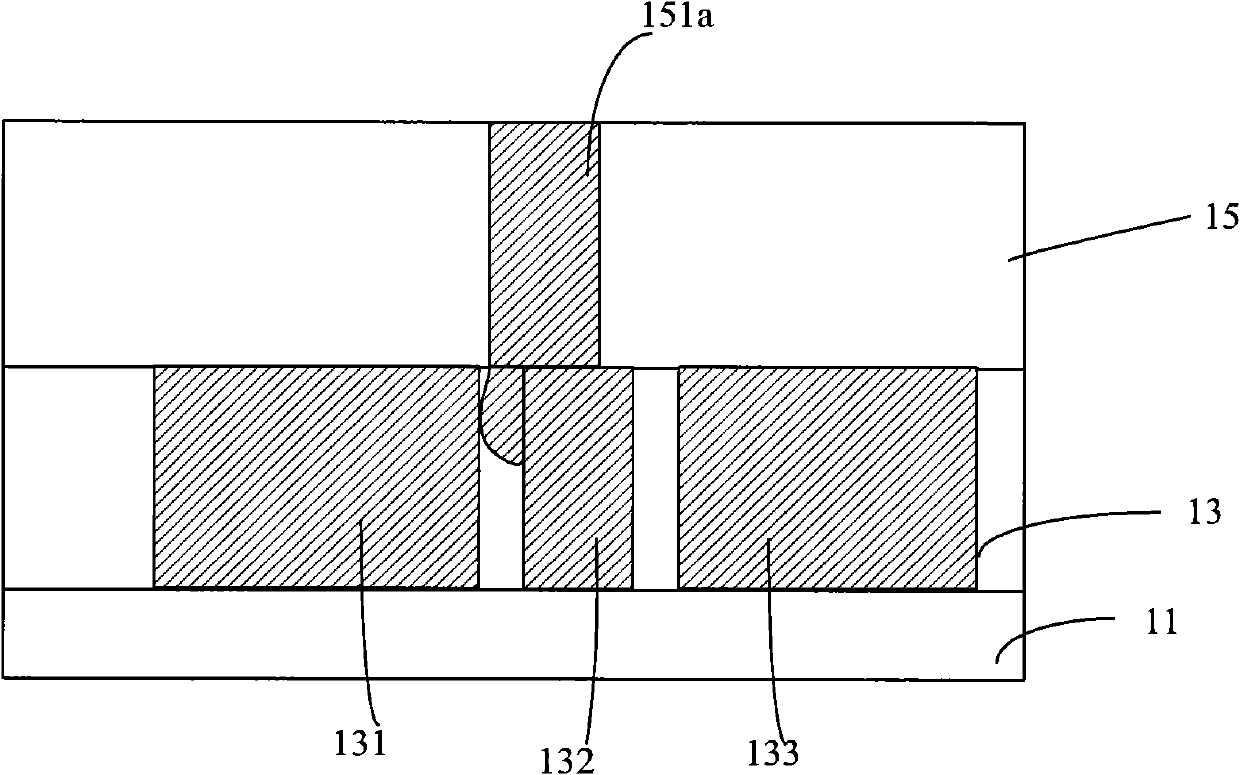

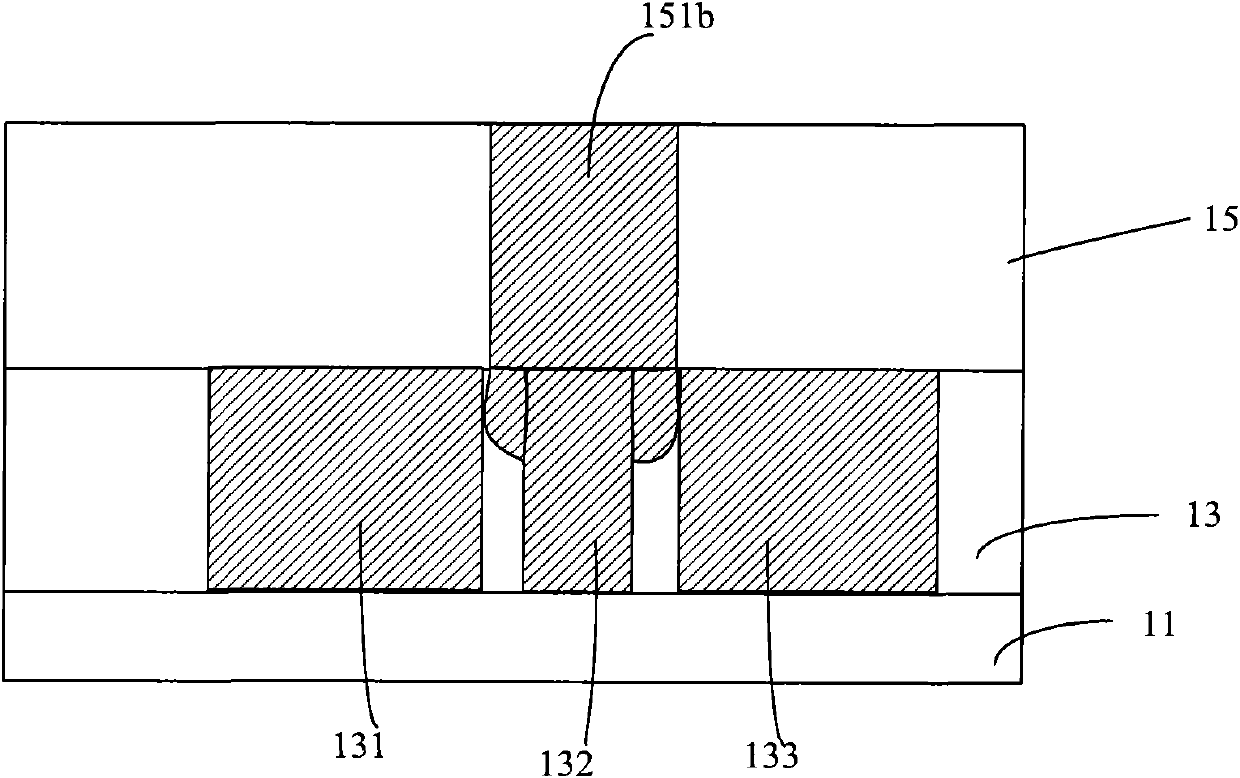

[0049] Figure 4 to Figure 8 It is a structural cross-sectional schematic diagram of a method for forming a semiconductor structure according to the first embodiment of the present invention.

[0050] First, if Figure 4 As shown, a substrate 21 is provided, and a first dielectric layer 23 is formed on the substrate 21 . The base 21 is formed with conductive structures (not shown).

[0051] The first dielectric layer 23 can be fluorine-doped silicon oxide, carbon-doped silicon oxide, or a porous medium layer formed by liquid colloidal silicon oxide-based materials. In this embodiment, the first dielectric layer 23 is Fluorine-doped silicon oxide is formed by chemical vapor deposition or plasma enhanced chemical vapor deposition.

[0052] Such as Figure 5 As shown, a first interconnection layer 231 , a second interconnection layer 232 , and a third interconnection layer 233 are formed in the first dielectric layer 23 through its thickness. The specific formation process i...

no. 2 example

[0068] Figure 9 to Figure 12 It is a schematic cross-sectional view of a method for forming a semiconductor structure according to a second embodiment of the present invention.

[0069] First, if Figure 9 A substrate 31 is shown having conductive structures formed therein.

[0070] A first dielectric layer 33 and an etch stop layer 35 are formed on the substrate 31 .

[0071] The first dielectric layer 33 can be fluorine-doped silicon oxide, carbon-doped silicon oxide, or a porous medium layer formed by liquid colloidal silicon oxide-based materials. In this embodiment, the first dielectric layer 33 is Fluorine-doped silicon oxide is formed by chemical vapor deposition.

[0072] The etch barrier layer 35 can be silicon nitride or silicon oxynitride, and the thickness range of the etch barrier layer 35 is The etching barrier layer 35 is formed by chemical vapor deposition or plasma enhanced chemical vapor deposition. As an embodiment, the etch stop layer 35 is silicon ni...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More