Electrostatic protection circuit of submicron integrated circuit

An integrated circuit, electrostatic protection technology, used in circuits, electrical components, electrical solid devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

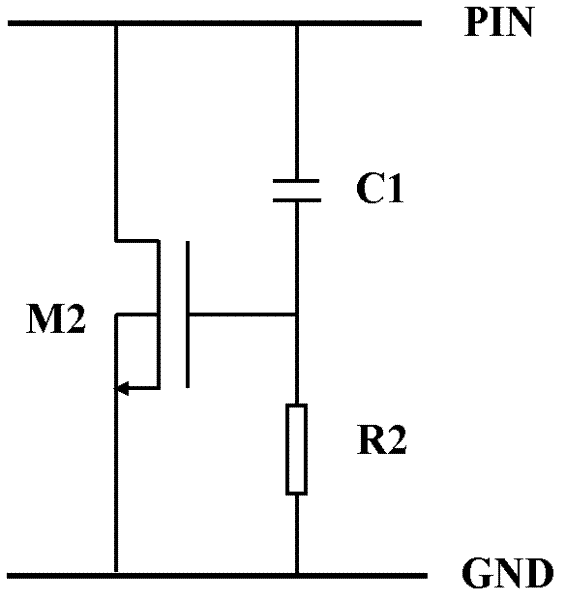

[0016] A submicron integrated circuit electrostatic protection circuit, used for ESD protection of internal circuits, such as Figure 4 shown, including:

[0017] NMOS tube (M3) is an ESD discharge tube, the drain of M3 is connected to the internal PIN of the protected circuit, the source and substrate of M3 are short-circuited to GND, and C2 is the parasitic capacitance between the gate and drain of M3 , the gate of M3 is connected to the drain of the NMOS transistor (M4);

[0018] The drain of M4 is connected to the gate of M3, the source of M4 is shorted to the substrate and connected to GND, and the gate of M4 is connected to the negative terminal of R2 and the positive terminal of C3;

[0019] The positive terminal of R2 is connected to the power supply VCC, the negative terminal of R2 is connected to the gate of M4, and the resistance of R2 is 10~20KΩ;

[0020] The positive terminal of C3 is connected to the gate of M4, the negative terminal of C3 is connected to GND, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More