Semiconductor packaging structure with multiple convex block structures

A packaging structure and semiconductor technology, which is applied in the direction of semiconductor devices, semiconductor/solid-state device parts, electric solid-state devices, etc., can solve the problems of semiconductor packaging reliability test, bump increase, etc., and achieve the effect of ensuring reliability and avoiding failure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

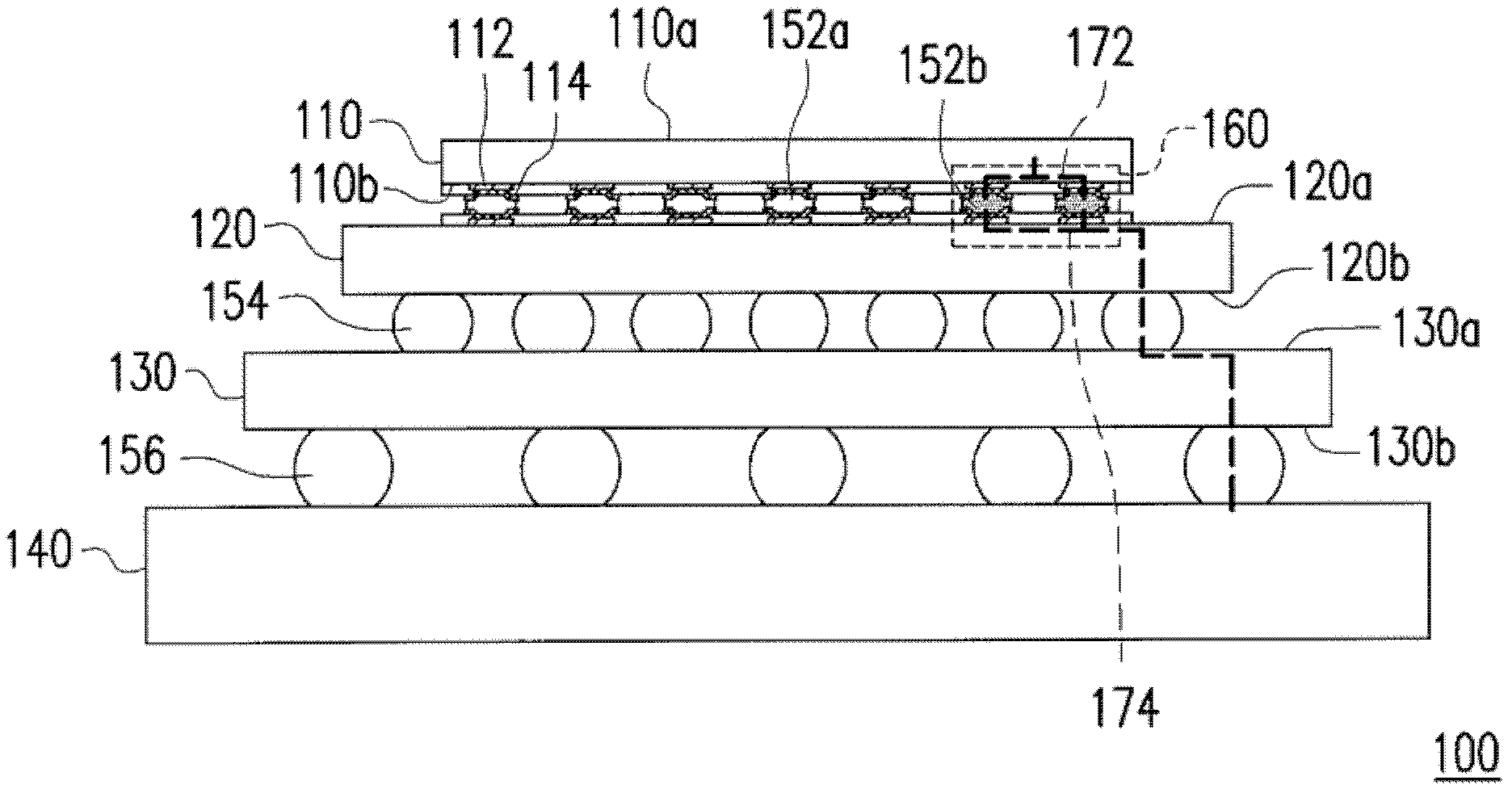

[0017] Reference figure 1 , Which illustrates a semiconductor package structure 100 according to an embodiment of the present invention. The semiconductor package structure 100 is formed by stacking semiconductor elements 110-140.

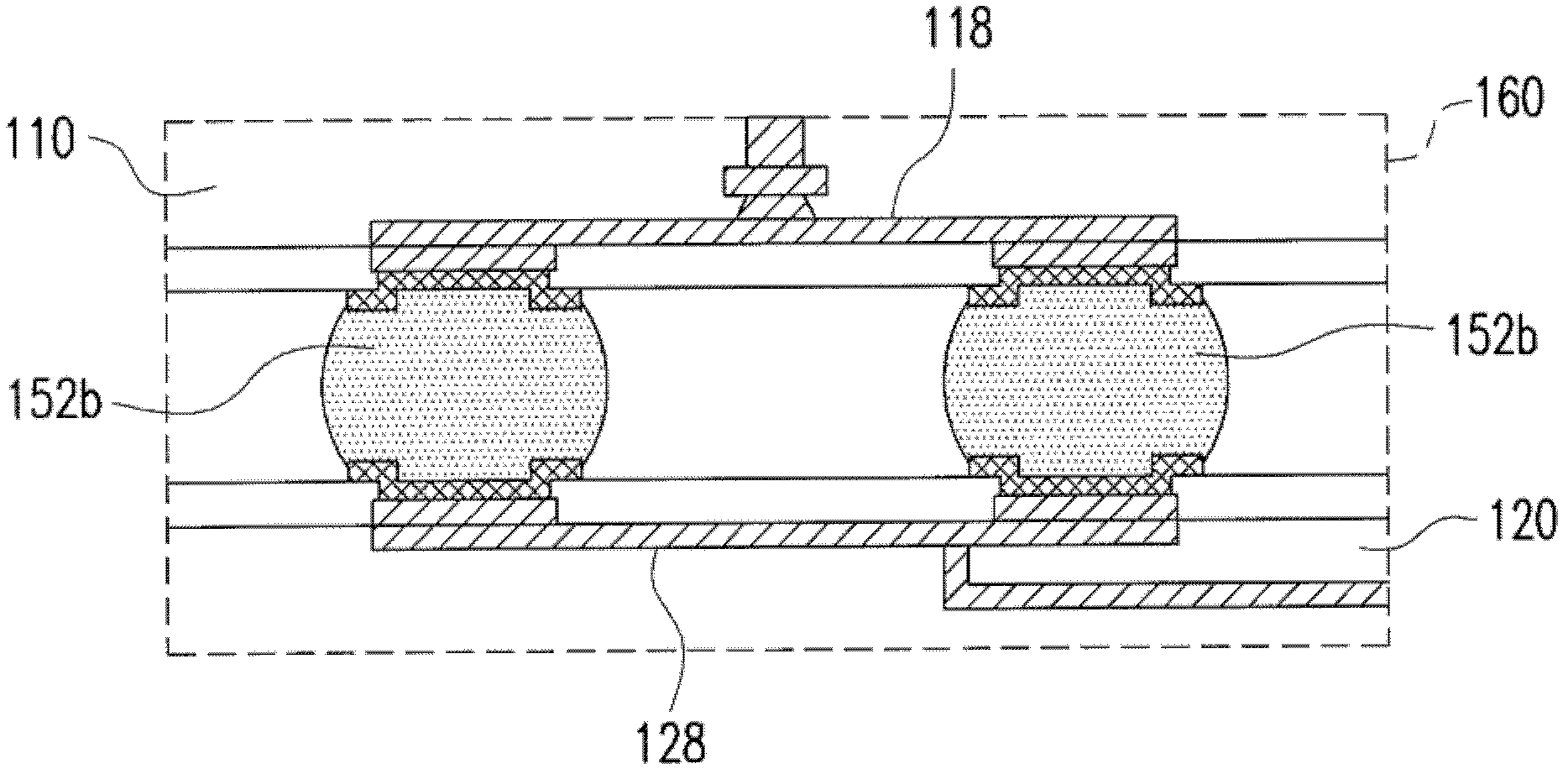

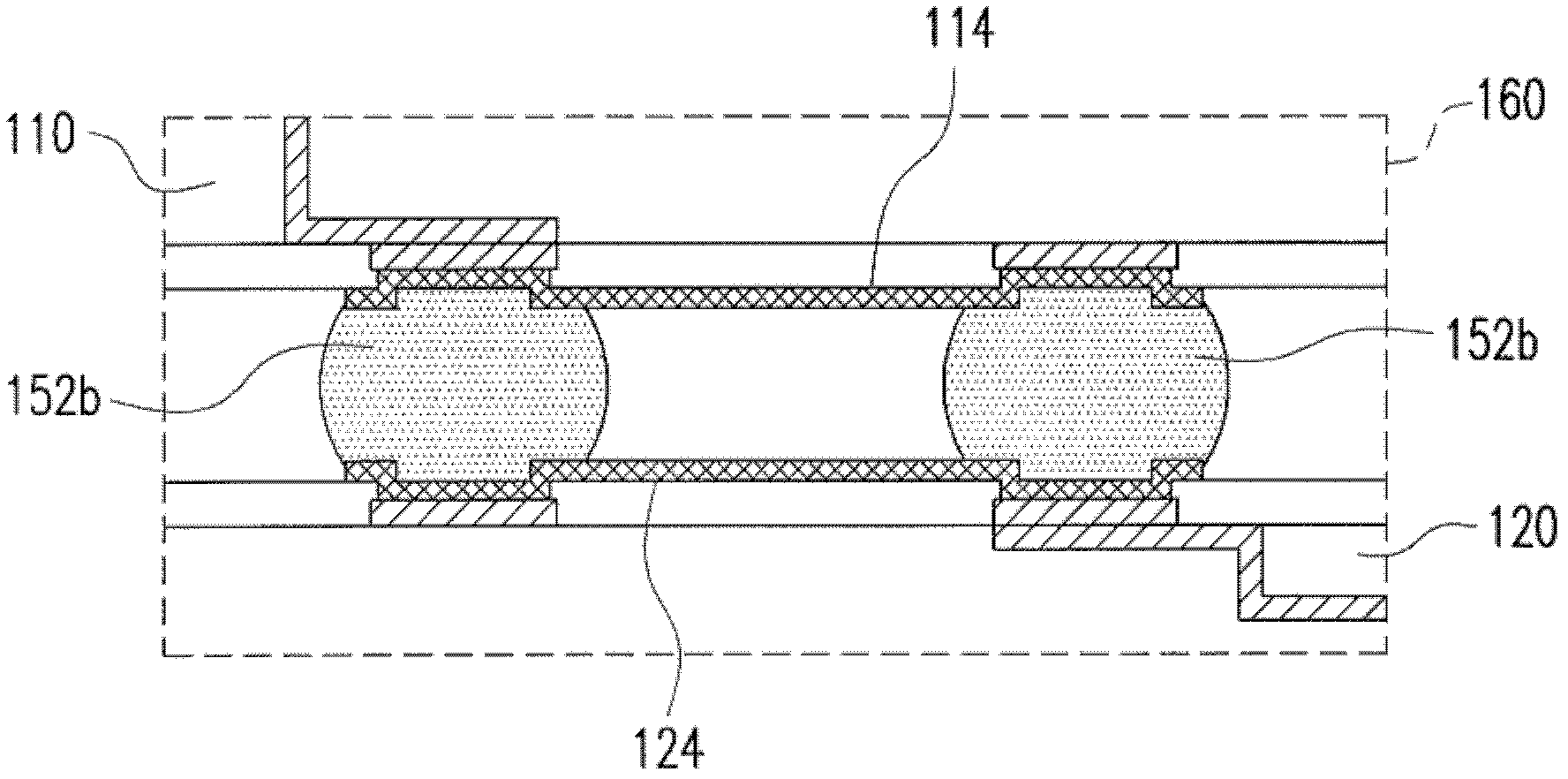

[0018] The semiconductor device 110, in this embodiment, is, for example, a chip, and has an upper surface 110a and a lower surface 110b. The lower surface 110b has a plurality of bonding pads 112, and a plurality of bottom metal layers 114 are disposed on the bonding pads 112. The semiconductor device 110 can be bonded to the semiconductor device 120 through the first bumps 152 a and the second bumps 152 b disposed on the underlying metal layer 114. The first bump 152a is disposed in the middle area of the lower surface 110b of the semiconductor device 110, the second bump 152b is disposed in the corner area of the lower surface 110b of the semiconductor device 110, and the second bump 152b surrounds the first Bumps 152, and the second bump 152b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More