Clock generation circuit

A clock generation circuit, a technology for inputting a clock, applied in the direction of electrical pulse generator circuits, electrical components, generating/distributing signals, etc., can solve problems such as PLL loss of synchronization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

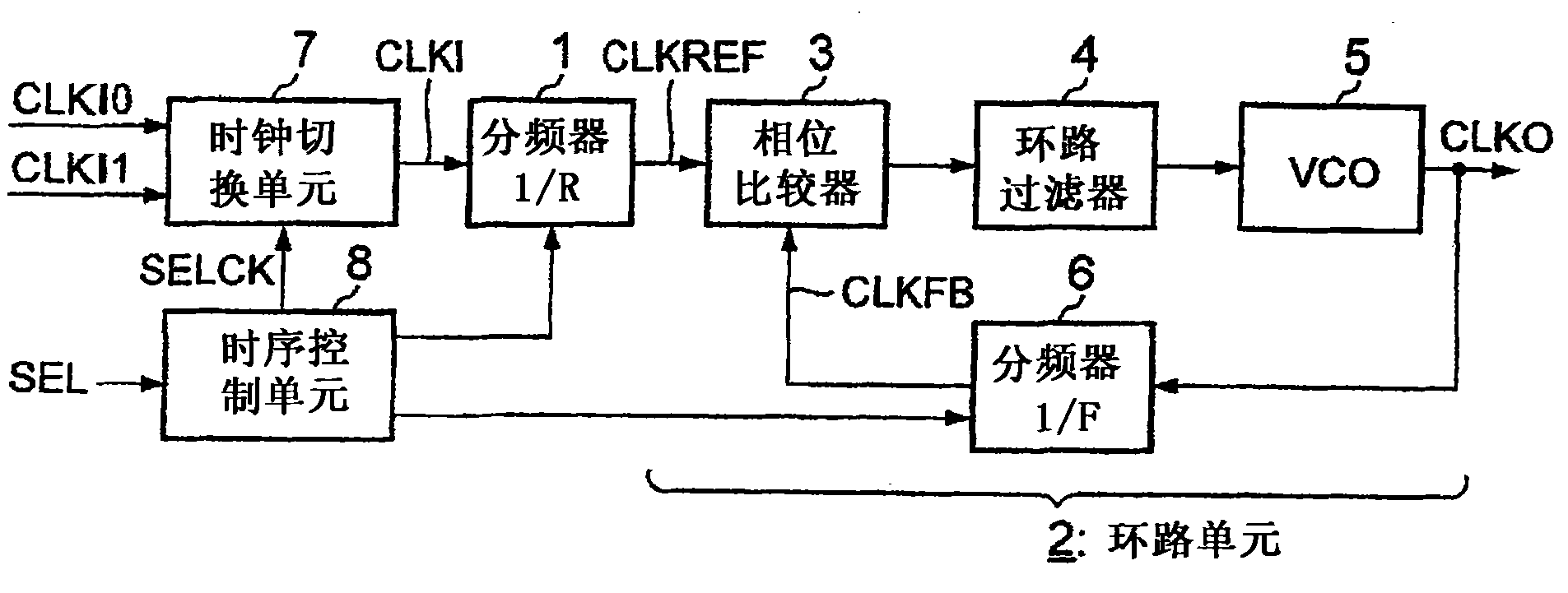

[0034] figure 1 is a block diagram showing the basic configuration of the clock generation circuit according to the first embodiment of the present invention. exist figure 1 , the circuit configuration of the part having frequency divider 1 and loop unit 2 is basically the same as Figure 12 same as shown in .

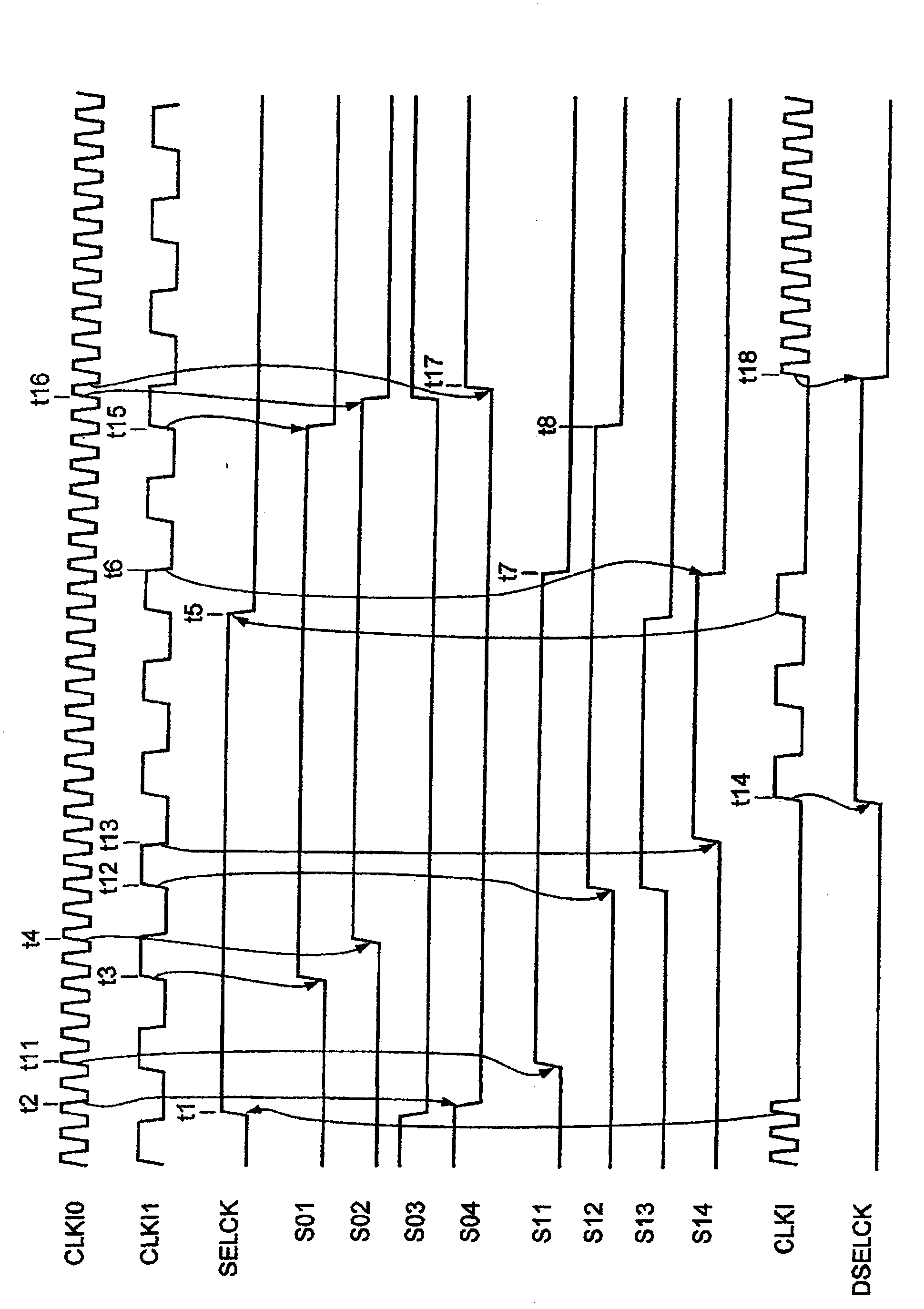

[0035] The clock generation circuit according to the first embodiment of the present invention is characterized by a clock switching unit 7 and a timing control unit 8 added to a circuit having a frequency divider 1 and a loop unit 2 . The input clocks CLKI0 and CLKI1 having frequencies different from each other are output to the clock switching unit 7 . The clock switching unit 7 selects one of the input clocks CLKI0 and CLKI1 according to the clock selection command SELCK output from the timing control unit 8 and supplies the selected clock to the frequency divider 1 as the input clock CLKI. The timing control unit 8 generates a clock selection command SELCK for...

no. 2 example

[0077] Figure 8 is a circuit diagram showing the configuration of a clock generating circuit according to a second embodiment of the present invention. Figure 9 is a timing chart showing the outline operation of the clock generation circuit, and Figure 10 is a time chart showing waveforms of respective units according to an embodiment of the present invention. According to the first embodiment of the present invention described above, in the case of switching the clock selection information SEL, the count value CNT1 of the input clock CLKI in the frequency divider 1 becomes "0" thereafter, and when the reference clock CLKREF is output, The clock selection command SELCK is switched to match the clock selection information SEL. According to the second embodiment of the present invention, such as Figure 9 As shown in , for example, in the case where the clock selection information SEL is switched from "0" to "1" in the period in which the frequency divider 1 performs the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com