Electrostatic discharge protection circuit

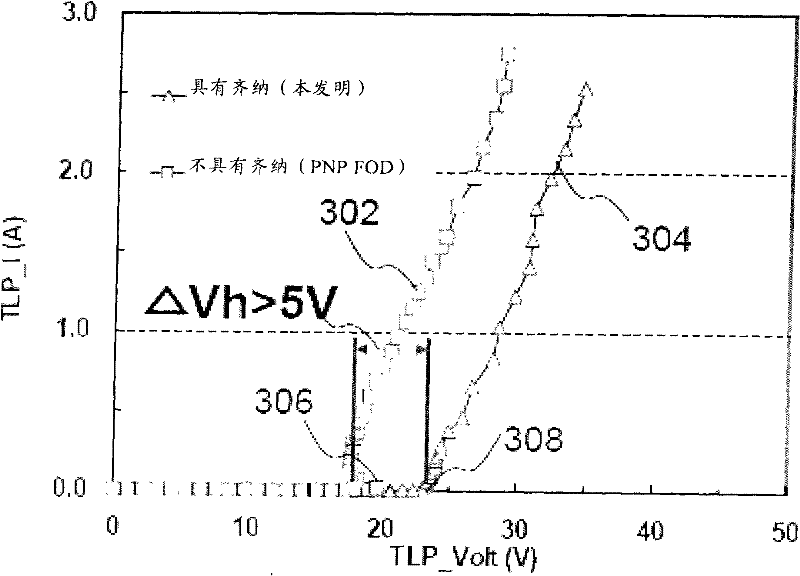

A technology for electrostatic discharge and protection of equipment, applied in the field of circuits, which can solve problems such as insufficient holding voltage, latch failure, large chip area, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The construction and use of the presently preferred embodiments are discussed in detail below. It should be appreciated, however, that the present invention provides many useful inventive concepts that can be implemented in a wide variety of specific contexts. The specific embodiments discussed are merely examples of specific ways to make and use the invention, and do not limit the scope of the invention.

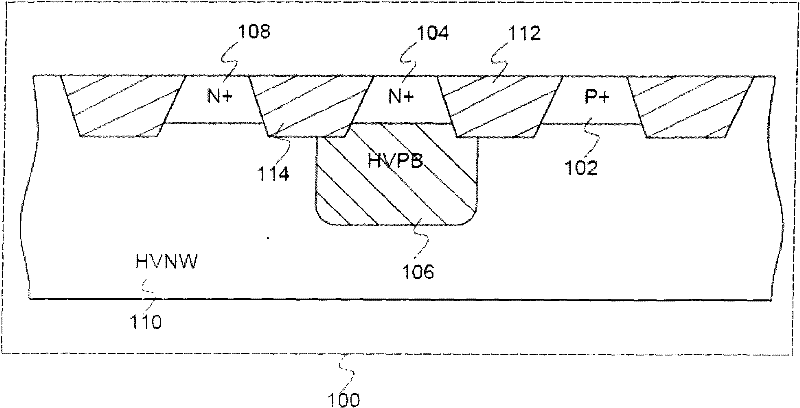

[0036] figure 1 A simplified cross-sectional view of an ESD protection structure 100 according to one embodiment is shown. The ESD protection structure 100 includes a P+ region 102, a first N+ region 104, a second N+ region 108, a first isolation region 112, a second isolation region 114, a high voltage P-type implant region 106 and a high voltage N well (HVNW) 110 . The first N+ region 104 and the high voltage P-type implant region 106 are sequentially disposed on the HVNW 110 . The high voltage P-type implantation region 106 is disposed under the first N+ regio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More