Semiconductor structure and manufacture method thereof

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as unfavorable short channel effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

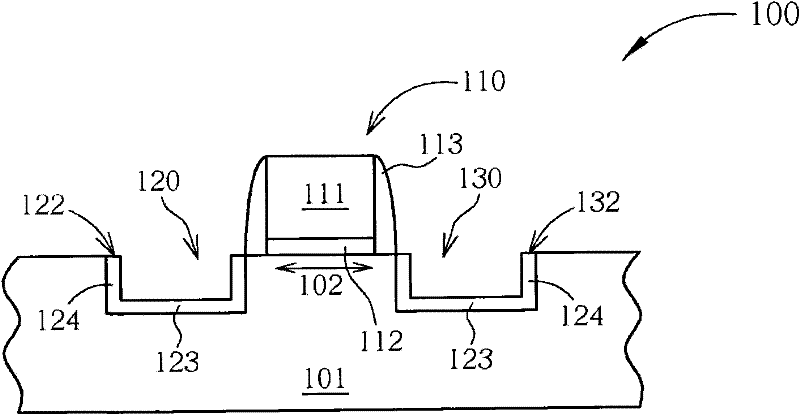

[0043] The invention provides a semiconductor structure and a manufacturing method thereof. The semiconductor structure of the present invention has a non-doped epitaxial layer close to the cavity and used as a buffer layer. These non-doped epitaxial layers can isolate the back diffusion of dopants in the doped epitaxial layer. In addition, the non-doped epitaxial layers have appropriate thicknesses, so the stress generated by the doped epitaxial layers will not be affected.

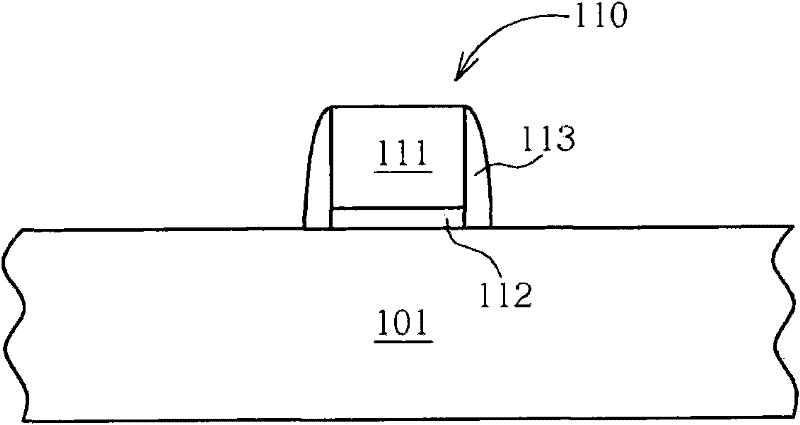

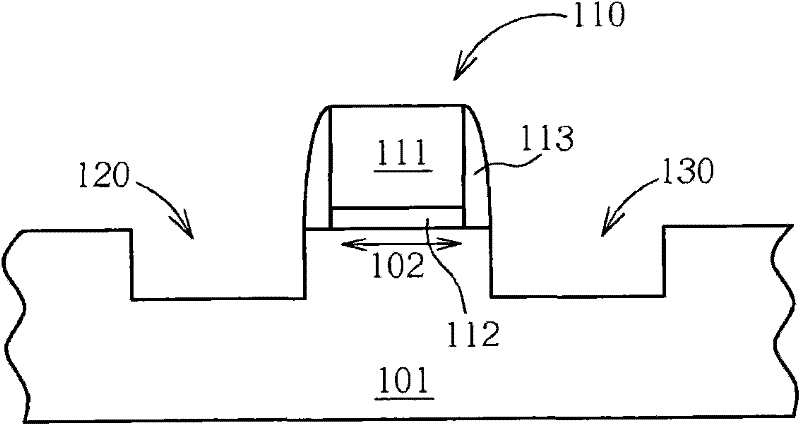

[0044] The present invention firstly provides a method for manufacturing a semiconductor structure. Figure 1-Figure 5 A schematic flow chart illustrating a method for fabricating a semiconductor structure of the present invention. Please refer to figure 1 , first provide a substrate 101 . The substrate 101 is usually a semiconductor substrate, such as silicon with a single crystal structure. Next, a gate structure 110 is formed on the substrate 101 . The required gate structure 110 can be formed o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More