Layout bipartition method

A two-partition and layout technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of high density, affecting the quality of chip manufacturing, and the production cost has no good prospects, etc., to achieve high accuracy and partition Reasonable results and convenient follow-up adjustments

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

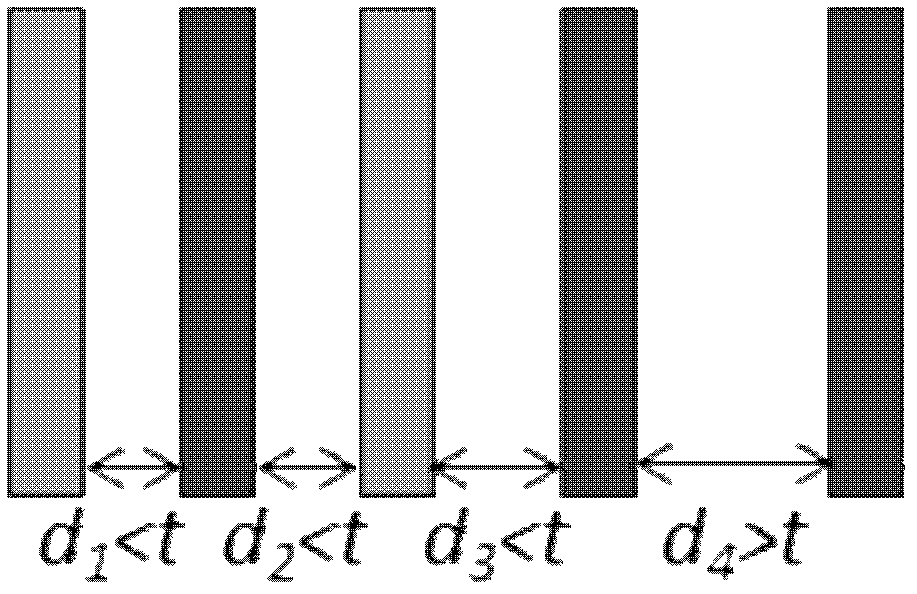

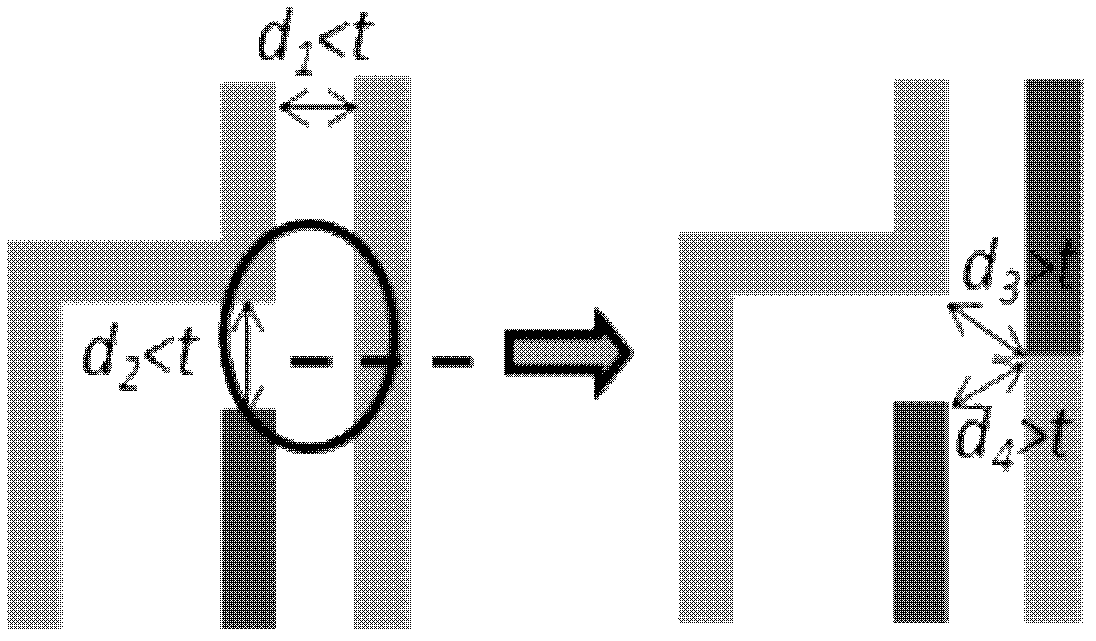

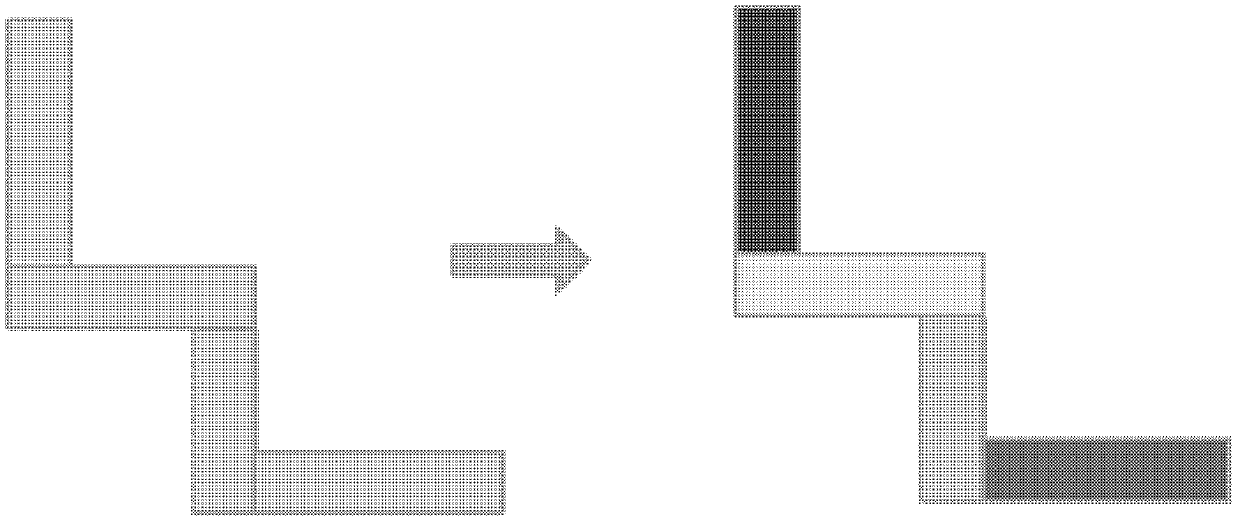

[0048] The double layout lithography technology is a method to solve the defect that the product quality is reduced due to the excessive layout density in the lithography process. The double layout lithography technology refers to dividing the content on a mask with high density into two masks at intervals on the basis of the existing lithography technology, so that the transistors on the two masks The density meets the standard of the existing photolithography technology, and then undergoes two photolithography etchings to restore the original mask. The principle is as Figure 1 to Figure 3 shown.

[0049] The invention proposes a method for bipartitioning the layout of an integrated circuit, by using the method, the layout of an integrated circuit can be reasonably divided into two according to the requirements of the double layout photolithograph...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com