Low-power-consumption clock frequency detection circuit

A technology of clock frequency and detection circuit, applied in the direction of frequency measurement device, etc., can solve the problem of leakage of confidential data by security chip, and achieve the effect of preventing information leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

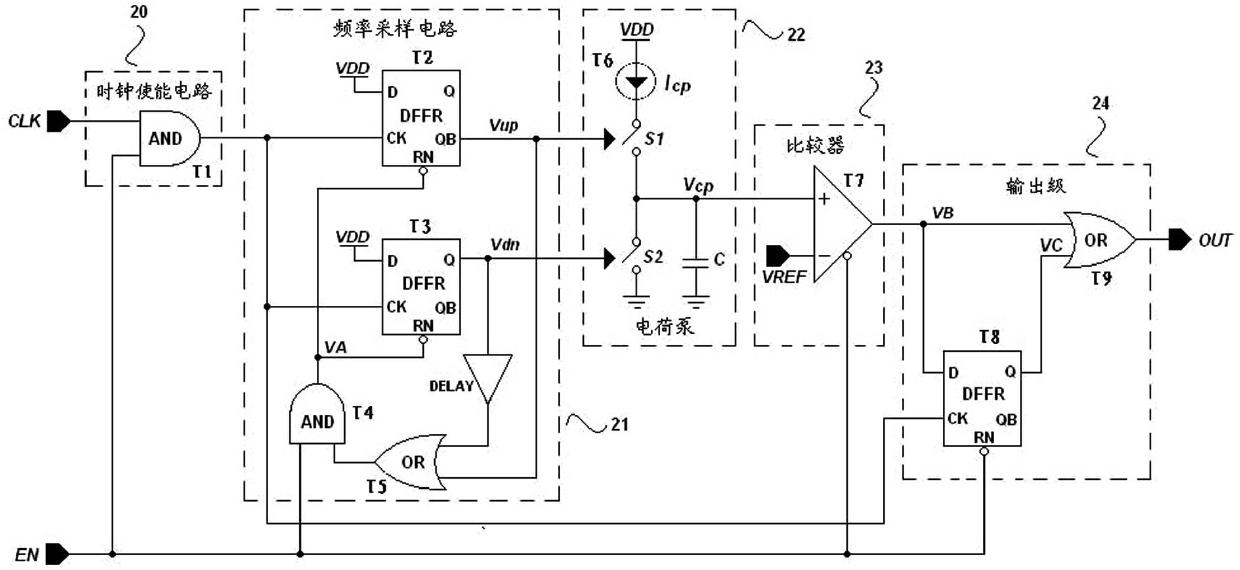

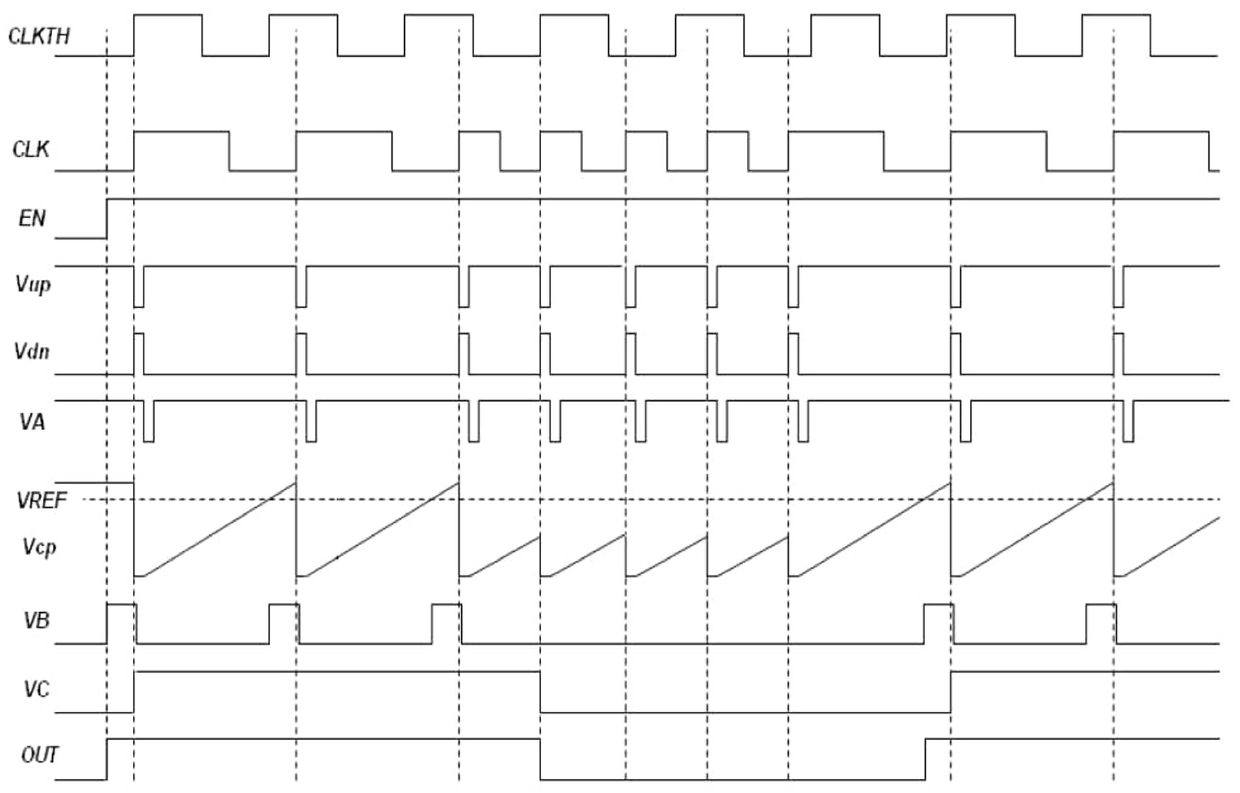

[0019] See figure 1 and figure 2 . The low power consumption clock frequency detection circuit of the present invention includes a clock enabling circuit 20 , a frequency sampling circuit 21 , a charge pump 22 , a comparator 23 and an output stage 24 connected in sequence. in:

[0020] The input terminals of the clock enable circuit 21 are respectively connected to the system clock terminal CLK and the system enable terminal EN, and output the system clock when the enable signal input by the system enable terminal is valid.

[0021] The system clock terminal CLK is used to input the system clock, and the system enable terminal EN is used to input the system enable signal.

[0022] In this specific embodiment, the clock enabling circuit 21 is composed of a first AND gate T1, and the two input terminals of the first AND gate T1 are respectively connected to the system clock terminal CLK and the system enable terminal EN.

[0023] The input terminal of the frequency sampling...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com