Over-erasing processing method and system for nonvolatile memory

A technology of non-volatile memory and processing method, which is applied in the field of semiconductor memory, can solve problems such as VT, and achieve the effects of improving accuracy, saving time, and ensuring accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

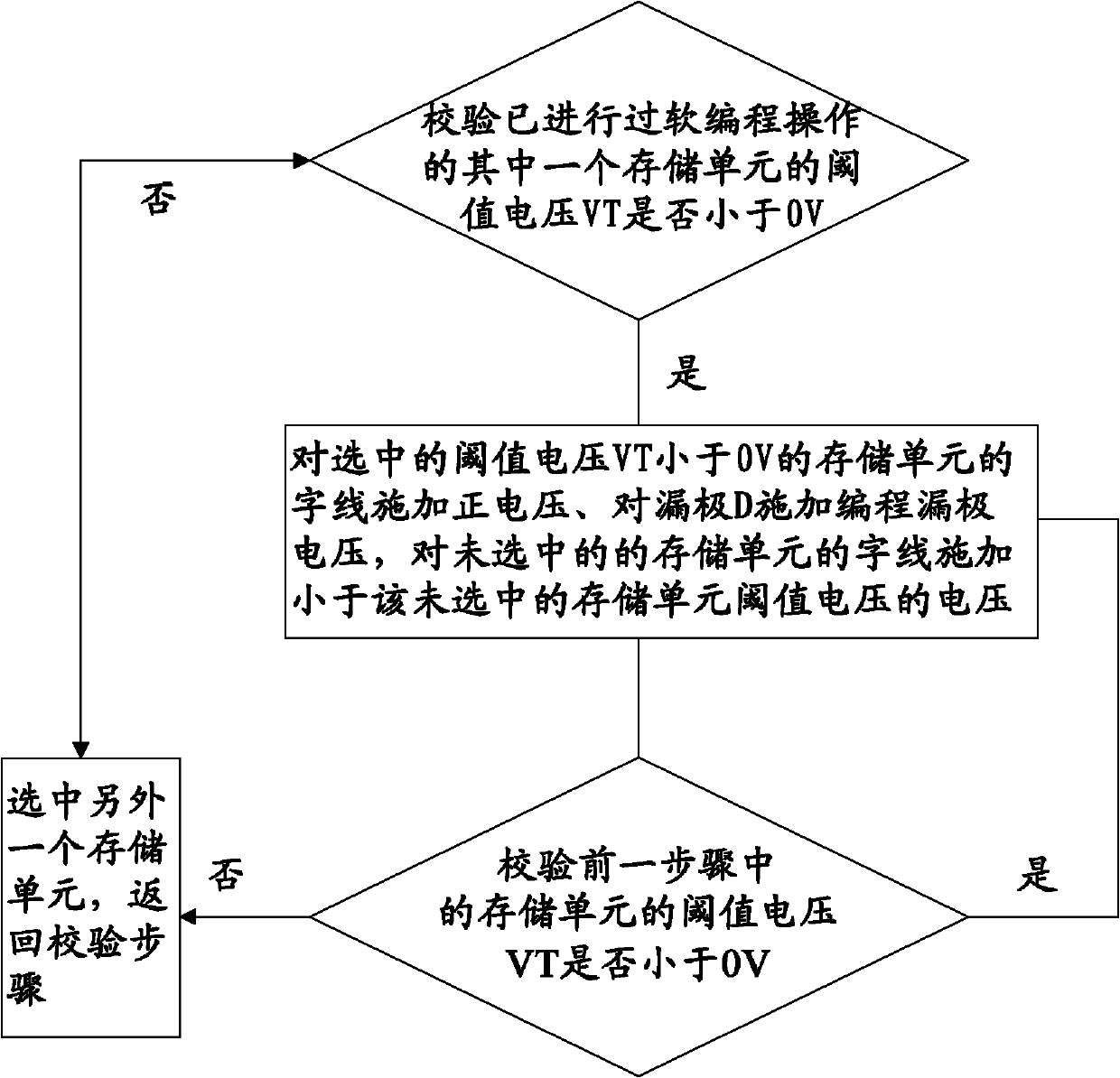

[0044] Please refer to figure 1 , showing a first embodiment of a non-volatile memory over-erasing processing method of the present invention, including the following steps:

[0045] 101. Verification: Select a memory cell that has undergone a soft programming operation, and verify whether the threshold voltage VT of the selected memory cell is less than 0V, if yes, perform step 102; if not, select another memory cell for calibration test;

[0046] 102. Voltage application: apply a positive voltage to the wordline (wordline, WL) of the selected memory cell whose threshold voltage VT is less than 0V, and apply a programming drain voltage to the drain D, and apply a voltage lower than the unselected memory cell to the wordline of the unselected memory cell. The voltage of the threshold voltage VT of the selected memory cell;

[0047] 103. Verifying again: verifying the threshold voltage V of the memory cell processed in step 102 T Whether it is less than 0V, if so, return to ...

Embodiment 2

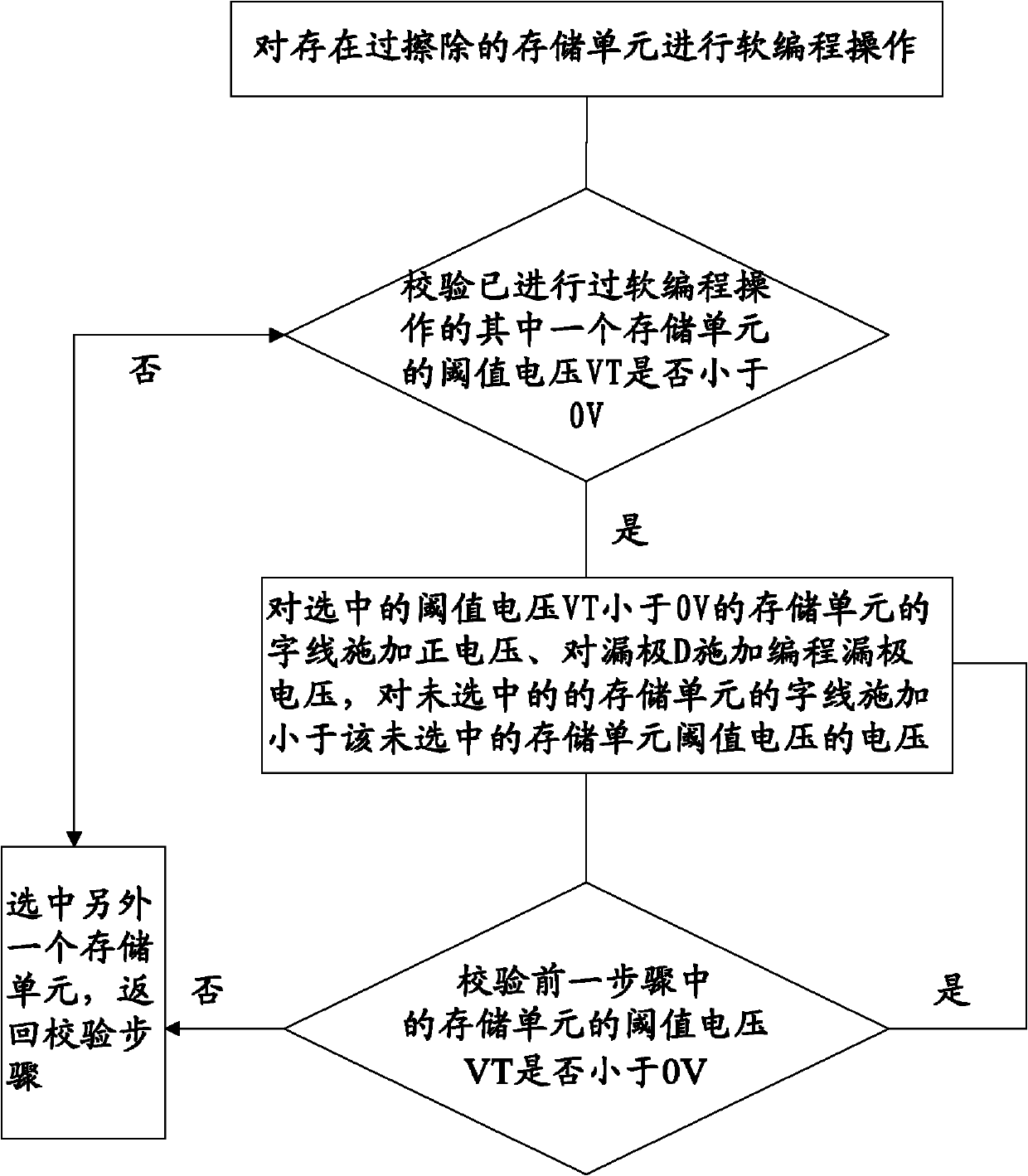

[0051] Please refer to figure 2 , showing a second embodiment of an over-erasing processing method for a non-volatile memory of the present invention, including the following steps:

[0052] 201. Soft programming: performing a soft programming operation on memory cells that have been erased;

[0053] 202. Verify: select a memory cell that has undergone a soft programming operation, and verify the threshold voltage V of the selected memory cell T Whether it is less than 0V, if so, then execute step 203; if not, then select another storage unit to verify;

[0054] 203. Voltage application: for the selected threshold voltage V T Apply a positive voltage to the wordline (wordline, WL) of the memory cell less than 0V, apply a programming drain voltage to the drain D, and apply a threshold voltage less than or equal to the threshold voltage V of the unselected memory cell to the wordline of the unselected memory cell T voltage;

[0055] 204, check again: check the threshold vol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More