Method for processing video processing tasks by aid of multi-core processing chip and system using method

A video processing and processing chip technology, applied in the field of video processing, can solve the problems of priority control failure, waste of HDVICP, waste, etc., to achieve the effect of convenient sharing and management, saving memory space, and improving utilization rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] In the following description, many technical details are proposed in order to enable readers to better understand the application. However, those skilled in the art can understand that without these technical details and various changes and modifications based on the following implementation modes, the technical solution claimed in each claim of the present application can be realized.

[0039] In order to make the purpose, technical solution and advantages of the present invention clearer, the following will further describe the implementation of the present invention in detail in conjunction with the accompanying drawings.

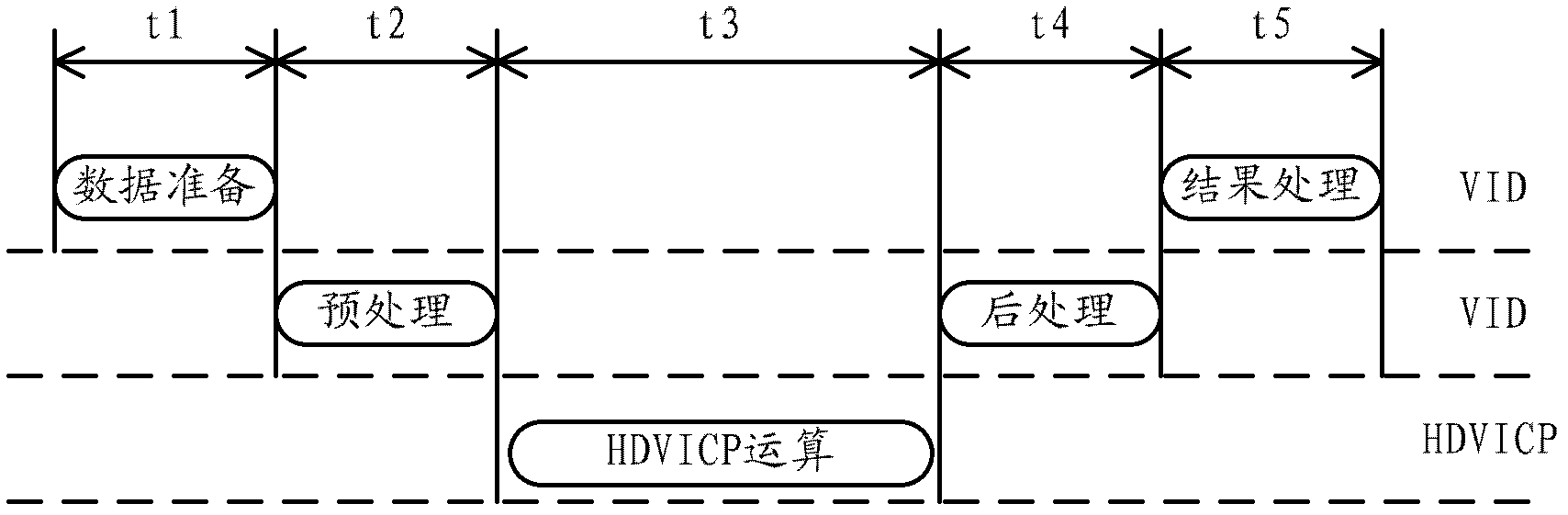

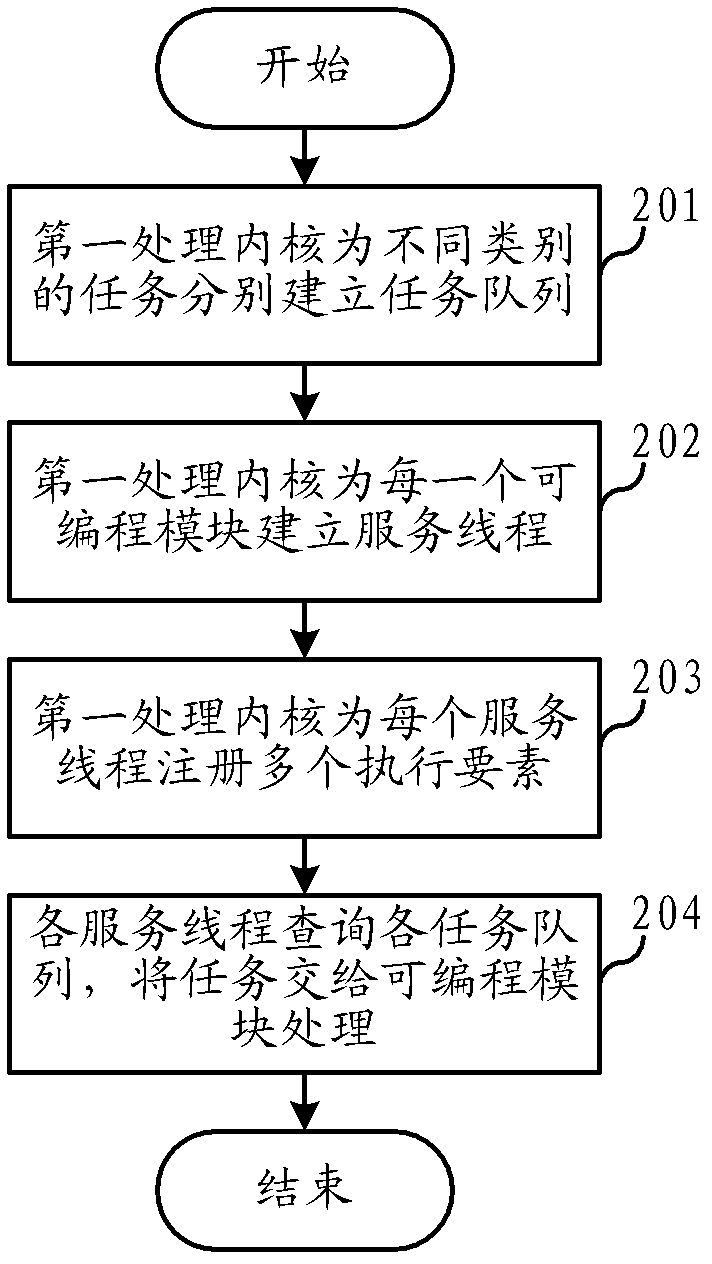

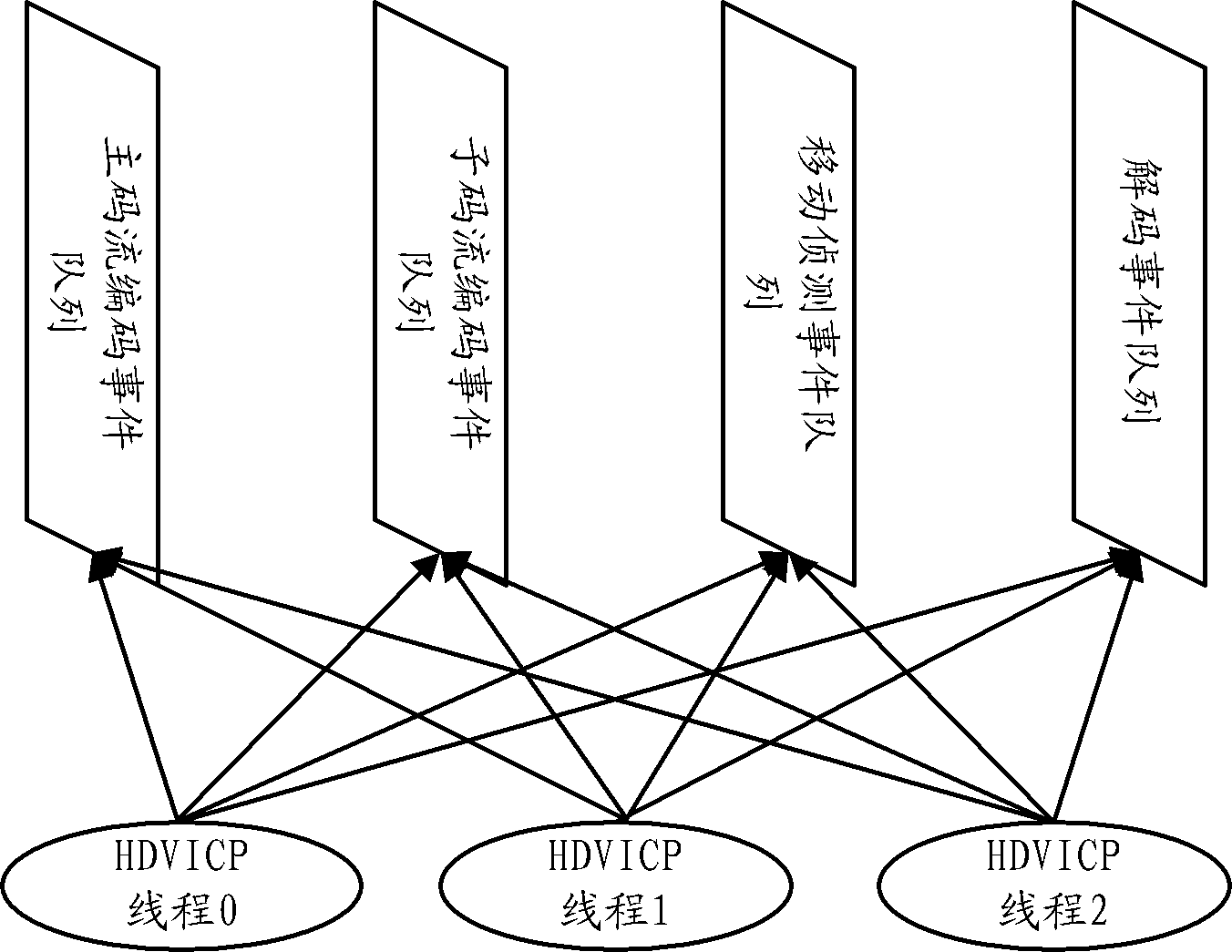

[0040] The first embodiment of the present invention relates to a method for processing video processing tasks by a multi-core processing chip. figure 2 It is a schematic flowchart of a method for processing video processing tasks by the multi-core processing chip. The chip includes a plurality of programmable modules for video processing, a fir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More