Transistor capable of improving tunnel penetration field effect

A field-effect transistor and tunneling technology, which is applied in the field of formation of enhanced tunnel penetration field-effect transistors, can solve the problems of not being able to suppress the bipolar conduction effect of the device well, the performance of the TFET device needs to be improved, and the operating speed of the device is reduced. Achieve the effects of suppressing the bipolar conduction effect, increasing the probability of tunnel penetration, and reducing the reverse control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

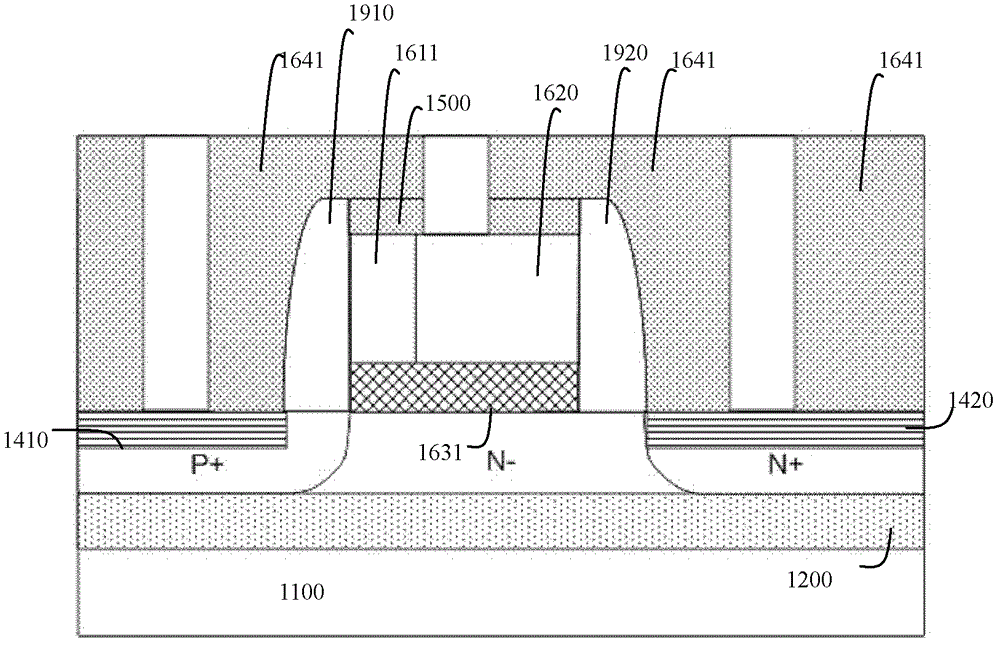

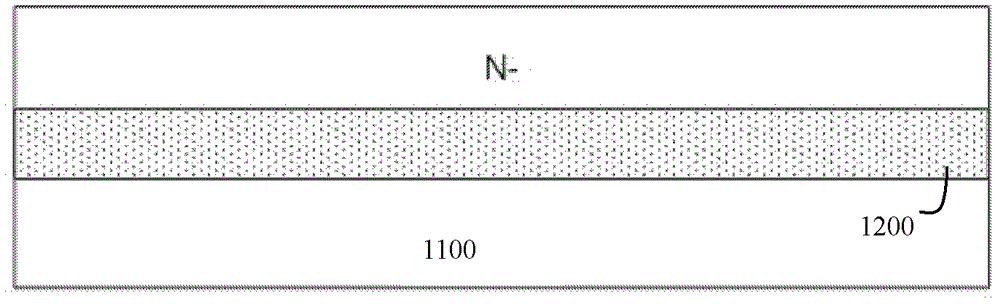

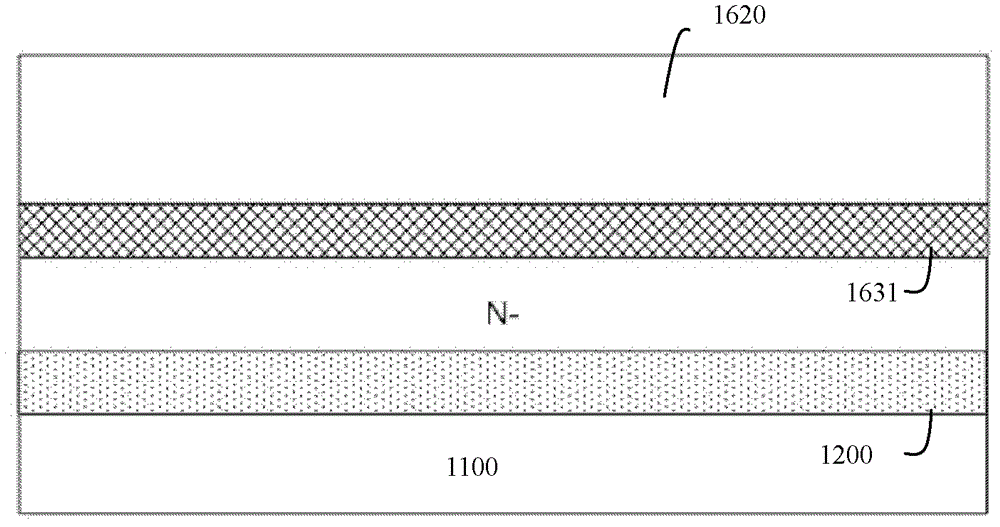

[0016] Such as figure 1 Shown is a diagram of an n-type enhanced tunneling field effect transistor according to an embodiment of the present invention. In the embodiment of the present invention, the n-type enhanced tunneling field effect transistor includes: a substrate 1100, a semi-insulating layer or insulating layer 1200, a channel region formed in the substrate 1100, and a channel region formed in the channel A source region and a drain region on both sides of the channel region, wherein the doping types of the drain region and the source region are opposite. The n-type enhanced tunneling field effect transistor further includes ohmic contact layers 1410 and 1420 on the source region and the drain region, and a gate stack formed on the channel region, wherein the gate stack includes a gate dielectric layer 1631, the gate stack further includes at least a first gate electrode 1611 and a second gate electrode 1620 distributed along the direction from the source region to t...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap