Photoetching simulation method and device

A simulation method and lithography technology, applied in the field of lithography simulation, can solve problems such as slow speed and affect the design efficiency of integrated circuits, and achieve the effect of improving simulation speed and reducing simulation computing tasks.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings. While illustrations of parameters including particular values may be provided herein, it should be understood that parameters need not be exactly equal to the corresponding values, but rather may approximate the values within acceptable error margins or design constraints.

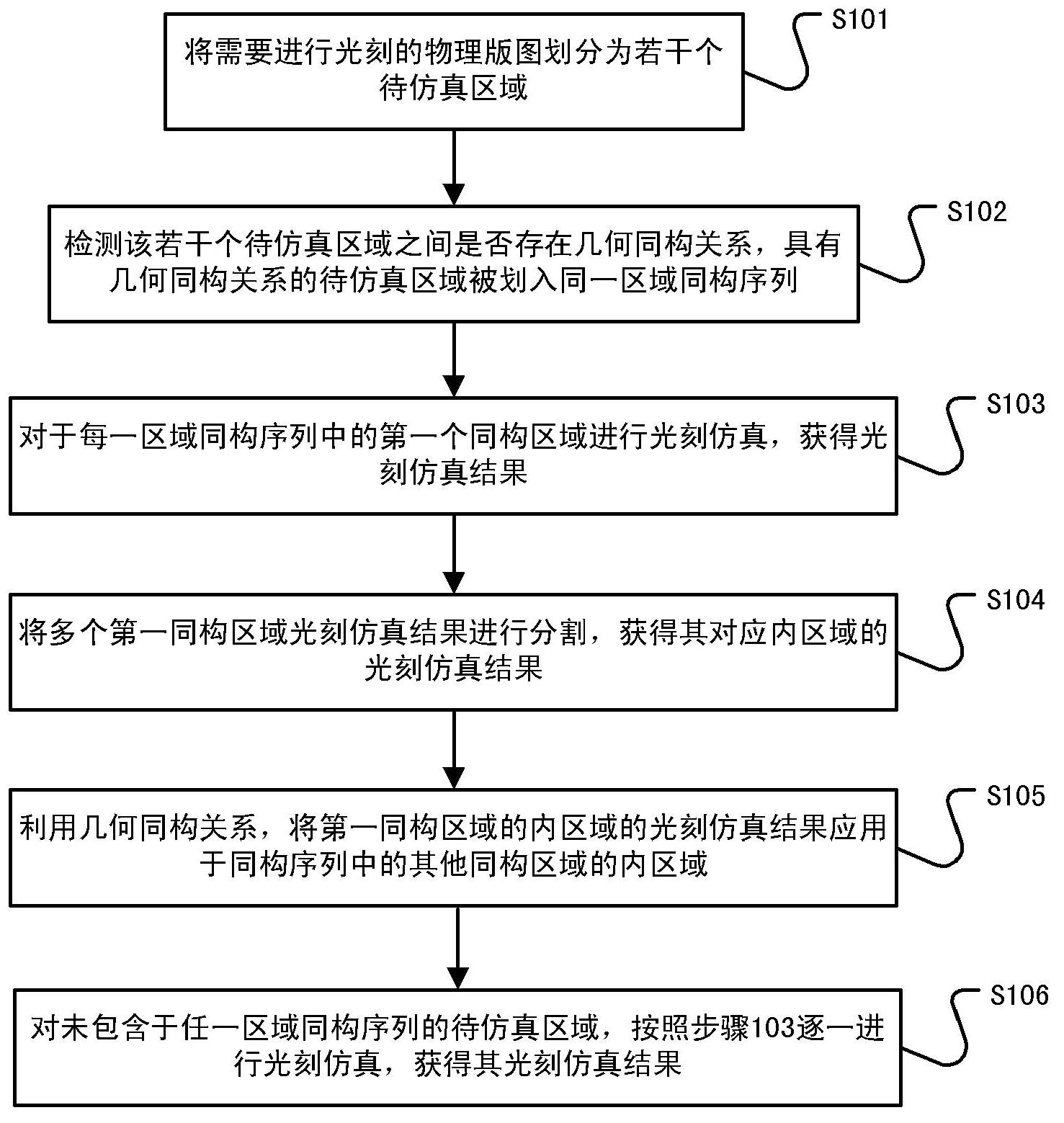

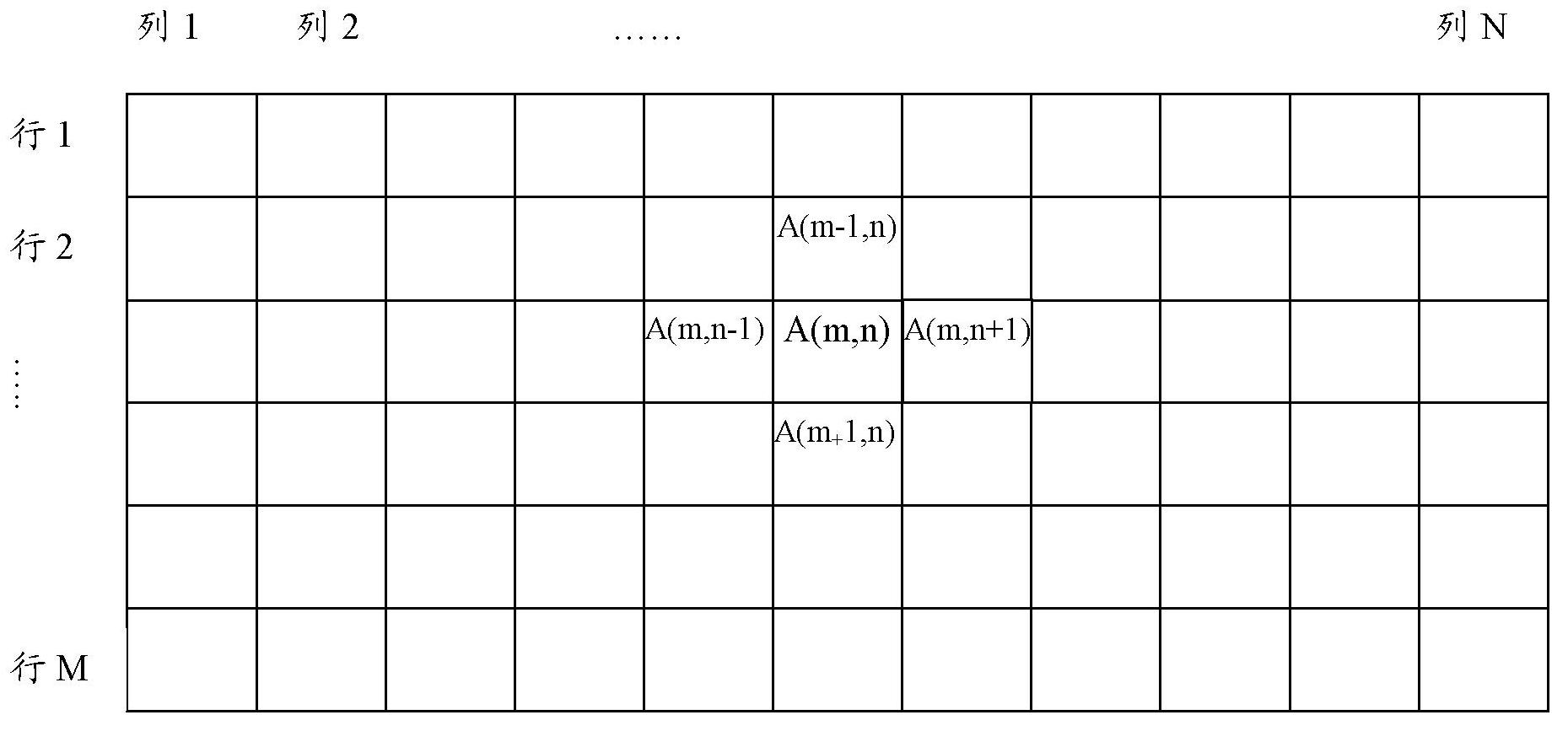

[0021] In the physical design of integrated circuits, there is a great deal of similarity in design patterns between local regions, which determines the similarity of lithography calculation process and calculation results between local regions. Based on the above findings, the present invention merges lithography simulation tasks in a graph isomorphism manner, performs a calculation on the same physical layout lithography simulation task based on gr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More