Nitride read only memory (NROM) structure device with low operating voltage

A low operating voltage, device technology, applied in the field of NROM structure devices, can solve the problems of high programming voltage, unit misprogramming, unfavorable memory chip density, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

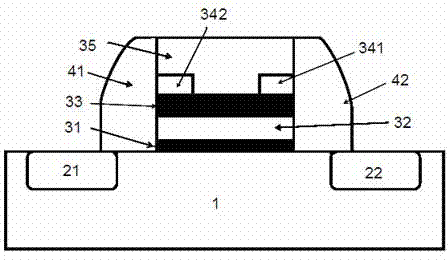

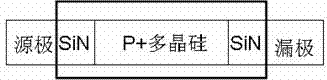

[0023] First prepare the P-type silicon substrate 1, firstly prepare a layer of 3.5nm bottom silicon oxide layer 31 on it, and then prepare a charge-storage silicon nitride layer 32 (N1) with a thickness of about 7nm for storing charges thereon. A blocking silicon oxide layer 33 (O2) of 5 nm thick is then prepared thereon. A silicon nitride layer 34 is deposited thereon, and the middle silicon nitride 34 is removed, and the ratio of the silicon nitride 341 and 342 at both ends and the middle area is controlled at 1:3:1. Then, P-type polysilicon 35 is deposited by an in-situ deposition method, and redundant polysilicon 35 is removed by etching. Finally, sidewalls 41, 42 and source and drain electrodes 21, 22 are formed, thereby forming figure 1 The structure diagram, figure 2 yes figure 1 top view diagram.

Embodiment 2

[0025] First prepare the P-type silicon substrate 1, first prepare a layer of 3.5nm bottom silicon oxide layer 31 on it, and then prepare a charge-storage silicon nitride layer 32 (N1) with a thickness of about 7nm for storing charges on it. . A blocking silicon oxide layer 33 (O2) of about 5 nm thickness is then prepared thereon. P-type polysilicon 35 is deposited thereon, and the polysilicon at both ends is removed, and the ratio between the area at the two ends removed by etching and the remaining area is controlled at 1:3:1. Finally, silicon nitride 341, 342 is deposited, excess silicon nitride is removed, and then sidewalls 41, 42 and source and drain electrodes 21, 22 are formed, so as to form figure 1 The structure diagram, figure 2 yes figure 1 top view diagram.

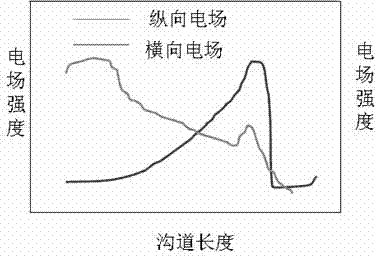

[0026] image 3 It is a schematic diagram of the relationship between the lateral electric field along the channel and the longitudinal electric field of the vertical channel and the channel length of t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com