Chip packaging method and wafer manufactured through chip packaging method

A chip packaging and wafer technology, used in semiconductor/solid-state device manufacturing, printing devices, printing, etc., can solve problems such as chip overflow, and achieve the effect of avoiding wafer warpage and avoiding the separation of adhesive and chip.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The specific implementation of the chip packaging method provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

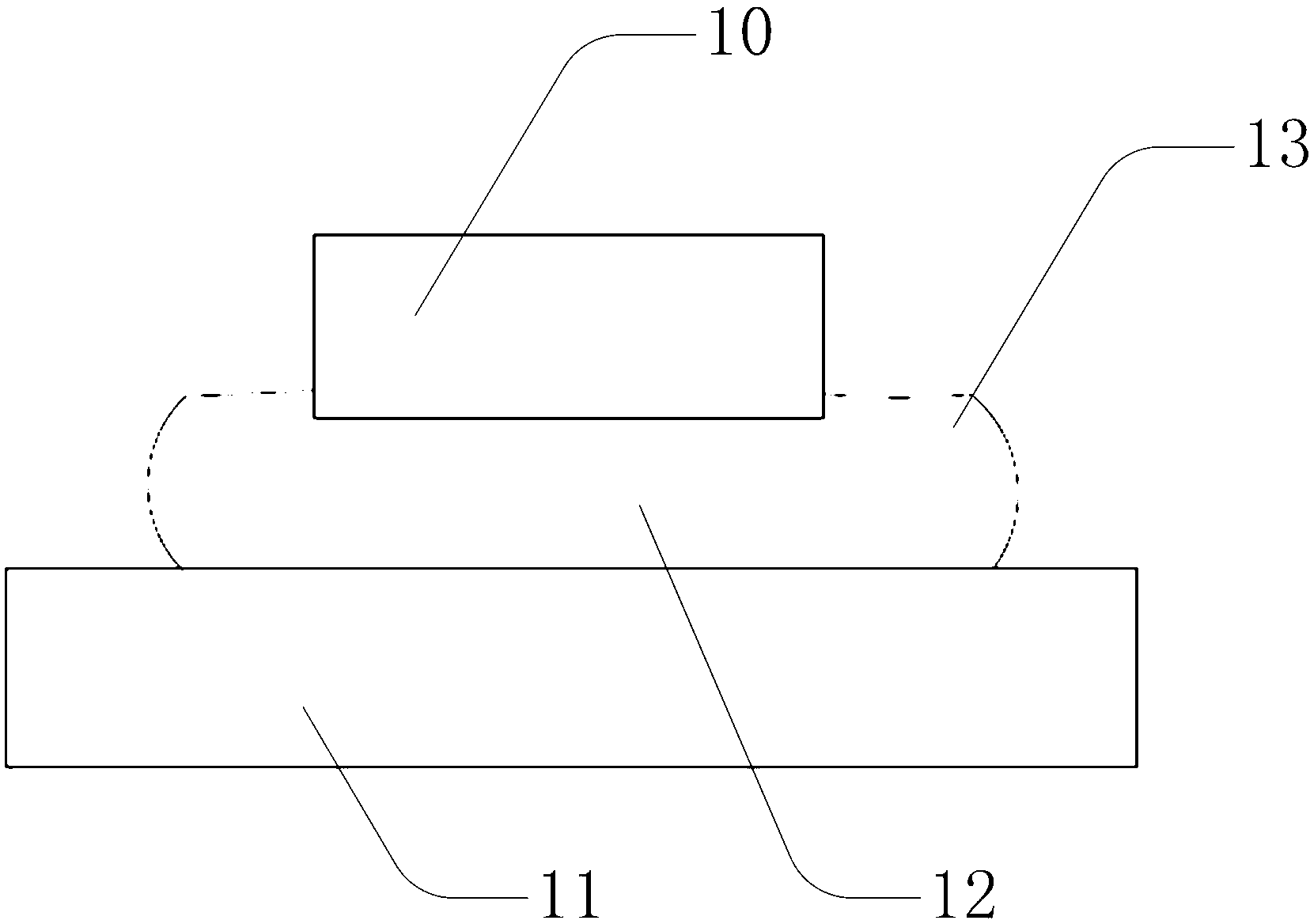

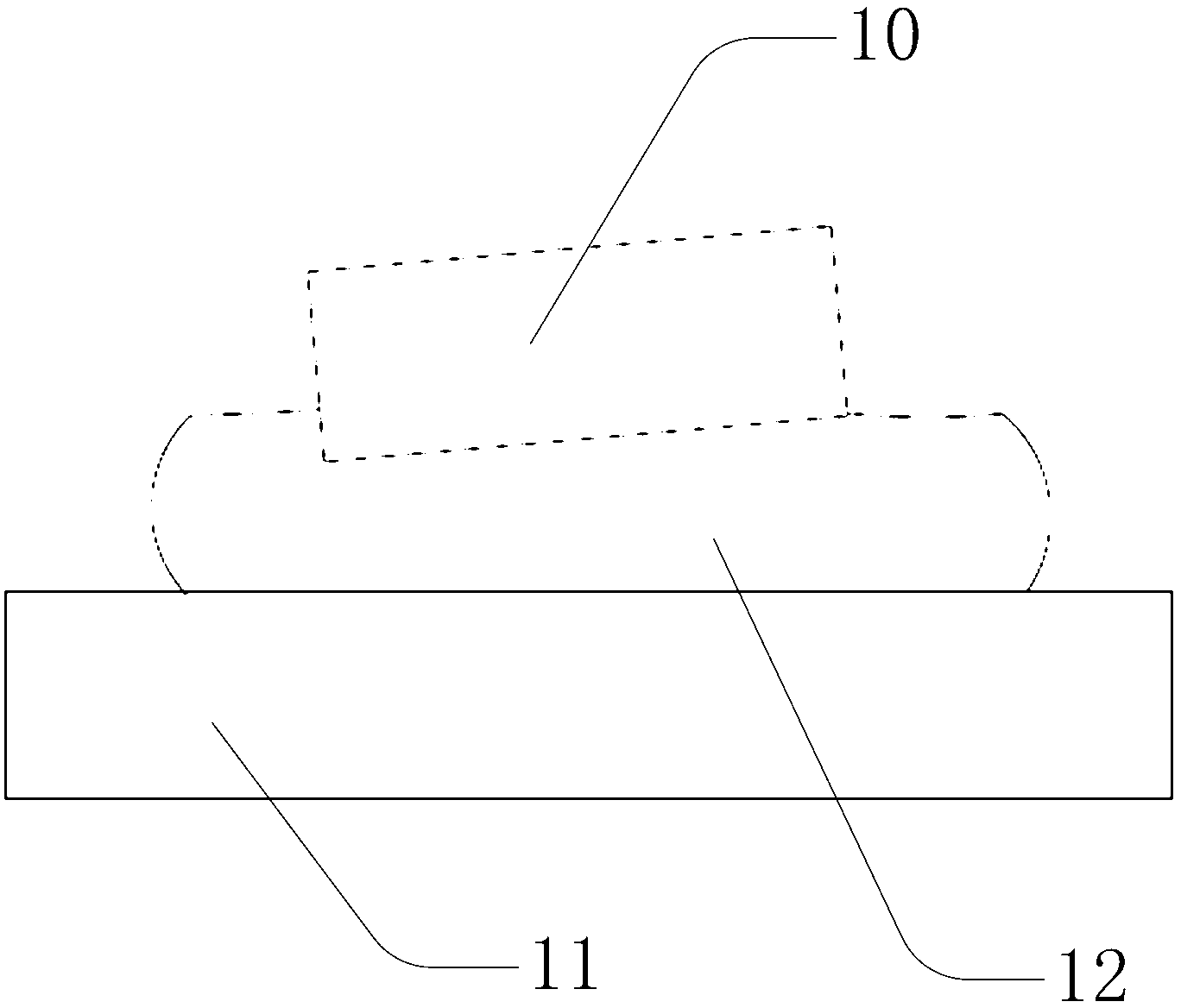

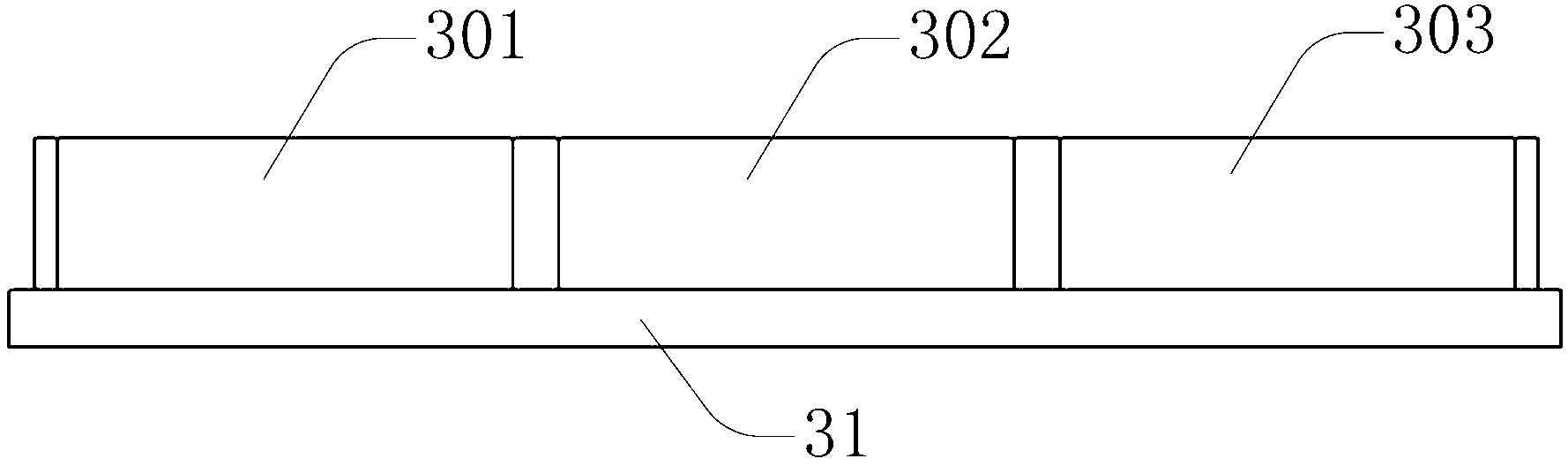

[0033] Figure 4 A schematic diagram of the steps of the chip packaging method of the present invention is shown. see Figure 4 , the chip packaging method includes the following steps: step S40, providing a wafer, the front of the wafer has a plurality of chips; S41, printing a chip adhesive on the back of each chip of the wafer with a screen, the screen has Multiple holes, each corresponding to a chip position; S42, dicing the wafer into multiple individual chips, each chip has an adhesive on the back; S43, providing a lead frame, and passing the chip through the bonding on the back paste on the lead frame; S44, wire bonding; S45, plastic packaging.

[0034] Figure 5A Shown is a schematic diagram of the wafer structure used in the present invention, and a plurality of chips 501 are distribute...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More