A kind of power mosfet device and its making method

A device and power technology, applied in the field of MOSFET devices and their manufacturing, can solve the problem that it is difficult to further improve the withstand voltage of the device terminal area, and achieve the effects of improving processing reliability, improving reliability and avoiding wafer warpage.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

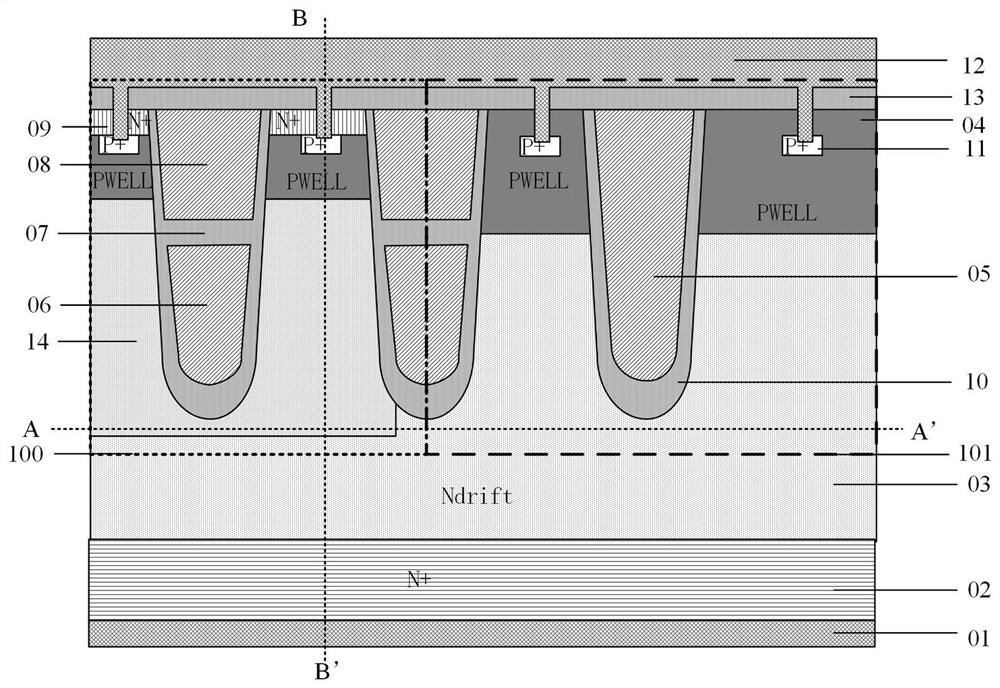

[0037] Refer to the attached figure 1 , the present invention discloses a power MOSFET device, the power MOSFET device is divided into an active region 100 and a terminal region 101, including a drain metal 01, and a first conductive type substrate 02 is arranged on the drain metal 01 , a first conductivity type epitaxial layer 03 is provided on the first conductivity type substrate 02, a second conductivity type epitaxial layer 04 is provided on the first conductivity type epitaxial layer 03, and the active region 100 is provided with a second conductivity type epitaxial layer 04. A first conductive type well region 14 is provided in the first conductive type epitaxial layer 03 and the second conductive type epitaxial layer 04 .

[0038] A first-type trench 07 and a second-type trench 10 made of insulating materials such as silicon dioxide are provided in the first-conductivity-type epitaxial layer 03 and the second-conductivity-type epitaxial layer 04. The first-type trench ...

Embodiment 2

[0042] A manufacturing method of a power MOSFET device, comprising the following steps:

[0043] Step 1: Select the material of the first conductive type substrate 02 and epitaxially grow the first conductive type epitaxial layer 03 on the surface thereof;

[0044] Step 2: using a mask window, selectively implanting first-conductivity-type ions into the active region 100 on the surface of the first-conductivity-type epitaxial layer 03 to form a first-conductivity-type well region 14;

[0045] Step 3: epitaxially form a second conductivity type epitaxial layer 04 on the surface of the first conductivity type epitaxial layer 03, and the first conductivity type well region 14 diffuses to the second conductivity type epitaxial layer 04 due to the high temperature during the epitaxy process middle;

[0046] Step 4: selectively etching the first type trench 07 in the active region 100 and the second type trench 10 in the terminal region 101 on the upper surface of the second conduc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More